# Current Saturation and Voltage Gain in Bilayer Graphene Field Effect **Transistors**

B. N. Szafranek,\*,† G. Fiori,† D. Schall,† D. Neumaier,<sup>§,†</sup> and H. Kurz<sup>†,§</sup>

Supporting Information

ABSTRACT: The emergence of graphene with its unique electrical properties has triggered hopes in the electronic devices community regarding its exploitation as a channel material in field effect transistors. Graphene is especially promising for devices working at frequencies in the 100 GHz range. So far, graphene field effect transistors (GFETs) have shown cutoff frequencies up to 300 GHz, while exhibiting poor voltage gains, another important figure of merit for analog high frequency applications. In the present work, we show that the voltage gain of GFETs can be improved significantly by using

bilayer graphene, where a band gap is introduced through a vertical electric displacement field. At a displacement field of -1.7 V/nm the bilayer GFETs exhibit an intrinsic voltage gain up to 35, a factor of 6 higher than the voltage gain in corresponding monolayer GFETs. The transconductance, which limits the cutoff frequency of a transistor, is not degraded by the displacement field and is similar in both monolayer and bilayer GFETs. Using numerical simulations based on an atomistic  $p_z$  tight-binding Hamiltonian we demonstrate that this approach can be extended to sub-100 nm gate lengths.

KEYWORDS: Bilayer graphene, field effect transistor, graphene devices, current saturation, voltage gain

The investigation of the ultimate potential and performance of graphene field effect transistors (GFET)<sup>1-3</sup> in radio frequency (RF) applications is currently one of the hot topics in the electrical engineering community.<sup>4</sup> Although the so far achieved cutoff frequencies  $f_{\rm T}$  in GFETs up to 300 GHz are quite promising for future applications,  $^{5-7}$  the fabricated devices show poor voltage gain. This could be a roadblock for their exploitation in RF electronics. The intrinsic voltage gain of a field effect transistor can be expressed by the transconductance g<sub>m</sub> and the output conductance g<sub>d</sub>. The former  $(g_{\rm m})$  is the derivative of the drain-current  $I_{\rm d}$  with respect to the gate voltage and reflects the strength of current modulation in the channel by the gate voltage, while  $g_d$ , the derivative of the drain current by the drain voltage, represents the inverse of the output resistance of the transistor. The intrinsic voltage gain can then be expressed by the ratio  $A_{\rm V}$  =  $g_{\rm m}/g_{\rm d}$ . In graphene very high values of  $g_{\rm m}$  up to 5.9 mS/ $\mu$ m were already obtained, while the weak current saturation yields  $g_d$  values comparable to  $g_m$ , leading to negligible voltage gain.<sup>8</sup> Therefore it is a major challenge to reduce  $g_d$  in GFETs, while preserving  $g_{\rm m}$ .

Up to now, several papers have addressed the output conductance of GFETs, showing that a reduction of g<sub>d</sub> can be achieved by increasing the gate coupling and by optimizing the interface between the graphene and the dielectric layers, which eventually led to  $A_{\rm V}$  close to 10. Although such results are quite promising, they are still far from performance

requirements for future RF devices, where  $A_{\rm V}$  = 30 is targeted for devices with sub-100 nm gate length. 12 The introduction of a small band gap in graphene was already proposed as possible solution to reduce the output conductance and to increase the voltage gain of GFETs. 13 Additionally, a reduction of the ouput conductance would also improve the thermal stability of a graphene based RF circuit. 14 In the present work we have taken this concept and explore the possibility of exploiting bilayer graphene in order to obtain GFETs with large  $A_{\rm V}$ . In bilayer graphene the application of a perpendicular electric displacement field leads to a tunable band gap reaching values up to 300 meV. 15-19 So far, this approach has been adopted to modulate the channel resistance in double- and single-gated bilayer GFETs<sup>20-22</sup> and to realize logic gates based on double-gated bilayer GFETs,<sup>23,24</sup> while an improved current saturation has been observed in bilayer GFETs only at liquid nitrogen temperatures (77 K).<sup>24</sup>

To investigate the effect of the band gap opening in bilayer GFETs on the output characteristics and the voltage gain, we have fabricated double-gated mono- and bilayer GFETs on a Si/SiO<sub>2</sub> substrate with Ni contacts, an Al<sub>2</sub>O<sub>3</sub> top-gate dielectric, and a Ti/Ni top-gate electrode.

Received: November 2, 2011 Revised: February 10, 2012 Published: February 17, 2012

<sup>&</sup>lt;sup>†</sup>Advanced Microelectronic Center Aachen (AMICA), AMO GmbH, Otto-Blumenthal-Strasse 25, 52074 Aachen, Germany

<sup>&</sup>lt;sup>‡</sup>Dipartimento di Ingegneria dell'Informazione, Università di Pisa, Via Caruso 16, 56122 Pisa, Italy

<sup>§</sup>Institute of Semiconductor Electronics, RWTH Aachen University, Sommerfeldstrasse 24, 52074 Aachen, Germany

Highly p-doped Si wafers covered with 90 nm thermally grown SiO<sub>2</sub> were used as a substrate. Prior to the graphene deposition, the substrate was coated with hexamethyldisilazane (HMDS) in a chemical vapor deposition process to make the SiO<sub>2</sub> substrate highly hydrophobic and reduce the hysteresis and intrinsic doping concentration of graphene based FETs.<sup>25</sup> Subsequently, the graphene was exfoliated with an adhesive tape from a natural graphite crystal and deposited on the substrate. The layer number of the graphene flakes was identified using optical microscopy and contrast determination of the graphene relative to the substrate.<sup>26</sup> For several flakes, also Raman spectroscopy has been applied for verification.<sup>27</sup> After graphene deposition, the contact electrodes were fabricated by photolithography, sputter deposition of 40 nm nickel and a subsequent lift-off process. The top-gate dielectric was deposited by thermal evaporation of 1 nm Al serving as a seed layer for the subsequent atomic layer deposition of 10 nm Al<sub>2</sub>O<sub>3</sub>. This resulted in an equivalent oxide thickness of 8 nm. The top-gate electrode consisting of 5 nm Ti and 40 nm Ni was defined with photolithography, sputter deposition, and lift-off. Ti has been chosen as the lower metal layer, because the work function mismatch between Ti and graphene leads to a slight ntype doping of the graphene channel.<sup>29</sup> An optical micrograph of a fabricated device is depicted in the inset of Figure 1. The

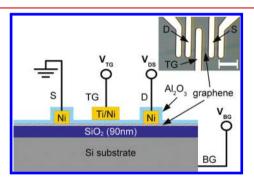

**Figure 1.** Experimental setup. Schematic of a double-gated GFET and the corresponding measurement setup used in our experiments. Inset: Optical micrograph of a double-gated bilayer GFET. The scale bar is  $10~\mu m$ .

gate length of all devices (2 monolayer and 3 bilayer GFETs) is 4  $\mu \rm m$  and the graphene channel width ranges from 4 to 9  $\mu \rm m$ . The length of the ungated graphene channel is 3  $\mu \rm m$  on each side of the top-gate electrode. We note that the charge carrier density and thus the resistance of the ungated graphene channel is strongly influenced by the applied back-gate voltage. All samples were measured in a needle probe station in nitrogen atmosphere at room temperature after an in situ annealing at 200 °C for one hour. For electrical characterization, a HP 4156 semiconductor parameter analyzer was used. The top-gate, source, and drain electrode were contacted using needle probes, and the back-gate voltage was applied to the substrate through the sample carrier. The sample has been biased as illustrated in Figure 1.

In the bilayer GFETs, the energy gap is manifested by a decrease of the minimum channel conductivity with increasing back-gate voltage  $V_{\rm BG}$  from -10 to -60 V. This results in an increased current modulation up to a value equal to 30, which is about a factor of 10 larger than the current modulation in the monolayer GFETs (see Supporting Information). From the transfer characteristics we have determined the field effect mobility. In the monolayer it is  $2200 \, \mathrm{cm}^2/(\mathrm{Vs})$  while in the

bilayer it is 2000 cm<sup>2</sup>/(Vs). These values are comparable with results shown in the literature for monolayer<sup>6,10</sup> and bilayer devices.<sup>21,30</sup>

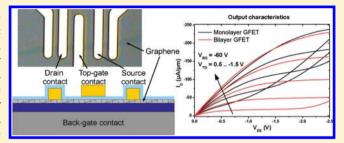

In Figure 2a,b, we show the output characteristics for a monolayer and a bilayer GFET at a back-gate voltage of -60 V.

**Figure 2.** Output characteristics. Current as a function of the source-drain voltage of (a) a monolayer GFET and (b) a bilayer GFET at a back-gate voltage  $V_{\rm BG}=-60~\rm V$ . The top-gate voltage  $V_{\rm TG}$  ranges from  $-1.5~\rm to~0.5~\rm V$  with  $0.5~\rm V$  steps.

The back-gate displacement field is around  $-1.7~\rm V/nm$ . This vertical displacement field introduces an electrically effective gap of approximately 80 meV in the bilayer graphene. Details on the calculation of the displacement field and the estimation of the energy gap are given in the Supporting Information. As can be seen in Figure 2, drain-current saturation is much more pronounced in the bilayer GFET compared to the monolayer GFET, where the lack of a band gap does not allow a proper pinch-off of the channel. The corresponding output conductance is by a factor of 10 smaller in the bilayer GFET compared to the monolayer GFET (0.002 and 0.02 mS/ $\mu$ m, respectively). Furthermore, drain-current saturation in the bilayer GFET is observable in a wider  $V_{\rm DS}$  range and at lower drain current densities. These improvements lead to a higher thermal stability and a lower power consumption compared to a monolayer GFET.

Current saturation in field effect transistors can be either due to electrostatic pinch-off of the channel or to velocity saturation of the charge carriers.<sup>32</sup> In the first case, transconductance is linear with the gate voltage, while in the second case it remains constant. In our monolayer GFET, the S-shape output characteristic is due to a local pinch-off of the channel as

previously shown by Meric et al.<sup>31</sup> For the bilayer GFET case instead, we have verified a linear dependence of  $g_{\rm m}$  on  $V_{\rm TG}$  (see Supporting Information). Therefore, we can conclude that the reduced output conductance in the bilayer GFET has to be imputed to an improved pinch-off of the channel, due to the electrostatically induced band gap.

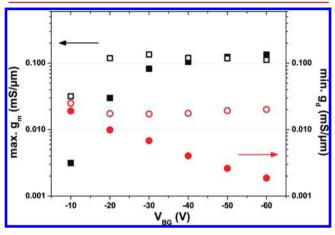

To investigate in more details the effect of the applied backgate voltage on the minimum output conductance (i.e., the influence of a band gap on the current saturation), we plot in Figure 3  $g_{\rm d}$  as a function of  $V_{\rm BG}$  for the monolayer and the

**Figure 3.** Maximum values of the transconductance  $g_{\rm m}$  (squares) and minimum values of the output conductance  $g_{\rm d}$  (circles) as a function of the applied back-gate voltage  $V_{\rm BG}$  for a monolayer (open symbols) and a bilayer GFET (filled symbols).

bilayer GFET. The data of all investigated devices is included in the Supporting Information. As can be seen,  $g_{\rm d}$  in the monolayer GFET depends only weakly on the applied backgate voltage, while a reduction by an order of magnitude can be observed in the bilayer device, when decreasing  $V_{\rm BG}$  from -10 to -60 V. This behavior is a clear signature of band gap opening in bilayer graphene for increasing vertical displacement field. The observed minimum output conductance in the monolayer GFETs is in the range of 0.02 to 0.05 mS/ $\mu$ m, which is in agreement with results shown for other monolayer GFETs.  $^{6-11}$  At  $V_{\rm BG}=-60$  V, the minimum output conductance in the bilayer GFETs is by a factor of 10 smaller in the range of 0.002 to 0.004 mS/ $\mu$ m.

Figure 3 also shows the maximum transconductances  $g_m$  for the monolayer and bilayer GFET as a function of the back-gate voltage. For small  $V_{\rm BG}$  from -10 to -20 V, we observe for both devices an initial increase of  $g_{\rm m}$ , which can be related to the reduction of the resistance in the ungated graphene channel by the applied  $V_{\rm BG}$ . At larger  $V_{\rm BG}$  (-30 to -60 V), we cannot observe a clear dependence of  $g_{\mathrm{m}}$  on the applied  $V_{\mathrm{BG}}$ . Furthermore, the transconductance  $g_m$  shows a similar behavior in the monolayer and the bilayer GFET. These findings can provide relevant information combined with the cutoff frequency  $f_T$ , which can be expressed in the quasi-static approximation as  $f_T = g_m/(2\pi C_G)$ , where  $C_G$  is the gate capacitance. Since the transconductance  $g_m$  does not degrade with increasing vertical displacement field, we can state that an improvement of the output conductance does not degrade  $f_{T}$ , as also demonstrated theoretically.<sup>14</sup>

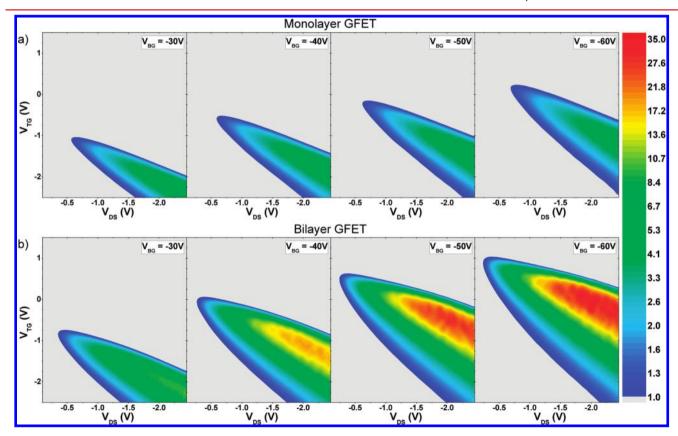

Figure 4. Contour plots of the voltage gain versus source-drain and top-gate voltage in a monolayer (a) and a bilayer GFET (b). The plots were calculated from the measured output characteristics at different applied back-gate voltages from -30 V (left) to -60 V (right). The voltage gain is color-coded in logarithmic scale.

The voltage gain  $A_V$  extracted from the output and transfer characteristics for the mono- and bilayer GFETs is plotted in Figure 4 as a function of  $V_{TG}$  and  $V_{DS}$  for different back-gate voltages; the light gray region refers to  $A_{\rm V}$  < 1. We observe that for the monolayer GFET the maximum value of A<sub>V</sub> is 6 independent of the  $V_{\rm BG}$ , while for the bilayer GFET the  $A_{\rm V}$ increases from 10 at  $V_{\rm BG}$  = -30 V to 35 at  $V_{\rm BG}$  = -60 V. Also, voltage gain is observed on a wider voltage region for bilayer than for the monolayer GFET. For both cases, the maximum shifts toward the top of the  $V_{\rm TG}-V_{\rm DS}$  plane for negatively increasing  $V_{\rm BG}$  that is due to the induced Fermi level shift within the channel. We conclude that the increase in voltage gain is a direct consequence of the reduction of the output conductance in the bilayer GFET, when increasing the applied negative back-gate voltage. The very same behavior has been observed in all the investigated samples, that is, three bilayer and two monolayer GFETs.

Parasitic effects like charge traps can distort a correct measurement of the output characteristics and even lead to a negative  $g_{\rm d}$ . In those cases,  $g_{\rm m}/g_{\rm d}$  does not reflect the intrinsic voltage gain properly. To check wether such effects compromise our measurements, we also have directly measured the voltage gain of a bilayer GFET integrated in a simple circuit. The measured voltage gain of the circuit was in excellent agreement with the values calculated from  $g_{\rm m}$  and  $g_{\rm d}$  (see Supporting Information). Thus, we are convinced that  $A_{\rm V} = g_{\rm m}/g_{\rm d}$  reflects the intrinsic voltage gain of the investigated devices and is not affected by parasitic effects.

The fabricated devices with a gate length of 4  $\mu$ m have rather large dimensions compared to state-of-the-art FETs, which have gate lengths in the submicrometer regime. In order to understand if drain-current saturation and voltage gain can still be observed in ultrashort channel devices, we have performed accurate numerical simulations based on an atomistic  $p_z$  tightbinding Hamiltonian. To this purpose, we have made extensive use of the open-source code NanoTCAD ViDES, 33 and we have performed simulations based on the self-consistent solution of the 2D Poisson and the Schroedinger equation with open boundary conditions, within the non-equilibrium Green's function (NEGF) formalism. Details on the simulations are given in the Supporting Information. The simulations show that improved output characteristics can still be observed for bilayer GFETs but not in monolayer GFETs, even when considering a short gate length of 40 nm. The simulated bilayer GFET shows a voltage gain of up to 10, while the monolayer device does not show any voltage gain  $(A_V < 1)$ . Such differences have to be attributed to the induced band gap in bilayer GFETs. The simulations demonstrate that using monolayer graphene without a band gap might be a road block for analog high frequency applications, where a voltage gain is required. Bilayer graphene with a band gap offers instead a viable option.

In summary, we have demonstrated that GFETs with a bilayer graphene channel are more suitable to achieve excellent current saturation and voltage gain. Thus, bilayer GFETs might show a higher thermal stability and reduced power consumption compared to monolayer devices. The main reason is the decreasing output conductance with increasing band gap in the bilayer graphene. Furthermore, we showed that the theoretical cutoff frequency  $f_{\rm T}$  is not influenced by the opening of the band gap. Through numerical simulations we demonstrated that current saturation and voltage gain can still be achieved in ultrascaled bilayer GFETs.

#### ASSOCIATED CONTENT

# **S** Supporting Information

Top- and back-gate transfer characteristics including comments on current modulation. Output characteristics at lower back-gate voltages. Dependence of the transconductance versus top-gate voltage in the saturation regime. Minimum output conductance and maximum transconductance of all investigated devices. Estimation of the maximum displacement field and the maximum energy gap. Comparison of calculated and measured voltage gain. Details on the simulations including device parameters, output characteristics, and voltage gain. This material is available free of charge via the Internet at http://pubs.acs.org.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: szafranek@amo.de.

#### **Notes**

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by the European Union under contract number 215752 ("GRAND"), by the German Science Foundation DFG under contract number BA 3788/2-1 ("Ultragraphen") and by the MIUR-PRIN project GRANFET (Prot. 2008S2CLJ9).

#### REFERENCES

- (1) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. *Science* **2004**, *306*, 666–669.

- (2) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Katsnelson, M. I.; Grigorieva, I. V.; Dubonos, S. V.; Firsov, A. A. *Nature* **2005**, 438, 197–200.

- (3) Zhang, Y.; Tan, Y.-W.; Stormer, H. L.; Kim, P. Nature 2005, 438, 201–204.

- (4) Schwierz, F. Nat. Nanotechnol 2010, 5, 487-496.

- (5) Liao, L.; Lin, Y.-C.; Bao, M.; Cheng, R.; Bai, J.; Liu, Y.; Qu, Y.; Wang, K. L.; Huang, Y.; Duan, X. *Nature* **2010**, *467*, 305–308.

- (6) Lin, Y. M.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H. Y.; Grill, A.; Avouris, P. *Science* **2010**, 327, 662.

- (7) Wu, Y.; Lin, Y.-m.; Bol, A. A.; Jenkins, K. A.; Xia, F.; Farmer, D. B.; Zhu, Y.; Avouris, P. *Nature* **2011**, 472, 74–78.

- (8) Clavel, M.; Poiroux, T.; Mouis, M.; Becerra, L.; Thomassin, J. L.; Zenasni, A.; Lapertot, G.; Rouchon, D.; Lafond, D.; Faynot, O. In *Ultimate Integration on Silicon (ULIS)*; 2011; pp 1–4.

- (9) Meric, I.; Dean, C. R.; Young, A. F.; Hone, J.; Kim, P.; Shepard, K. L. Tech. Dig. Int. Electron Devices Meet. 2010, 556-559.

- (10) Meric, I.; Dean, C. R.; Young, A. F.; Baklitskaya, N.; Tremblay, N. J.; Nuckolls, C.; Kim, P.; Shepard, K. L. *Nano Lett.* **2011**, *11*, 1093–1097.

- (11) Han, S.-J.; Jenkins, K. A.; Valdes Garcia, A.; Franklin, A. D.; Bol, A. A.; Haensch, W. *Nano Lett.* **2011**, *11*, 3690–3693.

- (12) International Technology Roadmap for Semiconductors 2009 Edition, "Radio Frequency and Analog/Mixed-Signal Technologies for Wireless Communications", Table RFAMS1. http://www.itrs.net (accessed Dec 1, 2011).

- (13) Majumdar, K.; Murali, K. V. R. M.; Bhat, N.; Xia, F.; Lin, Y.-M. Tech. Dig. Int. Electron Devices Meet. 2010, 32.4.1–32.4.4.

- (14) Das, S.; Appenzeller, J. IEEE Trans. Nanotechnol. 2011, 10, 1093-1098.

- (15) McCann, E. Phys. Rev. B 2006, 74, 161403.

- (16) Castro, E. V.; Novoselov, K. S.; Morozov, S. V.; Peres, N. M. R.; dos Santos, L.; Nilsson, J.; Guinea, F.; Geim, A. K.; Neto, A. H. C. *Phys. Rev. Lett.* **2007**, *99*, 216802.

- (17) McCann, E.; Fal'ko, V. Phys. Rev. Lett. 2006, 96, 086805.

- (18) Mak, K. F.; Lui, C. H.; Shan, J.; Heinz, T. F. Phys. Rev. Lett. 2009, 102, 256405.

- (19) Zhang, Y.; Tang, T.-T.; Girit, C.; Hao, Z.; Martin, M. C.; Zettl, A.; Crommie, M. F.; Shen, Y. R.; Wang, F. *Nature* **2009**, *459*, 820–823.

- (20) Xia, F.; Farmer, D. B.; Lin, Y.-M.; Avouris, P. Nano Lett. 2010, 10, 715-718.

- (21) Szafranek, B. N.; Schall, D.; Otto, M.; Neumaier, D.; Kurz, H. Appl. Phys. Lett. **2010**, 96, 112103.

- (22) Szafranek, B. N.; Schall, D.; Otto, M.; Neumaier, D.; Kurz, H. Nano Lett. **2011**, *11*, 2640–2643.

- (23) Li, S.-L.; Miyazaki, H.; Lee, M. V.; Liu, C.; Kanda, A.; Tsukagoshi, K. Small **2011**, 7, 1552–1556.

- (24) Li, S.-L.; Miyazaki, H.; Hiura, H.; Liu, C.; Tsukagoshi, K. ACS Nano 2011, 5, 500–506 2011.

- (25) Lafkioti, M.; Krauss, B.; Lohmann, T.; Zschieschang, U.; Klauk, H.; Klitzing, K.; Smet, J. H. *Nano Lett.* **2010**, *10*, 1149–1153.

- (26) Blake, P.; Hill, E. W.; Neto, A. H. C.; Novoselov, K. S.; Jiang, D.; Yang, R.; Booth, T. J.; Geim, A. K. Appl. Phys. Lett. 2007, 91, 063124.

- (27) Ferrari, A. C.; Meyer, J. C.; Scardaci, V.; Casiraghi, C.; Lazzeri, M.; Mauri, F.; Piscanec, S.; Jiang, D.; Novoselov, K. S.; Roth, S.; Geim, A. K. *Phys. Rev. Lett.* **2006**, *97*, 187401.

- (28) Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. *Appl. Phys. Lett.* **2009**, *94*, 062107.

- (29) Xu, H.; Zhang, Z.; Xu, H.; Wang, Z.; Wang, S.; Peng, L.-M. ACS Nano 2011, 5, 5031–5037.

- (30) Taychatanapat, T.; Jarillo-Herrero, P. Phys. Rev. Lett. 2010, 105, 166601.

- (31) Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. L. Nat. Nanotechnol 2008, 3, 654-659.

- (32) Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices, 3rd ed.; Wiley-Interscience: Hoboken, NJ, 2006.

- (33) Fiori, G.; Iannaccone, G. NanoTCAD ViDES, Version 1.21; published on Jul 8, 2009. https://nanohub.org/tools/vides (accessed Dec 1, 2011), DOI:10254/nanohub-r5116.5.