# This is a self-archived version of an original article. This version may differ from the original in pagination and typographic details.

Author(s): Martinella, Corinna; Stark, R.; Ziemann, T.; Alia, R. G.; Kadi, Y.; Grossner, U.; Javanainen, Arto

Title: Current Transport Mechanism for Heavy-Ion Degraded SiC MOSFETs

Year: 2019

Version: Accepted version (Final draft)

Copyright: © 2018 IEEE.

Rights: In Copyright

Rights url: http://rightsstatements.org/page/InC/1.0/?language=en

### Please cite the original version:

Martinella, C., Stark, R., Ziemann, T., Alia, R. G., Kadi, Y., Grossner, U., & Javanainen, A. (2019). Current Transport Mechanism for Heavy-Ion Degraded SiC MOSFETs. IEEE Transactions on Nuclear Science, 66(7), 1702-1709. https://doi.org/10.1109/TNS.2019.2907669

## Current Transport Mechanism for Heavy-Ion Degraded SiC MOSFETs

C. Martinella, *Member, IEEE*, R. Stark, *Member, IEEE*, T. Ziemann, *Member, IEEE*, R. G. Alia, *Member, IEEE*, Y. Kadi, *Member, IEEE*, U. Grossner *Member, IEEE* and A. Javanainen *Member, IEEE*

*Abstract*— High sensitivity of SiC power MOSFETs has been observed under heavy ion irradiation, leading to permanent increase of drain and gate leakage currents. Electrical postirradiation analysis confirmed the degradation of the gate oxide and the blocking capability of the devices. At low drain bias, the leakage path forms between drain and gate, while at higher bias the heavy ion induced leakage path is mostly from drain to source. An electrical model is proposed to explain the current transport mechanism for heavy-ion degraded SiC power MOSFETs.

*Index Terms*— SiC power MOSFETs, heavy ion irradiation, gate leakage, single event effects.

#### I. INTRODUCTION

Wide band-gap semiconductor, such as silicon-carbide (SiC) are very attractive for power devices due to their physical properties. The wide energy bandgap of 3.23 eV (4H SiC at room temperature) allows SiC devices to operate at high voltage, high temperatures and switching frequencies while achieving lower conduction losses in comparison to silicon [1], [2]. SiC devices are expected to be used in harsh environments, indeed it is considered as promising technology for space and accelerator applications, such as the injection kicker pulse generator for the Future Circular Collider [3].

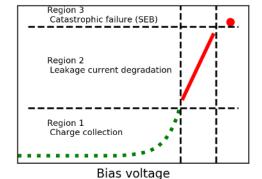

Recently, various studies were performed to investigate the radiation tolerance of SiC devices. High sensitivity has been noticed under heavy ion irradiation and a unique Single Event Effect (SEE) phenomenon has been observed in plain Schottky diodes, junction barrier Schottky diodes [4], [5] and SiC power MOSFETs [6], [7]. While silicon-based power MOSFETs typically directly experience catastrophic failure such as Single Event Gate Rupture (SEGR) or Single Event Burnout (SEB). SiC power MOSFETs, instead, are shown to exhibit three characteristic regions as a function of the drain-source bias conditions during the exposure, as visible in Fig. 1 [6].

Manuscript received October 5, 2018; revised February 3, 2019; accepted February 24, 2019. This work was in part supported by ETH Zurich Foundation and by the European Space Agency under Contract 4000111630/14/NL/PA.

C. Martinella is with CERN Engineering Department, 1211 Geneva 23, Switzerland and with the Department of Physics, University of Jyväskylä, FI-40014 Jyväskylä, Finland (e-mail: <u>corinna.martinella@cern.ch</u>).

A. Javanainen is with the Department of Physics, University of Jyväskylä, FI-40014 Jyväskylä, Finland and with the Electrical Engineering and Computer Science Department, Vanderbilt University, Nashville, TN 37235 USA (e-mail: arto.javanainen@jyu.fi).

R. Stark, T. Ziemann, U. Grossner are with the Advanced Power Semiconductor Laboratory (APS), ETHZ, 8092 Zurich, Switzerland (e-mails: stark@aps.ee.ethz.ch, ziemann@aps.ee.ethz.ch, ulrike.grossner@ethz.ch).

R. G. Alia, Y. Kadi are with CERN Engineering Department, 1211 Geneva 23, Switzerland (e-mails: ruben.garcia.alia@cern.ch, yacine.kadi@cern.ch).

1

Fig. 1. Three characteristic regions of damage for SiC power devices as a function of the drain-source bias during the heavy ion irradiation.

The first non-destructive region occurs at low bias voltages. In this region, the ion-induced charge is collected with a similar multiplication mechanism as in Si MOSFETs and no permanent damage is observed in the device. The second region occurs at higher bias, where a unique phenomenon is observed for SiC devices, causing permanent degradation resulting in increased leakage currents with increasing heavy ion fluence. The damage is not catastrophic, but the device operation may become limited. In the third region, at sufficiently high bias, a SEB occurs leading to a catastrophic failure of the device. The mechanism triggering the SEB in SiC MOSFETs is still under study. Different hypotheses have been formulated.

*Witulski et al.* [7] investigated the SEB through experimental measurements and TCAD simulations. Their work concludes that at sufficiently high current generated by the ion strike and applied bias, the parasitic bipolar junction transistor (BJT) which is an intrinsic part of the device structure, turns on, resulting in the catastrophic SEB. This mechanism is very similar to the SEB in silicon-based power MOSFETs.

In the same work, experimental measurements of SEB threshold voltages versus heavy-ions LET for 1200 V SiC MOSFETs are reported and compared with previous results based on the works of *Mizuta et al.* [6] and *Lauenstein et al.* [8]. In their work, all the MOSFETs exhibit catastrophic failure at bias voltage significantly lower than the rated 1200 V when exposed to heavy ions with LET values above  $10 \text{ MeV}/(mg/cm^2)$ . Conversely, at LET values below  $10 \text{ MeV}/(mg/cm^2)$ , SEB occurs at higher voltages and the region for ion-induced degradation (region 2 above) becomes narrower. Finally, at very low LET values, there is a direct transition from region 1 to region 3 as drain bias is increased, hence no permanent non-destructive leakage current increase is observed for light ions, including protons.

Shoji et al. studied the neutron-induced SEB in SiC power diodes [9] and SiC power MOSFETs [10] through experiments and TCAD simulations, concluding, differently, that an SEB can occur in a diode structure without activating the parasitic npn transitor. They claim that the catastrophic failure occurs due to a shift in the peak electric field in the n<sup>-</sup>drift/n<sup>+</sup> interface and punch-through of the electric field to the cathode at the device surface. Through TCAD simulations, *Shoji et al.* demonstrated similar mechanism in SiC power MOSFETs as a shift in the peak electric field and a punch-through at the n<sup>+</sup> source diffusion region.

Additionally, *Asai et al.* [11] performed studies with neutrons, concluding that there exists no consistent difference in SEB tolerance between SiC diodes and SiC MOSFETs and that the conventional SEB mechanisms developed in Si MOSFETs, such as parasitic bipolar transistor and tunneling assisted avalanche multiplication mechanism, may be suppressed in SiC devices [12].

For SiC MOSFETs the previous studies have mostly concentrated on the SEB and the permanent increase in the drain leakage. The ion-induced gate damage (such as SEGR) in these devices has not been previously discussed in that detail. For silicon power MOSFETs instead, the ion-induced effect in the gate oxide has been studied quite widely previously [13]. For SEGR the mechanism has been concluded as following. The primary ionizing ion generates electron-hole-pairs along the path through the oxide and the semiconductor, creating a track of ionized plasma in the active layer of the device. For an n-type device in off-state with a positive V<sub>DS</sub>, electrons move towards the drain (in VD-MOSFETs represented by the backside substrate and contact), while a high concentration of holes is created at the Si/SiO2 interface. Mirror charges are then induced at the gate and this creates a transient field across the oxide in addition to the applied field [14] [15]. Furthermore, the critical field required for the oxide breakdown is thought to be decreased by the ionization within the oxide induced by the impinging particle. The oxide response in Si power MOSFETs was described for the first time in [16].

A detailed description of SEGR mechanisms caused by heavy ions in Si Power MOSFETs is given in [17]. The important ion beam characteristics for inducing SEGR are the Linear Energy Transfer (LET) and the total energy deposited in the epitaxial layer (including the epi/substrate interface region).

Finally, three different types of SEGR modes have been proposed for Si power MOSFETs [18]; the micro-break, the thermal runaway and the avalanche breakdown. The proposed model for an enhanced gate current associated with a microbreak is that oxide defects from displacement damage caused by the ion hit create a significant number of damage sites at which there is a reduced potential barrier, permitting the tunneling of electrons from trapping sites in the oxide into the conduction band.

In this paper, we focus on the second region of degradation as shown in Fig.1, investigating the permanent non-catastrophic damage observed in SiC power MOSFETs during heavy ion irradiations. The results from the irradiation experiment and the electrical analysis are reported and discussed. The degradation rates were also calculated for all the tested devices and observed to be independent on the prior degradation. Finally, a mechanism describing the radiation induced leakage paths within the device structure is proposed and combined with simulations using an equivalent circuit to model this leakage.

#### II. EXPERIMENTAL METHODS

#### A. Experimental Setup

The heavy ion experiments were performed at the RADiation Effects Facility (RADEF) in the Accelerator Laboratory of the University of Jyväskylä, Finland. Three types of 4H-SiC MOSFETs from the manufacturer Cree/Wolfspeed, available as bare die (CPM2-1200-0025B, CPM2-1200-0080B, and CPM2-1200-0160B), were selected as devices under test (DUTs). All three DUTs are rated for  $V_{DS} = 1200 V$ , but differ in R<sub>DS(on)</sub> (25 m $\Omega$ , 80 m $\Omega$ , and 160 m $\Omega$ , respectively). All three types of devices are of the 2<sup>nd</sup> generation, and the different R<sub>DS(on)</sub> have been achieved by adjusting the active area in the die. This work discusses mostly the results for the 80 m $\Omega$  irradiations.

Bare die were used in order to directly expose the chip surface to the beam to allow sufficient penetration of the heavy ions through the sensitive layers of the device, without being stopped in the package materials.

The die were mounted on custom FR-4 carrier boards with gold (ENIG) surface using standard SAC 305 solder paste. While the drain connection was made by the large soldered bottom pad, the gate and source were connected by aluminum wire bonds with 300  $\mu$ m diameter. To minimize shadowing by the wires, only a single source wire was used. Each board housed 5 die individually biased with BNC connectors for gate and drain. Keithley Source Measure Unit models 2636 (two channels, up to 200V) and 2410 (one channel, up to 1100V) were used for biasing gate and drain respectively.

TABLE I

CHARACTERISTICS OF THE ION SPECIES USED IN THIS STUDY

| Ion                              | Energy<br>[MeV] | Energy/<br>nucleon<br>[MeV/amu] | LET <sup>SRIM</sup> @surface<br>[MeV/mg/cm <sup>2</sup> ] | Range<br>SiC <sup>SRIM</sup><br>[µm] |

|----------------------------------|-----------------|---------------------------------|-----------------------------------------------------------|--------------------------------------|

| <sup>56</sup> Fe <sup>+15</sup>  | 523             | 9.33                            | 20.05                                                     | 65.63                                |

| ${}^{82}\mathrm{Kr}^{+22}$       | 768             | 9.36                            | 33.75                                                     | 63.89                                |

| <sup>131</sup> Xe <sup>+35</sup> | 1217            | 9.29                            | 62.39                                                     | 61.43                                |

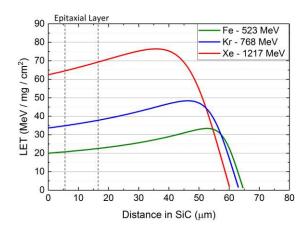

Fig. 2. Bragg curves as function of the penetration depth with SiC.

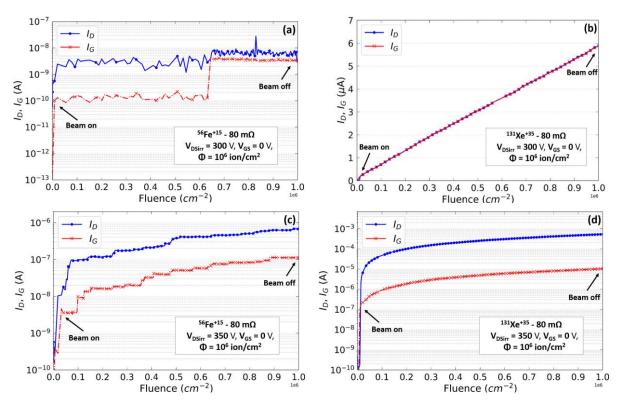

**Fig. 3.** Equal rate of increase in the gate and drain leakage currents during the irradiation at  $V_{DSirr} = 300$  V with <sup>56</sup>Fe<sup>+15</sup> (a) and <sup>131</sup>Xe<sup>+35</sup> (b). Each step in the leakage currents is caused by a single incident heavy ion. The y-axis in figure (b) is in linear scale and  $\mu$ A unit. At 350 V and above, the drain leakage increases with higher rate than the gate leakage, as visible during <sup>56</sup>Fe<sup>+15</sup> (c) and <sup>131</sup>Xe<sup>+35</sup> (d) irradiation. The fluence in each case was 10<sup>6</sup> ions/cm<sup>2</sup> with an uncertainty of +10%.

#### B. Heavy Ion Irradiation Tests

The boards were mounted in a vacuum chamber and the die exposed to a fluence of  $1x10^6$  ions/cm<sup>2</sup> during the test runs, while bias voltages were kept constant. The heavy ion species used during the test were  $^{131}Xe^{+35}$ ,  $^{82}Kr^{+22}$  and  $^{56}Fe^{+15}$ , with an energy per nucleon of ~ 9.3 MeV/amu. The ion characteristics are listed in Table 1. While the gate voltage V<sub>GS</sub> was set to 0 V to hold the device in off state, the drain voltage V<sub>DS</sub> was set to constant positive value during the irradiation and increased after each run until the device was considered broken due to the degradation. The I<sub>D</sub>-V<sub>DS</sub> and I<sub>G</sub>-V<sub>GS</sub> curves were measured after each run. The beams were at normal incidence to the DUT surface. All the irradiations and the I-V characterizations were performed at room temperature.

The ion LET versus the penetration depth in SiC was estimated with ECIF (European Component Irradiation Facility) Cocktail Calculator [19]. The Bragg curves for each ion species used in the tests are reported in Fig. 2. The epitaxial layer is highlighted in the figure by vertical dashed lines and it extends from 5  $\mu$ m until 18  $\mu$ m from the die surface. This confirms that the energy deposition is well defined within the active layer and the ions penetrate deep enough in the device structure to meet the worst-case energy deposition criterion as discussed in [20]. The main source of uncertainty is due to the fluence measurement and, in general, for the RADEF facility an error of +10% is considered.

#### C. Degradation Rate and Post Irradiation Analysis

The die were irradiated at different  $V_{DS}$  bias conditions and the drain and gate leakage currents were measured during the exposure. The degradation rate is defined as the difference between the leakage current measured at the end of the run (after exposure to the beam) and at the beginning of it (before exposure) normalized by the fluence and the active area of the die. The active area was calculated from the microscope images as the metallized area subtracted with the gate pad and the gate conductors. The shadowing effect due to the bond wires was estimated, obtaining an active area of 19.92 mm<sup>2</sup> for the 25 m $\Omega$ , 5.74 mm<sup>2</sup> for the 80 m $\Omega$  and 2.75 mm<sup>2</sup> for the 160 m $\Omega$  die.

3

Moreover, electrical analysis of the die was performed before and after the irradiation at the Advanced Power Semiconductor Laboratory (APS) at ETH Zurich, using a wafer probe station MPI TS200-HP connected with a measurement equipment Keithley PCT-4B.

#### III. RESULTS

#### A. Current Measurements During Irradiation

Drain and gate leakage currents were monitored during the exposure of the DUTs. If the device degradation was not severe at the end of the run, the V<sub>DS</sub> was increased, while V<sub>GS</sub> was kept constant at 0 V. At sufficiently high V<sub>DS</sub> bias, the same increase in absolute value of the drain and the gate leakage currents were observed during the exposure. The threshold drain-source voltage to observe degradation was determined at  $V_{DS}$  irr = 300 V, 200 V and 120 V during the irradiation with <sup>56</sup>Fe<sup>+15</sup>, <sup>82</sup>Kr<sup>+22</sup> and <sup>131</sup>Xe<sup>+35</sup> respectively. Fig. 3 presents the absolute values of I<sub>D</sub> and I<sub>G</sub> as a function of exposure time for two pristine 80 mΩ DUTs irradiated at  $V_{DS} = 300$  V with <sup>56</sup>Fe<sup>+15</sup> (a) and <sup>131</sup>Xe<sup>+35</sup> (b). Each step in the current is caused by a single

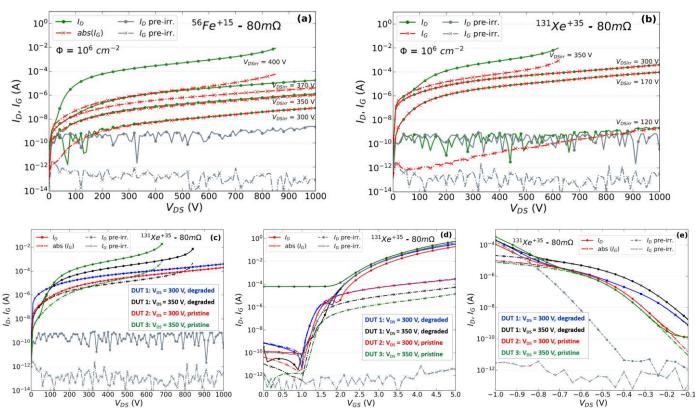

**Fig 4.** Post-irradiation  $I_D V_{DS}$  and  $I_G V_{DS}$  curves for 80 m $\Omega$  DUTs irradiated with  ${}^{56}Fe^{+15}$  (a) and  ${}^{131}Xe^{+35}$  (b). The drain-source bias during the irradiation are reported in the  $I_D V_{DS}$  graph as  $V_{DSirr}$ . Comparison of  $I_D V_{DS}$  and  $I_G V_{DS}$  (c), transfer characteristic (d) and body diode (e) for three DUTs exposed to  ${}^{131}Xe^{+35}$  at  $V_{DSirr} = 300 V$  and  $V_{DSirr} = 350 V$  as pristine die or after prior degradation from previous irradiation at lower  $V_{DSirr}$ .

incident ion. For <sup>131</sup>Xe<sup>+35</sup> the individual steps are less distinguishable due to high ion flux with respect to the speed of the current monitoring, hence only linear increase in leakage with increasing ion fluence is observed.

Conversely, during the runs at  $V_{DSirr} \ge 350 V$ , with all the devices and all the ions, the drain leakage was observed to increase at higher rate than the gate leakage. This behavior is illustrated in Fig. 3 (c, d) by showing the <sup>56</sup>Fe<sup>+15</sup> and <sup>131</sup>Xe<sup>+35</sup> results respectively, but the same trend was measured also with <sup>82</sup>Kr<sup>+22</sup> which has an intermediate LET. From the tests it is observed that the ion-induced leakage path is from drain to gate for  $V_{DSirr} \le 350 V$ , while at higher irradiation bias the leakage current is divided between drain-gate and drain-source paths, as discussed in more details below.

### B. Post-Irradiation measurements at RADEF and prior degradation effect

The drain and gate leakage were measured promptly after each run in absence of the beam, sweeping  $V_{DS}$  from 0 V to 1000 V with  $V_{GS} = 0 V$  and  $V_{GS}$  from 0 V to 5 V with  $V_{DS} =$ 1 V respectively. Permanent damage was observed in the post characteristics for devices tested with bias voltages above the degradation threshold. For all the DUTs the gate was permanently damaged and the blocking capability of the device degraded with increased  $V_{DSirr}$  during the test. In general, no latent defect damage was observed. If there was no damage during the exposure, it was not measured as well during the post-irradiation stressing the DUTs up to  $V_{GS} = 5 V$ .

In Fig. 4 the  $I_D$  and  $I_G$  as a function of  $V_{DS}$ , measured after each run, are shown for two 80 m $\Omega$  DUTs exposed to multiple irradiations with <sup>56</sup>Fe<sup>+15</sup> (a) and <sup>131</sup>Xe<sup>+35</sup> (b) beams. The history of the consecutive exposures is shown on the graph as V<sub>DSirr</sub>. In the case of <sup>56</sup>Fe<sup>+15</sup> the die was exposed also at  $V_{DSirr} =$ 340 V, 360 V, but the results are not shown here in order to have a more readable graph. The data for <sup>82</sup>Kr<sup>+22</sup> are also not presented here, but they are consistent with the results reported for <sup>56</sup>Fe<sup>+15</sup> and <sup>131</sup>Xe<sup>+</sup>.

4

These measurements confirm the trend that was already observed during the irradiation. Indeed, it is clearly visible that for the DUTs exposed to the beams at  $V_{DSirr} < 350 V$ , the observed drain and gate leakages are due to a direct path between drain and gate, as confirmed by the equal leakage currents values  $(|I_D| = |I_G|)$ . Conversely, for the DUTs irradiated at  $V_{DSirr} \ge 350 V$ , the drain and gate currents are equal at low  $V_{DS}$  values, but at higher  $V_{DS}$  the current starts to flow from drain to source through the channel  $(|I_D| > |I_G|)$ . The effect depends on the applied drain-source bias during the irradiation and on the ion LET values. Although the results are not discussed in this work, the same mechanism was observed also during the irradiation of the 25 m $\Omega$  and 160 m $\Omega$  die of the 2<sup>nd</sup> Generation Cree/Wolfspeed, which have different active area, but the same vertical cell structure.

Most of the tests were performed exposing the same DUT to consecutive irradiation runs. In order to analyse the effect of the degradation induced by the previous irradiations at lower voltage, the test was repeated with <sup>56</sup>Fe<sup>+15</sup> and <sup>131</sup>Xe<sup>+35</sup> beams using pristine die and exposing them for a single run at  $V_{DSirr} = 300 V$  and  $V_{DSirr} \ge 350 V$ . Three DUTs were selected for the analysis with <sup>131</sup>Xe<sup>+35</sup>: DUT 1 was exposed to <sup>131</sup>Xe<sup>+35</sup> at  $V_{DSirr} = 120 V, 170 V, 300 V, 350 V$  (same die as in Fig. 4 (b)),

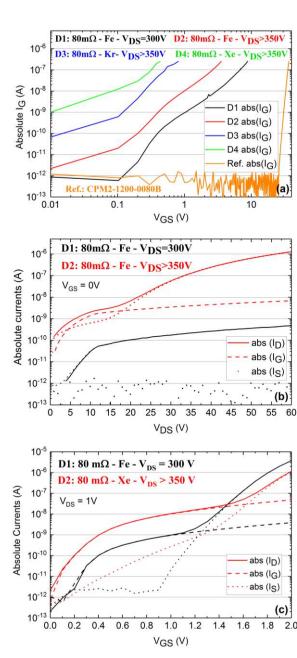

**Fig. 5.** (a)  $I_G V_{GS}$  measurements for irradiated devices in comparison with a reference measurements of a CPM2-1200-0080B die. (b)  $I_D V_{DS}$ ,  $I_G V_{DS}$ ,  $I_S V_{DS}$  current measurements ( $V_{GS} = 0 V$ ) (c)  $I_D V_{GS}$ ,  $I_G V_{GS}$ ,  $I_S V_{GS}$  current measurements ( $V_{DS} = 1 V$ ).

while DUT 2 and DUT 3 were exposed only for a single run at  $V_{DSirr} = 300$  V and  $V_{DSirr} \ge 350$  V respectively. Similarly it was done for <sup>56</sup>Fe<sup>+15</sup>, but the second pristine die was exposed to  $V_{DSirr} = 370$  V. All the irradiations were done with a fluence of 10<sup>6</sup> ion/cm<sup>2</sup>.

In Fig. 4 (c, d, e) the measurements are shown for the DUTs irradiated with  $^{131}Xe^{+35}$ . It is clearly visible in Fig. 4 (c) that the same characteristics are observed for the device already degraded as for the pristine die exposed to a single run. This result confirms that the current path within a degraded device is not affected by the prior damage history of the device, but it depends only on the drain-source bias during the irradiation (V<sub>DSirr</sub>). Moreover, in Fig. 4 (d) it can be seen that the transfer characteristics for the irradiated die are still comparable with

the reference values (i.e. DUT 1 is used as reference example and the difference is mostly caused by part-to-part variation). For DUT3 the transfer characteristics differs from that of the other devices probably because of some electrical stress induced effects during the post characterization. Finally, the body diode characteristic are presented in Fig. 4 (e). Here again the leakage path through the gate is evident at the lower V<sub>DS</sub> values where  $|I_D| = |I_G|$ , while at sufficiently high reverse voltage, the diode characteristics become dominant and the path is then through the body and it is comparable with the reference measurements for the pristine device (the differences again are caused by part-to-part variation). The measurements for <sup>56</sup>Fe<sup>+15</sup> confirm the same trend, concluding that no induced effect on the current path within a heavy ion degraded die was observed due to the prior irradiation history.

#### C. Post-Irradiation analysis.

After the irradiation tests, some of the die were electrically characterized at the APS Laboratory at ETH Zurich using a wafer probe station and measuring simultaneously the I<sub>G</sub>, I<sub>D</sub> and I<sub>S</sub>. The results in this section compare measurements of 3 DUTs tested at  $V_{DSirr} \ge 350 V$  with <sup>56</sup>Fe<sup>+15</sup>, <sup>82</sup>Kr<sup>+22</sup> and <sup>131</sup>Xe<sup>+35</sup> and a DUT tested at  $V_{DSirr} = 300 V$  with <sup>56</sup>Fe<sup>+15</sup>. For the latter DUT, the testing was stopped after the first exposure that induced degradation in the die, with only a single visible step in the drain and gate leakage.

In Fig. 5 (a) the gate leakage current measurements of the 4 DUTs in comparison with a reference measurement of a pristine CPM2-1200-0080B die are shown. It confirms that the gate oxide was heavily damaged during the irradiations and that the degradation is higher with increasing LET and drain-source bias voltage. Moreover, to not induce further damage in the device, the maximum measurable current was  $I_G = 10^{-7}$  A. This value was reached at lower  $V_{GS}$  with increasing damage.

The current analysis presented in Fig. 5 (b) was performed increasing  $V_{DS}$  until a drain current threshold level of 1mA was reached. In this case also the source current I<sub>S</sub> was measured, confirming the different current paths in devices tested at  $V_{DSirr} = 300 V$  and  $V_{DSirr} \ge 350 V$ , as discussed earlier.

Similar analysis is reported in Fig. 5 (c) as a function of  $V_{GS}$  with  $V_{DS} = 1 V$ . At low  $V_{GS}$ , the drain current flows from drain to gate, while at higher  $V_{GS}$  it flows from drain to source. This leads to the conclusion that the channel can still be controlled at  $V_{GS}$  below the  $V_{GS}$  breakdown voltage, although the gate leakage is very high. Hence, the assumption that the I<sub>D</sub> is flowing through the channel and not through the base part of the MOSFET is confirmed.

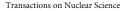

#### D. Degradation Rate

The degradation rates as a function of the drain-source bias(V<sub>DSirr</sub>) during the irradiation are presented in Fig. 6 (a) for the 25 m $\Omega$ , 80 m $\Omega$  and 160 m $\Omega$  DUTs irradiated with <sup>56</sup>Fe<sup>+15</sup>, <sup>82</sup>Kr<sup>+22</sup> and <sup>131</sup>Xe<sup>+35</sup> (the results refer to one DUT for each case). The permanent increase of the drain leakage during the ion exposure was normalized by the fluence and the active area of the die, as described previously.

In general, at  $V_{DSirr}$  values above the degradation threshold, the degradation rate increases with increasing  $V_{DSirr}$ . Focusing on the <sup>131</sup>Xe<sup>+35</sup> results, there is a sudden change in the bias dependent trend of the degradation rate as observed in Fig 6 (a)

Fig. 6. (a) Rate of heavy ion induced increase in drain leakage current as a function of the drain-source bias during the irradiation. The results refer to a single DUT for the 25 mΩ, 80 mΩ and 160 mΩ. For the pristine 80 mΩ a different DUT was used for each irradiation. The short history 80 mΩ reports the results for the same DUTs exposed first as pristine at  $V_{DSirr} = 300 V$ . (b) Magnified views of (a) considering heavy ion variation for the 80 m $\Omega$  die and comparison between the drain and the gate degradation rate.

at 300 V. This suggests that there can be two different mechanisms depending on the V<sub>DSirr</sub>, as seen during the experiment. Moreover, approaching the SEB threshold at approximately 500 V [7], the dependence of the degradation rate on the LET becomes less distinctive.

Furthermore, the degradation rates for a die exposed to multiple consecutive runs and pristine die exposed only to a single run (as explained earlier) are at the same magnitude. Additionally, the same die tested as pristine at  $V_{DSirr} = 300 V$ , were exposed for two more runs (at  $V_{DSirr} = 350 V$ , 400 V for  $^{131}$ Xe $^{+35}$  and  $V_{DSirr} = 370 V$  for  $^{56}$ Fe $^{+15}$ ). The results for these die with a shorter prior degradation history are again at the same magnitude as all the other results. This leads to the conclusion that the prior degradation does not affect the degradation rate. This observation could suggest that also the SEB threshold is not affected by the prior damage, however further studies are needed in order to verify the hypothesis.

A magnified view of the degradation rates for gate and drain leakage considering the LET variations for the 80 m $\Omega$  die is shown in Fig. 6 (b). A clear superimposition of the drain and the gate degradation is observed until  $V_{DSirr} = 300 V$ , independently from the prior degradation. At  $V_{DSirr} \ge 350 V$ , the gate degradation diverges from the drain response, showing a common behavior independent from the heavy ion LET.

#### IV. CURRENT TRANSPORT MODEL FOR HEAVY-ION DEGRADED SIC MOSFETS

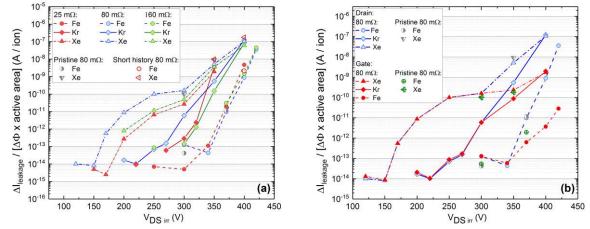

A heavy ion strike can induce damage at the gate interface and create a leakage path through the oxide in the neck side. From the experimental results and from the electrical postirradiation analysis, the heavy ion induced current path through the degraded device was schematized as follows.

At low V<sub>DS</sub> the current flows from drain to gate, exhibiting a linear dependence on the applied bias. Hence, the current voltage characteristics can be modeled by a simple resistor. This resistor can be considered to have two components  $R_{ox}$ and  $R_{epi}$  ( $R_{epi} \ll R_{ox}$ ) that represent the oxide resistance and the epilayer resistance, respectively. The effect of temperature variation during operation was not considered for the

estimation. Moreover, in a pristine device the oxide leakage current is negligible  $(R_{ox} \sim \infty)$ , hence the leakage flows through the body resistance R<sub>Body</sub>. As observed from the experimental results, this is not the case of a degraded device, concluding that:

$$\begin{cases} R_{ox} \gg R_{Body} \text{ (pristine device)} \\ \\ R_{Body} \gg R_{ox} \text{ (degraded device)} \end{cases}$$

(1)

At higher V<sub>DS</sub>, the leakage path was observed to be mostly from drain to source, with a lower contribution of leakage from drain to gate. It was hypothesized that the leakage through the gate oxide generates a voltage drop sufficient to partially open the channel, setting the MOSFET in a condition of "partial onstate", sufficient to allow the current flowing to the source.

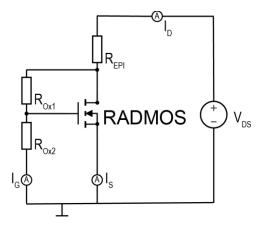

The electrical equivalent for the current transport is illustrated in Fig. 8 and is proposed to describe the heavy ion degraded device at  $V_{DS} < 100 V$ . The very small part of the channel that opens as a consequence of the radiation induced leakage in the gate is modelled with a MOSFET named RADMOS. The gate terminal of the RADMOS is controlled by the potential generated in the gate oxide of the DUT. The total

Fig. 7. Electrical equivalent for the heavy-ion induced current transport model in a degraded SiC power VD-MOSFET, valid at V<sub>DS</sub> < 100 V.

Fig. 8. Schematic layout proposed to describe the current transport in the heavy ion degraded device. The model was used to perform electrical simulations at  $V_{DS} < 100 V$ .

resistance of the gate was divided in  $R_{ox1} + R_{ox2}$  in order to simulate the potential gradient inside the oxide. At sufficiently high current flowing in the gate oxide, the  $V_{GS-RADMOS} > V_{th-RADMOS}$ , the channel is partially opened and the currents start to flow to the source.

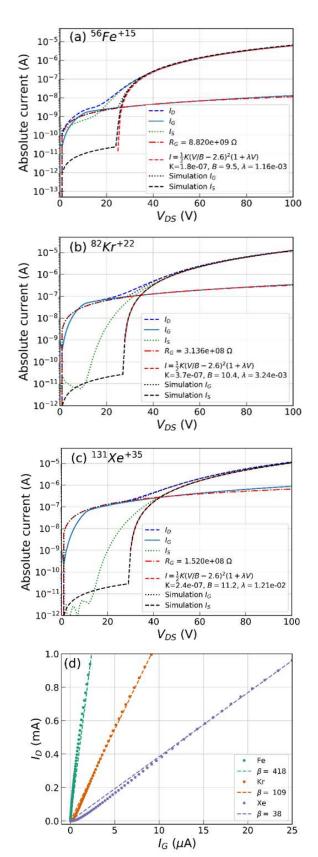

To confirm this hypothesis, fits for the I<sub>D</sub>, I<sub>S</sub>, I<sub>G</sub> measurements of the 80 m $\Omega$  device irradiated with <sup>56</sup>Fe<sup>+15</sup>, <sup>82</sup>Kr<sup>+22</sup> and <sup>131</sup>Xe<sup>+35</sup> were done. For  $V_{DS} < 100 V$ , it was confirmed that the I<sub>G</sub> follows a linear behavior (i.e. ohmic), while the I<sub>D</sub> and I<sub>S</sub> follow a quadratic behavior characteristic of a MOSFET in on state. From the fit was found the following equation for I<sub>S</sub>:

$$I_{S} = \frac{1}{2}K\left(\frac{V_{DS}}{B} - 2.6\right)^{2} (1 + \lambda V_{DS})$$

(2)

where  $B = (R_{ox1} + R_{ox2})/R_{ox2}$ , K is the transconductance and  $\lambda = \frac{\Delta L}{L}$  where L is the channel length. The fits were done for all the DUTs and the parameters are listed in Table II.

TADIEII

| PARAMETERS USED FOR THE SIMULATIONS |                                   |      |                         |                         |  |  |

|-------------------------------------|-----------------------------------|------|-------------------------|-------------------------|--|--|

| Ion                                 | $R_{oxide} \left[ \Omega \right]$ | В    | K [S]                   | λ                       |  |  |

| 56Fe+15                             | 8.82 x 10 <sup>9</sup>            | 9.5  | 1.80 x 10 <sup>-7</sup> | 1,16 x 10 <sup>-3</sup> |  |  |

| $^{82}{ m Kr}^{+22}$                | 3.13 x 10 <sup>8</sup>            | 10.4 | 3.70x 10 <sup>-7</sup>  | 3.24 x 10 <sup>-3</sup> |  |  |

| $^{131}Xe^{+35}$                    | 1.52 x 10 <sup>8</sup>            | 11.2 | 2.40 x 10 <sup>-7</sup> | 1.21 x 10 <sup>-2</sup> |  |  |

An electrical model to describe the degraded device is proposed in Fig. 8 and it was used to perform simulations with the parameters extracted from the fit. For all the cases,  $V_{th-RADMOS} = 2.6 V$  was used as first approximation, which is the typical V<sub>th</sub> for the pristine device. The comparison between the measurements, the fit and the simulation results are reported in Fig. 9 for the DUTs exposed to  ${}^{56}\text{Fe}^{+15}$  (a),  ${}^{82}\text{Kr}^{+22}$  (b) and  ${}^{131}\text{Xe}^{+35}$  (c) beams. For  $V_{DS} < 100 V$ , there is a very good agreement between the measurements, the fit and the electrical model proposed in Fig. 8. The results confirm the linear ohmic behavior for I<sub>G</sub> and the MOSFET behavior for I<sub>D</sub> and I<sub>S</sub> above the threshold voltage.

For  $V_{DS} > 100 V$ , another current transport mechanism, not fully explained by the model above, becomes dominant. The I<sub>D</sub> and I<sub>G</sub> start to follow an exponential behavior. A linear

7

Fig. 9. Comparison of measurements, fit and simulations of  $I_D$ ,  $I_G$ ,  $I_S$  as function of the  $V_{DS}$ . The model for the simulation is valid until  $V_{DS}$  = 100 V The results are shown for  ${}^{56}Fe^{+15}$  (a),  ${}^{82}Kr^{+22}$  (b) and  ${}^{131}Xe^{+35}$  (c). For  $V_{DS} > 100$  V, the behaviour becomes exponential and there is a linear proportionality between  $I_D$  and  $I_G$  (d). The current amplification  $\beta$  depends on the heavy ion induced degradation.

dependency is observed between  $I_D$  and  $I_G$  currents, as visible in Fig 9 (d). The current amplifications, defined as  $\beta$ , are reported on the graph and they are dependent on the heavy ion induced degradation. However, the current amplifications measured do not involve the parasitic n-p-n BJT typically associated with the SEB in power MOSFETs [7].

Although a detailed discussion of the SEB mechanisms is beyond the scope of the present article and the focus of the work is on the non-destructive degradation region, this secondary transistor observed in the sub-region of the SEB is different from the parasitic BJT described in the literature. However, the current amplification observed at  $V_{DS} > 100 V$ , could bring some suggestions on the description of the SEB phenomenon.

Finally, it has to be noticed that the observed charge transport mechanisms in ion-degraded SiC MOSFETs are different from those in SiC Schottky power diodes [21]. Indeed, in the case of ion-degraded SiC Schottky diodes, the charge transport is governed by the space charge limited current.

#### V. CONCLUSIONS

The ion-induced damage in the SiC power MOSFETs depends on the LET and the drain-source bias during the exposure. For all the DUTs, permanent increase in drain and gate leakage currents and degradation of the blocking capability were observed. Although no V<sub>th</sub> shift was observed in the DUTs, the gate oxide was strongly affected in all the cases, and it was already damaged after the irradiation at  $V_{DSirr} = 300V$ , 200 V and 120 V respectively with <sup>56</sup>Fe<sup>+15</sup>, <sup>82</sup>Kr<sup>+22</sup> and <sup>131</sup>Xe<sup>+35</sup>.

The results show that the ion-induced leakage path during the irradiation is from drain to gate when the irradiation bias is below 350 V. Above this bias voltage, the leakage current is divided between drain-gate and drain-source paths. Moreover, within the region studied  $(300 \le V_{DSirr} \le 350 V)$ , the leakage current path and the gate and drain degradation rate were observed to be independent on the prior degradation.

An electrical model is proposed to explain the current transport in the degraded SiC power MOSFETs. A current control phenomenon is described, leading first to the activation of the secondary MOSFET induced by radiation in the channel area (RADMOS) then, at  $V_{DS} > 100V$ , to an exponential behavior, with a linear dependence between I<sub>D</sub> and I<sub>G</sub> currents.

The mechanisms described here do not involve the parasitic n-p-n BJT, the intrinsic part of the device typically associated with catastrophic SEB in power MOSFETs [7]. However, the radiation induced secondary transistor as in the model proposed in this work, could bring some hints on the description of the SEB physical mechanisms.

Moreover, the charge transport model proposed for SiC power MOSFETs is also different from the one previously observed in SiC Schottky power diodes, where the charge transport is governed by the space charge limited current.

#### **ACKNOWLEDGEMENTS**

A. Tsibizov from the APS Laboratory at ETH Zurich is gratefully acknowledged for the numerous useful discussions. Moreover the authors thank the RADEF group at the Accelerator Laboratory of the University of Jyväskylä for permitting this experiment, in particular Mikko Rossi and Jukka Jaatinen for their help during the test.

#### REFERENCES

- H. J. van Daal, C. A. A. J. Greebe, W. F. Knippenberg and H. J. Vink, "Investigation on Silicon Carbide," *J. Appl. Phys.*, vol. 32, no. 10, pp. 2225-2233, Oct. 1961.

- [2] J. A. Cooper, M. R. Melloch, R. Singh, A. Agarwal and J. W. Palmour, "Status and prospects for SiC power MOSFETs," *IEEE Trans. Electron Devices*, vol. 49, no. 4, pp 658-664, Apr. 2002.

- [3] D. Woog, M. J. Barnes, L. Ducimetière, J. Holma and T. Kramer, "Design of an Inductive Adder for the FCC injection kicker pulse generator," *Journal of Physics*, Conf. Ser. 874 012096, Jul. 2017.

- [4] S. Kuboyama, C. Kamezawa, N. Ikeda, T. Hirao and H. Ohyama, "Anomalous Charge Collection in Silicon Carbide Schottky Barrier Diodes and Resulting Permanent Damage and Single-Event-Burnout," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3343-3348, Dec. 2006.

- [5] A. Javanainen *et al.*, "Heavy Ion Induced Degradation in SiC Schottky Diodes: Bias and Energy Deposition Dependence," *IEEE Trans. Nucl. Sci.*, vol 64, no. 1, pp. 415-420, Jan. 2017.

- [6] E. Mizuta, S. Kuboyama, H. Abe, Y. Iwata and T. Tamura, "Investigation of single-event damages on silicon carbide (SiC) power MOSFETs," *IEEE Trans Nucl. Sci.*, vol. 61, no. 4, pp. 1924-1928, Aug. 2014.

- [7] A.F. Witulski *et al.*, "Single-Event-Burnout Mechanisms in SiC Power MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 8, pp. 1951-1955, Jun. 2018.

- [8] J-M. Lauenstein *et al.*, "Silicon Carbide Power Device Performance Under Heavy-Ion Irradiation," presented at *IEEE Nuclear and Space Radiation Effects Conf.*, Boston, MA, USA, 2015 and NASA Report GSFC-E-DAA-TN25023, Jul. 2015.

- [9] T. Shoji, S. Nishida, K. Hamada and H. Tadano, "Experimental and simulation studies of neutron-induced single-event-burnout in SiC power diodes," *Jap. J. Appl. Phys.*, vol. 53, no. 4S, pp. 04EP03, Feb. 2014.

- [10] T. Shoji, S. Nishida, K. Hamada and H. Tadano, "Analysis of neutroninduced single-event burnout in SiC power MOSFETs," *Microelectron Reliab*, vol. 55, no. 9, pp. 1517-1521, Jun. 2015.

- [11] H. Asai *et al.*, "Tolerance Against Terrestrial Neutron-Induced Single-Event-Burnout in SiC MOSFETs," *IEEE Trans Nucl. Sci.*, vol. 61, no. 6 pp. 3109-3114, Dec. 2014.

- [12] T. Shoji et al., "Reliability design for neutron induced single-event burnout of IGBT," *IEEJ Trans. Industry App.*, vol. 131, no. 8, pp 992-999, Aug. 2011.

- [13] T. A. Fischer, "Heavy-ion-induced gate rupture in Power MOSFETs," *IEEE Trans. Nucl. Sci.*, vol 34, no. 6, pp 1786-1791, Dec. 1987.

- [14] J. R. Brews, M. Allenspach, R. Schrimpf, K. F. Galloway, J. L. Titus and C. Frank Wheatley, "A conceptual model of a single-event gate-rupture in power MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 40, no. 6, pp. 1959-1966, Dec. 1993.

- [15] M. N. Darwish, M. A. Shibib, M. R. Pinto and J. L. Titus, "Single event gate rupture of power DMOS transistors," in *Proc. IEDM '93*, Washington, DC, USA, 1993, pp. 671-674.

- [16] J. L. Titus, C. F. Wheatley, K. M. Van Tyne, J. F. Krieg, D. I. Burton and A. B. Campbell, "Effect of ion energy upon dielectric breakdown of the capacitor response in vertical power MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 45, no. 6, pp. 2492-2499, Dec. 1998.

- [17] J-M. Lauenstein *et al.*, "Effects of Ion Atomic Number on Single-Event Gate Rupture (SEGR) Susceptibility of Power MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2628-2636, Dec. 2011.

- [18] L. Scheick, L. Selva, Y. Chen and L. D. Edmonds, "Current Leakage Evolution in Partially Gate Ruptured Power MOSFETs," *IEEE Trans Nucl. Sci.*, vol 55, no. 4, pp. 2366-2375, Sep. 2008.

- [19] A. Javanainen et al., "Linear Energy Transfer of Heavy Ions in Silicon," IEEE Trans. Nucl. Sci., vol.54, no. 4, pp. 1158-1162, Aug. 2007.

- [20] Veronique Ferlet-Cavrois *et al.*, "Influence of Beam Conditions and Energy for SEE Testing," *IEEE Trans. Nucl. Sci.*, vol 59, no. 4, pp. 1149-1160, Aug. 2012.

- [21] A. Javanainen *et al.*, "Charge Transport Mechanism in Heavy-Ion Driven Leakage Current in Silicon Carbide Schottky Power Diodes," *IEEE Trans. Nucl. Sci.*, vol 16, no. 2, pp 208-2012, Jun. 2016.