Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.DOI

# DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

# GERALDO F. OLIVEIRA<sup>1</sup>, JUAN GÓMEZ-LUNA<sup>1</sup>, LOIS OROSA<sup>1</sup>, SAUGATA GHOSE<sup>2</sup>, NANDITA VIJAYKUMAR<sup>3</sup>, IVAN FERNANDEZ<sup>1,4</sup>, MOHAMMAD SADROSADATI<sup>1</sup>, and ONUR MUTLU<sup>1</sup>

<sup>1</sup>ETH Zürich, Switzerland

<sup>2</sup>University of Illinois Urbana-Champaign, USA

<sup>3</sup>University of Toronto, Canada

<sup>4</sup>University of Malaga, Spain

Corresponding author: Geraldo F. Oliveira (e-mail: geraldod@inf.ethz.ch).

**ABSTRACT** Data movement between the CPU and main memory is a first-order obstacle against improving performance, scalability, and energy efficiency in modern systems. Computer systems employ a range of techniques to reduce overheads tied to data movement, spanning from traditional mechanisms (e.g., deep multi-level cache hierarchies, aggressive hardware prefetchers) to emerging techniques such as Near-Data Processing (NDP), where some computation is moved close to memory. Prior NDP works investigate the root causes of data movement bottlenecks using different profiling methodologies and tools. However, there is still a lack of understanding about the key metrics that can identify different data movement bottlenecks and their relation to traditional and emerging data movement mitigation mechanisms. Our goal is to methodically identify potential sources of data movement mitigation techniques (e.g., caching and prefetching) to more memory-centric techniques (e.g., NDP), thereby developing a rigorous understanding of the best techniques to mitigate each source of data movement.

With this goal in mind, we perform the first large-scale characterization of a wide variety of applications, across a wide range of application domains, to identify fundamental program properties that lead to data movement to/from main memory. We develop the first systematic methodology to classify applications based on the sources contributing to data movement bottlenecks. From our large-scale characterization of 77K functions across 345 applications, we select 144 functions to form the first open-source benchmark suite (DAMOV) for main memory data movement studies. We select a diverse range of functions that (1) represent different types of data movement bottlenecks, and (2) come from a wide range of application domains. Using NDP as a case study, we identify new insights about the different data movement bottlenecks and use these insights to determine the most suitable data movement mitigation mechanism for a particular application. We open-source DAMOV and the complete source code for our new characterization methodology at https: //github.com/CMU-SAFARI/DAMOV.

**INDEX TERMS** benchmarking, data movement, energy, memory systems, near-data processing, performance, processing-in-memory, workload characterization, 3D-stacked memory

#### I. INTRODUCTION

**T** ODAY'S computing systems require moving data from main memory (consisting of DRAM) to the CPU cores so that computation can take place on the data. Unfortunately, this *data movement* is a major bottleneck for system performance and energy consumption [1, 2]. DRAM technology scaling is failing to keep up with the increasing memory demand from applications [2]–[29], resulting in significant latency and energy costs due to data movement [1]–[3, 5, 6, 30]–[49]. High-performance systems have evolved to include mechanisms that aim to alleviate data movement's impact on system performance and energy consumption, such as deep

cache hierarchies and aggressive prefetchers. However, such mechanisms not only come with significant hardware cost and complexity, but they also often fail to hide the latency and energy costs of accessing DRAM in many modern and emerging applications [1, 5, 50]-[52]. These applications' memory behavior can differ significantly from more traditional applications since modern applications often have lower memory locality, more irregular access patterns, and larger working sets [36, 45, 46, 53]–[61]. One promising technique that aims to alleviate the data movement bottleneck in modern and emerging applications is Near-Data Processing (NDP) [1, 33, 34, 46]–[48, 54, 55, 59]–[118],<sup>1</sup> where the cost of data movement to/from main memory is reduced by placing computation capability close to memory. In NDP, the computational logic close to memory has access to data that resides in main memory with significantly higher memory bandwidth, lower latency, and lower energy consumption than the CPU has in existing systems. There is very high bandwidth available to the cores in the logic layer of 3Dstacked memories, as demonstrated by many past works (e.g., [1, 46, 59, 60, 62]-[64, 67]-[69, 74, 76, 99, 119]). To illustrate this, we use the STREAM Copy [120] workload to measure the peak memory bandwidth the host CPU and an NDP architecture with processing elements in the logic layer of a single 3D-stacked memory (e.g., Hybrid Memory Cube [73]) can leverage.<sup>2</sup> We observe that the peak memory bandwidth that the NDP logic can leverage (431 GB/s) is  $3.7 \times$  the peak memory bandwidth that the host CPU can exploit (115 GB/s). This happens since the external memory bandwidth is bounded by the limited number of I/O pins available in the DRAM device [121].

Many recent works explore how NDP can benefit various application domains, such as graph processing [46, 47, 54, 63, 74, 93, 122]–[126], machine learning [1, 61, 69, 70, 84, 85, 103], bioinformatics [59, 60, 68], databases [55, 61, 63, 66, 67, 74, 86, 102], security [71, 105, 106], data manipulation [49, 86, 88, 89, 127]–[130], and mobile workloads [1, 61]. These works demonstrate that simple metrics such as last-level CPU cache Misses per Kilo-Instruction (MPKI) and Arithmetic Intensity (AI) are useful metrics that serve as a proxy for the amount of data movement an application experiences. These metrics can be used as a potential guide for choosing when to apply data movement mitigation mechanisms such as NDP. However, such metrics (and the corresponding insights) are often extracted from a small set of applications, with similar or not-rigorously-analyzed data movement characteristics. Therefore, it is difficult to generalize the metrics and insights these works provide to a broader set of applications, making it unclear what different metrics can reveal about a new (i.e., previously uncharacterized) application's data movement behavior (and how to mitigate its associated data movement costs).

<sup>1</sup>We use the term NDP to refer to *any* type of Processing-in-Memory [37].

<sup>2</sup>See Section II for our experimental evaluation methodology.

We illustrate this issue by highlighting the limitations of two different methodologies commonly used to identify memory bottlenecks and often used as a guide to justify the use of NDP architectures for an application: (a) analyzing a roofline model [131] of the application, and (b) using lastlevel CPU cache MPKI as an indicator of NDP suitability of the application. The roofline model correlates the computation requirements of an application with its memory requirements under a given system. The model contains two roofs: (1) a diagonal line ( $y = Peak Memory Bandwidth \times$ Arithmetic Intensity) called the memory roof, and (2) a horizontal line (y = Peak System Throughput) called the compute roof [131]. If an application lies under the memory roof, the application is classified as memory-bound; if an application lies under the compute roof, it is classified as compute-bound. Many prior works [99, 103, 132]-[144] employ this roofline model to identify memory-bound applications that can benefit from NDP architectures. Likewise, many prior works [1, 36, 51, 54, 55, 145]-[150] observe that applications with high last-level cache MPKI<sup>3</sup> are good candidates for NDP.

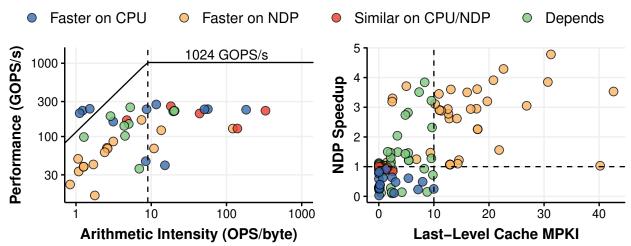

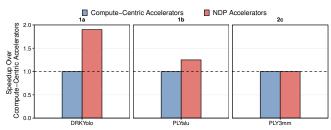

Figure 1 shows the roofline model (left) and a plot of MPKI vs. speedup (right) of a system with general-purpose NDP support over a baseline system without NDP for a diverse set of 44 applications (see Table 8). In the MPKI vs. speedup plot, the MPKI corresponds to a baseline host CPU system. The speedup represents the performance improvement of a general-purpose NDP system over the baseline (see Section II-D for our methodology). We make the following observations. First, analyzing the roofline model (Figure 1, left), we observe that most of the memory-bound applications (yellow dots) benefit from NDP, as foreseen by prior works. We later observe (in Section III-C1) that such applications are DRAM bandwidth-bound and are a natural fit for NDP. However, the roofline model does not accurately account for the NDP suitability of memory-bound applications that (i) benefit from NDP only under particular microarchitectural configurations, e.g., either at low or high core counts (green dots, which are applications that are either bottlenecked by DRAM latency or suffer from L3 cache contention; see Sections III-C3 and III-C4); or (ii) experience performance degradation when executed using NDP (blue dots, which are applications that suffer from the lack of a deep cache hierarchy in NDP architectures; see Section III-C6). Second, analyzing the MPKI vs. speedup plot (Figure 1, right), we observe that while all applications with high MPKI benefit from NDP (yellow dots with MPKI higher than 10), some applications with low MPKI can also benefit from NDP in all of the NDP microarchitecture configurations we evaluate (yellow dots with MPKI lower than 10) or under specific NDP microarchitecture configurations (green dots with MPKI lower than 10). Thus, even though both the roofline model and MPKI can identify some specific sources of memory bottlenecks and can sometimes be used as a proxy

<sup>&</sup>lt;sup>3</sup>Typically, an MPKI value greater than 10 is considered *high* by prior works [151]–[157].

Geraldo F. Oliveira et al.: DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

Figure 1: Roofline (left) and last-level cache MPKI vs. NDP speedup (right) for 44 memory-bound applications. Applications are classified into four categories: (1) those that experience performance degradation due to NDP (blue; Faster on CPU), (2) those that experience performance improvement due to NDP (yellow; Faster on NDP), (3) those where the host CPU and NDP performance are similar (red; Similar on CPU/NDP), (4) those that experience either performance degradation or performance improvement due to NDP depending on the microarchitectural configuration (green; Depends).

for NDP suitability, they alone cannot definitively determine NDP suitability because they cannot comprehensively identify different possible sources of memory bottlenecks in a system.

Our goal in this work is (1) to understand the major sources of inefficiency that lead to data movement bottlenecks by observing and identifying relevant metrics and (2) to develop a benchmark suite for data movement that captures each of these sources. To this end, we develop a new three-step methodology to correlate application characteristics with the primary sources of data movement bottlenecks and to determine the potential benefits of three example data movement mitigation mechanisms: (1) a deep cache hierarchy, (2) a hardware prefetcher, and (3) a general-purpose NDP architecture.<sup>4</sup> We use two main profiling strategies to gather key metrics from applications: (i) an architecture-independent profiling tool and (ii) an architecture-dependent profiling tool. The architecture-independent profiling tool provides metrics that characterize the application memory behavior independently of the underlying hardware. In contrast, the architecture-dependent profiling tool evaluates the impact of the system configuration (e.g., cache hierarchy) on the memory behavior. Our methodology has three steps. In Step 1, we use a hardware profiling tool to identify memory-bound functions across many applications. This step allows for a quick first-level identification of many applications that suffer from memory bottlenecks and functions that cause these bottlenecks. In Step 2, we use the architecture-independent profiling tool to collect metrics that provide insights about the

memory access behavior of the memory-bottlenecked functions. In *Step 3*, we collect architecture-dependent metrics and analyze the performance and energy of each function in an application when each of our three candidate data movement mitigation mechanisms is applied to the system. By combining the data obtained from all three steps, we can systematically classify the leading causes of data movement bottlenecks in an application or function into different bottleneck classes.

Using this new methodology, we characterize a large, heterogeneous set of applications (345 applications from 37 different workload suites) across a wide range of domains. Within these applications, we analyze 77K functions and find a subset of 144 functions from 74 different applications that are memory-bound (and that consume a significant fraction of the overall execution time). We fully characterize this set of 144 representative functions to serve as a core set of application kernel benchmarks, which we release as the open-source DAMOV (DAta MOVement) Benchmark Suite [158]. Our analyses reveal six new insights about the sources of memory bottlenecks and their relation to NDP:

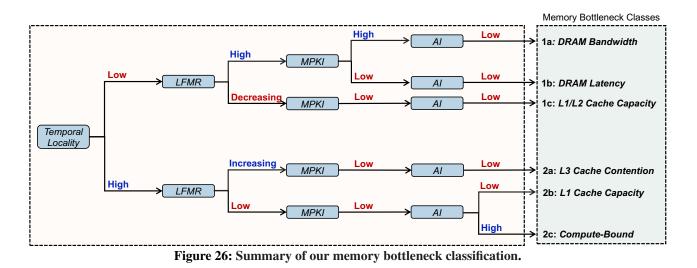

- 1) Applications with high last-level cache MPKI and low temporal locality are *DRAM bandwidth-bound*. These applications benefit from the large memory bandwidth available to the NDP system (Section III-C1).

- 2) Applications with low last-level cache MPKI and low temporal locality are *DRAM latency-bound*. These applications do *not* benefit from L2/L3 caches. The NDP system improves performance and energy efficiency by sending L1 misses directly to DRAM (Section III-C2).

- A second group of applications with low LLC MPKI and low temporal locality are *bottlenecked by L1/L2 cache capacity*. These applications benefit from the NDP system

<sup>&</sup>lt;sup>4</sup>We focus on these three data movement mitigation mechanisms for two different reasons: (1) deep cache hierarchies and hardware prefetchers are standard mechanisms in almost all modern systems, and (2) NDP represents a promising paradigm shift for many modern data-intensive applications.

at low core counts. However, at high core counts (and thus larger L1/L2 cache space), the caches capture most of the data locality in these applications, decreasing the benefits the NDP system provides (Section III-C3). We make this observation using a *new* metric that we develop, called *last-to-first miss-ratio (LFMR)*, which we define as the ratio between the number of LLC misses and the total number of L1 cache misses. We find that this metric accurately identifies how efficient the cache hierarchy is in reducing data movement.

- 4) Applications with high temporal locality and low LLC MPKI are *bottlenecked by L3 cache contention* at high core counts. In such cases, the NDP system provides a cost-effective way to alleviate cache contention over increasing the L3 cache capacity (Section III-C4).

- 5) Applications with high temporal locality, low LLC MPKI, and low AI are bottlenecked by the *L1 cache capacity*. The three candidate data movement mitigation mechanisms achieve similar performance and energy consumption for these applications (Section III-C5).

- 6) Applications with high temporal locality, low LLC MPKI, and high AI are *compute-bound*. These applications benefit from a deep cache hierarchy and hardware prefetchers, but the NDP system degrades their performance (Section III-C6).

We publicly release our 144 representative data movement bottlenecked functions from 74 applications as the first opensource benchmark suite for data movement, called DAMOV Benchmark Suite, along with the complete source code for our new characterization methodology [158].

This work makes the following key contributions:

- We propose the first methodology to characterize dataintensive workloads based on the source of their data movement bottlenecks. This methodology is driven by insights obtained from a large-scale experimental characterization of 345 applications from 37 different benchmark suites and an evaluation of the performance of memorybound functions from these applications with three datamovement mitigation mechanisms.

- We release DAMOV, the first open-source benchmark suite for main memory data movement-related studies, based on our systematic characterization methodology. This suite consists of 144 functions representing different sources of data movement bottlenecks and can be used as a baseline benchmark set for future data-movement mitigation research.

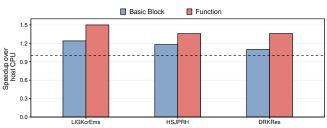

- We show how our DAMOV benchmark suite can aid the study of open research problems for NDP architectures, via four case studies. In particular, we evaluate (i) the impact of load balance and inter-vault communication in NDP systems, (ii) the impact of NDP accelerators on our memory bottleneck analysis, (iii) the impact of different core models on NDP architectures, and (iv) the potential benefits of identifying simple NDP instructions. We conclude that our benchmark suite and methodology

can be employed to address many different open research and development questions on data movement mitigation mechanisms, particularly topics related to NDP systems and architectures.

#### **II. METHODOLOGY OVERVIEW**

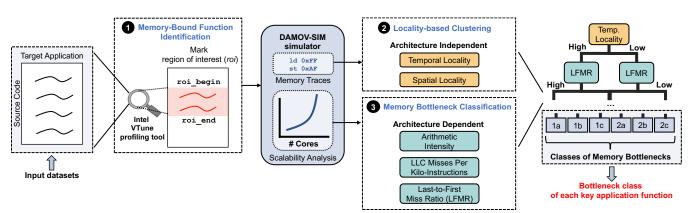

We develop a new workload characterization methodology to analyze data movement bottlenecks and the suitability of different data movement mitigation mechanisms for these bottlenecks, with a focus on Near-Data Processing (NDP). Our methodology consists of three main steps, as Figure 2 depicts: (1) memory-bound function identification using application profiling; (2) locality-based clustering to analyze spatial and temporal locality in an architecture-independent manner; and (3) memory bottleneck classification using a scalability analysis to nail down the sources of memory boundedness, including architecture-dependent characterization. Our methodology takes as input an application's source code and its input datasets, and produces as output a classification of the primary source of memory bottleneck of important functions in an application (i.e., bottleneck class of each key application function). We illustrate the applicability of this methodology with a detailed characterization of 144 functions that we select from among 77K analyzed functions of 345 characterized applications. In this section, we give an overview of our workload characterization methodology. We use this methodology to drive the analyses we perform in Section III.

#### A. EXPERIMENTAL EVALUATION FRAMEWORK

As our scalability analysis depends on the hardware architecture, we need a hardware platform that can allow us to replicate and control all of our configuration parameters. Unfortunately, such an analysis cannot be performed practically using real hardware, as (1) there are very few available NDP hardware platforms, and the ones that currently exist do not allow us to comprehensively analyze our generalpurpose NDP configuration in a controllable way (as existing platforms are specialized and non-configurable); and (2) the configurations of real CPUs can vary significantly across the range of core counts that we want to analyze, eliminating the possibility of a carefully controlled study. As a result, we must rely on accurate simulation platforms to perform an accurate comparison across different configurations. To this end, we build a framework that integrates the ZSim CPU simulator [159] with the Ramulator memory simulator [160] to produce a fast, scalable, and cycle-accurate open-source simulator called DAMOV-SIM [158]. We use ZSim to simulate the core microarchitecture, cache hierarchy, coherence protocol, and prefetchers. We use Ramulator to simulate the DRAM architecture, memory controllers, and memory accesses. To compute spatial and temporal locality, we modify ZSim to generate a single-thread memory trace for each application, which we use as input for the locality analysis algorithm described in Section II-C (which statically

### IEEE Access

Figure 2: Overview of our three-step workload characterization methodology.

computes the temporal and spatial locality at word-level granularity).

#### B. STEP 1: MEMORY-BOUND FUNCTION IDENTIFICATION

The first step (labeled ① in Figure 2) aims to identify the functions of an application that are *memory-bound* (i.e., functions that suffer from data movement bottlenecks). These bottlenecks might be caused at any level of the memory hierarchy. There are various potential sources of memory boundedness, such as cache misses, cache coherence traffic, and long queuing latencies. Therefore, we need to take all such potential causes into account. This step is optional if the application's memory-bound functions (i.e., regions of interest, *roi*, in Figure 2) are already known *a priori*.

Hardware profiling tools, both open-source and proprietary, are available to obtain hardware counters and metrics that characterize the application behavior on a computing system. In this work, we use the Intel VTune Profiler [161], which implements the well-known *top-down analysis* [162]. Top-down analysis uses the available CPU hardware counters to hierarchically identify different sources of CPU system bottlenecks for an application. Among the various metrics measured by top-down analysis, there is a relevant one called *Memory Bound* [163] that measures the percentage of CPU pipeline slots that are *not* utilized due to any issue related to data access. We employ this metric to identify functions that suffer from data movement bottlenecks (which we define as functions where *Memory Bound* is greater than 30%).

#### C. STEP 2: LOCALITY-BASED CLUSTERING

Two key properties of an application's memory access pattern are its inherent spatial locality (i.e., the likelihood of accessing nearby memory locations in the near future) and temporal locality (i.e., the likelihood of accessing a memory location again in the near future). These properties are closely related to how well the application can exploit the memory hierarchy in computing systems and how accurate hardware prefetchers can be. Therefore, to understand the sources of memory bottlenecks for an application, we should analyze how much spatial and temporal locality its memory accesses inherently exhibit. However, we should isolate these properties from particular configurations of the memory subsystem. Otherwise, it would be unclear if memory bottlenecks are due to the nature of the memory accesses or due to the characteristics and limitations of the memory subsystem (e.g., limited cache size, too simple or inaccurate prefetching policies). As a result, in this step (labeled **2** in Figure 2), we use *architecture-independent* static analysis to obtain spatial and temporal locality metrics for the functions selected in the previous step (Section II-B). Past works [164]–[173] propose different ways of analyzing spatial and temporal locality in an architecture-independent manner. In this work, we use the definition of spatial and temporal metrics presented in [166, 167].

The spatial locality metric is calculated for a window of memory references<sup>5</sup> of length W using Equation 1. First, for every W memory references, we calculate the minimum distance between any two addresses (*stride*). Second, we create a histogram called the *stride profile*, where each bin *i* stores how many times each *stride* appears. Third, to calculate the spatial locality, we divide the *percentage* of times stride *i* is referenced (*stride profile*(*i*)) by the stride length *i* and sum the resulting value across all instances of *i*.

$$Spatial \ Locality = \sum_{i=1}^{\#bins} \frac{stride \ profile(i)}{i} \qquad (1)$$

A spatial locality value close to 0 is caused by large *stride* values (e.g., regular accesses with large strides) or random accesses, while a value equal to 1 is caused by a completely sequential access pattern.

The temporal locality metric is calculated by using a histogram of reused addresses. First, we count the number of times each memory address is repeated in a window of L memory references. Second, we create a histogram called *reuse profile*, where each bin *i* represents the number of times a memory address is reused, expressed as a power of 2. For each memory address, we increment the bin that represents

<sup>&</sup>lt;sup>5</sup>We compute both the spatial and temporal locality metrics at the word granularity. In this way, we keep our locality analysis architecture-independent, using *only* properties of the application under study.

the corresponding number of repetitions. For example, *reuse* profile(0) represents memory addresses that are reused only once. *reuse* profile(1) represents memory addresses that are reused twice. Thus, if a memory address is reused N times, we increment *reuse*  $profile(\lfloor log_2 N \rfloor)$  by one. Third, we obtain the temporal locality metric with Equation 2.

$$Temporal \ Locality = \sum_{i=0}^{\#bins} \frac{2^i \times reuse \ profile(i)}{total \ memory \ accesses}$$

(2)

A temporal locality value of 0 indicates no data reuse, while a value close to 1 indicates very high data reuse (i.e., a value equal to 1 means that the application accesses a single memory address continuously).

To calculate these metrics, we empirically select window lengths W and L to 32. We find that different values chosen for W and L do not significantly change the conclusions of our analysis. We observe that our conclusions remain the same when we set both values to 8, 16, 32, 64, and 128.

#### D. STEP 3: BOTTLENECK CLASSIFICATION

While Step 2 allows us to understand inherent application sources for memory boundedness, it is important to understand how hardware architectural features can also result in memory bottlenecks. As a result, in our third step (3) in Figure 2), we perform a scalability analysis of the functions selected in Step 1, where we evaluate performance and energy scaling for three different system configurations. The scalability analysis makes use of three architecturedependent metrics: (1) Arithmetic Intensity (AI), (2) Misses per Kilo-Instruction (MPKI), and (3) a new metric called Last-to-First Miss-Ratio (LFMR). We select these metrics for the following reasons. First, AI can measure the compute intensity of an application. Intuitively, we expect an application with high compute intensity to not suffer from severe data movement bottlenecks, as demonstrated by prior work [174]. Second, MPKI serves as a proxy for the memory intensity of an application. It can also indicate the memory pressure experienced by the main memory system [45, 47, 48, 58, 151, 153, 156, 175]-[177]. Third, LFMR, a new metric we introduce and is described in detail later in this subsection, indicates how efficient the cache hierarchy is in reducing data movement.

As part of our methodology development, we evaluate other metrics related to data movement, including raw cache misses, coherence traffic, and DRAM row misses/hits/conflicts. We observe that even though such metrics are useful for further characterizing an application (as we do in some of our later analyses in Section III-C), they do not necessarily characterize a specific type of data movement bottleneck. We show in Section IV-A that the three architecture-dependent and two architectureindependent metrics we select for our classification are enough to accurately characterize and cluster the different types of data movement bottlenecks in a wide variety of applications.

#### 1) Definition of Metrics.

We define Arithmetic Intensity (AI) as the number of arithmetic and logic operations performed per L1 cache line accessed.<sup>6</sup> This metric indicates how much computation there is per memory request. Intuitively, applications with high AI are likely to be computationally intensive, while applications with low AI tend to be memory intensive. We use MPKI at the last-level cache (LLC), i.e., the number of LLC misses per one thousand instructions. This metric is considered to be a good indicator of NDP suitability by several prior works [1, 36, 51, 54, 55, 145]-[149]. We define the LFMR of an application as the ratio between the number of LLC misses and the total number of L1 cache misses. We find that this metric accurately identifies how much an application benefits from the deep cache hierarchy of a contemporary CPU. An LFMR value close to 0 means that the number of LLC misses is very small compared to the number of L1 misses, i.e., the L1 misses are likely to hit in the L2 or L3 caches. However, an LFMR value close to 1 means that very few L1 misses hit in L2 or L3 caches, i.e., the application does not benefit much from the deep cache hierarchy, and most L1 misses need to be serviced by main memory.

#### 2) Scalability Analysis and System Configuration.

The goal of the scalability analysis we perform is to nail down the specific sources of data movement bottlenecks in the application. In this analysis, we (i) evaluate the performance and energy scaling of an application in three different system configurations; and (ii) collect the key metrics for our bottleneck classification (i.e., AI, MPKI, and LFMR). During scalability analysis, we simulate three system configurations of a general-purpose multicore processor:

- A host CPU with a deep cache hierarchy (i.e., private L1 (32 kB) and L2 (256 kB) caches, and a shared L3 (8 MB) cache with 16 banks). We call this configuration *Host CPU*.

- A host CPU with a deep cache hierarchy (same cache configurations as in *Host CPU*), augmented with a stream prefetcher [178]. We call this configuration *Host CPU with prefetcher*.

- An NDP CPU with a single level of cache (only a private read-only<sup>7</sup> L1 cache (32 kB), as assumed in many prior NDP works [1, 46, 51, 63, 66, 74, 99, 101, 119, 179]) and no hardware prefetcher. We call this configuration *NDP*.

The remaining components of the processor configuration are kept the same (e.g., number of cores, instruction window

<sup>&</sup>lt;sup>6</sup>We consider AI to be architecture-dependent since we consider the number of cache lines accessed by the application (and hence the hardware cache block size) to compute the metric. This is the same definition of AI used by the hardware profiling tool we employ in *Step 1* (i.e., the Intel VTune Profiler [161]).

<sup>&</sup>lt;sup>7</sup>We use read-only L1 caches to simplify the cache coherence model of the NDP system. Enabling efficient synchronization and cache coherence in NDP architectures is an open-research problem, as we discuss in Section III-F.

size, branch predictor) to isolate the impact of only the caches, prefetchers, and NDP. This way, we expect that the performance and energy differences between the three configurations to come exclusively from the different data movement requirements. For the three configurations, we sweep the number of CPU cores in our analysis from 1 to 256, as previous works [46, 66, 180] show that large core counts are necessary to saturate the bandwidth provided by modern high-bandwidth memories, and because modern CPUs and NDP proposals can have varying core counts. The core count sweep allows us to observe (1) how an application's performance changes when increasing the pressure on the memory subsystem, (2) how much Memory-Level Parallelism (MLP) [176, 181]–[184] the application has, and (3) how much the cores leverage the cache hierarchy and the available memory bandwidth. We proportionally increase the size of the CPU's private L1 and L2 caches when increasing the number of CPU cores in our analysis (e.g., when scaling the CPU core count from 1 to 4, we also scale the aggregated L1/L2 cache size by a factor of 4). We use out-of-order and in-order CPU cores in our analysis for all three configurations. In this way, we build confidence that our trends and findings are independent of a specific underlying general-purpose core microarchitecture. We simulate a memory architecture similar to the Hybrid Memory Cube (HMC) [73], where (1) the host CPU accesses memory through a high-speed offchip link, and (2) the NDP logic resides in the logic layer of the memory chip and has direct access to the DRAM banks (thus taking advantage of higher memory bandwidth and lower memory latency). Table 1 lists the parameters of our host CPU, host CPU with prefetcher, and NDP baseline configurations.

#### 3) Choosing an NDP Architecture.

We note that across the proposed NDP architectures in literature, there is a lack of consensus on whether the architectures should make use of general-purpose NDP cores or specialized NDP accelerators [36, 37]. In this work, we focus on general-purpose NDP cores for two major reasons. First, many prior works (e.g., [1, 46, 51, 63, 66, 76, 99, 101, 119, 147, 179, 190, 192]-[194]) suggest that general-purpose cores (especially simple in-order cores) can successfully accelerate memory-bound applications in NDP architectures. In fact, UPMEM [83], a start-up building some of the first commercial in-DRAM NDP systems, utilizes simple in-order cores in their NDP units inside DRAM chips [83, 140]. Therefore, we believe that general-purpose NDP cores are a promising candidate for future NDP architectures. Second, the goal of our work is not to perform a design space exploration of different NDP architectures, but rather to understand the key properties of applications that lead to memory bottlenecks that can be mitigated by a simple NDP engine. While we expect that each application could potentially benefit further from an NDP accelerator tailored to its computational and memory requirements, such customized architectures open many challenges for a methodical characterization, such

as the need for significant code refactoring, changes in data mapping, and code partitioning between NDP accelerators and host CPUs.<sup>8,9</sup>

#### **III. CHARACTERIZING MEMORY BOTTLENECKS**

In this section, we apply our three-step workload characterization methodology to characterize the sources of memory bottlenecks across a wide range of applications. First, we apply *Step 1* to identify memory-bound functions within an application (Section III-A). Second, we apply *Step 2* and cluster the identified functions using two architecture-independent metrics (spatial and temporal locality) (Section III-B). Third, we apply *Step 3* and combine the architecture-dependent and architecture-independent metrics to classify the different sources of memory bottlenecks we observe (Section III-C).

We also evaluate various other aspects of our three-step workload characterization methodology. We investigate the effect of increasing the last-level cache on our memory bottleneck classification in Section III-D. We provide a validation of our memory bottleneck classification in Section III-E. We discuss the limitations of our proposed methodology in Section III-F.

#### A. STEP 1: MEMORY-BOUND FUNCTION IDENTIFICATION

We first apply Step 1 of our methodology across 345 applications (listed in Appendix C) to identify functions whose performance is significantly affected by data movement. We use the previously-proposed top-down analysis methodology [162] that has been used by several recent workload characterization studies [5, 195, 196]. As discussed in Section II-B, we use the Intel VTune Profiler [161], which we run on an Intel Xeon E3-1240 processor [197] with four cores. We disable hyper-threading for more accurate profiling results, as recommended by the VTune documentation [198]. For the applications that we analyze, we select functions (1) that take at least 3% of the clock cycles, and (2) that have a Memory Bound percentage that is greater than 30%. We choose 30% as the threshold for this metric because, in preliminary simulation experiments, we do not observe significant performance improvement or energy savings with data movement mitigation mechanisms for functions whose Memory Bound percentage is less than 30%.

The applications we analyze come from a variety of sources, such as popular workload suites (Chai [199], CORAL [200], Parboil [201], PARSEC [202], Rodinia [203], SD-VBS [204], SPLASH-2 [205]), benchmarking (STREAM [120], HPCC [206], HPCG [207]), bioinformatics [208], databases [209, 210], graph processing frameworks (GraphMat [211], Ligra [212]), a map-reduce framework (Phoenix [213]), and neural networks (AlexNet

$<sup>^{8}</sup>$ We show in Section V-B that our DAMOV benchmark suite is useful to rigorously study NDP accelerators.

<sup>&</sup>lt;sup>9</sup>The development of a new methodology or extension of our methodology to perform analysis targeting function-specific, customized, or reconfigurable NDP accelerators is a good direction for future work.

| Table 1: Evaluated Host CPU and NDP system configurations.                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                           | Host CPU Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                                           | 1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Host CPU                                                                  | 1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide in-order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Processor                                                                 | Buffers: 128-entry ROB; 32-entry LSQ (each)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                                           | Branch predictor: Two-level GAs [185]. 2,048 entry BTB; 1 branch per fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Private                                                                   | 32 KB, 8-way, 4-cycle; 64 B line; LRU policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| L1 Cache                                                                  | Energy: 15/33 pJ per hit/miss [51, 186]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Private                                                                   | 256 KB, 8-way, 7-cycle; 64 B line; LRU policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| L2 Cache                                                                  | MSHR size: 20-request, 20-write, 10-eviction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                                           | Energy: 46/93 pJ per hit/miss [51, 186]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                           | 8 MB (16-banks), 0.5 MB per bank, 16-way, 27-cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Shared                                                                    | 64 B line; LRU policy; Bi-directional ring [187]; Inclusive; MESI protocol [188]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| L3 Cache                                                                  | MSHR size: 64-request, 64-write, 64-eviction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                                           | Energy: 945/1904 pJ per hit/miss [51, 186]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                           | Host CPU with Prefetcher Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Processor,                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Private L1 Cache, Private L2 Cache,<br>and Share L3 Cache                 | Same as in Host CPU Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                                                           | Same as in Host CPU Configuration Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| and Share L3 Cache                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| and Share L3 Cache                                                        | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| and Share L3 Cache                                                        | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries NDP Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher                                    | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher NDP CPU                            | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order         1, 4, 16, 64, and 256 cores @ 2.4 GHz, 32 nm; 4-wide in-order                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher NDP CPU                            | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order         1, 4, 16, 64, and 256 cores @ 2.4 GHz, 32 nm; 4-wide in-order         Buffers: 128-entry ROB; 32-entry LSQ (each)                                                                                                                                                                                                                                                                                                           |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher NDP CPU Processor                  | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order         1, 4, 16, 64, and 256 cores @ 2.4 GHz, 32 nm; 4-wide in-order         Buffers: 128-entry ROB; 32-entry LSQ (each)         Branch predictor: Two-level GAs [185]. 2,048 entry BTB; 1 branch per fetch                                                                                                                                                                                                                        |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher NDP CPU Processor Private          | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order         1, 4, 16, 64, and 256 cores @ 2.4 GHz, 32 nm; 4-wide in-order         Buffers: 128-entry ROB; 32-entry LSQ (each)         Branch predictor: Two-level GAs [185]. 2,048 entry BTB; 1 branch per fetch         32 KB, 8-way, 4-cycle; 64 B line; LRU policy; Read-only Data Cache                                                                                                                                             |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher NDP CPU Processor Private          | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order         1, 4, 16, 64, and 256 cores @ 2.4 GHz, 32 nm; 4-wide in-order         Buffers: 128-entry ROB; 32-entry LSQ (each)         Branch predictor: Two-level GAs [185]. 2,048 entry BTB; 1 branch per fetch         32 KB, 8-way, 4-cycle; 64 B line; LRU policy; Read-only Data Cache         Energy: 15/33 pJ per hit/miss [51, 186]                                                                                             |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher NDP CPU Processor Private L1 Cache | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order         1, 4, 16, 64, and 256 cores @ 2.4 GHz, 32 nm; 4-wide in-order         Buffers: 128-entry ROB; 32-entry LSQ (each)         Branch predictor: Two-level GAs [185]. 2,048 entry BTB; 1 branch per fetch         32 KB, 8-way, 4-cycle; 64 B line; LRU policy; Read-only Data Cache         Energy: 15/33 pJ per hit/miss [51, 186]         Common                                                                              |  |  |  |

| and Share L3 Cache L2 Cache Prefetcher NDP CPU Processor Private          | Stream prefetcher [178, 189]: 2-degree; 16 stream buffers; 64 entries         NDP Configuration         1, 4, 16, 64, and 256 cores @2.4 GHz, 32 nm; 4-wide out-of-order         1, 4, 16, 64, and 256 cores @ 2.4 GHz, 32 nm; 4-wide in-order         Buffers: 128-entry ROB; 32-entry LSQ (each)         Branch predictor: Two-level GAs [185]. 2,048 entry BTB; 1 branch per fetch         32 KB, 8-way, 4-cycle; 64 B line; LRU policy; Read-only Data Cache         Energy: 15/33 pJ per hit/miss [51, 186]         Common         HMC v2.0 Module [73] 32 vaults, 8 DRAM banks/vault, 256 B row buffer |  |  |  |

[214], Darknet [215]). We explore different input dataset sizes for the applications and choose real-world input datasets that impose high pressure on the memory subsystem (as we expect that such real-world inputs are best suited for stressing the memory hierarchy). We also use different inputs for applications whose performance is tightly related to the input dataset properties. For example, we use two different graphs with varying connectivity degrees (rMat [217] and USA [218]) to evaluate graph processing applications and two different read sequences to evaluate read alignment algorithms [60, 219, 220].

In total, our application analysis covers more than 77K functions. To date, this is the most extensive analysis of data movement bottlenecks in real-world applications. We find a set of 144 functions that take at least 3% of the total clock cycles and have a value of the Memory Bound metric greater or equal to 30%, which forms the basis of DAMOV, our new data movement benchmark suite. We provide a list of all 144 functions selected based on our analysis and their major characteristics in Appendix A.

After identifying memory-bound functions over a wide

range of applications, we apply Steps 2 and 3 of our methodology to classify the primary sources of memory bottlenecks for our selected functions. We evaluate a total of 144 functions out of the 77K functions we analyze in Step 1. These functions span across 74 different applications, belonging to 16 different widely-used benchmark suites or frameworks.

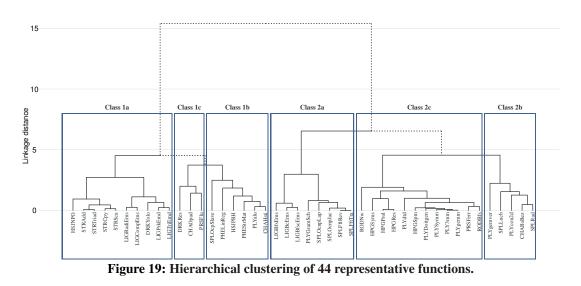

From the 144 functions that we analyze further, we select a subset of 44 representative functions to explore in-depth in Sections III-B and III-C and to drive our bottleneck classification analysis. We use the 44 representative functions to ease our explanations and make figures more easily readable. Table 8 in Appendix A lists the 44 representative functions that we select. The table includes one column that indicates the class of data movement bottleneck experienced by each function (we discuss the classes in Section III-C), and another column representing the percentage of clock cycles of the selected function in the whole application. We select representative functions that belong to a variety of domains: benchmarking, bioinformatics, data analytics, databases, data mining, data reorganization, graph processing, neural networks, physics, and signal processing. In Section III-E, we validate our classification using the remaining 100 functions and provide a summary of the results of our methodology when applied to all 144 functions.

<sup>&</sup>lt;sup>10</sup>The default HMC interleaving scheme (Row:Column:Bank:Vault [73]) interleaves consecutive cache lines across vaults, and then across banks [216].

Geraldo F. Oliveira et al.: DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

#### B. STEP 2: LOCALITY-BASED CLUSTERING

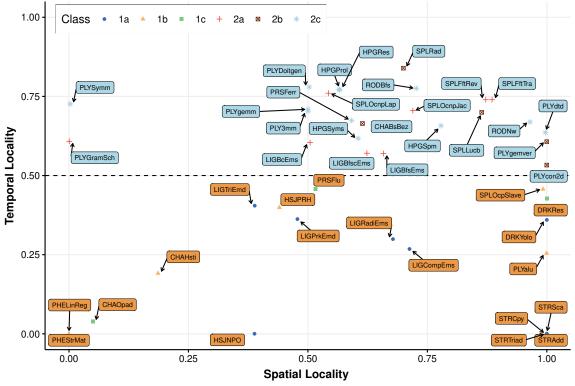

We cluster the 44 representative functions across both spatial and temporal locality using the K-means clustering algorithm [221]. Figure 3 shows how each function is grouped. We find that two groups emerge from the clustering: (1) low temporal locality functions (orange boxes in Figure 3), and (2) high temporal locality functions (blue boxes in Figure 3). Intuitively, the closer a function is to the bottom-left corner of the figure, the less likely it is to take advantage of a multi-level cache hierarchy. These functions are more likely to be good candidates for NDP. However, as we see in Section III-C, the NDP suitability of a function also depends on a number of other factors.

#### C. STEP 3: BOTTLENECK CLASSIFICATION

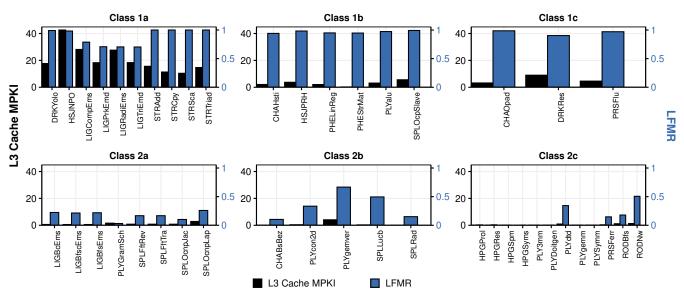

Within the two groups of functions identified in Section III-B, we use three key metrics (AI, MPKI, and LFMR) to classify the memory bottlenecks. We observe that the AI of the analyzed low temporal locality functions is low (i.e., always less than 2.2 ops/cache line, with an average of 1.3 ops/cache line). Among the high temporal locality functions, there are some with low AI (minimum of 0.3 ops/cache line) and others with high AI (maximum of 44 ops/cache line). LFMR indicates whether a function benefits from a deeper cache hierarchy. When LFMR is low (i.e., less than 0.1), then a function benefits significantly from a deeper cache hierarchy, as most misses from the L1 cache hit in either the L2 or L3 caches. When LFMR is high (i.e., greater than 0.7), then most L1 misses are not serviced by the the L2 or L3 caches, and

must go to memory. A medium LFMR (0.1–0.7) indicates that a deeper cache hierarchy can mitigate some, but not a very large fraction of L1 cache misses. MPKI indicates the memory intensity of a function (i.e., the rate at which requests are issued to DRAM). We say that a function is memory-intensive (i.e., it has a high MPKI) when the MPKI is greater than 10, which is the same threshold used by prior works [151]–[157].

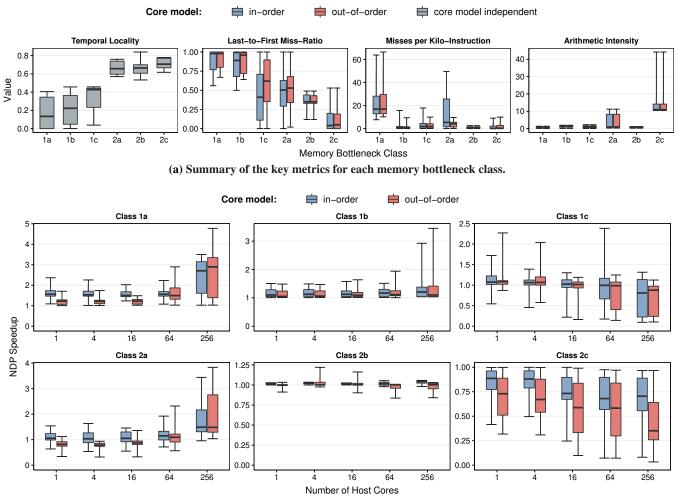

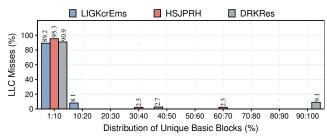

We find that six classes of functions emerge, based on their temporal locality, AI, MPKI, and LFMR values, as we observe from Figures 3 and 4. We observe that spatial locality is not a key metric for our classification (i.e., it does not define a bottleneck class) because the L1 cache, which is present in both host CPU and NDP system configurations, can capture most of the spatial locality for a function. Figure 4 shows the LFMR and MPKI values for each class. Note that we do not have classes of functions for all possible combinations of metrics. In our analysis, we obtain the temporal locality, AI, MPKI, and LFMR values and their combinations empirically. Fundamentally, not all value combinations of different metrics are possible. We list some of the combinations we do *not* observe in our analysis of 144 functions:

- A function with high LLC MPKI does *not* display low LFMR. This is because a low LFMR happens when most L1 misses hit the L2/L3 caches. Thus, it becomes highly unlikely for the L3 cache to suffer many misses when the L2/L3 caches do a good job in fulfilling L1 cache misses.

- A function with high temporal locality does not display

Figure 3: Locality-based clustering of 44 representative functions.

VOLUME 4, 2016

Figure 4: L3 Cache MPKI and Last-to-First Miss Ratio (LFMR) for 44 representative functions.

both high LFMR and high MPKI. This is because a function with high temporal locality will likely issue repeated memory requests to few memory addresses, which will likely be serviced by the cache hierarchy.

• A function with low temporal locality does *not* display low LFMR since there is little data locality to be captured by the cache hierarchy.

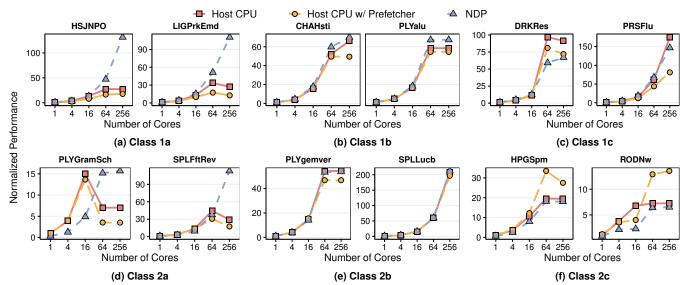

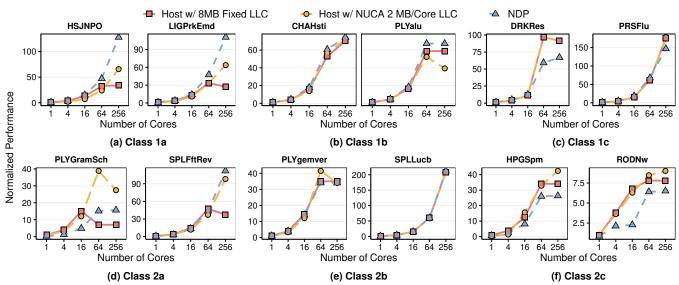

We discuss each class in detail below, identifying the memory bottlenecks for each class and whether the NDP system can alleviate these bottlenecks. To simplify our explanations, we focus on a smaller set of 12 representative functions (out of the 44 representative functions) for this part of the analysis. Figure 5 shows how each of the 12 functions scales in terms of performance for the *host CPU*, *host CPU with prefetcher*, and *NDP* system configurations.

### 1) Class 1a: Low Temporal Locality, Low AI, High LFMR, and High MPKI (*DRAM Bandwidth-Bound Functions*)

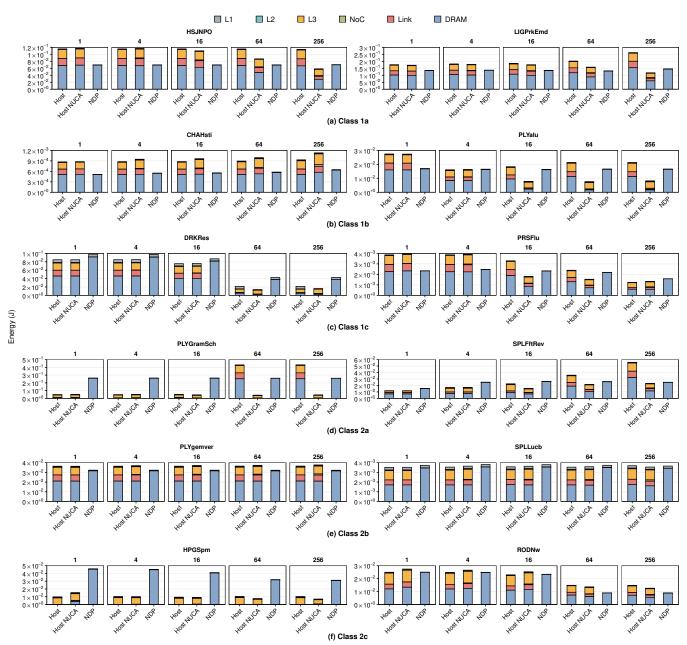

Functions in this class exert high main memory pressure since they are highly memory intensive and have low data reuse. To understand how this affects a function's suitability for NDP, we study how performance scales as we increase the number of cores available to a function, for the host CPU, host CPU with prefetcher, and NDP system configurations. Figure 5(a) depicts performance<sup>11</sup> as we increase the core count, normalized to the performance of one host CPU core, for two representative functions from Class 1a (HSJNPO and LIGPrkEmd; we see similar trends for all functions in the class).

We make three observations from the figure. First, as the number of host CPU cores increases, performance eventually stops increasing significantly. For HSJNPO, host CPU performance increases by  $27.5 \times$  going from 1 to 64 host CPU cores but only 27% going from 64 host CPU cores to 256

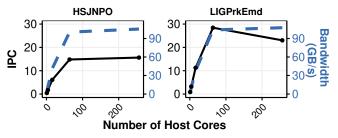

host CPU cores. For LIGPrkEmd, host CPU performance increases by  $33 \times$  going from 1 to 64 host CPU cores but decreases by 20% going from 64 to 256 host CPU cores. We find that the lack of performance improvement at large host CPU core counts is due to main memory bandwidth saturation, as shown in Figure 6. Given the limited DRAM bandwidth available across the off-chip memory channel, we find that Class 1a functions saturate the DRAM bandwidth once enough host CPU cores (e.g., 64) are used, and thus these functions are bottlenecked by the DRAM bandwidth. Second, the host CPU system with prefetcher slows down the execution of the HSJNPO (LIGPrkEmd) function compared with the host CPU system without prefetcher by 43% (38%), on average across all core counts. The prefetcher is ineffective since these functions have low temporal and spatial locality. Third, when running on the NDP system, the functions see continued performance improvements as the number of NDP cores increases. By providing the functions with access to the much higher bandwidth available inside memory, the NDP system can greatly outperform the host CPU system at a high enough core count. For example, at 64/256 cores, the NDP system outperforms the host CPU system by  $1.7 \times / 4.8 \times$  for HSJNPO, and by  $1.5 \times / 4.1 \times$  for LIGPrkEmd.

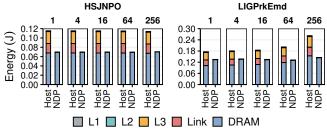

Figure 7 depicts the energy breakdown for our two representative functions. We make two observations from the figure. First, for HSJNPO, the energy spent on DRAM for both host CPU system and NDP system are similar. This is due to the function's poor locality, as 98% of its memory requests miss in the L1 cache. Since LFMR is near 1, L1 miss requests almost always miss in the L2 and L3 caches and go to DRAM in the host CPU system for all core counts we evaluate, which requires significant energy to query the large caches and then to perform off-chip data transfers. The NDP system does not access L2, L3, and off-chip links, leading

<sup>&</sup>lt;sup>11</sup>Performance is the inverse of application execution time.

Geraldo F. Oliveira et al.: DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

Figure 5: Performance of 12 representative functions on three systems: host CPU, host CPU with prefetcher, and NDP, normalized to one host CPU core.

Figure 6: Host CPU system IPC vs. utilized DRAM Bandwidth for representative Class 1a functions.

to large system energy reduction. Second, for LIGPrkEmd, the DRAM energy is higher in the NDP system than in the host CPU system. Since the function's LFMR is 0.7, some memory requests that would be cache hits in the host CPU's L2 and L3 caches are instead sent directly to DRAM in the NDP system. However, the total energy consumption on the host CPU system is still larger than that on the NDP system, again because the NDP system eliminates the L2, L3 and offchip link energy.

Figure 7: Cache and DRAM energy breakdown for representative Class 1a functions at 1, 4, 16, 64, and 256 cores.

DRAM bandwidth-bound applications such as those in Class 1a have been the primary focus of a large number

VOLUME 4, 2016

of proposed NDP architectures (e.g., [1, 46, 54, 69, 76, 132, 133, 192, 222, 223]), as they benefit from increased main memory bandwidth and do not have high AI (and, thus, do not benefit from complex cores on the host CPU system). An NDP architecture for a function in Class 1a needs to extract enough MLP [57, 176, 181]–[184, 224]–[229] to maximize the usage of the available internal memory bandwidth. However, prior work has shown that this can be challenging due to the area and power constraints in the logic layer of a 3D-stacked DRAM [1, 46]. To exploit the high memory bandwidth while satisfying these area and power constraints, the NDP architecture should leverage application memory access patterns to efficiently maximize main memory bandwidth utilization.

We find that there are two dominant types of memory access patterns among our Class 1a functions. First, functions with regular access patterns (DRKYolo, STRAdd, STRCpy, STRSca, STRTriad) can take advantage of specialized accelerators or Single Instruction Multiple Data (SIMD) architectures [1, 66], which can exploit the regular access patterns to issue many memory requests concurrently. Such accelerators or SIMD architectures have hardware area and thermal dissipation that fall well within the constraints of 3D-stacked DRAM [1, 46, 64, 230]. Second, functions with irregular access patterns (HSJNPO, LIGCompEms, LIGPrkEmd, LIGRadiEms) require techniques to extract MLP while still fitting within the design constraints. This requires techniques that cater to the irregular memory access patterns, such as prefetching algorithms designed for graph processing [46, 231]–[235], pre-execution of difficult access patterns [57, 58, 151, 183, 184, 236]-[243] or hardware accelerators for pointer chasing [55, 56, 149, 193, 244]-[246].

Geraldo F. Oliveira et al.: DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

### 2) Class 1b: Low Temporal Locality, Low AI, High LFMR, and Low MPKI (*DRAM Latency-Bound Functions*)

While functions in this class do not effectively use the host CPU caches, they do not exert high pressure on the main memory due to their low MPKI. Across all Class 1b functions, the average DRAM bandwidth consumption is only 0.5 GB/s. However, all the functions have very high LFMR values (the minimum is 0.94 for CHAHsti), indicating that the host CPU L2 and L3 caches are ineffective. Because the functions cannot exploit significant MLP but still incur longlatency requests to DRAM, the DRAM requests fall on the critical path of execution and stall forward progress [57, 58, 151, 176, 247]. Thus, Class 1b functions are bottlenecked by DRAM latency. Figure 5(b) shows performance of both the host CPU system and the NDP system for two representative functions from Class 1b (CHAHsti and PLYalu). We observe that while performance of both the host CPU system and the NDP system scale well as the core count increases, NDP system performance is always higher than the host CPU system performance for the same core count. The maximum (average) speedup with NDP over host CPU at the same core count is  $1.15 \times (1.12 \times)$  for CHAHsti and  $1.23 \times (1.13 \times)$  for PLYalu.

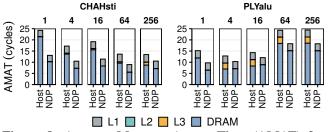

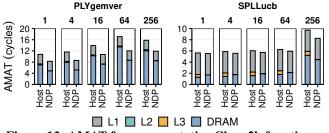

We find that the NDP system's improved performance is due to a reduction in the Average Memory Access Time (AMAT) [248]. Figure 8 shows the AMAT for our two representative functions. Memory accesses take significantly longer in the host CPU system than in the NDP system due to the additional latency of looking up requests in the L2 and L3 caches, even though data is rarely present in those caches, and going through the off-chip links.

Figure 8: Average Memory Access Time (AMAT) for representative Class 1b functions.

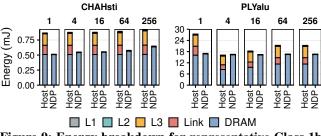

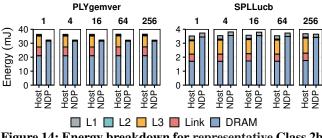

Figure 9 shows the energy breakdown for Class 1b representative functions. Similar to Class 1a, we observe that the L2/L3 caches and off-chip links are a large source of energy usage in the host CPU system. While DRAM energy increases in the NDP system, as L2/L3 hits in the host CPU system become DRAM lookups with NDP, the overall energy consumption in the NDP system is greatly smaller (by 69% maximum and 39% on average) due to the lack of L2 and L3 caches.

Class 1b functions benefit from the NDP system, but primarily because of the lower memory access latency (and energy) that the NDP system provides for memory requests that need to be serviced by DRAM. These functions could

Figure 9: Energy breakdown for representative Class 1b functions.

benefit from other latency and energy reduction techniques, such as L2/L3 cache bypassing [51, 249]–[260], low-latency DRAM [15, 22]–[26, 89, 127, 261]–[276], and better memory access scheduling [153]–[157, 175]–[177, 247, 277]–[290]. However, they generally do *not* benefit significantly from prefetching (as seen in Figure 5(b)), since infrequent memory requests make it difficult for the prefetcher to successfully train on an access pattern.

# 3) Class 1c: Low Temporal Locality, Low AI, Decreasing LFMR with Core Count, and Low MPKI (*L1/L2 Cache Capacity Bottlenecked Functions*)

We find that the behavior of functions in this class depends on the number of cores they are using. Figure 5(c) shows the host CPU system and the NDP system performance as we increase the core count for two representative functions (DRKRes and PRSFlu). We make two observations from the figure. First, at low core counts, the NDP system outperforms the host CPU system. With a low number of cores, the functions have medium to high LFMR (0.5 for DRKRes at 1 and 4 host CPU cores; 0.97 at 1 host CPU core and 0.91 at 4 host CPU cores for PRSFlu), and behave like Class 1b functions, where they are DRAM latency-sensitive. Second, as the core count increases, the host CPU system begins to outperform the NDP system. For example, beyond 16 (64) cores, the host CPU system outperforms the NDP system for DRKRes (PRSFlu). This is because as the core count increases, the aggregate L1 and L2 cache size available at the host CPU system grows, which reduces the miss rates of both L2 and L3 caches. As a result, the LFMR decreases significantly (e.g., at 256 cores, LFMR is 0.09 for DRKRes and 0.35 for PRSFlu). This indicates that the available L1/L2 cache capacity bottlenecks Class 1c functions.

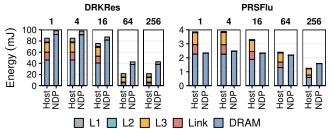

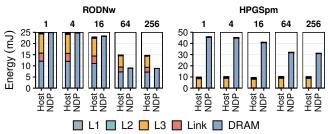

Figure 10 shows the energy breakdown for Class 1c functions. We make three observations from the figure. First, for functions with larger LFMR values (PRSF1u), the NDP system provides energy savings over the host CPU system at lower core counts, since the NDP system eliminates the energy consumed due to L3 and off-chip link accesses. Second, for functions with smaller LFMR values (DRKRes), the NDP system does not provide energy savings even for low core counts. Due to the medium LFMR, enough requests still hit in the host CPU system L2/L3 caches, and these cache hits become DRAM accesses in the NDP system,

which consume more energy than the cache hits. Third, at high-enough core counts, the NDP system consumes more energy than the host CPU system for all Class 1c functions. As the LFMR decreases, the functions effectively utilize the caches in the host CPU system, reducing the off-chip traffic and, consequently, the energy Class 1c functions spend on accessing DRAM. The NDP system, which does not have L2 and L3 caches, pays the larger energy cost of a DRAM access for all L2/L3 hits in the host CPU system.

Figure 10: Energy breakdown for representative Class 1c functions.

We find that the primary source of the memory bottleneck in Class 1c functions is limited L1/L2 cache capacity. Therefore, while the NDP system improves performance and energy of some Class 1c functions at low core counts (with lower associated L1/L2 cache capacity), the NDP system does not provide performance and energy benefits across all core counts for Class 1c functions.

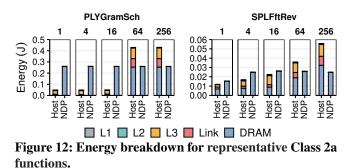

## 4) Class 2a: High Temporal Locality, Low AI, Increasing LFMR with Core Count, and Low MPKI (*L3 Cache Contention*

#### **Bottlenecked Functions**)

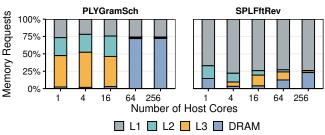

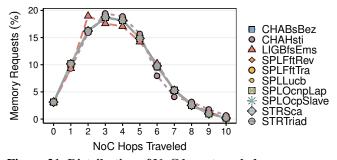

Like Class 1c functions, the behavior of the functions in this class depends on the number of cores that they use. Figure 5(d) shows the host CPU system and the NDP system performance as we increase the core count for two representative functions (PLYGramSch and SPLFftRev). We make two observations from the figure. First, at low core counts, the functions do not benefit from the NDP system. In fact, for a single core (16 cores), PLYGramSch slows down by 67% (3 $\times$ ) when running on the NDP system, compared to running on the host CPU system. This is because, at low core counts, these functions make reasonably good use of the cache hierarchy, with LFMR values of 0.03 for PLYGramSch and lower than 0.44 for SPLFftRev until 16 host CPU cores. We confirm this in Figure 11, where we see that very few memory requests for PLYGramSch and SPLFftRev go to DRAM (5% for PLYGramSch, and at most 13% for SPLFftRev) at core counts lower than 16. Second, at high core counts (i.e., 64 for PLYGramSch and 256 for SPLFftRev), the host CPU system performance starts to decrease. This is because Class 2a functions are bottlenecked by cache contention. At 256 cores, this contention undermines the cache effectiveness and causes the LFMR to increase to 0.97 for PLYGramSch and 0.93 for SPLFftRev. With the last-level cache rendered essentially

ineffective, the NDP system greatly improves performance over the host CPU system: by  $2.23 \times$  for PLYGramSch and  $3.85 \times$  for SPLFftRev at 256 cores.

Figure 11: Memory request breakdown for representative Class 2a functions.