# **DC Distributed Power Systems**

# Analysis, Design and Control for a Renewable Energy System

Per Karlsson

Doctoral Dissertation in Industrial Electrical Engineering Department of Industrial Electrical Engineering and Automation

Department of Industrial Electrical Engineering and Automation Lund University Box 118 SE-221 00 LUND SWEDEN

ISBN 91-88934-25-X CODEN:LUTEDX/(TEIE-1033)/1-200/(2002)

© 2002 Per Karlsson Printed in Sweden by Media-Tryck, Lund University Lund 2002

### **Abstract**

Renewable energy systems are likely to become wide spread in the future due to environmental demands. As a consequence of the dispersed nature of renewable energy systems, this implies that there will be a distributed generation of electric power. Since most of the distributed electrical energy sources do not provide their electric power at line frequency and voltage, a DC bus is a useful common connection for several such sources. Due to the differences in output voltage among the sources, depending on both the type of source and their actual operating point, the sources are connected to the DC power system via power electronic converters. The intention behind the presented work is not to replace the existing AC power system, but to include local DC power systems. The AC and DC power systems are connected at some points in the network. The renewable energy sources are weak compared to the present hydro power and nuclear power plants, resulting in a need of power conditioning before the renewable energy is fed to the transmission lines. The benefit of such an approach is that power conditioning is applied on a central level, i.e. at the interface between the AC and DC power systems.

The thesis starts with an overview of related work. Present DC transmission systems are discussed and investigated in simulations. Then, different methods for load sharing and voltage control are discussed. Especially, the voltage droop control scheme is examined thoroughly. Since the droop control method does not require any high-speed communication between sources and loads, this is considered the most suitable for DC distributed power systems. The voltage feed back design of the controller also results in a specification of the DC bus capacitors (equivalents to DC link capacitors of single converters) needed for filtering. If the converters in the DC distribution system are equipped with capacitors selected from this design criterion and if the DC bus impedance is neglected, the source converters share the total load equally in per unit.

The same DC distribution bus configuration is studied in a wind power application. Especially the dynamic properties of load-source interactions are highlighted. They are interesting since the sources are considered weak for a distributed power system. This is illustrated with simulations where the power is fed from wind turbines only and constant power loads are controlled at the same time as the DC bus voltage level. The wind power generators are modeled as permanent-magnet synchronous machines. The controller needed for the machines, including position estimation and field weakening, is discussed. To control the DC bus voltage, the available wind power must be higher than the power consumed by the loads and the excess power removed by pitch angle control. Pitch angle control is a comparably slow process and, therefore, the DC bus voltage controller must handle the transient power distribution.

Personal safety and prevention of property damage are important factors of conventional AC power systems. For the investigated DC power system this is maybe even more important due to the fact that the star point of the sources and loads is left ungrounded or grounded through high impedance. The difficulty of detecting ground faults arises from the fact that the AC sources and loads are ungrounded or have high impedance to ground in order to effectively block zero-sequence currents flowing between the AC systems. A grounding scheme for the DC distribution system together with algorithms for detection of ground faults, are presented. The proposed method detects ground faults on both the AC and DC sides and is extended to cover short circuit faults with a minor work effort.

Two schemes for high voltage interconnection of DC systems are studied. One of them provides galvanic isolation, which is an advantage since elevated voltage might appear in the DC systems otherwise, in the case of a ground fault in the high voltage interconnection.

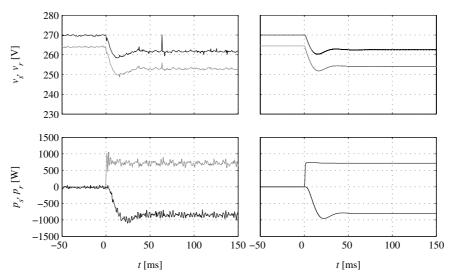

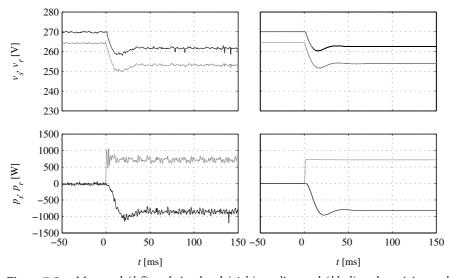

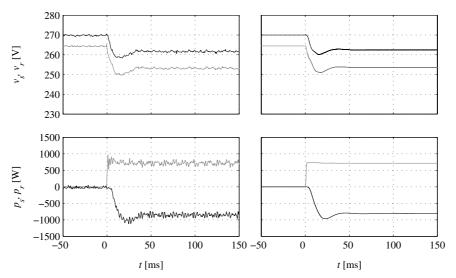

Experimental verifications follow the theoretical investigations introduced above. First, dynamic properties are studied and the behaviour predicted from theoretical analysis and simulations is verified. Then, load sharing is investigated. Also in this investigation, the experimental results agree with the simulated.

# **Acknowledgements**

First, I would like to thank my colleague and friend Jörgen Svensson who I have worked with the last three years. I would also like to express my sincere gratitude to my friend and former colleague Martin Bojrup, who I worked with during 1996-1999.

I am very grateful to my two mentors, Professor Lars Gertmar and Professor Sture Lindahl. Both Lars and Sture have time to discuss all kinds of topics, not only technical.

I would also like to thank my supervisors, Professor Mats Alaküla and Professor Gustaf Olsson. Professor Alaküla, who has been my main supervisor, has shown much enthusiasm for power electronics, not strictly focusing on the research project. Even if his schedule is tight, Mats has always time to give a helping hand. Mats has also encouraged me to participate in courses and meetings, which is greatly acknowledged. Gustaf is also head of the department. As such, he strives hard to provide a friendly atmosphere at the department, which has been very successful.

The steering committee, including the four professors above, and Dr Magnus Akke, Dr Olof Samuelsson and Dr Jan Svensson has contributed with valuable comments and discussions. This has enhanced my work and is greatly acknowledged.

I would also like to thank Anders Lasson, ABB Utilities AB, and Ulf Thorén, Sydkraft AB from the steering committee of the former research project I was involved in together with Martin Bojrup.

Professor Frede Blaabjerg and Dr Stig Munk Nielsen, both at Aalborg University in Denmark, have also meant a lot to me. In 1996 they assisted me when I evaluated the SABER™ simulation software. Professor Blaabjerg also evaluated my Licentiate's thesis on Quasi Resonant DC Link Converters.

I would like to express my gratitude to the staff at IEA. Even if all the people at the department are helpful and friendly there are those that I owe a special thank. Dr Christian Rosen is a very good friend and a person you can discuss anything with. He has also proof read several of my articles, which is greatly acknowledged. Also at IEA, Getachew Darge and Bengt Simonsson have provided practical help for electronic designs. I think that Bengt has at least one catalogue or data book for every apparatus and component. I must thank Dr Ulf Jeppsson who used to maintain the UNIX-system with softwares like SABER<sup>TM</sup> and ACE<sup>TM</sup>, and nowadays takes care of the economical issues of the department. Thanks to the former Associate Professor at IEA, Stig Lindquist, for always being nice.

I am very thankful to Magnus, Mats, Lars, Christian, Jan and Jörgen for proof reading my thesis.

I have also had the privilege to work together with Annika Nilsson, Department of Building and Environmental Technology, Lund University. Annika does not hesitate to teach environmental issues in an advanced course on power electronics or present the same material on a conference on power electronics.

I also thank the staff at ABB University in Ludvika, especially Ewa Wikström and Elly Hartings, for encouraging me to participate in their courses on HVDC and HVDC Light.

I do not know how to thank my family enough. My parents, Siv and Axel, have always encouraged me to study without putting any requirements on the result. They have also helped me with all kinds of practical issues and financial support for my undergraduate studies. I cannot imagine that this would have been possible without your help – thanks again. My dear and beloved Anna has enhanced my life to a large extent. Though I spend too much time at the department, Anna does not complain. I hope that I sometime can return this patience when she needs it.

The Control of Renewable Energy Sources (CORE) project is financially supported by DESS (Delegationen för Energiförsörjning i SydSverige, The Board for Energy Supply in Southern Sweden). This support is gratefully acknowledged.

Per Karlsson

# **Contents**

| CHAP | TER 1 INTRODUCTION                          | 1  |

|------|---------------------------------------------|----|

| 1.1  | Objectives                                  | 2  |

| 1.2  | Contributions                               |    |

| 1.3  | Outline of the thesis.                      |    |

| 1.4  | Publications                                | 5  |

| 1.5  | Previous work                               | 7  |

| 1.6  | Specification of a distributed power system | 20 |

| CHAP | TER 2 EXISTING DC POWER SYSTEMS             | 21 |

| 2.1  | HVDC                                        | 22 |

| 2.2  | VSC based HVDC                              | 26 |

| CHAP | TER 3 DC BUS VOLTAGE CONTROL                | 31 |

| 3.1  | Investigated system                         | 32 |

| 3.2  | DC bus model                                | 33 |

| 3.3  | Controller structure                        | 34 |

| 3.4  | Cable impedance                             | 44 |

| 3.5  |                                             |    |

| 3.6  | Concluding remarks                          |    |

| CHAP | TER 4 WIND POWERED DC BUS                   | 63 |

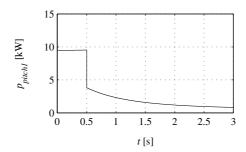

| 4.1  | Pitch angle control                         | 64 |

| 4.2  | Droop offset control                        | 66 |

| 4.3  | Speed estimation                            |    |

| 4.4  | Field weakening                             | 68 |

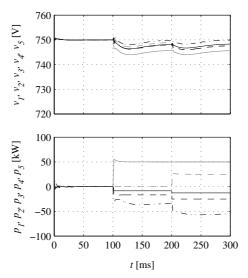

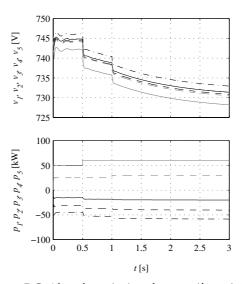

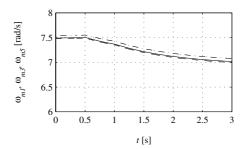

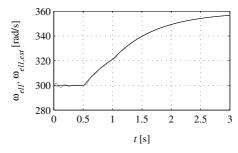

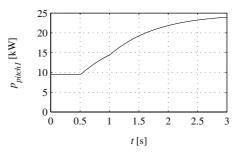

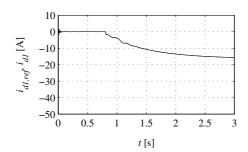

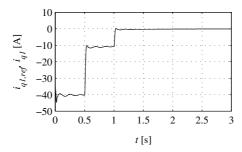

| 4.5  | Simulations                                 | 70 |

| CHAP | TER 5 FAULT DETECTION AND CLEARANCE  | 79  |

|------|--------------------------------------|-----|

| 5.1  | Grounding and fusing                 | 79  |

| 5.2  | Fault situations                     | 80  |

| 5.3  | Detection and selectivity            | 88  |

| 5.4  | Simulations                          | 94  |

| СНАР | TER 6 DC TRANSMISSION                | 105 |

| 6.1  | The back-to-back structure           | 105 |

| 6.2  | The DAB structure                    | 109 |

| 6.3  | Proposed interconnection structure   | 114 |

| CHAP | TER 7 MEASUREMENTS                   | 119 |

| 7.1  | Experimental set-up                  | 119 |

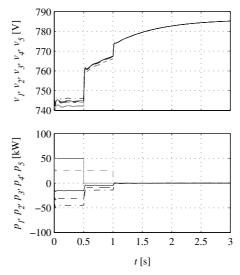

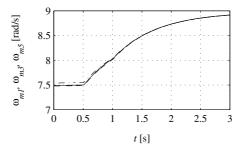

| 7.2  | Dynamic properties                   | 121 |

| 7.3  | Load sharing                         | 130 |

| CHAP | TER 8 CONCLUSIONS                    | 135 |

| 8.1  | Summary of results                   | 135 |

| 8.2  | Future work                          | 138 |

| REFE | RENCES                               | 139 |

| APPE | NDIX A MODULATION                    | 149 |

| A.1  | Modulation methods                   | 149 |

| A.2  | Vector representation                | 155 |

| APPE | NDIX B VECTOR CONTROL                | 167 |

| APPE | NDIX C CONVERTER LOSSES              | 171 |

| APPE | NDIX D NORMALISATION                 | 177 |

| D.1  | Base system for a single converter   | 177 |

| D.2  | Converter data expressed in per unit | 178 |

| APPE | NDIX E NOMENCLATURE                  | 183 |

# **Chapter 1**

### Introduction

In this chapter DC distributed power systems (DPS) are introduced together with a review of the DC DPS state of the art technology. Renewable energy systems are likely to become wide spread in the future, due to environmental demands, for example, regarding pollution. This implies that there will be a distributed generation of electric power. Since several of the distributed electrical energy sources provide DC voltage, several such sources might be connected. Due to the differences in output voltage among the sources, depending on both the type of source and their actual operating point, the sources are connected to the DC power system via power electronic converters.

It should be clear that the intention is not to replace the existing AC power system, but to include local DC systems [14]. These AC and DC systems are connected at some points in the network. The benefit of such an approach arises from the fact that renewable energy sources are weak compared to present fossil fuel, hydro power and nuclear power plants, resulting in a need of power conditioning before being fed to the transmission lines. With a DC distributed system, conditioning can be applied at a central level of the AC distribution system, close to the DC system connection points. Also, several consumer loads operate on DC (rectified AC). Therefore, DC distribution could be used to omit the need for transformers and rectifiers in every single load.

The DC distributed power system has various kinds of energy storage added, which means that it can support nearby customers during AC power system failure or emergency situations. Also, sensitive equipment likely to be installed in future intelligent buildings also needs energy backup, i.e. uninterruptable

power supply (UPS) properties. This is already in use, for example, in telecommunication sub-stations where backup batteries are usually installed. Another example is given in [63] where a battery powered DC system is supplying the AC system circuit breaker control system. Of course, reliable operation of such systems is necessary.

A larger part of the power transmission network is likely to use high voltage direct current (HVDC) transmission technology in the future [14]. Also, the recently introduced medium voltage DC (MVDC) technology is likely to be used in DC distributed power systems [14]. This implies that future electric power systems constitute a mixture between AC and DC technology.

A distributed power system with as much as several hundred power electronic converters, call for new methods and technologies, both on the operator and system level. Not only an increased control effort is required, but also the complexity of protection systems will increase in the case of dispersed generation [31]. This is true especially if autonomous operation of the distributed power system is intended.

This work addresses control and stability issues of DC distributed power systems together with their connections to surrounding AC power systems, sources and loads. Also grounding and issues on fault detection and clearance are considered.

#### 1.1 Objectives

The main objective of this work is to study the consequences of large-scale incorporation of power electronic converters in DC distributed power systems. The main objective is split into several sub-objectives, all imperative for a large-scale system. The first issue to treat is selection of a suitable system voltage, at least at the consumer level. Stability and dynamic properties of DC voltage control are of great concern. Requirements on hardware and software should be stated so that the system could grow, i.e. additional converters installed in an existing system, without system degradation. Voltage control in the case of weak sources should also be investigated, since several of the renewable energy sources possess low inertia. Suitable grounding and fault detection schemes should be investigated. Connection of several DC systems should be investigated. One important objective is that the need of communication should be studied.

1.2 Contributions 3

#### 1.2 Contributions

The contributions of this work are given in Chapters 3 to 7 and concluded in Chapter 8. The main results are summarised here. Suitable voltage levels are not explicitly discussed in the thesis. Instead, a DC bus voltage level suitable for 400 V AC sources and loads is adopted. This is due to the fact that by doing so, the proposed system voltage covers existing consumer loads. Future apparatus might require a different load voltage level. To compensate this shortcoming, a large portion of the investigation is made on a per unit (p.u.) basis. Therefore, the results can be used for any DC bus voltage level.

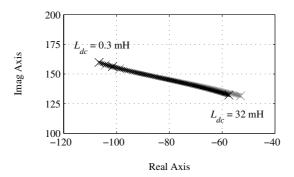

The converters are first specified with focus on interaction between the AC and DC sides. Then a DC bus voltage droop controller is adopted. The demands on interaction together with droop requirements give a specification of the relation between rated power and converter DC side filter, i.e. DC bus capacitance, for each converter. The dynamic properties are investigated, both by means of stability analysis, in terms of root-locus, and large-signal simulations. It is found that for reasonable DC bus cable parameters, stability is of minor concern, for the selected DC side filter. In other words, the requirements on interaction between input and output of the converters is stronger than the stability requirement. Voltage droop control provides autonomous load sharing, implying that communication is not needed. The selected implementation of the droop algorithm and the controller parameters allow an arbitrary number of converters in the DC system. Furthermore, the already inserted units are not altered if additional units are incorporated.

A wind powered DC system is adopted to investigate voltage control and load sharing in the case of renewable energy sources. In this case a speed droop algorithm is developed. The dynamic properties of speed and voltage droop control are investigated. It is concluded that low-speed communication is beneficial for non-dispatchable sources. A fault detection algorithm is developed. The algorithm is studied for different levels of communication, ranging from none to point-to-point communication. An existing converter topology is adopted for interconnection of DC systems. The same converter topology is also used for power transmission. Voltage droop control is adopted also here. Thus, high-speed communication is not necessary. However, when low-bandwidth communication is utilised, the system operator has the ability to control power flow. A laboratory set-up is designed to verify voltage control, load sharing and fault detection.

#### 1.3 Outline of the thesis

This chapter contains a brief introduction to the thesis and the academic work presented. A survey of previous work is also given. Chapter 2 reviews classical HVDC and Voltage Source Converter (VSC) based HVDC transmission systems. The study includes simulations, where especially the harmonic content of the currents is compared.

In Chapter 3, voltage and power control methods for the investigated distributed power system are developed. This analysis also results in a method for selection of DC bus filter capacitors. The steady state and dynamic properties of the selected control scheme are investigated for varying cable parameters. Load sharing is investigated for different voltage control methods.

In Chapter 4, the same system but with weak sources is investigated. Here, the DC power system is fed only with wind power and still constant power loads can be supplied and the DC bus voltage controlled. Personal safety and protection of equipment are important issues for any power system and Chapter 5 is devoted to these topics. The chapter starts with a presentation of the grounding scheme and typical fault conditions. Then the methods of fault detection and localisation are presented and verified in simulations.

In Chapter 6, connection of DC distributed systems is considered. The proposed scheme contains a transformer, providing galvanic separation between different DC systems. In Chapter 7, measurement results verifying dynamic properties, load sharing and fault detection are presented. The work is concluded in Chapter 8.

MATLAB<sup>TM</sup> Power System Blockset is utilised for the time-domain simulations of Chapter 2 where thyristor based converters are considered. DYMOLA<sup>TM</sup> is utilised for the time-domain simulations including transistor based converters, i.e. for the simulation of VSC based HVDC transmission in Chapter 2 and all time-domain simulations in Chapters 3 to 7. Large-signal converter models are used for simulations investigating two-converter systems and DC transmission systems. Average converter models are utilised for simulations where load sharing or fault detection is investigated. Discrete-time controllers are utilised for both the large-signal and the average converter models. MATLAB<sup>TM</sup> is used in Chapter 3 for investigation of stability for different cable parameters in terms of root-locus of the poles. The simulations in the appendixes are all carried out in MATLAB<sup>TM</sup>-SIMULINK<sup>TM</sup>.

1.4 Publications 5

#### 1.4 Publications

The results presented in this thesis regard DC bus voltage control and fault detection and clearance, found in Chapters 3, 4, 5 and 7. The main results of these chapters are also presented in

- P. Karlsson and J. Svensson, "DC Bus Voltage Control for Renewable Energy Distributed Power Systems", IASTED Power and Energy Systems Conference, PES 2002 Conf. Proc., Marina del Rey, CA, USA, May 13-15, 2002, pp. 333-338.

- P. Karlsson and J. Svensson, "Fault Detection and Clearance in DC Distributed Power Systems", IEEE Nordic Workshop on Power and Industrial Electronics, NORPIE 2002 workshop proc., Stockholm, Sweden, Aug. 12-14, 2002, CD-ROM pages 6.

- P. Karlsson and J. Svensson, "DC Bus Voltage Control for a Distributed Power System", provisionally accepted for publication in IEEE transactions on power electronics, paper no. 2001-834-LP.

- P. Karlsson and J. Svensson, "Voltage Control and Load Sharing in DC Distribution Systems", submitted to European Conference on Power Electronics and Applications, EPE 2003, Toulouse, France, Sept. 2-4, 2003.

The thesis author has also authored the publication

J. Svensson and P. Karlsson, "Wind Farm Control Software Structure", International Workshop on Transmission Networks for Offshore Wind Farms, workshop proc., Stockholm, Sweden, Apr. 11-12, 2002, proceeding pages 15.

in the same research project. The contribution made by the thesis author in the last paper is minor.

The previous work on off-board battery chargers for electric vehicles, also part of the research work, is reported in

P. Karlsson, M. Bojrup, M. Alaküla and L. Gertmar, "Efficiency of Off-Board, High Power, Electric Vehicle Battery Chargers with Active Power Line Conditioning Capabilities", European Conference on Power Electronics and Applications, EPE '97 Conf. Rec., Trondheim, Norway, Sept. 8-10, 1997, vol. 4, pp. 4688-4692.

- M. Bojrup, P. Karlsson, B. Simonsson and M. Alaküla, "A Dual Purpose Battery Charger for Electric Vehicles", IEEE Power Electronics Specialists Conference, PESC '98 Conf. Rec., Fukuoka, Japan, May 17-22, 1998, vol. 1, pp. 565-570.

- M. Bojrup, P. Karlsson, M. Alaküla and L. Gertmar, "A Multiple Rotating Integrator Controller for Active Filters", European Conference on Power Electronics and Applications, EPE '99 Conf. Rec., Lausanne, Switzerland, Sept. 7-9, 1999, CD-ROM pages 9.

- P. Karlsson, M. Bojrup, M. Alaküla and L. Gertmar, "Zero Voltage Switching Converters", IEEE Nordic Workshop on Power and Industrial Electronics, NORPIE 2000 workshop proc., Aalborg, Denmark, Jun. 13-16, 2000, pp. 84-88.

- P. Karlsson, M. Bojrup, M. Alaküla and L. Gertmar, "Design and Implementation of a Quasi-Resonant DC Link Converter", European Conference on Power Electronics and Applications, EPE 2001 Conf. Rec., Graz, Austria, Aug. 27-29, 2001, CD-ROM pages 10.

Only minor parts of the work reported in the second and third publications above are attributed the author of this thesis. The work on resonant converters reported in the other publications above is also the basis of the Licentiate's thesis

P. Karlsson, "Quasi Resonant DC Link Converters - Analysis and Design for a Battery Charger Application", Licentiate thesis, Department of Industrial Electrical Engineering and Automation, Lund Institute of Technology, Lund, Sweden, November 1999.

This work was evaluated by Professor Frede Blaabjerg at the Department of Energy Technology, Aalborg University, Denmark.

Besides the publications within the research projects, another publication related to power electronics education has been presented

A. Nilsson, P. Karlsson and L. Gertmar, "Environmental Engineering in the Power Electronics Education", European Conference on Power Electronics and Applications, EPE 2001 Conf. Rec., Graz, Austria, Aug. 27-29, 2001, CD-ROM pages 10.

Less than half of the work of this paper is attributed the thesis author.

#### 1.5 Previous work

This section provides a literature survey of previous work on renewable energy sources and distributed power systems in which the most relevant previous work is discussed. A classification of the papers is made based on the nature of the references even though several of them cover more than one topic. However, the references are sorted under the topic, which the thesis author find most interesting in the context of the rest of the thesis.

#### **Distributed energy systems**

Several arguments for distributed power systems are listed in [31]. Among these, transmission capability saturation of centralised power systems and related stability problems seem most important. The additional intelligence needed to control, protect and maintain distributed power systems is focused in [31]. The future market of (DC) distributed power systems is discussed in [33], where it is concluded that the growing market includes computer, military/aerospace and communication applications. It is also stated that distributed power systems are more costly than centralised. Note that in [31], the distributed system is part of a nation wide power transmission/distribution system including dispersed generation. In [33], the distributed system intended is restricted to supply power to electronic equipment like inside a single computer.

Power electronics for use in renewable energy applications are discussed in [14]. Also some benefits and drawbacks associated with renewable energy sources are discussed. Photovoltaic, fuel cell and wind energy systems are reviewed briefly. Small-scale hydro pump stations or battery banks for electric energy storage are, however, not discussed in [14]. Still, they are included in the principal scheme of a distributed power system, together with flywheel and superconducting magnetic energy storages.

#### DC distributed power systems

Some of the literature studied does not fit into the study, though interesting. For example, [39][40][41][42][66] investigate a high current, low voltage DC mesh with thyristor based converters. In [39][40][42], a superconducting power system is considered, whereas an industrial power distribution system with inherent UPS properties is considered in [41][66]. The intended system

might contain several hundred thyristor based sources (rectifiers) and loads (inverters), but the simulated systems are of considerably lower complexity. In [39], a DC power system formed by one rectifier and three inverters is studied. In [40][41][42][66], three rectifiers are used as sources. Since three sources are present, load sharing has to be considered. In all these cases, DC voltage droop control is used to give appropriate load sharing. This means that a voltage droop characteristic is assigned to each source. In [40][66], the LVDC mesh is simplified to a ring bus and in [42] a superconducting energy storage (SMES) is added to the system. The paper [41] focuses on investigation of the droop scheme. It is stated that this works well for superconducting networks. However, the performance of a non-superconducting network is questioned.

In the literature the term power electronic building block (PEBB) is sometimes used as a term for generic building blocks for power conversion, control and distribution with control intelligence and autonomy. The work presented in [11] proposes a distributed digital controller for PEBBs. The main requirements and desired features of such a controller is discussed in [11]. The proposed controller is based on components presently available and used in other applications.

A 600 W front-end source converter module and a 300 W load converter module are designed in [36]. The source converter is designed for zero voltage transition (ZVT) technique and the load converter utilises zero voltage switching (ZVS) technique. The source converter is formed by a single-phase rectifier, equipped with a power factor corrector (PFC), i.e. followed by a boost converter. The DC system voltage equals 48 V. Experimental results are included in [36]. In [46], converter topologies suitable for DC distributed power systems are evaluated. Especially, source side front-end boost rectifier candidates are investigated but also load side converter modules.

#### Voltage control and load sharing

There are basically two different methods to achieve load sharing. One of the methods is referred to as the droop concept and the other as the master/slave concept.

For the droop concept, a finite loop gain for the DC voltage controller is adopted. A droop characteristic is obtained from the transfer function slope in the *P-V* plane at the desired DC bus voltage. Since this droop characteristic appears as a negative slope in the *P-V* plane, load sharing is obtained. The

quality of load sharing is determined by the negative slope of the droop characteristic, i.e. for a steep slope, load sharing is good but voltage regulation is poor. On the other hand, for a shallow slope, load sharing is poor but voltage regulation is good. Therefore, a trade-off between voltage regulation and load sharing has to be made for the droop concept.

In the master/slave concept, only one of the source converters is controlling the DC bus voltage. The other source converters are current controlled. This results in a stiff DC bus voltage regulation and a fully controllable load sharing.

The papers [38][52][58] give an overview of these paralleling methods. According to [52], five different droop schemes exist. The first is based on the use of converters with inherent droop feature. The second scheme is based on voltage droop due to series resistors. The third scheme is called voltage droop via output current feedback. The fourth scheme is referred to as current mode with low DC gain. The fifth is scheduling control via a non-linear gain. The benefits of the droop schemes are the ease of implementation and expansion and that no communication between the converters (i.e. supervisory control) is needed. This gives high modularity and reliability. The main disadvantages are that the voltage regulation is degraded to achieve the droop characteristic and that the current sharing is poor due to open loop control of the entire system.

The next large group identified in [52] is referred to as active current sharing schemes. Common to these schemes, is that an additional control loop is used to provide current sharing. According to [52], three different active current sharing control structures are used for parallel converter systems. The first control structure is called inner loop regulation (ILR). The second control structure is referred to as outer loop regulation (OLR). The third structure relies on an external controller (EC). EC implies a large number of interconnections between the converters. This means that both the modularity and reliability might be degraded. It is, however, stated in [52] that the rapid development of distributed power systems implies that this technique should be examined in a new light. The high level supervisory controller can be redundant, and the converter cells are only responsible for gating and fault indication. This method is likely to yield the highest performance because of its possibility of interleaving [52].

Also six current programming (CP) methods for active current sharing schemes are reviewed in [52]. Of these six, three are average and three are

master/slave current programming methods. Seven methods to operate multiple DC-DC converters in parallel are given in [38]. In [58], four methods to achieve load sharing in parallel converter systems are given.

In [29], load sharing properties are studied by examining the output plane (output current versus voltage). A small-signal model is developed for the investigation. Simulations and experiments verify the theoretical results. The output plane is derived from equations for current programmed converters in [13]. The output plane is verified in large-signal simulations and experiments. Droop load sharing is evaluated in [37]. One of the important conclusions made in [37] is that the droop method requires precise control of the initial output voltage. It is also stated that the main advantages of the droop control method compared to other converter paralleling schemes, are the ease of implementation and that communication by means of control-wire connection is not required.

A droop function with a programmed droop resistance equal to the equivalent series resistance (ESR) of the output capacitor is proposed in [16]. Load sharing with the selected droop function is investigated by means of simulations and experiments.

A paralleling scheme called central-limit control, closely related to master/slave control, is presented in [64] and reviewed in [58]. The main difference between master/slave and central-limit control is that for the latter all the sources regulate the load converter DC bus voltage.

Autonomous master/slave current sharing is used in [62] for two source converters connected in parallel. A small-signal model for the two source converters together with their controllers is derived. A current sharing algorithm is also presented. Current sharing control is necessary since otherwise small differences in the source converter parameters would cause severe load imbalance. Also, the voltage loop is investigated. Design of the compensators is discussed but only a few actual results are concluded.

In a situation where several converters connected to the DC distribution bus that all control the voltage precisely to the reference at their respective connection point, load sharing among sources is not controlled. Instead, load sharing is entirely determined by the distribution bus impedance [75].

In [76], it is stated that distributed power systems have better performance than centralised. Moreover, it is stated that the sources connected in parallel to the DC bus (front-end boost rectifiers), should share the load to ensure proper

operation. In [76], the droop method is used together with gain scheduling, which is said to give a robust design in terms of source-load interaction, i.e. good load sharing and good voltage regulation for a modular design approach.

According to [76], the main problems of master/slave load sharing are that fast communication is required and that a single point failure can disable the entire system. Also, all modules are control dependent. Six important issues are addressed in [76]. The first is stability, for example, in terms of interactions between parallel converters (especially in the case of three-phase sources due to the appearance of zero-sequence currents). The second important issue is load sharing when several sources are connected in parallel to the DC distribution bus. The third issue is modularity, i.e. the ability to manufacture and maintain the DC system. The fourth issue is autonomous control enhancing modularity and providing increased system reliability and redundancy. The fifth issue is DC bus voltage control, which is imperative. The sixth and last issue identified in [76], is the source output impedance which indeed affect several of the other issues, for example, the interaction between converters connected to the DC system.

The gain-scheduling method utilised in [76] is based on a modified droop method where the voltage loop gain is increased for increasing output power in such a way that the voltage error decreases compared to the case with a constant gain droop function. According to [76], both DC bus voltage control and load sharing show better performance compared to master/slave control. An interesting option not discussed in [76] is to use an adaptive controller for the DC bus voltage control.

In [44], a droop load sharing scheme is investigated where the DC bus voltage reference is adaptively controlled for each converter, in order to improve voltage regulation and load sharing.

#### Small-signal stability based on impedance specification

A system with an arbitrary number of DC-DC source converters paralleled using master/slave control, is investigated in [61]. Small-signal stability and dynamic performance are investigated. Also, a current sharing compensator is developed. The compensator is designed in the frequency-domain and verified through time-domain simulations.

A small-signal model for a parallel rectifier system is derived in [12]. Dynamic properties in the case of long inductive and resistive cables are investigated. It

is found that the cable parameters do not affect the dynamic properties extensively. Load sharing is investigated for both droop and master/slave methods. It is found that a system with parallel rectifiers is stable provided that each individual rectifier is stable when the droop method is applied. This is not true in the case of master/slave control, which should be designed carefully.

Small-signal stability criteria for DC-DC converter systems often end up in an impedance specification, where the relation between source converter output impedance  $Z_i$  and total load converter input impedance  $Z_i$  is given by

$$|Z_o| << |Z_i| = 1 / \left| \sum_{k} (1/Z_{i,k}) \right| \tag{1.1}$$

where  $Z_{i,k}$  is the input impedance for converter k. This impedance criterion was first established in the paper "Input Filter Considerations in Design and Application of Switching Regulators" written by Middlebrook in 1976 [55].

Some of the more recent impedance specifications for stable operation of DC distribution systems instead specify a "forbidden" region in the complex frequency plane [20][21][28][70]. In [70], a forbidden region for the total loop gain is specified so that a minimum phase margin is ensured. This is further developed in [20][21] where the individual load converter impedance is specified so that the forbidden region is avoided by applying

$$\operatorname{Re}\left(\frac{Z_o}{Z_{i,k}}\right) < -\frac{1}{2} \cdot \frac{P_{load,k}}{P_{source}} \tag{1.2}$$

and

$$-90^{\circ} - \Phi_k < \left( \angle Z_o - \angle Z_{i,k} \right) < 90^{\circ} + \Phi_k \tag{1.3}$$

where

$$\Phi_k = \arcsin \left| \frac{1}{2} \cdot \frac{Z_{i,k}}{Z_o} \cdot \frac{P_{load,k}}{P_{source}} \right|$$

(1.4)

The results obtained in [20][21] are applied for the power supply of a Pentium processor in [71]. The power system of the investigated PC provides the voltage levels 3.3 V, 5 V and 12 V. The interactions between source and

load are found to be strong but no instability occurs. However, it is found that conditional stability problems might occur. It is stated that conditional stability problems cannot be solved by the application of the impedance criterion. According to [71], there are two possible solutions to check for conditional stability. The first is to derive the system transfer function with different loads, which is generally very complicated. The second is to include gain information in the impedance criterion, giving a set of impedance curves for the source converter output impedance. There are also two methods reducing the risk for occurrence of conditional stability. The first is to increase the source converter DC side capacitance. The second is to apply a current feedback loop. The work in [20][21] together with the stability margin monitoring method presented in [22][23][24][50] is concluded in [25].

In the paper [65], the relationship between stability and DC bus capacitance is studied. Also fault propagation is investigated. The main objective of the investigation is to minimise the DC bus capacitance.

In [28], large DC power systems for space applications are investigated. Here, equation (1.1) is used for small-signal stability analysis. It is also pointed out that large-signal or transient stability issues are of great concern. The methods suggested for large-signal analysis are computer analysis involving Bode plots, Nyquist curves and transient responses. Also, hardware testing, both for validation and model development, are used in the stability analysis.

Input filter design is discussed in [27]. Here, all the DC-DC converters are equipped with an input filter. Initially, the effect of the input filter on the DC-DC converter transfer function is investigated. Then, the extra element theorem [56] is used to investigate the effect caused by the impedance seen from the filter input terminals. This impedance is divided into two parts: the source (series) impedance and the cumulative (shunt) impedance, i.e. the collective regulator input impedance resulting from the input filters of the other power modules. If

$$\begin{aligned} |Z_s| &< |Z_n| \\ |Z_s| &< |Z_d| \end{aligned} \tag{1.5}$$

hold, where  $Z_s$  is the filter output impedance,  $Z_n$  and  $Z_d$  are the DC-DC converter input impedances with the output nulled and shorted, respectively, then the DC-DC converter transfer function is in principle unaltered by the input filter [27]. Furthermore, this means that the negative impedance

resulting from a constant power load is decoupled from the DC distribution bus. It is found that if several DC-DC converters, equipped with filters designed from this rule are connected to a common DC distribution bus, then the cumulative impedance is positive and decrease as the number of power modules increase. This means that the stability margin increases as the number of connected power modules increases.

In [51], power buffering is utilised to enhance stability of a DC distributed power system during transients. This is achieved by reducing the loop gain, and consequently, the negative incremental input impedance of the converters so that the sum of the source output impedance and the negative incremental input impedance is positive. This yields a stable system. Another possibility is also discussed in [51], where the power buffer is controlled to a certain input impedance during the transients.

#### Large-signal stability

Large-signal stability is treated in [2], where the distributed power system is formed by one single DC source with several load converters connected. Each load converter is equipped with an input *LC*-filter. The *LC*-filters are modeled as ideal except for a resistor *R* connected in series with the inductor. The large-signal stability constraints are expressed as boundaries on *R*. The upper limit for *R* is formed by application of the equilibrium point condition, i.e. by investigation of the maximum *R* yielding an intersection between the source and the load characteristics. According to [2], this gives

$$R < \frac{1}{4} \cdot \frac{V_{dc}^2}{P_o} \tag{1.6}$$

where  $V_{dc}$  is the DC source voltage and  $P_o$  is the load converter output power. The lower limit for R is found from the mixed potential criterion. In [2], lower limits on R are established for the cases with one, two and n load converters connected to a single DC source. However, computational problems appear for larger systems. Therefore, approximations are used in the case of multiple constant power loads. In the case of n constant power loads it is also assumed that these are equal in terms of filter component values and output power. For this case, an approximate lower bound is given by [2]

$$R > \sqrt{\frac{L}{C}}\sqrt{2n^2 - n} \tag{1.7}$$

For high n, the resistance R has to be high, which implies high power dissipation. In [2], it is found that the approximation of the lower bound for R gives an error between the approximated maximum singular value and the exact approaching 11% as n increases.

#### Robustness against parameter uncertainty

In [47], DC power system stability is investigated with focus on robustness against parameter uncertainty. Robust control theories are applied to DC power systems. According to [47], this is done to cope with the sensitivity to parameter and load variation resulting in DC power systems prone to instability. The stability robustness is investigated by computing the multivariable stability margin,  $k_m$ , and the structured singular value,  $\mu$ . Calculating these quantities exactly is cumbersome. Therefore, different approximation methods are investigated in [47].

The inherent instability of DC distribution systems originates from the fact that constant power loads appear as negative resistances to the regulators (source converters). The equivalent resistance seen from the regulator is [47]

$$R_{eq} = \frac{\partial v}{\partial i} = -\frac{v_{bus}^2}{P} \tag{1.8}$$

In [47], Middlebrook's Criterion [55] is regarded as the normal way to handle this problem, i.e. to use an isolation concept. Two problems arise from using Middlebrook's Criterion according to [47]. Firstly, parameter variations are not covered by the criterion and, secondly, it is intended for a two-port system. For the multiloop case considered in [47], a multiple input multiple output (MIMO) system should instead be investigated, which is not covered by Middlebrook's Criterion. In [47], expressing the electrical system as a MIMO system and then use the convex hull algorithm to calculate the stability margin is instead emphasised. This method is compared to other.

#### Converter modeling and control

Modeling and control issues for front-end three-phase boost rectifiers are discussed in [34]. An average model is developed and the stability with different loads connected across the DC side is investigated. Since an average model is used, a constant power load is modeled as a resistor with negative resistance. A non-linear controller, e.g. with feed forward of the load current, gives the best performance.

Modeling of a four-leg inverter, i.e. a neutral connected inverter, used in a PEBB based DC distributed power system, is investigated in [67]. The fourleg converter is presented in [78]. As in [34], the converter model in [67] is averaged. The converter input filter is of LC-type but with an RC-circuit connected across the capacitor to increase the shunt impedance at high frequencies. The impedance overlap between the filter input and output impedances is investigated, to fulfil equation (1.1). As expected, the interaction between input and output decreases as the damper resistance increases, i.e. the phase margin increases. In [67], a single source converter formed by a transistor front-end rectifier is considered. The DC side filter of the transistor rectifier is formed by a capacitor. Interaction between the rectifier output filter and the inverter input filter is also investigated. As in the previous case, the phase margin increases with increasing damper resistance. The same result is achieved by increasing the rectifier DC side capacitance. A more interesting solution exists according to [67]: if the controller bandwidth is reduced, the phase margin is increased. The interesting characteristic about this feature is that it can be tuned online, whereas the system has to be shut down for the other two methods.

In [75], two source converters connected to the same DC distribution bus are modeled simultaneously to investigate their interaction. Here, master/slave control is used and it is claimed that the same control strategy as in the single source case applies. However, it is stated that for long distribution distances with several sources and loads, other control strategies are probably required.

A switch model for large-signal modeling of distributed power systems is studied in [10]. It is found that the simulation with the proposed model shows good agreement with device level simulations. It is also found that the simulation time is reduced significantly.

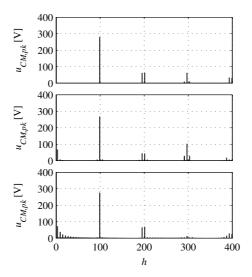

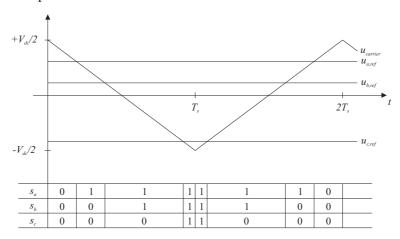

#### The zero-sequence current in distributed power systems

The fact that grid connected converters might give rise to high common mode currents is well known. This causes problems like bearing currents and insulation problems in electrical machines [48]. The common mode current results from the variations in voltage potential of the DC side supply rails, depending on the actual switch state. Consequently, the fundamental of the common mode current appears at switching frequency. The capacitive coupling between the supply rails and ground provides a path for the common mode current. Due to the capacitive nature of the current path, the common mode current magnitude increases with increasing switching frequency.

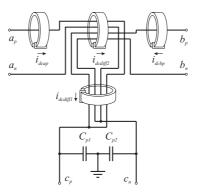

In [72], the supply rail voltage shift is analysed. First, the neutral to ground voltage variation for a diode rectifier/three-phase converter combination is investigated. The neutral is in this case the star-point of the load at the converter output, which for example could be the star-point of an electrical machine. It is shown that the neutral to ground voltage varies as the negative supply rail to neutral voltage for the rectifier with the converter switching superimposed. Both simulations and measurements are shown. Second, the same investigation is made for a controlled rectifier/converter combination, connected back-to-back. In this case the situation is even worse, at least in terms of high frequency content, since the negative supply rail to ground voltage variation is determined by the switching frequency of the rectifier. According to [72], one way to partly reduce the problem is to synchronise the modulation carriers of the rectifier and converter. Note that synchronisation should be avoided if modularity and autonomous control is desired. Also a third case is investigated, where two generators feed the same DC distribution bus via transistor rectifiers. In this case it is complicated to synchronise the switching patterns since it is likely that the generators operate at different load conditions. Furthermore, there might be extremely high zero-sequence currents if both generators are grounded to the same physical ground potential. Three methods are proposed to reduce the problems related with common mode currents. First the alleviation method, which includes installing electromagnetic interference (EMI) suppressing chokes, filtering and the use of soft-switching techniques. The second method is referred to as a tolerant method, where EMI currents are allowed but shielding is used in the motor to reduce the bearing currents and insulation stress. The third method addresses new converter topologies, where the four-leg VSC [67][78] is mentioned as an example. In [1], high impedance grounding is investigated to manage problems associated with neutral voltage shift.

In [74], two transistor rectifiers are connected to the same generator (or equivalently AC power system) and the rectifiers feed the same DC distribution bus. It is found that in the average simulation model, in *dq*-coordinates (Appendix B), the zero-sequence current does not appear. Instead, a *dq0* simulation model has to be adopted. In this simulation model, a high zero-sequence current appears. This problem is especially obvious when one of the rectifiers has the switch state 000 and the other 111 (Appendix A), which means that the DC distribution bus voltage is applied across the sum of the generator stator inductances for each phase. In [74], this is solved by adopting a modulation strategy where the zero voltage vectors, 000 and 111, are not utilised for the source rectifiers. In [77], a non-isolated system of one front-

end boost rectifier and one inverter is studied, from a converter modulation point of view. It is found that the proposed modulation scheme (interleaving) reduces the common mode current. In [75], ground loop interactions between two generators with a common ground, is also discussed.

An active filter for the DC bus is discussed in [73]. The active filter is formed by a transistor half-bridge and a DC link capacitor. The DC distribution bus side filter is purely inductive. The active filter is required to reduce AC current components injected from three-phase voltage source converters. These AC components result from negative-sequence or harmonic currents on the AC side of the three-phase converters. In [73], the switching frequency of the active filter is selected considerably higher than the one of the other converters of the DC distribution bus. The high switching frequency implies that interactions between the other converters can be suppressed, resulting in a stabilising effect. Consequently, the DC distribution bus impedance is tuned for best performance, thus, enhancing the stability. Note that the DC link capacitor voltage must be higher than the DC bus voltage, for the active filter.

#### **Electromagnetic interference**

In the paper [8], EMI problems related to switch mode power supplies connected to a DC distribution bus of long length are investigated. The load converter switching appears as a variable load, which generates reflections. The high rise and fall times generate high frequency signals radiated by the long power system conductors.

In [15], high frequency interaction in terms of disturbance propagation from DC distribution bus voltage to load converter output voltage is addressed. The problem is investigated from an analytical point of view and with simulations and experiments. The key result is that the switching frequencies of the converters should be as equal as possible to reduce load converter output oscillations.

#### Load flow and short circuit calculations

DC power system analysis in terms of load flow and short circuit calculations is investigated in [26]. Numerous source models (i.e. battery charger, rectifier and generator models) are given. Also connector models for load flow and short circuit calculations are investigated. Loads and branches are modeled. According to [26], the present standards (in the year 1996) are not complete and need further work.

In [3], the methods of the IEC draft standard "Calculation of short circuit-currents in dc auxiliary installations in power plants and substations" are investigated. The calculations are intended to determine appropriate fusing for the system. Four different loads are investigated in [3]. These are the (thyristor) converter in 50 or 60 Hz AC systems, stationary lead-acid batteries, smoothing capacitors and DC motors. The straightforward methods given in the standard are compared with EMTP simulations. The standard gives conservative estimates of the short circuit currents (25% overestimated). Also, the time constants estimated according to the standard are longer than the simulated. The standard was not applicable (in the year 1996) to large DC systems, such as railway traction systems, HVDC transmission systems and photovoltaic systems. According to [3], the reason is that the models developed for the standard do not cover the set of electrical parameters appearing for these systems.

A detailed model of an *RL*-fed bridge converter for use in a Newton-Raphson power flow program for industrial AC/DC power systems is derived in [68]. This is done since bridge models in simulation packages are generally only valid in, for example, HVDC applications where the commutation resistance is negligible. Two systems are simulated to demonstrate the accuracy, a coal mine electrical power system and a railway power system. It is found that the developed model yields a considerably higher accuracy for systems with high commutation resistance.

Due to the differences between load-flow studies of AC and DC power systems, a new algorithm and a DC simulation package are developed in [79]. The load flow algorithm is based on the Newton–Raphson method. DC load flow simulation models are developed for constant DC voltage power sources, batteries, AC/DC rectifiers, constant power load, constant current load, constant resistance load and time-varying load. Several case studies are simulated, and their voltage profiles are shown.

#### Grounding

According to [72], the best ground point is the mid-potential between the positive and negative conductors of the DC distribution bus. This means that the voltage shift is localised to each sub-system. In [17], grounding issues for drive systems in general are discussed. A thorough analysis is presented and it is found that high impedance grounding is expected to be used in the future as fault detection systems become more accurate and reliable.

#### 1.6 Specification of a distributed power system

This section contains the main requirements put on a future DC distributed power system. The requirements are based on the previously addressed objectives of this work.

- The power system should be well adapted to operate with present sources and loads, in terms of voltage and frequency. It should also provide a high degree of load and source power controllability.

- The system should be expandable, i.e. new load and source units should be possible to add, without altering units already connected.

- Communication between individual converters should be avoided since adding new units will be more complicated. Also, the system could suffer from reliability problems. On the other hand, communication at a low bandwidth is considered necessary for supervisory control. Therefore, single converters are allowed to rely on low bandwidth communication but should be able to operate as stand-alone units.

- The degree of personal safety should be equal to or better than in the present power system.

The basic requirements above lead to other, more technical, requirements. For example, high bandwidth source and load side current controllers should be adopted to provide load and source power controllability. Also, the high bandwidth of the current controllers together with the desire to not rely on (high-speed) communication result in a demand of long equivalent time constants of the DC bus voltage control. This also makes the DC bus robust against disturbances on converter load and source sides, for example, negative-sequence disturbances.

# **Chapter 2**

# **Existing DC power systems**

There are few systems utilising DC to transmit or distribute electrical power by means of DC today. Most power is transmitted and distributed by means of AC. The AC grid frequency is thereby the most essential control parameter and after that generation and distribution of reactive power to keep the voltage within specified limits. The stability of an AC power system is strongly dependent on its electro-magnetic characteristics and to a minor extent on power electronics because power systems expanded over wide areas during half a century when DC based high-voltage transmission was non-competitive. During the latter half of the last century, HVDC transmission became cost effective, especially as a way to connect asynchronous grids.

For the last decades, the feasibility of low-voltage self-commutated inverters connected to a common DC bus has increased, resulting in LVDC distribution systems feeding industrial adjustable-speed drives. Converters similar to the ones utilised in VSC based HVDC and in industrial drives are also used on-board electrical railway vehicles equipped with a common low-voltage, LV, or medium-voltage, MV, DC bus. The main aspect of those, so-called, traction drives is that the converters connected to the propulsion drives are normally handling the same power levels but split into parallel drives due to redundancy and/or rating reasons. There is usually also an auxiliary power converter connected to the common DC bus.

In this chapter, HVDC transmission systems are discussed since these are judged to have relevance as a background to the DC distributed power systems to be studied. First, the classical HVDC link is investigated. Second, the recently introduced VSC based HVDC concept, utilising insulated gate bipolar transistor (IGBT) technology, is discussed.

#### **2.1 HVDC**

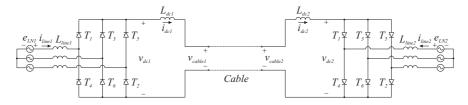

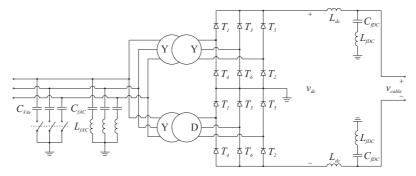

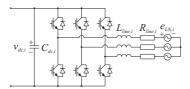

The principal structure of a classical HVDC transmission link consists of two three-phase thyristor converters connected via an intermediate inductive DC bus. However, in real installations, more complicated converter structures are utilised. Also, shunt reactive compensators and passive filters for suppression of harmonics are used. This is further discussed at the end of this section. Figure 2.1 shows a principal schematic of an HVDC transmission system.

Figure 2.1: Principal schematic of an HVDC power transmission system.

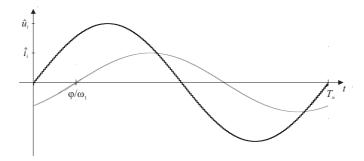

The leftmost converter in Figure 2.1 operates as rectifier and the rightmost as inverter. The average DC bus voltage for control angle  $\alpha$  is calculated from

$$V_{dc} = \frac{1}{T/6} \int_{T/6}^{2} \hat{e}_{LL} \cos(\omega_{1}t) dt = 6 \frac{\hat{e}_{LL}}{2\pi} \int_{-\pi/6+\alpha}^{\pi/6+\alpha} \cos(\omega_{1}t) d(\omega_{1}t) = \frac{3}{\pi} \hat{e}_{LL} \cos(\alpha) =$$

$$= \frac{3\sqrt{2}}{\pi} E_{LL} \cos(\alpha) = V_{dc0} \cos(\alpha)$$

(2.1)

where  $E_{LL}$  is the RMS grid voltage and  $V_{de0}$  is the average DC bus voltage in the case of a three-phase diode rectifier. Note that  $\alpha$  is defined as the angular displacement from the angle where the corresponding diode rectifier would have experienced a commutation, to the angle where it takes place. For a single-phase diode rectifier this angle coincides with the zero crossing of the phase voltage. For a three-phase rectifier this angle is where two line-to-line voltages  $e_{LL}$  intersect.

The rectifier operates at control angles between  $0^{\circ}$  and  $90^{\circ}$  and therefore its thyristors are connected so that the power is positive flowing into the DC cable. The inverter operates at control angles between  $90^{\circ}$  and  $180^{\circ}$  and therefore its thyristors are connected in such a way that the power is positive flowing out of the DC cable.

2.1 HVDC 23

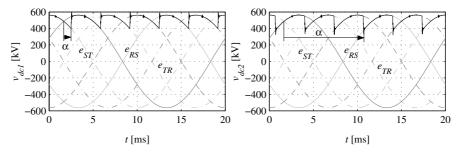

Figure 2.2 shows the line-to-line voltages, DC side voltage and control angle for the rectifier and inverter, respectively.

**Figure 2.2:** Line-to-line voltages, DC side voltage and control angles for the rectifier (*left*) and inverter (*right*) of an HVDC transmission system.

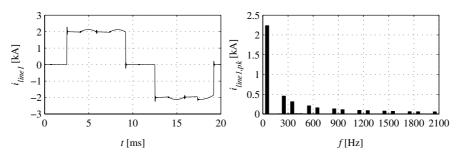

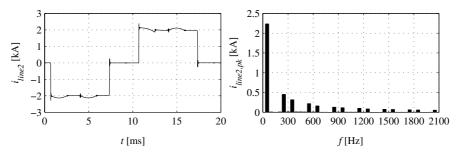

In Figure 2.3 and Figure 2.4, the *R*-phase line current and its spectrum are shown for the rectifier and inverter, respectively.

**Figure 2.3:** *R*-phase line current (*left*) and its spectrum (*right*) for the rectifier of an HVDC transmission system.

**Figure 2.4:** *R*-phase line current (*left*) and its spectrum (*right*) for the inverter of an HVDC transmission system.

The only major difference between the line currents in Figure 2.3 and Figure 2.4 is the phase lag of slightly less than 180° for currents flowing out from the AC grids. Consequently, the spectrums for rectifier and inverter operation are similar. The center of the line current pulse is displaced, by an angle equal to the control angle, relative to the line voltage. This means that the line current exhibits a phase lag  $\varphi = \alpha$ . Therefore, the active P and reactive power Q are

$$\begin{cases} P = \sqrt{3}E_{LL}I_{line,1}\cos(\alpha) \\ Q = \sqrt{3}E_{LL}I_{line,1}\sin(\alpha) \end{cases}$$

(2.2)

where  $E_{LL}$  and  $I_{line,1}$  are the RMS grid voltage and fundamental line current, respectively. Assuming a constant DC side current  $I_{dc}$ , the average DC power is given by

$$P = V_{dc}I_{dc} = \frac{3\sqrt{2}}{\pi}E_{LL}I_{dc}\cos(\alpha)$$

(2.3)

If the losses are neglected this implies that

$$P = \sqrt{3}E_{LL}I_{line,1}\cos(\alpha) = \frac{3\sqrt{2}}{\pi}E_{LL}I_{dc}\cos(\alpha) \iff I_{line,1} = \frac{\sqrt{6}}{\pi}I_{dc} \qquad (2.4)$$

The line currents are in principle square for a high DC inductance,  $L_{dcl}+L_{dc2}$ . For a square line current (60° conduction interval), the harmonics are

$$I_{line,k} = \frac{2\sqrt{2}}{k\pi} I_{dc} \sin\left(\frac{k\pi}{3}\right) \tag{2.5}$$

for k=1,5,7,11,13, etc. This is an important feature of three-phase diode and thyristor rectifiers with inductive DC links.

Classical HVDC utilises an inductive DC bus, as shown in Figure 2.1. Since the overhead lines are also inductive, the commutations take a finite time. This time is termed commutation overlap. Note that the commutation overlap affects the spectrum of a thyristor based current source converter (CSC), since the edges are slightly smoother due to the finite current derivatives. However, the reduction in harmonic content is negligible, at least for low order harmonics. Therefore, it is still a good approximation to assume that the amplitude of the harmonics fall of as 1/k where k is the harmonic order.

2.1 HVDC 25

#### **Practical HVDC installations**

Several modifications are made for practical HVDC installations, Figure 2.5, compared to the principal discussed previously.

Figure 2.5: Realistic schematic of an HVDC power station.

The main reasons for these modifications are related to the shape of the line currents, shown in Figure 2.3 and Figure 2.4. First, the centers of the current pulses are displaced compared to the centers of the sinusoidal pulses of the line voltages. This corresponds to a phase lag  $\varphi = \alpha$  and yields that reactive power is consumed. To circumvent this, switched shunt capacitor banks are installed on the AC line sides of the HVDC transmission. A switched capacitor bank is formed by several capacitors connected to the line through circuit breakers in such a way that the reactive power delivered can be varied in steps. This is required since the reactive power consumed by a thyristor rectifier is

$$Q = \sqrt{3}E_{LL}I_{line.1}\sin(\alpha) \tag{2.6}$$

which means that the reactive power consumed is dependent both on the RMS value of the line current fundamental and the control angle. The second issue regarding the AC line currents relates to their harmonic content. Two methods are used to reduce the harmonics. First, twelve pulse thyristor converter structures are used instead of the basic six-pulse thyristor converter discussed here. A twelve-pulse converter consists of two six-pulse bridges with the DC sides connected in series. The six-pulse bridges are connected to the same AC grid via a three-winding three-phase transformer. One of the thyristor converters is connected to a delta ( $\Delta$ ) winding and the other to a wye (Y) winding. This means that there is a 30° phase shift between the AC voltages feeding the two converters. This implies that there is a 30° phase shift between the currents fed to the converters also. Since the transformer

connected to the converters has a common primary side for both secondary windings, the line current on the primary side will exhibit its lowest harmonic around the 12<sup>th</sup> harmonic, i.e. the 11<sup>th</sup> and 13<sup>th</sup> order harmonics are the lowest appearing. The next pair of current harmonics appearing, are of the 23<sup>rd</sup> and 25<sup>th</sup> order. Passive shunt filters tuned to these specific harmonics are also included to further reduce the harmonic content of the AC line currents.

Traditional line-commutated, thyristor based HVDC transmission systems are difficult to build and operate cost-effectively with larger complexity than those two-terminal ones discussed above. The recently introduced VSC based HVDC transmission systems are more feasible to use as multi-terminal systems. By adopting VSCs, the problems associated with reactive power consumption and harmonics production are circumvented to a large extent.

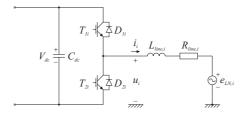

#### 2.2 VSC based HVDC

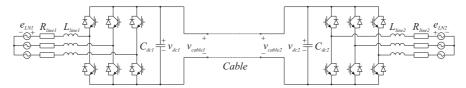

HVDC Light (trademark of ABB) [19] and HVDC Plus (trademark of Siemens) are basically extensions of the IGBT back-to-back converter, operating at higher power and voltage levels and with an intermediate cable between the converters. Even though this might seem as small step from a development point of view it has resulted in numerous new patents. The main reason is that the development of VSC based HVDC has forced the limits of power electronic converter technology. For example, IGBT valves withstanding more than 100 kV (through series connection) have been developed, light triggered gate or drive circuits have been developed, new cable technologies have emerged and so on. Of course, this introduction cannot provide all the details but instead focuses on the basic operation. Figure 2.6 shows a principal scheme of a VSC based HVDC transmission system.

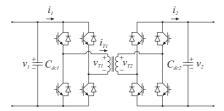

Figure 2.6: Basic VSC HVDC power transmission interconnection.

From Figure 2.6 it is clear that transistor based VSCs are used for this new type of HVDC transmission system. Three-phase VSCs inherently provide the possibility of bidirectional power flow. Both the sending and receiving end converters are current controlled on the AC side, since these sides are

2.2 VSC based HVDC 27

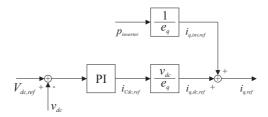

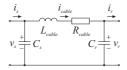

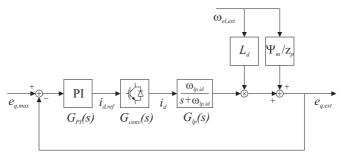

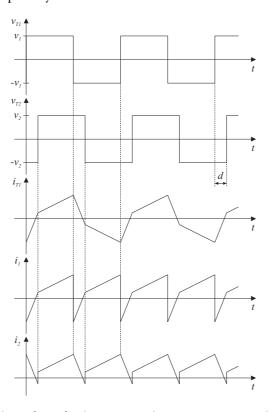

inductive. The current controllers operate in the *dq*-frame as described in Appendix B. The sending end converter is responsible for controlling the DC bus voltage. To enhance the dynamic performance of DC bus voltage control, information on the output power of the receiving end converter should be fed forward to the DC bus voltage controller. The DC bus voltage controller for the converter operated as rectifier is shown in Figure 2.7.

Figure 2.7: DC bus voltage controller for VSC based HVDC.

Figure 2.8 shows a more realistic VSC based HVDC scheme where additional AC side filters are included. This is required due to the fact that both sides of each converter are grounded and still third order injection modulation (Appendix A) is used, resulting in a zero-sequence voltage. To attenuate the current harmonics, shunt filters tuned to switching frequency are inserted between the converter AC side interface and the transformer. Figure 2.8 also shows high frequency filters (100 kHz and above) inserted at the DC side of the converter. These are required to avoid disturbances transmitted from the cable, which could interfere with broadcasting and other radio frequency equipment. Following the high frequency DC side filter, a common mode choke is inserted.

Figure 2.8: Realistic VSC based HVDC converter station.

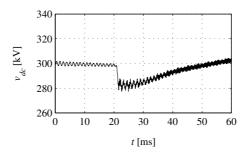

A VSC based HVDC transmission system consisting of two converters according to Figure 2.8 and a T-model of an HVDC cable (similar to the  $\pi$ -link shown in Figure 3.3) is investigated in simulations. The converters have a rated power of 330 MVA each and the nominal DC cable voltage is 300 kV

(±150 kV). The reactance of the inductive line filters equal 0.14 p.u. and the equivalent time constant of each converter including DC link capacitor is 2 ms. The rated power is the same as the one given in [19] and the other data are typical for an HVDC Light system. For the simulations, the rated line-toline voltage is set to 150 kV. The shunt filter is tuned to switching frequency (1950 Hz) so that the fundamental current component equals 0.01 p.u., which yields appropriate values for both  $L_{fl}$  and  $C_{fl}$ . The high frequency filter on the DC side is based on a characteristic frequency of 100 kHz and  $C_{\ell} = C_{\ell}/10$ . If the capacitance of  $C_{\ell}$  is higher, it will affect the characteristic frequency of the shunt harmonic filter. The mutual inductance of the common mode choke is set to the same value as  $L_p$  and the magnetic coupling factor is set to 0.99. The capacitance of  $C_{\beta}$  is set to  $C_{\beta}=2\cdot C_{p}$ . These component values most likely defer from the ones intended for the real installation. Also the DC bus voltage controller and the converter current controllers are not equal to the ones used in the real installation. Probably the current controllers used here have higher gain than the ones in the real installation.

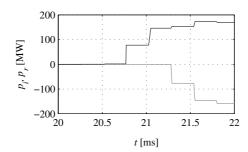

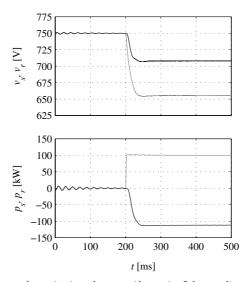

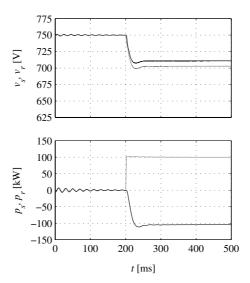

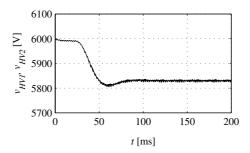

Figure 2.9 and Figure 2.10 show the converter power and DC bus voltage, respectively, for a time-domain simulation starting at no-load. The inverter receives an output power command equal to 165 MW (half rated power) at time t=20.0 ms. The current controller becomes aware of the increased power reference at time 20.25 ms, and calculates the desired AC side voltage reference which is applied one sample later, at time 20.5 ms. The current immediately starts to increase, but this is not noticed by the current controller before the next sample instant, at 20.75 ms. At this time, the current controller of the inverter sends a power reference to the converter acting as a rectifier, which increases its power demand. Due to the time required to establish a rectifier input power corresponding to the inverter output power, the DC bus voltage is somewhat reduced, see Figure 2.10.

**Figure 2.9:** Inverter AC side power (*black*) and rectifier AC side power (*grey*).

2.2 VSC based HVDC 29

Figure 2.10: Rectifier DC side voltage.

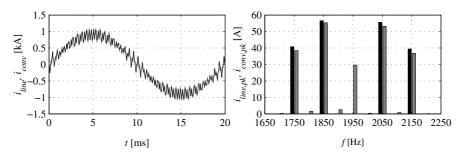

Figure 2.11 shows the line and converter currents for both the rectifier and inverter. It is seen that the currents contain a rather high ripple, originating from switching. Especially, the converter currents exhibit a high ripple at the power increase. These ripple currents are mainly zero-sequence switching frequency components. The ripple is not so pronounced in the line currents, due to the shunt harmonic filter. The high gain of the current controllers makes this problem worse. Figure 2.12 shows the stationary line and converter currents for the inverter, together with the corresponding harmonic spectrums in the vicinity of switching frequency. The shunt filter tuned to switching frequency attenuates this component effectively.

**Figure 2.11:** Line current (*black*) and converter current (*grey*) for the rectifier (*top*) and inverter (*bottom*) for a load power increase. The currents are positive flowing into the AC grids.

**Figure 2.12:** Line current (*black*) and converter current (*grey*) for the inverter (*left*) and line current spectrum (*black*) and converter current spectrum (*grey*) for the inverter at frequencies close to switching frequency (*right*).

In practical HVDC Light installations, resistors are connected in parallel to the inductors of the shunt filter. As a consequence, harmonics in a broader frequency spectrum are attenuated. Therefore, the harmonics around switching frequency in Figure 2.12 are attenuated more effectively in a real installation.

Feed forward of the output power of the inverter for DC bus voltage control is not used in real installations. Due to the low equivalent time constant of the converters, only low rate of change of the inverter output power is allowed.

The HVDC Light installations of comparably low rating, approximately 50 MW, are based on two-level converter technology (Figure 2.8). To achieve higher power ratings (300 MW), three-level VSCs are utilised [19].

Self-commutated two-level converters of the same type as used in the study of VSC based HVDC form, thus, a basis for the investigated multi-terminal DC distribution system. Some experience could also be found from industry and traction as mentioned in the introduction to this chapter.

# **Chapter 3**

# DC bus voltage control

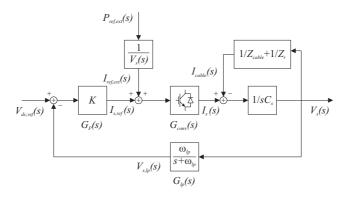

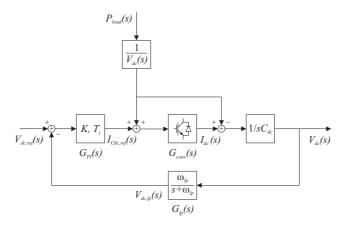

Two different DC bus voltage control schemes are investigated. One of the methods, referred to as the communication or master/slave method, strongly relies on fast communication between the source and load converters. The output power, with sign, is calculated for each of the converters. Information on total output power is fed forward to the converters. One of the converters, the master, is responsible for controlling the DC bus voltage. Feed forward of the total output power allows for high bandwidth DC bus voltage control. The DC bus voltage controller is, however, still required during transients and to compensate for losses in the DC power system. Due to the resistive voltage drop, a proportional-integral (PI) controller is adopted in order to avoid stationary DC bus voltage error.

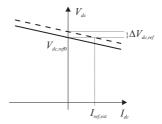

The other method is referred to as voltage droop control. Droop control does not require any communication at all between the converters. Instead, the DC bus voltage is measured at the source converter terminals. All the source converters contribute to balance the total power consumed by the loads and the losses of the DC power system. In common voltage droop control, the DC bus voltage decreases linearly as the output power for the converter increases, in order to give stable operation. This, of course, yields a stationary error in the DC bus voltage. Therefore, a restoration process to reduce the stationary DC bus voltage error is also discussed.

The chapter begins with an overview of the investigated system. Then the DC bus model used for the analysis is introduced. The controller structures are investigated and appropriate controller parameters are derived. The dynamic properties in the case of droop control are investigated. Last, the investigated DC bus voltage control schemes are compared in terms of load sharing.

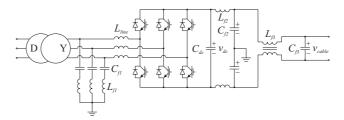

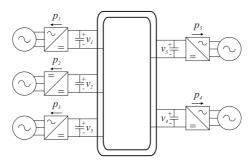

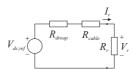

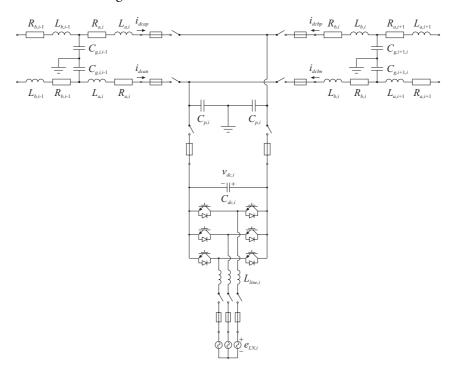

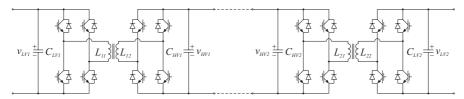

## 3.1 Investigated system

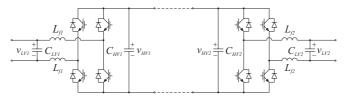

The investigated DC distribution network model consists of five converters: three are operated as sources and two are feeding power to loads. The converters are connected to galvanically separated AC power sources or loads. The sources and loads are modeled as three-phase grids. The grids are galvanically separated, i.e. without common reference, to avoid a low-impedance path for the zero-sequence and third order harmonic currents [72].

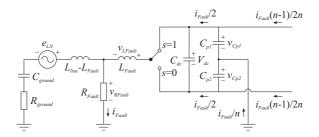

To investigate the transient response of the DC bus voltage controllers, the power references for the power fed to the loads are changed in steps. Therefore, the dynamics of the generators, wind turbines, etc. might interfere with the dynamics of the voltage control. This is further discussed in Chapter 4, where a distributed system operated only with wind power is investigated. Figure 3.1 shows a five-converter DC power system configuration, representative for the power systems considered in the analysis.

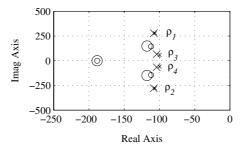

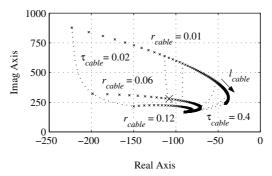

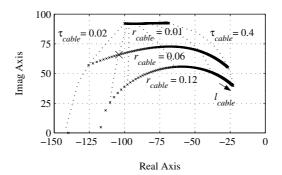

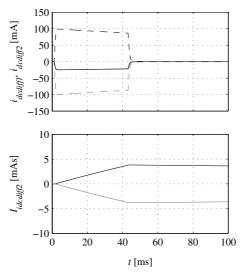

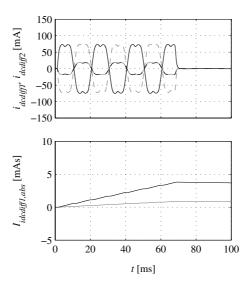

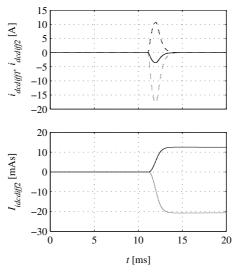

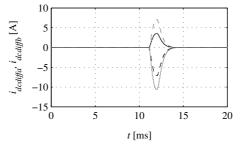

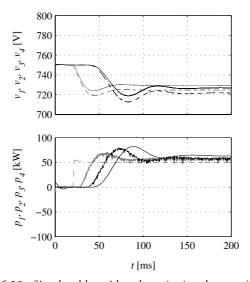

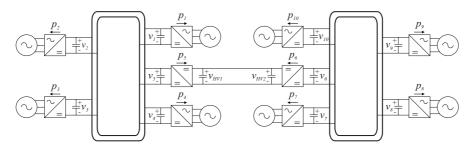

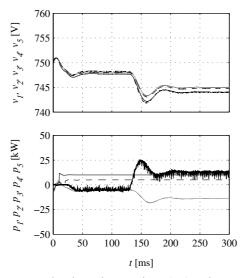

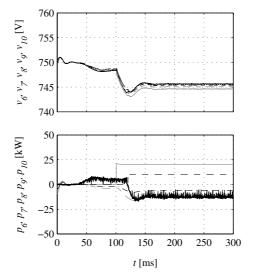

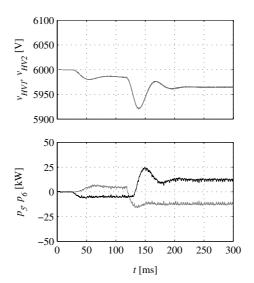

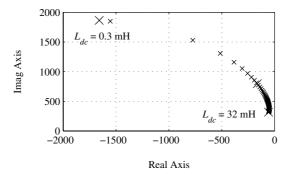

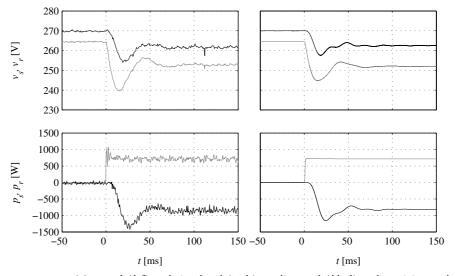

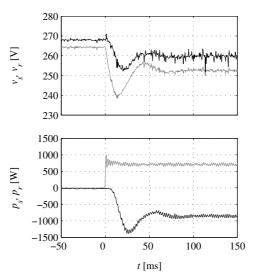

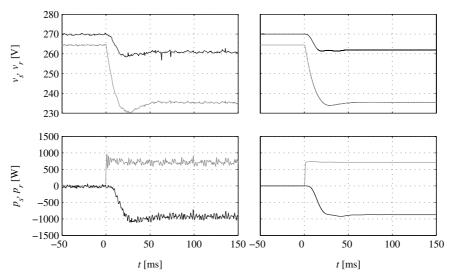

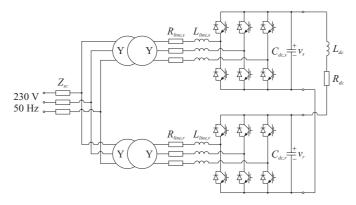

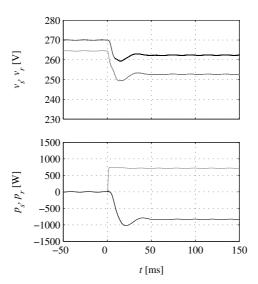

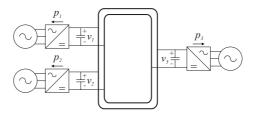

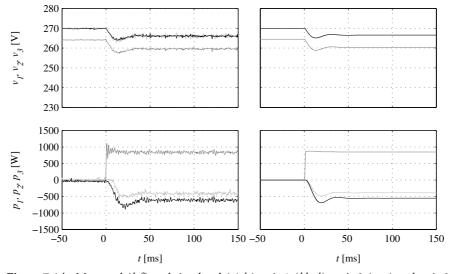

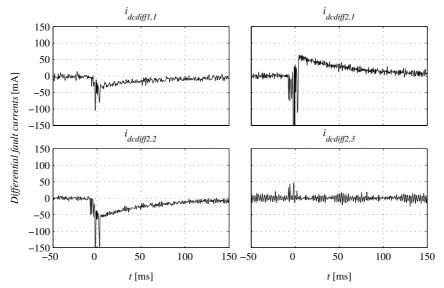

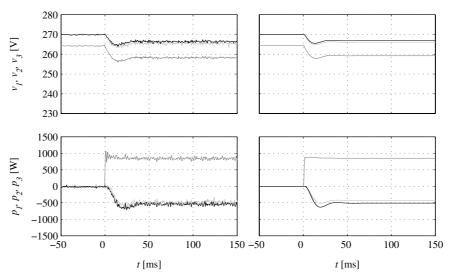

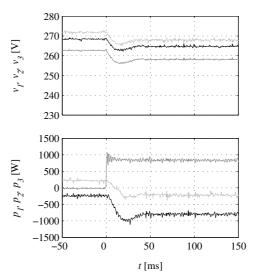

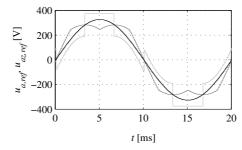

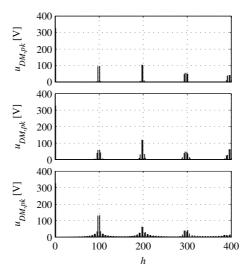

Figure 3.1: The investigated DC power system configuration.