Missouri University of Science and Technology Scholars' Mine

Electrical and Computer Engineering Faculty Research & Creative Works

**Electrical and Computer Engineering**

01 Oct 2000

# DC Power Bus Modeling using a Circuit Extraction Approach Based on a Mixed-Potential Integral Equation Formulation and an Iterative Equation Solver

Jun Fan Missouri University of Science and Technology, jfan@mst.edu

James L. Drewniak *Missouri University of Science and Technology*, drewniak@mst.edu

James L. Knighten

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

J. Fan et al., "DC Power Bus Modeling using a Circuit Extraction Approach Based on a Mixed-Potential Integral Equation Formulation and an Iterative Equation Solver," *Proceedings of the IEEE 9th Topical Meeting on Electrical Performance of Electronic Packaging (2000, Scottsdale, AZ)*, pp. 143-146, Institute of Electrical and Electronics Engineers (IEEE), Oct 2000.

The definitive version is available at https://doi.org/10.1109/EPEP.2000.895513

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

## DC Power Bus Modeling Using a Circuit Extraction Approach based on a Mixed-Potential Integral Equation Formulation and an Iterative Equation Solver

Jun Fan, James. L. Drewniak, and James L. Knighten\* Electromagnetic Compatibility Laboratory, University of Missouri-Rolla, Rolla, MO65409 Tel: 573-341-4969, Fax: 573-341-4532 <u>jfan@umr.edu</u>, drewniak@umr.edu \*NCR Corporation, 17095 Via del Campo, San Diego, CA 92127 Tel: 858-485-2537, Fax: 858-485-3788 Jim.Knighten@SanDiegoCA.NCR.COM

### Abstract

This paper presents a quick and simple approach to perform circuit simulations for an equivalent circuit extracted from a first principles formulation for DC power bus structures. Comparisons between the modeling and measurements demonstrate the application of this approach in DC power bus designs.

## Introduction

DC power bus modeling in multi-layer printed circuit board (PCB) or multi-chip module (MCM) substrates is a critical issue in high-speed digital circuit designs. A circuit extraction approach based on a mixed-potential integral equation formulation, denoted CEMPIE, has been developed and successfully applied in various power bus modeling [1], [2]. From a power bus structure; CEMPIE extracts an equivalent passive circuit from a first principles formulation. This circuit is exported to SPICE for circuit simulations. This approach is generally applicable for various power bus studies in the sense that all kinds of SPICE models of IC devices, transmission lines, sources, etc., can be included as lumped circuit models. However, for some simple frequency investigations, the approach is not very computationally efficient on both the simulation speed and the storage memory. Further, some commercial SPICE versions experience a convergence problem for the bias point and DC sweep simulations for a very large-scale {R, L, C} network. A simple approach to perform the swept-frequency  $|S_{21}|$  and input impedance simulations by directly solving the system matrix equation using an iterative method is presented in this paper. Some simple lumped circuit elements, such as decoupling capacitors, can be added to the extracted circuit by modifying the system equation. An example demonstrates the effectiveness of this approach.

#### Formulation

The CEMPIE formulation is similar to the formulation of classical scattering problems. An incident electric field is assumed. The ground plane, and the multi-layer medium in the DC power bus structure are assumed of infinite size, and incorporated into the calculation of the Green's functions. Then, the remaining conducting surfaces, including the planar power plane and vertical surfaces of vias, are replaced by induced surface currents and charges. By enforcing boundary conditions on these conducting surfaces for the vector sum of the incident and induced electric fields, an integral equation results. This equation is discretized and tested using a standard Method of Moments procedure. By further assuming the electric potential over each mesh cell is constant, a final system matrix equation is established as [1]

$[\mathbf{Y}][\boldsymbol{\varphi}] = -[\mathbf{I}^{\mathsf{e}}],$

## (1)

where  $[I^{e}]$  is the impressed node current vector;  $[\phi]$  is the node scalar-potential vector; and, [Y] is the system admittance matrix. An equivalent {L, C, R} circuit is extracted from the system admittance matrix [Y]. In the original CEMPIE approach, this extracted equivalent circuit is exported into SPICE where other circuit elements are included and various simulations are performed. The equivalent circuit is extracted in the fashion that they can reproduce the system admittance matrix in SPICE with minimum errors. In the approach presented in this paper, however, the equivalent circuit element values are not calculated. Rather, the system admittance matrix is transferred to the equation solver without changes, assuming it is reproduced with no error at all. Then, external lumped circuit elements, as well as excitations (sources), are added into the system admittance matrix.

Each lumped circuit element or source can be characterized using a simple element admittance matrix or/and a source vector. Most entries of the element admittance matrix and the source vector are zero, except at several special locations, which are related to the circuit nodes where the element or source

Authorized licensed use limited to: Missouri University of Science and Technology. Downloaded on June 1, 2009 at 14:03 from IEEE Xplore. Restrictions apply

is connected into the circuit model. Typical lumped circuit elements and sources encountered in DC power bus modeling and their corresponding element admittance matrices or/and source vectors are illustrated in Table 1. If one of the nodes is the common ground node, its corresponding row and column is eliminated. All element admittance matrices corresponding to all externally incorporated lumped circuit elements and sources should be added to the system admittance matrix obtained from the CEMPIE approach. Similarly, all source vectors sum up, forming the impressed node current vector. Then, the new system matrix equation becomes

$[\mathbf{Y}'][\boldsymbol{\varphi}'] = -[\mathbf{I}^{\bullet}'].$

(2)

Note that the number of total circuit nodes may increase after incorporating lumped circuit elements and sources.

|                              | Circuit elements                                                   | Element matrices and source vectors                                                                                                                                                                                                                        |

|------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-port admittance            | i Y j<br>e[]0                                                      | $i  j$ $i  \begin{bmatrix} Y & -Y \\ -Y & Y \end{bmatrix}$ $\begin{bmatrix} Y' \end{bmatrix}:  j  \begin{bmatrix} -Y & Y \\ -Y & Y \end{bmatrix}$                                                                                                          |

| 2-port admittance<br>network | $\begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix}$ | $[\mathbf{Y'}]: \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                        |

| Voltage source               | $i \xrightarrow{V_s} R_s j$                                        | $\begin{bmatrix} \mathbf{i} & \mathbf{j} \\ \mathbf{i} & \begin{bmatrix} y_{R_s} & -y_{R_s} \\ -y_{R_s} & y_{R_s} \end{bmatrix} \begin{bmatrix} \mathbf{I}^{\mathbf{e}} \mathbf{j} \end{bmatrix} \begin{bmatrix} -v_s \\ v_{s_s} \\ y_{s_s} \end{bmatrix}$ |

| Ideal current<br>source      | i I <sub>s</sub> j                                                 | $\begin{bmatrix} \mathbf{i} & I_s \\ I^{e'} \end{bmatrix}$                                                                                                                                                                                                 |

Table 1: Typical lumped circuit elements and corresponding element matrices and source vectors.

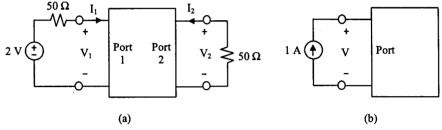

$|S_{21}|$  and input impedance are often used for DC power bus studies. They are easy to measure, and are good indications of power bus behavior in the frequency domain. Figure 1 illustrates the setup conditions of source and load for the  $|S_{21}|$  and input impedance simulations. In Figure 1(a), a 2-volt voltage source with a 50  $\Omega$  source impedance is added at Port 1, while the load at Port 2 is a 50  $\Omega$  resistor. Then, voltages at Ports 1 and 2 are

| $=\sqrt{50(a_1+b_1)},$ | (3) |

|------------------------|-----|

| $=\sqrt{50(a_1+b_1)},$ | (5) |

$$V_2 = \sqrt{50}b_2,\tag{4}$$

where the system impedance is assumed as 50  $\Omega$ ;  $a_1$  is the incident wave at Port 1, and,  $b_1$  and  $b_2$  are reflection waves at Ports 1 and 2, respectively. Since Port 2 has a matched impedance, its incident wave is zero, namely,  $a_2 = 0$ . Therefore, according to the definition of scattering parameters [3],

$$S_{21} = \left(\frac{b_2}{a_1}\right)_{a_2=0} = \frac{b_2}{a_1}$$

(5)

The current flowing into Port 1 can be expressed as

$$I_1 = (a_1 - b_1) / \sqrt{50}, \tag{6}$$

$$I_1 = (2 - V_1)/50.$$

(7)

Substituting (7) into (6) results:

$$V_1 = 2 - \sqrt{50}(a_1 - b_1).$$

Based on (3) and (8),  $a_1$  can be derived as

$a_1 = \frac{1}{\sqrt{50}}.$

Substituting (4) and (9) into (5)

Substituting (4) and (9) into (5),  $S_{21} = V_2$

results. Therefore, the voltage at Port 2, which is the potential of the output node, is the desired S  $_{21}$ , under the source and load conditions specified in Figure 1(a). The input impedance is a one-port parameter. As shown in Figure 1(b), an ideal unit current source is added at a port. The voltage value at the same port is the desired input impedance looking into that port.

Figure 1: Setups of (a)  $|S_{21}|$ , and (b) input impedance simulations.

## **Iterative Equation Solver**

The new system equation (2) is established after incorporating lumped circuit elements and specifying source and load conditions. This linear equation can then be solved for unknown node potentials. There are two different classes of methods: direct and iterative methods. Direct methods are usually Gaussian elimination type of methods, such as LU, QR, and Cholesky factorizations [4]. They usually require large storage memory. The algorithms involve access to the individual matrix elements. By contrast, iterative methods obtain an approximate solution through a finite number of steps. The system matrix is involved only indirectly, and no full factorization has to be stored. Therefore much larger scale systems can be handled [5]. However, iterative methods are not universally applicable. Their performance depends on system matrix properties like diagonal dominance or the existence of an underlying differential operator.

DC power bus structures usually result in very large-scale system matrix equations using the CEMPIE formulation, since the whole power plane has to be discretized into small triangular cells. An iterative method, the biconjugate gradient stabilized method, is used to solve the system equation (2), instead of direct methods. The computational complexity of the iterative method is proportional to the number of nonzero elements in the system matrix, though it also depends linearly on the row and column sizes. To improve the computational efficiency, the system matrix [Y'] is sparsed. The non-diagonal entries in a row are compared with the diagonal element in that row, which is the dominant element since it represents the field reaction within a mesh cell. If the magnitudes of the non-diagonal entries are 10<sup>-8</sup> times smaller than the magnitude of the dominant element, the entries are set to be zero.

The convergence rate of iterative methods depends on the system matrix properties. A preconditioner can be used to transform a linear system equation with unsuitable matrix properties into one that has the same solution with the original equation, but has more favorable matrix properties [5]. The incomplete LU factorization is used as a preconditioner in this study. It is found that the preconditioner dramatically increases the convergence speed, although it incurs some initial setup cost as well as the application cost in each step, for the DC power bus modeling problems investigated in this study.

#### Results

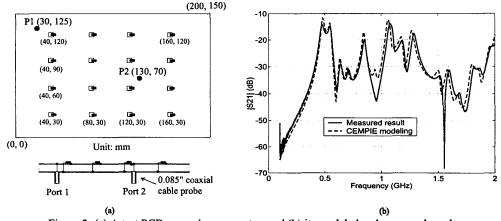

This modeling approach was used to model some PCB DC power bus structures. Figure 2(a) shows an example of a two-layer PCB with two planes representing the power and ground, respectively. Sixteen surface mount technology (SMT) decoupling capacitors were uniformly distributed over the board. One end of every capacitor was directly connected to the top layer, while the other end to the bottom layer through a 24 mil diameter via. The 63 mil dielectric material was FR-4 with a dielectric constant of  $\varepsilon_r = 4.7$ , and loss

(9)

tangent of tan  $\delta = 0.02$ .  $|S_{21}|$  between two test ports was investigated both experimentally and using the modeling approach. A network analyzer was used with a full two-port calibration. The reference planes were further rotated to the SMA terminals looking into the power bus. The individual capacitor values were 0.01  $\mu$ F, with nominal parasitic inductance and resistance values of 820 pH and 120 m $\Omega$ . The power bus with the capacitor vias, but no capacitors, was formulated using the CEMPIE approach. The decoupling capacitors were then added into the CEMPIE extracted circuit as series RLC circuits. The modeled and measured results are compared in Figure 2(b). They agree favorably from 100 MHz to 2 GHz.

Figure 2: (a) A test PCB power bus geometry; and (b) its modeled and measured results.

Totally 3549 mesh edges and 2422 mesh cells were used in the CEMPIE extraction approach. It took approximately 38 minutes to obtain the system equation (1), and approximately 5 hours 40 minutes to complete the  $|S_{21}|$  simulation with 201 frequency points from 100 MHz to 2 GHz using the iterative equation solver, both in a Pentium III PC with a 450 MHz CPU and 512 MB memory. This was a big improvement compared with a direct method. It took approximately 32 hours for the same problem to be solved using an LU factorization on the same computer. Other small-scale power bus modeling examples show that this approach is approximately 20-30 times faster than the full CEMPIE approach.

## Conclusion

The approach presented in this paper to perform circuit simulations by solving the system equation using an iterative method is very suitable and computationally efficient for frequency-domain DC power bus modeling. Agreements between modeling and measurements demonstrate its effectiveness.

## References

- [1] J. Fan, H. Shi, A. Orlandi, J. L. Knighten, and J. L. Drewniak, "Modeling DC power-bus structures with vertical discontinuities using a circuit extraction approach based on a mixed-potential integral equation formulation," Submitted for publication to the *IEEE Transactions on Components*, *Packaging, and Manufacturing Technology: Part B - Advanced Packaging.*

- [2] H. Shi, Study of Printed Circuit Board Power-Bus Design with a Circuit Extraction Technique Based on a Quasi-Static MPIE/MOM Formulation, Ph.D thesis, Department of Electrical and Computer Engineering, University of Missouri-Rolla, 1997.

- [3] D. M. Pozar, *Microwave Engineering*, Addison Wesley, 1990.

- [4] Using MATLAB, version 5, The Mathworks Inc., 1999.

- [5] R. Barrett, M. Berry, T. F. Chan, J. Demmel, J. M. Donato, J. Dongarra, V. Eijkhout, R. P. C. Romine, and H. Van der Vorst, *Templates for the Solution of Linear Systems: Building Blocks for Iterative Methods*, Society for Industrial and Applied Mathematics, 1994.