# DC Voltage Ratio Control Strategy for Multilevel Cascaded Converters Fed with a Single DC Source

S. Vazquez, *Member*, *IEEE*, J. I. Leon, *Member*, *IEEE*, L. G. Franquelo, *Fellow Member*, *IEEE*, J. J. Padilla and J. M. Carrasco, *Member*, *IEEE*

Abstract-Recently, a multilevel cascaded converter fed with a single dc source has been presented. An analysis of the steady state working limits of this type of converter is presented in this paper. Limits of the maximum output voltage and the minimum and maximum loading conditions for a stable operation of the converter are addressed. In this paper, a way to achieve any dc voltage ratio (inside the stable operation area of the converter) between the H-bridges of the single dc source cascaded H-bridge converter is presented. The proposed dc voltage ratio control is based on a time domain modulation strategy that avoids the use of the inappropriate states to achieve the dc voltage ratio control. The proposed technique is a feed-forward modulation technique which takes into account the actual dc voltage of each H-bridge of the converter leading to output waveforms with low distortion. In this way, the dc voltage of the floating H-bridge can be controlled whilst the output voltage has low distortion independently of the desired dc voltage ratio. Experimental results from a twocell cascaded converter are presented in order to validate the proposed dc voltage ratio control strategy and the introduced concepts.

Index Terms—Multilevel systems, Modulation, Voltage Control.

#### I. INTRODUCTION

ULTILEVEL cascaded H-bridge converters (CHB) have been a focus of research since they were first presented in 1975 [1]. This interest is due to their advantages compared to other multilevel converter topologies in terms of minimum number of devices, modularity, reliability and fault tolerance. CHB have been successfully applied in applications where a high number of levels are required [2]-[5]. A multilevel CHB is composed by a series connection of H-bridges, also called cells. The dc link voltage ratio of a CHB is defined as the relation between the dc link voltages of the cells of the converter. Note that, a converter with dc voltage ratio k:1 in a two-cell CHB means that  $V_{C1}=kV_{C2}$ . Depending on the number of cells in the power converter and the dc voltage ratio between the cells, the number of possible output voltage levels changes. In previous works, dc voltage ratios 1:1, 2:1 and 3:1 have been studied and the number of levels achieved by these power converter topologies has been determined [6].

Recently, multilevel CHB fed using only a single dc source have been introduced for applications such as renewable

Manuscript received October 9, 2008. Accepted for publication March 2, 2009. Copyright © 2009 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org. S. Vazquez, J. I. Leon, L. G. Franquelo, J. J. Padilla and J. M. Carrasco are with the Electronic Engineering Department, University of Seville (Spain), (e-mail: svazquez@gte.esi.us.es).

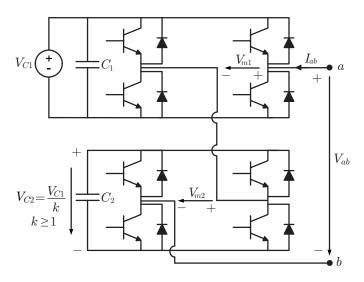

energy and motor drives [7]–[10]. This power converter is called in this paper SDC-CHB and, as an example, the two-cell SDC-CHB is shown in Fig. 1. The upper H-bridge dc voltage is constant and the floating dc voltage  $V_{C2}$  has to be controlled by the switching of the power converter. The dc voltage ratio of the two-cell SDC-CHB shown in Fig. 1 is k:1 fulfilling that

$$V_{C2} = \frac{V_{C1}}{k}. (1)$$

Selective harmonic elimination methods have been usually applied to the two-cell SDC-CHB in order to achieve good low harmonic distortion response [7]–[9]. On the other hand, a hybrid modulation technique has been used in [10]. However, in all the previous works, only dc voltage ratios equal to 2:1 were used [7]-[10]. In front of this fact, the dc voltage control strategy proposed in this paper can achieve any dc voltage ratio if the stable operation is possible (see section V). In addition, previous modulation techniques do not take into account errors in the dc voltages of the CHB and this fact leads to distorted output voltage and current waveforms. This distortion can be attenuated using a modulation technique based on the feed-forward concept [11]-[14]. This paper uses the feed-forward modulation technique applied to CHB (and called 1D-FFSVM) introduced in [15] which can be applied to the SDC-CHB.

Fig. 1. Two-cell single-phase CHB fed using only an external dc source (SDC-CHB). Voltage  $V_{C2}$  is a floating voltage.

The structure of this paper is the following: In section II a brief introduction of the state of the art of the modulation techniques for the SDC-CHB is addressed. In section III, the 1D-FFSVM technique is summarized. This technique is applied in section IV where the proposed voltage control technique depending on the desired voltage ratio k:1 is described. In order to complete the study and to determine the limits of the proposed dc voltage control strategy, an analysis of the maximum output phase voltage and the possible loading conditions that achieve a stable operation is presented in section V. The experimental results of the proposed modulation technique including the dc voltage ratio control are shown in section VI. Finally, in section VII the conclusions of the proposed work are addressed.

## II. MODULATION TECHNIQUES AND DC VOLTAGE RATIO CONTROL FOR MULTILEVEL CHB AND SDC-CHB

Different multilevel modulation techniques for CHB have been presented in the literature. Many of these techniques have been extended from classic pulse width modulation (PWM) [16], [17], space-vector modulation (SVM) methods [18]–[21] and selective harmonic elimination (SHE) techniques [22]–[25]. Related with the SDC-CHB topology, previous works have used SHE techniques with a reduced number of switching angles [7], [8] or hybrid modulation techniques reducing the commutations of the fixed dc voltage H-bridge of the converter [10]. All these modulation techniques achieve good results obtaining good harmonic spectrum results and controlling the floating dc voltage.

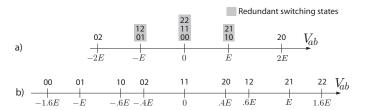

In this work, a particularization of the time domain modulation technique 1D-FFSVM is applied. This time domain modulation can be considered as a SVM technique because is based on the generation of the reference voltage determined by the controller as an average of the discrete output voltages that can be achieved by the power converter. As in the SVM techniques, the discrete switching states of a power converter are placed in a control region reducing the modulation strategy to a geometrical problem. The control region of a singlephase CHB converter can be represented as a 1D control region using the phase voltage  $V_{ab}$  as the control variable [21], [26]. The output of the H-bridge<sub>i</sub> can take any of three different output voltages  $(-V_{Ci}, 0, V_{Ci})$ , defined as H-bridge states 0, 1 and 2 respectively. In the single-phase two-cell SDC-CHB, up to nine output voltages can be achieved and they are summarized in Table I where has been imposed that  $V_{C1}$ =E. Using Table I it is possible to represent the control region of the single-phase two-cell SDC-CHB for any value of the floating dc voltage  $V_{C2}$ . The control region is plotted mapping the states created by the variation in the dc voltages of the cells [15]. For instance, the control region of the twocell SDC-CHB with dc voltage ratios 1:1 ( $V_{C1}=V_{C2}=E$ ) and 1.66:1  $(V_{C1}=E,V_{C2}=0.6E)$  are represented in Fig. 2. In the control region representation, switching state XY means that the upper H-bridge has state X and the lower H-bridge has state Y.

From Fig. 2, if the dc voltage ratio is 1:1 the presence of redundant switching vectors is clear [21]. The shadowed

TABLE I

TWO-CELL SDC-CHB SWITCHING STATES.

| Upper H-bridge | Lower H-bridge | Phase Voltage |

|----------------|----------------|---------------|

| State          | State          | $(V_{ab})$    |

| 0              | 0              | $-E-V_{C2}$   |

| 0              | 1              | -E            |

| 1              | 0              | $-V_{C2}$     |

| 0              | 2              | $-E + V_{C2}$ |

| 1              | 1              | 0             |

| 2              | 0              | $E-V_{C2}$    |

| 1              | 2              | $V_{C2}$      |

| 2              | 1              | E             |

| 2              | 2              | $E + V_{C2}$  |

Fig. 2. 1D Control region of the single-phase two-cell SDC-CHB. From top to bottom: a)  $V_{C1}$ = $V_{C2}$ =E (ratio 1:1) b)  $V_{C1}$ =E,  $V_{C2}$ =0.6E (ratio 1.66:1).

switching states are redundant because they achieve the same voltage  $V_{ab}$  and therefore are located in the same position of the control region. For instance, considering dc voltage ratio 1:1 two different switching states (10 and 21) achieve  $V_{ab}=E$ . This redundancy property can be used to control the dc voltages of the power converter as is shown in [21] for different multilevel converter topologies.

The control of the dc voltage ratio in the SDC-CHB using the redundancy property has been introduced in previous works achieving dc voltage ratio 2:1 [7]–[10]. However, in this work, any dc voltage ratio is considered if the stable operation can be achieved (see section V). The redundancy property is lost when the dc voltage ratio is different of 1:1 or 2:1. Therefore, the redundancy can not be used as a general tool to achieve any dc voltage ratio control of the SDC-CHB. In order to solve this problem, the 1D-FFSVM technique is applied to the SDC-CHB.

### III. 1D-FFSVM TECHNIQUE FOR MULTILEVEL CHB

The concept of the feed-forward modulation introduced in [11] was used to develop a simple feed-forward modulation called 1D-FFSVM for the single-phase CHB. A feed-forward modulation technique is based on the calculation of the control region of the power converter taking into account the actual dc voltages of the capacitors of the power converter. The calculations of the switching sequence and the switching times are made using this control region determined online. Using the 1D-FFSVM technique, any voltage unbalance does not affect the output voltage of the converter because the actual dc voltages  $V_{C1}$  and  $V_{C2}$  are taken into account in the modulation process. In this way, if a dc voltage unbalance is present, the undesirable distortion in the output voltage and current waveforms is reduced. In this paper, as the desired dc voltage ratios could be non integer numbers, the 1D-FFSVM technique

is very suitable to be applied to the two-cell SDC-CHB. In this way, the desired output sinusoidal waveforms with low distortion are generated for any value of the desired dc voltage ratio. The 1D-FFSVM technique has been used in this paper. In order to make the paper self-contained and to improve the clarity of the text, a summary of the 1D-FFSVM technique is presented.

The 1D-FFSVM technique determines several factors  $k_1, k_2$  and  $k_3$  depending on the actual dc voltage values of the CHB as is summarized in Table II. In this table, factor  $\rho$  is defined as

$$\rho = \frac{1}{V_{C1} + V_{C2}}. (2)$$

In [15], the dc voltage ratio control of a two-cell singlephase CHB is studied in detail. Different cases have to be studied depending on the actual values of the dc voltages and the sign of the phase current  $I_{ab}$ . The effect of each switching state on the dc voltages is well known and is applied to multilevel converters along with the concept of the redundant vectors in the SVM strategies to control the dc voltages of the dc link in different multilevel converter topologies. In the 1D control regions of the 1D-FFSVM technique with dc voltage ratio control, the switching states of the converter that lead to increase the voltage unbalance have been eliminated and therefore are reduced versions of the general 1D control regions. Table III is used to define all the cases when the desired dc voltage ratio is 1:1 (cases from A to H). In addition, in Table III the desired evolution of the dc voltages of the CHB is shown in the fourth column. This information is useful when the dc voltage ratio k:1 (k different of 1 is studied).

For each case (from A to H), reduced versions of the 1D control regions similar to those presented in Fig. 2 have to be used to determine the switching sequence and the switching times. Once the 1D control region to be considered is known, the 1D-FFSVM technique with dc voltage ratio control carries out a normalization of the phase voltage  $V_{ab}$  obtaining factor a as

TABLE II  $k_i$  FACTORS DEFINITIONS [15]

| DC Voltage                    | $k_i$ factors                 |

|-------------------------------|-------------------------------|

| Condition                     | expression                    |

|                               | $k_1 = \rho(V_{C1} - V_{C2})$ |

| $V_{C2} < V_{C1} \le 2V_{C2}$ | $k_2 = \rho V_{C2}$           |

|                               | $k_3 = \rho V_{C1}$           |

|                               | $k_1 = \rho V_{C2}$           |

| $V_{C1} > 2V_{C2}$            | $k_2 = \rho(V_{C1} - V_{C2})$ |

|                               | $k_3 = \rho V_{C1}$           |

|                               | $k_1 = \rho(V_{C2} - V_{C1})$ |

| $V_{C1} < V_{C2} \le 2V_{C1}$ | $k_2 = \rho V_{C1}$           |

|                               | $k_3 = \rho V_{C2}$           |

|                               | $k_1 = \rho V_{C1}$           |

| $V_{C2} > 2V_{C1}$            | $k_2 = \rho(V_{C2} - V_{C1})$ |

|                               | $k_3 = \rho V_{C2}$           |

TABLE III

CASES OF STUDY OF THE DC VOLTAGE RATIO CONTROL STRATEGY WITH

DC VOLTAGE RATIO 1:1 [15]

| Phase          | Actual                        | dc Voltage | Desired dc                |

|----------------|-------------------------------|------------|---------------------------|

| Current        | dc Voltage                    | Ratio 1:1  | Voltage Condition         |

| Condition      | Condition                     | Case       | $V_{C1}^*, V_{C2}^*$      |

| $I_{ab} > 0$   | $V_{C2} < V_{C1} \le 2V_{C2}$ | Case A     | $\downarrow$ , $\uparrow$ |

|                | $V_{C1} > 2V_{C2}$            | Case B     | $\downarrow$ , $\uparrow$ |

|                | $V_{C1} < V_{C2} \le 2V_{C1}$ | Case C     | $\uparrow$ , $\downarrow$ |

|                | $V_{C2} > 2V_{C1}$            | Case D     | $\uparrow$ , $\downarrow$ |

| $I_{ab} \le 0$ | $V_{C2} < V_{C1} \le 2V_{C2}$ | Case E     | $\downarrow$ , $\uparrow$ |

|                | $V_{C1} > 2V_{C2}$            | Case F     | $\downarrow$ , $\uparrow$ |

|                | $V_{C1} < V_{C2} \le 2V_{C1}$ | Case G     | $\uparrow$ , $\downarrow$ |

|                | $V_{C2} > 2V_{C1}$            | Case H     | $\uparrow$ , $\downarrow$ |

TABLE IV SWITCHING SEQUENCE AND SWITCHING TIMES FOR CASE A [15]

| Condition           | Switching | Switching Times                 |

|---------------------|-----------|---------------------------------|

|                     | Sequence  | $(t_2=1-t_1)$                   |

| $-k_3 > a \ge -1$   | 01-00     | $t_1 = \frac{a+1}{1-k_3}$       |

| $-k_1 > a \ge -k_3$ | 02-01     | $t_1 = \frac{a+k_3}{k_3-k_1}$   |

| $0 > a \ge -k_1$    | 11-02     | $t_1 = \frac{a + k_1}{k_1}$     |

| $k_2 > a \ge 0$     | 12-11     | $t_1 = \frac{a}{k_2}$           |

| $1 \ge a \ge k_2$   | 22-12     | $t_1 = \frac{a - k_2}{1 - k_2}$ |

$$a = \frac{V_{ab}}{V_{C1} + V_{C2}} = \rho V_{ab}. (3)$$

Using the factors  $k_1$ ,  $k_2$  and  $k_3$  defined in Table II, and depending on the unbalance case from A to H determined in Table III, an iterative geometrical search of factor a in the resulting reduced 1D control region finally determines the switching sequence and the switching times. The switching sequence is formed by the two nearest switching states of the 1D control region. As an example, the results obtained for case A are summarized in Table IV. Similar tables were obtained for all the cases [15]. All the determined switching sequences generates the desired phase voltage  $V_{ab}$  whilst the dc voltages tend to be controlled towards their desired values. The calculations involved in the process are very simple.

# IV. DC VOLTAGE RATIO CONTROL FOR MULTILEVEL SDC-CHB

The aim of this paper is to control any dc voltage ratio using a SDC-CHB always fulfilling that  $V_{C1} \geq V_{C2}$ . As was mentioned in section II previous works have demonstrated that some specific dc voltage ratios can be controlled choosing properly the redundant switching states in the switching sequence. DC voltage ratios different of 1:1 or 2:1 are not controlled because the redundancy property is lost. In this paper, using the 1D-FFSVM technique and the proposed dc voltage ratio control method any dc voltage ratio can be achieved. However, it should be noticed that the controllability of the system has to be studied because it depends on the

desired dc voltage ratio and the power factor as is addressed in section V.

The proposed way to control the balance of the dc voltage of the floating cell of the two-cell SDC-CHB inverter is similar to the technique to carry out the dc voltage control for the two-cell CHB acting as a synchronous rectifier. As was mentioned before, this technique is based on the exclusion of the inappropriate states in the switching sequence regardless of whether or not they are redundant. In this paper, a generalization of the method is presented in order to achieve any dc voltage ratio using the two-cell SDC-CHB acting as an inverter.

#### A. Target: DC voltage ratio 1:1

In this section of the paper the control objective is to have the same voltage in each cell of the SDC-CHB. The dc voltage control method summarized in previous section is directly applied to the two-cell SDC-CHB. The determination of the switching sequence and the switching times follows the next steps:

- 1) Determination of the  $k_i$  factors using Table II.

- 2) Determination of the unbalance case (from A to H) using Table III.

- 3) Normalization of the desired phase voltage  $V_{ab}^*$  using expression (3) obtaining factor a.

- 4) Geometrical search of factor *a* in the reduced 1D control region. The switching sequence and the switching times are calculated using tables similar to Table IV depending on the unbalance case (from A to H) [15]. These tables describe the modulation strategies related to 1D control regions similar to those shown in Fig. 2 where some of the switching states have been eliminated because they tend to unbalance the dc voltages of a multilevel CHB. Therefore, the same modulation strategy can be used to control the dc voltage of the two-cell SDC-CHB.

#### B. Target: DC voltage ratio k:1

Taking into account any current and voltage condition, any case considering the dc voltage ratio k:1 can be reduced to a case present on the dc voltage ratio 1:1 study (cases from A to H) summarized in Table III. Depending on the desired value of the dc voltage ratio k, Table V or Table VI has to be used to achieve the dc voltage ratio target. Table V shows the case  $2 > k \ge 1$  and Table VI shows the case  $k \ge 2$ .

In order to understand these tables, several examples are shown. Firstly, let's assume that the desired dc voltage ratio is 1.5:1, the phase current  $I_{ab}$  is positive and the actual dc voltage unbalance fulfills that  $V_{C2} < V_{C1} \le 1.5 V_{C2}$ . These conditions included in those defined for case A in Table III for a desired dc voltage ratio equal to 1:1. Under these voltage and current assumptions, it can be noticed that it is desired that  $V_{C1}$  increases and  $V_{C2}$  decreases to achieve the 1.5:1 dc voltage ratio. These desired dc voltage conditions ( $V_{C1} \uparrow, V_{C2} \downarrow$ ), shown in the fourth column of Table V, do not coincide with the desired dc voltage conditions of case A in Table III where it is desired completely the opposite. Cases A, B, C and D have opposite effects on the dc voltage values compared with cases E, F, G and H respectively. Therefore, in the example

TABLE V CASES OF STUDY OF THE DC VOLTAGE RATIO CONTROL STRATEGY WITH DC VOLTAGE RATIO  $k:1,1\leq k\leq 2$

| Actual                         | Associated                                                                                                                                                                                                                                                                                                                                                            | Desired dc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dc Voltage                     | dc Voltage                                                                                                                                                                                                                                                                                                                                                            | Voltage Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Condition                      | Ratio 1:1 Case                                                                                                                                                                                                                                                                                                                                                        | $V_{C1}^*, V_{C2}^*$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{C2} < V_{C1} \le kV_{C2}$  | Case E                                                                                                                                                                                                                                                                                                                                                                | $\uparrow$ , $\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $2V_{C2} \ge V_{C1} > kV_{C2}$ | Case A                                                                                                                                                                                                                                                                                                                                                                | $\downarrow,\uparrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $V_{C1} > 2V_{C2}$             | Case B                                                                                                                                                                                                                                                                                                                                                                | $\downarrow$ , $\uparrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{C1} < V_{C2} \le 2V_{C1}$  | Case C                                                                                                                                                                                                                                                                                                                                                                | $\uparrow$ , $\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{C2} > 2V_{C1}$             | Case D                                                                                                                                                                                                                                                                                                                                                                | $\uparrow$ , $\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{C2} < V_{C1} \le kV_{C2}$  | Case G                                                                                                                                                                                                                                                                                                                                                                | $\uparrow$ , $\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $2V_{C2} \ge V_{C1} > kV_{C2}$ | Case E                                                                                                                                                                                                                                                                                                                                                                | $\downarrow$ , $\uparrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{C1} > 2V_{C2}$             | Case F                                                                                                                                                                                                                                                                                                                                                                | $\downarrow$ , $\uparrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{C1} < V_{C2} \le 2V_{C1}$  | Case G                                                                                                                                                                                                                                                                                                                                                                | $\downarrow,\uparrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $V_{C2} > 2V_{C1}$             | Case H                                                                                                                                                                                                                                                                                                                                                                | $\uparrow$ , $\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                | $\begin{array}{c} \text{dc Voltage} \\ \text{Condition} \\ \\ V_{C2} < V_{C1} \leq kV_{C2} \\ 2V_{C2} \geq V_{C1} > kV_{C2} \\ V_{C1} > 2V_{C2} \\ \\ V_{C1} < V_{C2} \leq 2V_{C1} \\ V_{C2} > 2V_{C1} \\ \\ V_{C2} > 2V_{C1} \\ \\ V_{C2} < V_{C1} \leq kV_{C2} \\ 2V_{C2} \geq V_{C1} > kV_{C2} \\ V_{C1} > 2V_{C2} \\ V_{C1} < V_{C2} \leq 2V_{C1} \\ \end{array}$ | $\begin{array}{cccc} \text{dc Voltage} & \text{dc Voltage} \\ \text{Condition} & \text{Ratio 1:1 Case} \\ \hline V_{C2} < V_{C1} \le kV_{C2} & \text{Case E} \\ 2V_{C2} \ge V_{C1} > kV_{C2} & \text{Case A} \\ V_{C1} > 2V_{C2} & \text{Case B} \\ V_{C1} < V_{C2} \le 2V_{C1} & \text{Case C} \\ V_{C2} > 2V_{C1} & \text{Case D} \\ \hline V_{C2} < V_{C1} \le kV_{C2} & \text{Case G} \\ 2V_{C2} \ge V_{C1} > kV_{C2} & \text{Case E} \\ V_{C1} > 2V_{C2} & \text{Case F} \\ V_{C1} < V_{C2} \le 2V_{C1} & \text{Case G} \\ \hline \end{array}$ |

TABLE VI CASES OF STUDY OF THE DC VOLTAGE RATIO CONTROL STRATEGY WITH DC VOLTAGE RATIO k:1,k>2

| Phase           | Actual                         | Associated     | Desired dc                |

|-----------------|--------------------------------|----------------|---------------------------|

| Current         | dc Voltage                     | dc Voltage     | Voltage Condition         |

| Condition       | Condition                      | Ratio 1:1 Case | $V_{C1}^*, V_{C2}^*$      |

|                 | $V_{C2} < V_{C1} \le 2V_{C2}$  | Case E         | $\uparrow$ , $\downarrow$ |

|                 | $kV_{C2} \ge V_{C1} > 2V_{C2}$ | Case F         | $\uparrow$ , $\downarrow$ |

| $I_{ab} > 0$    | $V_{C1} > kV_{C2}$             | Case B         | $\downarrow$ , $\uparrow$ |

|                 | $V_{C1} < V_{C2} \le 2V_{C1}$  | Case C         | $\uparrow$ , $\downarrow$ |

|                 | $V_{C2} > 2V_{C1}$             | Case D         | $\uparrow$ , $\downarrow$ |

|                 | $V_{C2} < V_{C1} \le 2V_{C2}$  | Case A         | $\uparrow$ , $\downarrow$ |

|                 | $kV_{C2} \ge V_{C1} > 2V_{C2}$ | Case B         | $\uparrow$ , $\downarrow$ |

| $I_{ab} \leq 0$ | $V_{C1} > kV_{C2}$             | Case F         | $\downarrow$ , $\uparrow$ |

|                 | $V_{C1} < V_{C2} \le 2V_{C1}$  | Case G         | $\uparrow$ , $\downarrow$ |

|                 | $V_{C2} > 2V_{C1}$             | Case H         | $\uparrow$ , $\downarrow$ |

case, the final case to be applied is case E in order to fulfill with the desired dc voltage conditions  $(V_{C1} \uparrow, V_{C2} \downarrow)$ .

On the other hand, let's assume in a second example that the desired dc voltage ratio is 1.5:1, the phase current  $I_{ab}$  is positive and the actual dc voltage unbalance fulfills that  $2V_{C2} \geq V_{C1} > kV_{C2}$ . This dc voltage condition also is included in case A in Table III for a desired dc voltage ratio equal to 1:1. In this second example, the desired dc voltage conditions, shown in the fourth column of Table V, are  $(V_{C1}\downarrow,V_{C2}\uparrow)$  what coincides with the desired dc voltage conditions of case A in Table III. Therefore, the case to be applied in order to tend to the desired dc voltage ratio 1.5:1 is case A. All the cases for desired dc voltage ratios k:1 can be studied using similar considerations and the results are summarized in Table V and Table VI.

Finally, as a summary, the determination of the switching sequence and the switching times to achieve an specific desired dc voltage ratio *k*:1 follows the next steps:

- 1) Determination of the  $k_i$  factors using Table II.

- 2) Determination of the unbalance case (from A to H) using Table V or Table VI depending on the value of the desired dc voltage ratio k.

- 3) Normalization of the desired phase voltage  $V_{ab}^*$  using expression 3 obtaining factor a.

- 4) The switching sequence and the switching times are calculated using tables similar to Table IV depending on the unbalance case (from A to H).

As can be observed, the step 2 is the only difference between the dc voltage ratio 1:1 case and any dc voltage ratio k:1.

The proposed technique can be extended to SDC-CHB with more than two H-bridges. The required study to extend the proposed modulation technique for SDC-CHB with higher number of power cells rises proportionally in complexity, since the number of cases to be analyzed increases. However, this study can be done offline writing similar tables compared with those obtained for the two-cell SDC-CHB case. However, it should be noticed that the online calculations needed to execute the corresponding modulation technique do not increase significantly. This fact was also reported for the 1D-FFSVM technique in [15].

## V. ANALYSIS OF THE CONTROLLABILITY OF THE SDC-CHB

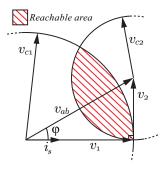

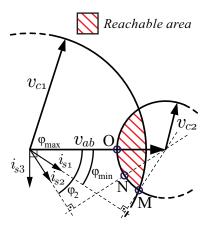

An analysis of the performance of the SDC-CHB in terms of the limits of the output phase voltage and loading conditions is presented in this section. The fundamental harmonic of the output phase voltage  $(V_{ab,1})$ , the fundamental harmonic of the phase current  $(I_{ab,1})$  and the fundamental harmonic of the output voltage of each H-bridge  $(V_{m1,1},V_{m2,1})$  are considered in this analysis. A phasorial representation, as in [27], is used plotting the RMS values of these magnitudes defined respectively as  $v_{ab}$ ,  $i_{ab}$ ,  $v_1$  and  $v_2$ . As  $V_{ab} = V_{m1} + V_{m2}$ , it is fulfilled that  $V_{ab,1} = V_{m1,1} + V_{m2,1}$  and  $v_{ab} = v_1 + v_2$ . In addition, in these phasorial diagrams, the maximum output voltages in RMS of each H-bridge can be calculated as

$$v_{c1} = \frac{2\sqrt{2}}{\pi} V_{C1}$$

$$v_{c2} = \frac{2\sqrt{2}}{\pi} V_{C2}.$$

(4)

#### A. Output voltage analysis

In the SDC-CHB operation, the average active power demanded by the load has to be provided by the fixed cell. The floating cell only can contribute with reactive power, on the contrary the floating capacitor voltage changes. The maximum output voltage that can be achieved by the SDC-CHB depends on the ratio between the RMS value of the voltage of the fixed voltage cell  $(v_{c1})$  and the RMS value of the desired phase voltage  $(v_{ab})$ . Two situations have to be considered:

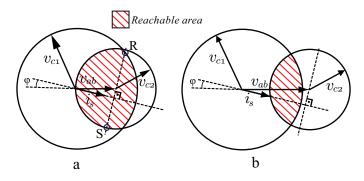

I)  $v_{c1} \geq v_{ab}$ : In this case  $v_{ab}$  can be generated only using the fixed cell. Fig. 3 shows this situation for a certain load value. In this figure the red marked region represents the set of points that can be used to compose  $v_{ab}$ . In steady state operation, only the points located over the segment MN in Fig. 3 ensure that the floating capacitor voltage remains constant. These points are located over the perpendicular line to the phase current  $i_{ab}$  representing only reactive power exchange between the floating cell and the load. The rest of points inside

Fig. 3. Reachable area when  $v_{c1} \ge v_{ab}$ . Stable operation points.

Fig. 4. Reachable area when  $v_{c1} < v_{ab}$ . Stable operation points.

the red marked area, although can be chosen to generate  $v_{ab}$ , induce variations in the floating capacitor dc voltage. There is some active power extracted or injected from the floating cell, depending on the projection of  $v_{c2}$  over  $i_{ab}$ . However, these points can be used during the transient operation to regulate the floating capacitor dc voltage value.

As was said above, if the desired phase voltage  $v_{ab}$  is less or equal than  $v_{c1}$ , it can be generated only with the fixed voltage H-bridge. However, some extra advantages can be found in the sense of enhancement of the quality of the output waveform because, depending on the actual dc voltage ratio, new output voltage levels can be used if the floating H-bridge is used.

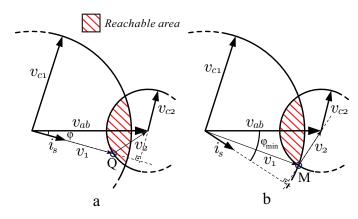

2)  $v_{c1} < v_{ab}$ : In this case the phase voltage  $v_{ab}$  can not be generated only with the fixed cell and therefore the floating cell contributes critically in the generation of the phase voltage. Fig. 4 shows this situation for a certain load value. Again the red marked region represents the set of points that can be used to compose  $v_{ab}$ , and the points located over the segment MN are those that only exchange reactive power between the floating cell and the load ensuring that the floating capacitor voltage remains constant. A similar analysis compared with that done in subsection V-A1 can be done. Similar conclusions concerning the points that should be used during steady and transient state can be obtained. However new conclusions related with the advantages and disadvantages can be done.

It can be noticed that if desired phase voltage  $v_{ab}$  is greater than  $v_{c1}$ , the maximum phase voltage that can be generated with the SDC-CHB exceeds to that generated with

Fig. 5. Maximum stable phase voltage achieved by the two-cell SDC-CHB.

the fixed voltage H-bridge. As a consequence, the SDC-CHB expands the load operation range over the a simple H-bridge converter. The maximum stable phase voltage that can be achieved depends on the values of  $v_{c1}$  and  $v_{c2}$ . Fig. 5 shows the maximum output voltage that can be generated by the SDC-CHB for a given load.

It can be observed that the maximum active and reactive power consumed by the load are fixed by the values of  $v_{c1}$  and  $v_{c2}$ . The active power provided by the SDC-CHB has to be generated from the fixed cell. For this reason only the reactive power range of the converter is expanded. As well as the load operation range increase, the enhancement of the quality of the output waveform is also added as new output voltage levels appear depending on the dc voltage ratio.

#### B. Output load analysis

As was pointed out in section V-A, the output load operation range of the SDC-CHB only exceeds the fixed voltage H-bridge when  $v_{c1} < v_{ab}$ . For this reason in this section only this case is studied.

To develop the analysis of the output load range, it is assumed that the phase voltage  $V_{ab}$  tracks a sinusoidal waveform reference with fixed amplitude. Fig. 6 shows that it is not possible to use any load power factor to achieve stable operation in the SDC-CHB. Fig. 6a shows a load power factor with unstable operation. The phase voltage  $v_{ab}$  can be reached using for instance the point Q. However this point involves active power drawn from the floating cell leading to an unstable operation of the SDC-CHB. To avoid this, it is necessary to ensure that only reactive power is drawn from the floating cell. Fig. 6b shows the maximum load power factor that ensures SDC-CHB operation without active power supplied from the floating cell. In this case the phase voltage  $v_{ab}$  can be reached from point M. This operation point represents the maximum load power factor that could be connected to the SDC-CHB to achieve stable operation for a given output voltage.

It should be pointed out that the load power factor can be decreased without restrictions. Fig. 7 shows the output load operation range for loads with inductive power factor. It can be observed that the load angle can vary from  $\varphi_{min}$  represented by point M to  $\pi/2$  obtained in point O. Any intermediate angle can be used as the converter load, for example point N. An analogue representation can be done for loads with capacitive power factor only changing the sign of the angles  $\varphi$ .

Fig. 6. Analysis of the stable operation points. a) Unstable operation point. b) Maximum power factor that achieve stable operation.

Fig. 7. Converter operation load range with inductive power factor.

## VI. EXPERIMENTAL RESULTS

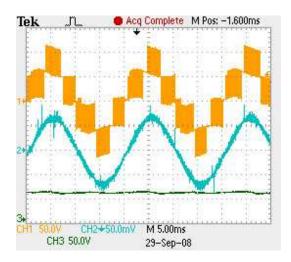

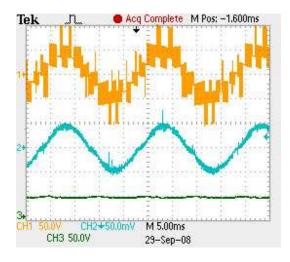

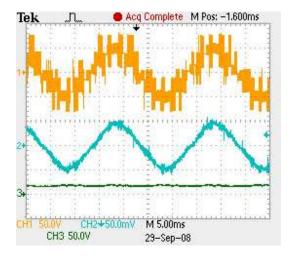

The proposed control strategy to achieve any dc voltage ratio for a single-phase two-cell SDC-CHB has been experimentally tested in a 5 kVA laboratory prototype shown in Fig. 8. The SDC-CHB inverter is connected to a RL load (R=7  $\Omega$ , L=2 mH.) In this experiment,  $V_{C1}$  voltage value is fixed by an external ac/dc diode bridge ( $V_{C1}$ =60 V) and  $V_{C2}$  voltage is controlled using the proposed dc voltage ratio control strategy.

#### A. Target: dc voltage ratio 1:1

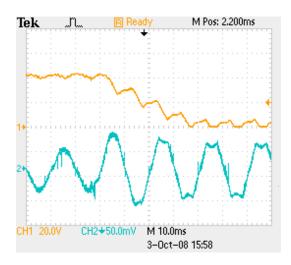

The experimental results when the desired dc voltage ratio is 1:1 are shown in Fig. 9. The desired phase voltage is 50  $V_{RMS}$ . It can be seen that using the 1D-FFSVM technique within the dc voltage ratio control method, the floating voltage of the capacitor  $V_{C2}$  is controlled fulfilling that  $V_{C1}$ = $V_{C2}$ =60 V. At the same time, the generated phase voltage and phase current have good quality achieving a total harmonic distortion value of the phase current considering up to  $50^{th}$  harmonic order (THD<sub>50</sub>) equal to 5.72%.

#### B. Target: dc voltage ratio k:1

The desired phase voltage is in this case 35  $V_{RMS}$ . Firstly the desired dc voltage ratio is 1.5:1. The results are shown in Fig. 10 where it can be seen that the desired dc voltage

ratio is achieved since  $V_{C1}$ =60 V and  $V_{C2}$ =40 V. In a second experiment, the desired dc voltage ratio is fixed to 3.5:1. The results are shown in Fig. 11 where the desired dc voltage ratio is also achieved since  $V_{C1}$ =60 V and  $V_{C2}$ =17.15 V.

It can be seen from Fig. 10 and Fig. 11 that the phase voltage and the phase current waveforms are slightly distorted compared with the output current using a voltage ratio 1:1 (Fig. 9). In fact, the THD<sub>50</sub> value of the phase current of Fig. 10 and Fig. 11 are respectively equal to 6.45% and 6.81%. This distortion depends on the chosen dc voltage ratio and does not depend on the loading conditions. Using a dc voltage ratio k:1 different of 1:1 or 2:1 the phase voltage becomes deteriorated. Using dc voltage ratio 1:1 or 2:1 the redundancy property permits to achieve the desired output voltage without distorting the control region even eliminating some switching states because they are redundant. Using a dc voltage ratio k:1 different of 1:1 or 2:1 the redundancy property is lost and eliminating some switching states the control region changes. This fact creates higher voltage steps in the modulated phase voltage. However, it can be noticed that using a dc voltage ratio k:1 different of 1:1 or 2:1, nine different output voltages can be achieved by the single-phase two-cell SDC-CHB. Using the dc voltage ratio 1:1 or 2:1 the number of output voltage levels is five and seven respectively. The increase of the number of output voltage levels with dc voltage ratio k:1 compensates the slight distortion of the phase voltage and phase current making comparable the total harmonic distortion (THD) of the output waveforms.

An experiment testing the stability of the system has been performed and the results are shown in Fig. 12. In the experiment, the two-cell SDC-CHB converter is firstly working under a steady state stable situation. The fixed voltage  $V_{C1}$  is 60 V and the floating voltage  $V_{C2}$  is 40 V (desired dc voltage ratio equal to 1.5:1). The converter is connected to a RL load (R=7  $\Omega$ , L=2 mH.) and the desired modulated RMS phase voltage  $v_{ab}$  is 35 V<sub>RMS</sub>. Suddenly,  $v_{ab}$  value is changed to 60 V<sub>RMS</sub> making the converter operation unstable. This

Fig. 8. 5 kVA single-phase two-cell SDC-CHB prototype.

Fig. 9. Experimental Results for the SDC-CHB with dc voltage ratio target 1:1. Phase voltage  $(V_{ab})$ , phase current  $(I_{ab})$  and dc voltage of the floating H-bridge  $(V_{C2})$ .

Fig. 10. Experimental Results for the SDC-CHB with dc voltage ratio target 1.5:1. Phase voltage  $V_{ab}$  (Channel 1), phase current  $I_{ab}$  (Channel 2) and dc voltage of the floating H-bridge  $V_{C2}$  (Channel 3).

Fig. 11. Experimental Results for the SDC-CHB with dc voltage ratio target 3.5:1. Phase voltage  $(V_{ab})$ , phase current  $(I_{ab})$  and dc voltage of the floating H-bridge  $(V_{C2})$ .

Fig. 12. Stability test of the SDC-CHB with dc voltage ratio target 1.5:1. Phase current  $(I_{ab})$  and dc voltage of the floating H-bridge  $(V_{C2})$ .

Fig. 13. Analytical situations of the stability experiment shown in Fig. 12. a) Stable operation with  $v_{ab}$ = 35  $V_{RMS}$  b) Unstable operation with  $v_{ab}$ = 60  $V_{RMS}$ .

phenomenon can be explained using the phasorial diagram of the system under both experimental conditions. In Fig. 13, the stable and the unstable operation of the converter is represented. It is clear that the converter can generate  $v_{ab}$ = 35  $V_{RMS}$  with the actual phase angle of the experiment ( $\varphi$ =5.12°) because there are possible solutions to achieve the desired dc voltage ratio with no active power drawn by the floating voltage cell (all the solutions between point R and S). However, when the desired phase voltage is  $v_{ab}$ = 60  $V_{RMS}$ , there are not points of the reachable area where this active power is zero. Therefore the floating voltage of the cell drops to zero and the control can not be achieved.

#### VII. CONCLUSIONS

In this paper, the dc voltage ratio control of a single-phase two-cell CHB fed using only a dc source (called in this paper SDC-CHB) is presented. This control technique is based on the elimination of the switching states which tend to make unstable the floating dc voltage. Using the proposed control strategy any dc voltage ratio k:1 ( $k \ge 1$ ) can be achieved but taking into account the controllability limits of the system. In this way, an analysis of the stable operation of the SDC-CHB depending on the desired phase voltage to be generated and the loading conditions has been addressed.

The proposed dc voltage ratio control technique is applied using the 1D-FFSVM for multilevel CHB. Using this feed-forward modulation and the proposed dc voltage ratio control technique, the phase voltage is generated even under dc voltages unbalanced situations reducing the output waveforms distortion. In this way, a good performance under transient or steady state dc voltages unbalance is achieved. The technique can be extended to be applied to SDC-CHB converters with more than two H-bridges with the consequent increase of the necessary operations. However, it can be noticed that this study can be done offline writing similar tables compared with those obtained for the two-cell SDC-CHB case. The online calculations needed to execute the corresponding modulation technique do not increase significantly.

Experimental results using a 5 kVA two-cell single-phase SDC-CHB are shown in order to validate the proposed dc voltage ratio control technique.

#### ACKNOWLEDGMENT

The authors gratefully acknowledge financial support provided by the Spanish Ministry of Science and Technology under project TEC2006-03863 and by the Andalusian Government Research Council under project EXC/2005/TIC-1172.

#### REFERENCES

- R. H. Baker and L. H. Bannister, Electric power converter, U.S. Patent 3 867 643, Feb. 18, 1975.

- [2] J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt and S. Kouro, "Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [3] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo and M. M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Magazine*, vol. 2, no. 2, pp. 28–39, June 2008.

- [4] Y. Cheng, C. Qian, M. L. Crow, S. Pekarek and S. Atcitty, "A Comparison of Diode-Clamped and Cascaded Multilevel Converters for a STATCOM With Energy Storage," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1512–1521, Oct. 2006.

- [5] J. M. Carrasco, L. G. Franquelo, J. T. Bialasiewicz, E. Galvan, R. Portillo, M. M. Prats, J. I. Leon and N. Moreno-Alfonso, "Power-Electronic Systems for the Grid Integration of Renewable Energy Sources: A Survey," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1002–1016, June 2006.

- [6] M. D. Manjrekar, P. K. Steimer and T. A. Lipo, "Hybrid multilevel power conversion system: a competitive solution for high-power applications," *IEEE Trans. Ind. Applicat.*, vol. 36, Issue 3, pp. 834–841, May-June 2000.

- [7] Z. Du, L. M.Tolbert, J. N. Chiasson and B. Ozpineci, "A cascade multilevel inverter using a single DC source," IEEE 21<sup>st</sup> Annual Applied Power Electronics Conference and Exposition (APEC '06), 19-23 March 2006.

- [8] Z. Du, L. M. Tolbert, J. N. Chiasson, B. Ozpineci, H. Li and A. Q. Huang, "Hybrid Cascaded H-bridges Multilevel Motor Drive Control for Electric Vehicles," IEEE 37<sup>th</sup> Power Electronics Specialists Conference (PESC'06), 18-22 June 2006.

- [9] J. N. Chiasson, B. Ozpineci and L. M. Tolbert, "A Five-Level Three-Phase Hybrid Cascade Multilevel Inverter Using a Single DC Source for a PM Synchronous Motor Drive," IEEE 22<sup>nd</sup> Annual Applied Power Electronics Conference (APEC 2007), pp. 1504–1507, Feb. 25-March 1 2007.

- [10] H. Li, K. Wang, D. Zhang and W. Ren, "Improved Performance and Control of Hybrid Cascaded H-bridge Inverter for Utility Interactive Renewable Energy Applications," IEEE 38<sup>th</sup> Power Electronics Specialists Conference (PESC'07), pp. 2465–2471, 17-21 June 2007.

- [11] N. Celanovic, I. Celanovic and D. Boroyevich, "The feedforward method of controlling three-level diode clamped converters with small DClink capacitors," IEEE 32<sup>nd</sup> Power Electronics Specialists Conference (PESC'01), vol. 3, pp. 1357–1362, 17-21 June 2001.

- [12] J. Pou, D. Boroyevich and R. Pindado, "New feedforward space-vector PWM method to obtain balanced AC output voltages in a three-level neutral-point-clamped converter," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 1026–1034, Oct. 2002.

- [13] S. Kouro, P. Lezana, M. Angulo and J. Rodriguez, "Multicarrier PWM with DC-Link Ripple Feedforward Compensation for Multilevel Inverters," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 52–59, Jan. 2008.

- [14] J. I. Leon, S. Vazquez, R. Portillo, L. G. Franquelo, J. M. Carrasco, P. W. Wheeler, A. J. Watson, "Three-Dimensional Feed-Forward Space Vector Modulation Applied to Multilevel Diode-Clamped Converters," *IEEE Trans. Ind. Electron.*, in press.

- [15] J. I. Leon, S. Vazquez, A. J. Watson, P. W. Wheeler, L. G. Franquelo and J. M. Carrasco, "Feed-forward Space Vector Modulation for Single-Phase Multilevel Cascade Converters with any DC voltage ratio," *IEEE Trans. Ind. Electron.*, in press.

- [16] G. Carrara, S. Gardella, M. Marchesoni, R. Salutari and G. Sciutto, "A new multilevel pwm method: A theoretical analysis," *IEEE Trans. Power Electron.*, vol. 7, no. 3, pp. 497–505, July 1992.

- [17] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 858–867, August 2002.

- [18] A. K. Gupta and A. M. Khambadkone, "A space vector PWM scheme for multilevel inverters based on two-level space vector PWM," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1631–1639, Oct. 2006.

- [19] N. Celanovic and D. Boroyevich, "A fast space-vector modulation algorithm for multilevel three-phase converters," *IEEE Trans. Ind. Applicat.*, vol. 37, no. 2, pp. 637–641, Mar./Apr. 2001.

- [20] C. Rech and J. R. Pinheiro, "Hybrid Multilevel Converters: Unified Analysis and Design Considerations," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 1092–1104, April 2007.

- [21] J. I. Leon, R. Portillo, S. Vazquez, J. J. Padilla, L. G. Franquelo and J. M. Carrasco, "Simple Unified Approach to Develop a Time Domain Modulation Strategy for Single-Phase Multilevel Converters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 9, pp. 3239–3248, Sept. 2008.

- [22] H. S. Patel and R. G. Hoft, "Generalized techniques of harmonic elimination and voltage control in thyristor inverters-Part 1: Harmonic elimination," *IEEE Trans. Ind. Applicat.*, vol. IA-9, pp. 310–317, May/June 1973.

- [23] V. G. Agelidis, A. I. Balouktsis and C. Cossar, "On Attaining the Multiple Solutions of Selective Harmonic Elimination PWM Three-Level Waveforms Through Function Minimization," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 996–1004, March 2008.

- [24] Z. Du, L. M. Tolbert, J. N. Chiasson and B. Ozpineci, "Reduced Switching-Frequency Active Harmonic Elimination for Multilevel Converters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 4, pp. 1761–1770, April 2008.

- [25] A. J. Watson, P. W. Wheeler and J. C. Clare, "A Complete Harmonic Elimination Approach to DC Link Voltage Balancing for a Cascaded Multilevel Rectifier," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2946–2953, Dec. 2007.

- [26] J. I. Leon, R. Portillo, L. G. Franquelo, S. Vazquez, J. M. Carrasco and E. Domínguez, "New space vector modulation technique for single-phase multilevel converters," IEEE International Symposium on Industrial Electronics (ISIE'07), pp. 617–622, 4–7 June 2007.

- [27] S. Vazquez, J. I. Leon, J. M. Carrasco, L. G. Franquelo, E. Galvan, J. A. Sanchez and E. Dominguez "Controller Design for a Single-Phase Two-Cell Multilevel Cascade H-bridge Converter," IEEE International Symposium on Industrial Electronics, 2008 (ISIE 2008), pp. 1–6, June 30–July 2 2008.

Sergio Vazquez (S'04, M'08) was born in Seville, Spain, in 1974. He received the B.S. and M.S. degrees in industrial engineering from the University of Seville (US) in 2003 and 2006, respectively. In 2002, he was with the Power Electronics Group, US, working in R&D projects. He is currently an Assistant Professor with the Department of Electronic Engineering in the US. His research interests include electronic power systems, modeling, modulation and control of power electronic converters and power quality in renewable generation plants.

Jose I. Leon (S'04, M'07) was born in Cádiz, Spain, in 1976. He received the B.S. and M.S. and PhD degrees in telecommunications engineering from the University of Seville (US), Spain, in 1999, 2001 and 2006 respectively. In 2002, he joined the Power Electronics Group, US, working in R&D projects. Currently, he is an Associate Professor with the Department of Electronic Engineering, US. His research interests include electronic power systems, modeling, modulation and control of power converters and industrial drives.

Leopoldo G. Franquelo (M'84, SM'96, F'05) was born in Málaga, Spain. He received the M.Sc. and Ph.D. degrees in electrical engineering from the University de Seville (US), Seville, Spain in 1977 and 1980 respectively. His current research interest lies on modulation techniques for multilevel inverters and its application to power electronic systems for renewable energy systems. He was the Vice-President of the Industrial Electronics Society (IES) Spanish Chapter (2002 - 2003), member at Large of the IES AdCom (2002 - 2003). He was the Vice-

President for Conferences of the IES (2004 - 2007), in which he has also been a Distinguished Lecturer since 2006. He has been an Associated Editor for the IEEE Transactions on Industrial Electronics since 2007. Since January 2008 he is President Elect of IEEE Industrial Electronics Society.

Jose J. Padilla was born in Cordoba, Spain, in 1983. He received the B.S. degree in industrial electronics engineering from the University of Cordoba (UCO), Spain, in 2004. Currently, he is studying for B.S. degree in telecommunications engineering in the University of Seville (US), Seville, Spain. In 2007, he joined the Power Electronics Group, US, working in R&D projects. His research interests include electronic power systems, modulation, control and experimental testings of power electronics converters.

Juan M. Carrasco (M'97) was born in San Roque, Spain. He received the M.Eng. and Dr.Eng. degrees in industrial engineering from the University of Seville (US), Seville, Spain, in 1989 and 1992, respectively. From 1990 to 1995, he was an Assistant Professor with the Department of Electronic Engineering in the US where he is currently an Associate Professor. He has been working for several years in the power electronic field where he was involved in the industrial application of the design and development of power converters applied to

renewable energy technologies. His current research interests are in distributed power generation and the integration of renewable energy sources.