# De-Embedding Transmission Line Measurements for Accurate Modeling of IC Designs

Alain M. Mangan, Sorin P. Voinigescu, Senior Member, IEEE, Ming-Ta Yang, and Mihai Tazlauanu

Abstract—A new technique to de-embed the contributions of parasitic structures from transmission line measurements is presented and applied to microstrip lines fabricated in 90- and 130-nm RF-CMOS technologies. De-embedded measurements are used to extract characteristic impedance, attenuation constant, group delay, and effective permittivity. The effective thickness of the ground plane is demonstrated to be as important as the thickness of the top metal layer in minimizing interconnect loss. Furthermore, it is confirmed that metal area densities as low as 65% are adequate for the ground plane of microstrip lines.

*Index Terms*—Characterization, de-embedding, deep-submicrometer technologies, integrated circuits, interconnect, losses, microstrip lines, slotted ground planes, transmission lines.

#### I. INTRODUCTION

EMAND for increased bandwidth in communication systems has lead to ever higher operating frequencies and data rates in integrated circuits. The most recent examples of such developments are radio systems at 60 GHz [1], as well as broad-band communication networks with data rates up to 80 Gb/s [2]. As the frequency range of these applications enters the mm-wave regime, wavelengths become comparable to on-chip component dimensions. Hence, transmission lines play an increasingly vital role in both narrow-band [3] and broad-band [4] circuit design. Whether used intentionally or not, transmission lines are becoming essential in describing circuit behavior. Accurate models are therefore required.

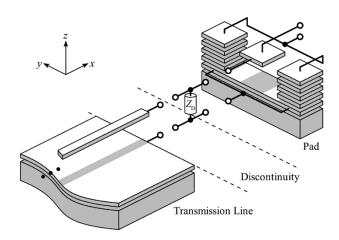

Although transmission line theory is well established, uncertainties in various process parameters demand some form of measurement for model verification. However, any measurement is limited by an inherent flaw whereby test pads and interconnect are needed to access the device under test (DUT) (Fig. 1). Accurate de-embedding is therefore required to eliminate the parasitic contributions. Transmission line de-embedding techniques can also be used to remove parasitics from other device test structures [5].

Most de-embedding procedures rely completely on lumped equivalent circuits to model parasitics [6]–[9]. By contrast,

Manuscript received May 15, 2005; revised October 21, 2005. This work was supported in part by Micronet, CITO, and Quake Technologies Inc. CAD tools were provided by CMC through grants from NIT, CFI, and OIT. A. Mangan was supported by grants from Micronet, CITO, and Quake Technologies. The review of this paper was arranged by Editor C. McAndrew.

A. Mangan and S. Voinigescu are with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON, Canada, M5S 3G4.

M.-T. Yang is with TSMC, Hsinchu 300-77, Taiwan, R.O.C.

M. Tazlauanu is with Quake Technologies Inc., Ottawa, ON, Canada, K2K

Digital Object Identifier 10.1109/TED.2005.861726

Fig. 1. Composition of a microstrip line test structure.

it has been shown that the propagation constant  $(\gamma)$  can be extracted from the measurement of two transmission lines  $(\ell_1 \neq \ell_2)$ , without using explicit models for the pad parasitics, or calibrating the VNA [10]. Consequently, extraction techniques mostly focus on the characteristic impedance  $(Z_C)$

The new technique proposed in this paper relies on the symmetry of transmission line test structures. With regards to the extraction of  $\gamma$ , it is equivalent to that in [10], thus maintaining the state of the art [5]. It can also be shown that, when the test structure measurements are reciprocal  $(S_{12} = S_{21})$ , the proposed technique is equivalent to that of [15]. Unlike the latter technique, a more physically intuitive solution is obtained through the appropriate exploitation of both ABCD and Y parameter representations.

After a brief description of the de-embedding algorithm, the proposed technique will be applied to microstrip line test structures fabricated in two RF-CMOS technologies. The results will be used to establish a relationship between line configuration and expected circuit performance.

#### II. THEORY

#### A. De-Embedding

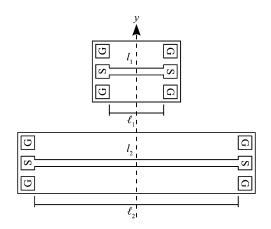

Consider two transmission line test structures of length  $\ell_1$  and  $\ell_2$ , where  $\ell_1 < \ell_2$  (Fig. 2). If properly designed, the structures will be perfectly symmetric about the y axis. By definition, the symmetry signifies that swapping ports 1 and 2 will not change the resulting S, Z, or Y matrices

$$S = \text{Swap}(S), \quad Z = \text{Swap}(Z), \quad Y = \text{Swap}(Y)$$

(1)

where Swap() swaps ports 1 and 2 of an S, Z, or Y matrix

$$\operatorname{Swap}\left(\begin{bmatrix} a_{11} & a_{12} \\ a_{21} & a_{22} \end{bmatrix}\right) \equiv \left(\begin{bmatrix} a_{22} & a_{21} \\ a_{12} & a_{11} \end{bmatrix}\right). \tag{2}$$

Fig. 1 reveals that the transmission matrix of either test structure can be decomposed into a cascade of 5 two-port networks consisting of the two pads, the intrinsic device, and the associated pad-line discontinuities  $(Z_{\rm D})$ . To simplify the derivations, the pad-line discontinuities will be lumped together with the pads, without loss of generality. Consequently, the (ABCD) transmission matrix of test structure  $l_i$ ,  $M_{l_i}^t$ , can be represented as the following product:

$$\boldsymbol{M}_{l_i}^t \equiv \boldsymbol{M}_{P1} \boldsymbol{M}_{l_i} \boldsymbol{M}_{P2} \tag{3}$$

where

$M_{l_i}$  represents the intrinsic line segment of structure i;

$M_{P1}$  represents the left pad;

$M_{P2}$  represents the right pad.

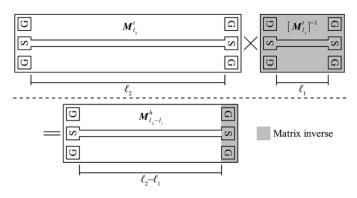

With this simple expression describing the test structures, we will derive an equation for the intrinsic transmission line. First, consider multiplying  $M_{l_2}^t$  with the inverse of  $M_{l_1}^t$  (Fig. 3)

$$M_{l_2-l_1}^h \equiv M_{l_2}^t \times [M_{l_1}^t]^{-1}$$

$$= M_{P1} M_{l_2} M_{l_1}^{-1} M_{P1}^{-1}$$

$$\equiv M_{P1} M_{l_2-l_1} M_{P1}^{-1}$$

(4)

where we define

$\begin{array}{ll} \pmb{M}_{l_2-l_1}^h & \text{ as the hybrid "structure" } \pmb{M}_{l_2}^t \times [\pmb{M}_{l_1}^t]^{-1} \text{ and } \\ \pmb{M}_{l_2-l_1} & \text{ as a line segment of length } \ell_2-\ell_1. \end{array}$

Assuming that the left pad can be modeled solely by a lumped admittance,  $Y_L$ , we have

$$\mathbf{M}_{P1} \equiv \begin{bmatrix} 1 & 0 \\ Y_L & 1 \end{bmatrix} \tag{5}$$

$$\boldsymbol{M}_{l_2-l_1}^h = \begin{bmatrix} 1 & 0 \\ Y_L & 1 \end{bmatrix} \boldsymbol{M}_{l_2-l_1} \begin{bmatrix} 1 & 0 \\ -Y_L & 1 \end{bmatrix}. \tag{6}$$

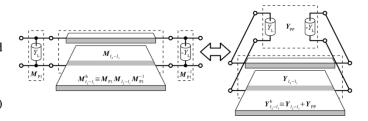

This will be referred to as the lumped pad assumption. Under the lumped pad assumption, the hybrid "structure" can be expressed in terms of Y parameters, as a parallel combination of the intrinsic transmission line and the parasitic lumped pads (Fig. 4)

$$\boldsymbol{Y}_{l_2-l_1}^h \equiv \boldsymbol{Y}_{l_2-l_1} + \begin{bmatrix} Y_L & 0\\ 0 & -Y_L \end{bmatrix} \tag{7}$$

where  $Y_{l_2-l_1}^h$  is the Y parameter representation of  $M_{l_2-l_1}^h$  and  $Y_{l_2-l_1}$  is the Y parameter representation of  $M_{l_2-l_1}$ .

Since the intrinsic device is symmetric, its Y parameters can be isolated by connecting  $\mathbf{Y}_{l_2-l_1}^h$  in parallel with a port-swapped version of itself, thus canceling out the effects of the pads

$$Y_{l_2-l_1} \equiv \frac{Y_{l_2-l_1}^h + \operatorname{Swap}(Y)_{l_2-l_1}^h}{2}.$$

(8)

Fig. 2. Two transmission line test structures.

Fig. 3. Multiplying the transmission matrix of line 2 with the matrix inverse of line 1

Fig. 4. Equivalent representations of the hybrid "structure" under the lumped pad assumption.

# B. Extraction

Assuming that a lossy transmission line of length  $\ell_2 - \ell_1$  can be modeled by [16]

$$\mathbf{M}_{l_2-l_1} \equiv \begin{bmatrix} A & B \\ C & D \end{bmatrix}$$

$$\equiv \begin{bmatrix} \cosh \gamma(\ell_2 - \ell_1) & Z_c \sinh \gamma(\ell_2 - \ell_1) \\ Z_C^{-1} \sinh \gamma(\ell_2 - \ell_1) & \cosh \gamma(\ell_2 - \ell_1) \end{bmatrix}$$

(9)

we can extract the characteristic impedance  $(Z_C)$  and the propagation constant  $(\gamma)$  using

$$Z_C = \sqrt{\frac{B}{C}} \left[\Omega\right] \quad \text{and} \quad \gamma = \frac{\cosh^{-1} A}{\ell_2 - \ell_1}.$$

(10)

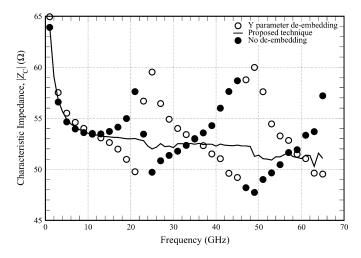

Fig. 5. Measured  $Z_C$  of a  $\ell_2 = 3.68$  mm meandering microstrip line.

Fig. 5 shows the extracted characteristic impedance of a  $\ell_2$  = 3.68 mm meandering microstrip line. The results demonstrate that the proposed technique is more immune to the discontinuities in the  $Z_C(f)$  characteristics, which are typically pronounced near frequencies where  $\ell = n\lambda/2$ . Note that the short microstrip line segment used for de-embedding is only  $\ell_1$  = 100  $\mu$ m long.

## III. MEASUREMENTS

#### A. Setups

1) 50-GHz Setup: Measurements were performed on an HP8510C VNA with flexible cables and Cascade Microtech device probes at Quake Technologies in Ottawa. The measurements were calibrated using the line-reflect-match (LRM) algorithm provided with the VNA, and the standards from a Cascade Microtech ISS 101–190 substrate.

2) 65-GHz Setup: Measurements were performed on a Wiltron 360B VNA with semi-rigid cables and Cascade Microtech device probes at the University of Toronto. The measurements were calibrated using the LRM algorithm provided by the WinCal software from Cascade Microtech, and the standards from a Cascade Microtech ISS 101–190 substrate.

LRM calibrations were used to compensate for the measurement system and move the reference plane up to the probe tips. Test structures fabricated in the 90-nm process were measured using both setups with excellent agreement between the two setups. The structures fabricated in the 130-nm process were measured solely with the 50-GHz setup.

## B. 90-nm RF-CMOS Test Structures

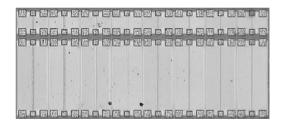

- 1) Fabricated Devices: Eight pairs of microstrip test structures were designed using various conductor and ground plane configurations (Fig. 6). When comparing characteristics, the convention "metal [x] over  $[y]w = [z] \mu m$ " will refer to a microstrip line designed with a metal x conductor, a metal y ground plane, and a conductor width of z micrometers. For reference, the process uses a 0.9- $\mu m$ -thick metal 8 layer and a 3.3- $\mu m$ -thick metal 9 layer, both implemented in copper.

- 2) Layout: Access to the microstrip line conductors is provided by chamfered 50  $\times$  50  $\mu m^2$  signal pads constructed in

Fig. 6. Micrograph of the eight transmission lines implemented in the 90-nm technology. Both the long (600  $\mu$ m) and the short (100  $\mu$ m) lines are present.

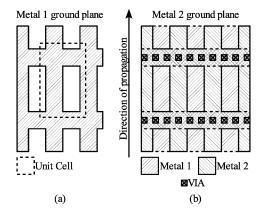

Fig. 7. Mesh pattern used for (a) metal 1 slotted ground planes (b) metal 2 slotted ground planes.

metal 9. On either side of each signal pad, larger pads are used to contact the ground plane using ground–signal–ground (GSG) device probes of 100- $\mu$ m pitch. A highly doped n-well connected to the ground pads is placed under the signal pads. The resultant pad capacitance was measured to be in the order of only 16–17 fF.

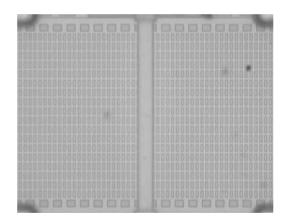

As CMOS technologies advanced beyond the 180-nm node, increasingly stringent metal density rules prohibited the design of solid ground planes. To accommodate these restrictions, metal ground planes must now be slotted. In these technologies, the ideal ground plane design implements the maximum allowed metal density with the smallest slot dimension possible. If the slots are much shorter than the wavelength, they will not affect the line characteristics significantly. With all microstrip lines designed in the 90-nm process, metal 1 ground planes are constructed from the unit cell mesh sketched in Fig. 7(a), corresponding to a metal density of approximately 65%. For lines constructed with metal 2 ground planes, the metal 2 mesh is positioned such as to cover the slots in the metal 1 mesh [Fig. 7(b)]. The two meshes are shunted together to increase the effective ground plane thickness, and reduce its resistance. A micrograph of the slotted ground plane from one of the short lines is presented in Fig. 8.

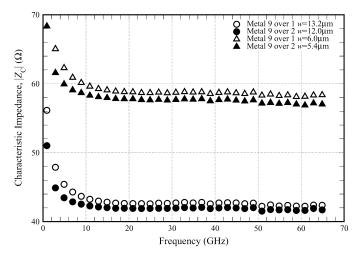

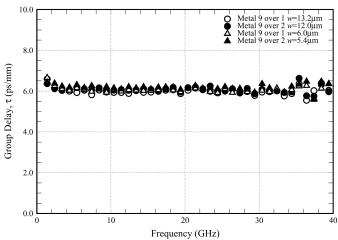

3) Characteristic Impedance and Dispersion in Lossy Lines: Fig. 9 shows that, with microstrip line configurations typically used in IC designs,  $Z_C$  exhibits a strong frequency dependence at frequencies below 10 GHz. Similar results are observed for the group delay below 2 GHz (Fig. 10). It should be emphasized that these nonidealities are neither artifacts of the measurement system nor of the de-embedding technique.

Fig. 8. Micrograph of a slotted ground plane.

Fig. 9. Characteristic impedance as a function of frequency for transmission lines fabricated with a metal 9 conductor in the 90-nm process.

$Z_C$  and  $\gamma$  can be expressed in terms of RLGC parameters using

$$Z_C = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \tag{11}$$

$$\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)}.$$

(12)

At sufficiently high frequencies ( $\omega L\gg R$  and  $\omega C\gg G$ ), we have  $Z_C\approx \sqrt{L/C}$  and  $\beta\approx \sqrt{LC}$ . Below these frequencies,  $Z_C$  and  $\tau\equiv \partial\beta/\partial\omega$  are, in general, frequency dependent. For example, as  $\omega\to 0$ , the "dc" characteristic impedance is given by  $Z_C\approx \sqrt{R/G}$ .

Assuming little frequency dependence of the RLGC parameters, it is possible to obtain frequency independent values for both  $Z_C$  and  $\tau$  through circuit design, by ensuring that R/G = L/C. Such distortionless lines are preferable for broad-band digital circuits, and can normally be realized by periodically loading the line with either a series inductor [17] or a parallel resistor [18]. The resistive solution increases G, making it possible for the designer to set  $Z_C$  to a desired value, whereas increasing L inevitably pulls it closer to the (typically large) "dc" value.

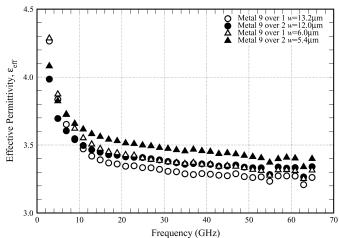

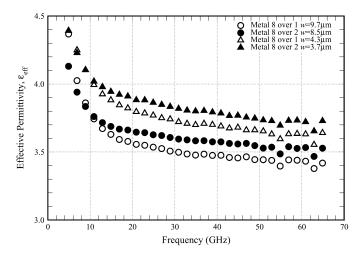

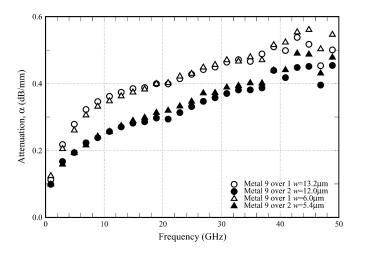

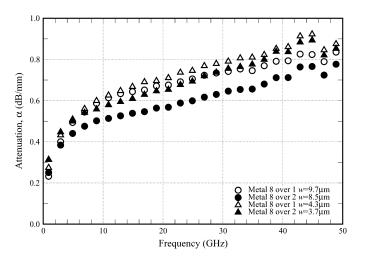

4) Impact of Materials and Geometry on Electrical Characteristics: A preliminary inspection of Figs. 11 and 12 indicates

Fig. 10. Group delay as a function of frequency for transmission lines fabricated with a metal 9 conductor in the 90-nm process.

Fig. 11. Effective permittivity as a function of frequency for transmission lines fabricated with a metal 9 conductor in the 90-nm process.

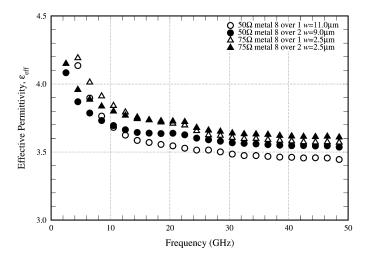

Fig. 12. Effective permittivity as a function of frequency for transmission lines fabricated with a metal 8 conductor in the 90-nm process.

that wider conductors lead to a smaller effective permittivity  $(\epsilon_{\text{eff}} \equiv (c(\beta/\omega))^2)$ . This is a direct result of the passivation layer having a much higher permittivity than the lower- $\kappa$  interlayer dielectrics (ILDs). Microstrip lines with wider conductors

Fig. 13. Attenuation as a function of frequency for transmission lines fabricated with a metal 9 conductor in the 90-nm process.

Fig. 14. Attenuation as a function of frequency for transmission lines fabricated with a metal 8 conductor in the 90-nm process.

more closely resemble parallel plate waveguides. As a consequence, less field components penetrate the higher- $\kappa$  passivation layers [17].

When compared to lines with metal 9 conductors, those designed with metal 8 conductors have a noticeably higher effective permittivity. This difference is mainly attributed to the fact that the higher- $\kappa$  passivation layer does not extend very far over the metal 9 conductor. Consequently, the low permittivity of air helps offset the high permittivity of the passivation layers. For lines designed with metal 8 conductors, the lower- $\kappa$  layer of air is now much farther away from the conductor surface. Moreover, relatively higher-permittivity dielectrics are used to fill the space of the absent metal 9 material. Combined, these factors cause the systematic jump in  $\epsilon_{\rm eff}$  observed between the lines using different conductor metals. This explanation is further confirmed by the spread in measured  $\epsilon_{\rm eff}$ . The lines designed with metal 8 conductors have a larger spread due to the larger difference in permittivities above and below the conductor.

In order to minimize losses, it is important to be able to identify the dominant source. Comparing Figs. 13 and 14, we can see that lines with metal 8 conductors are lossier than those realized with metal 9 conductors. This trend starts at low frequencies,

Fig. 15. Technology comparison of the attenuation in lines designed with the topmost conductor and a metal 1 ground plane.

Fig. 16. Technology comparison of the attenuation in lines designed with the topmost conductor and a metal 2 ground plane.

where a difference in dc resistance is readily apparent. The consistently lower dc resistance of the lines with metal 9 conductors is a direct result of the thicker metal 9 layer. Even the narrowest metal 9 line has a larger cross-sectional area than the widest one using metal 8.

A second trend is related to the ground plane and is made evident from the attenuation plots. As the frequency increases, the lines with a metal 1 ground plane exhibit more loss than those with a metal 2 ground plane. This can be explained by the larger effective thickness of the metal 2 ground planes which are shunted together with a metal 1 mesh. The only exception occurs for the narrowest line ( $w=3.7~\mu{\rm m}$ ), for which the conductor remains the dominant source of loss.

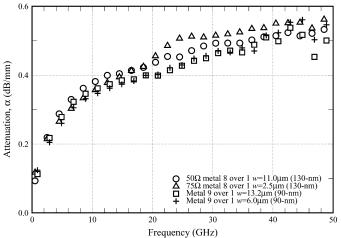

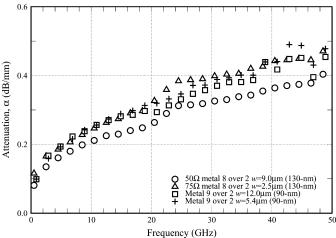

## C. Technology Comparison

In order to cover a larger device space, microstrip lines fabricated in a 130-nm RF-CMOS process were also characterized. Although the two processes have similar backend, they use slightly different ILD and metal thicknesses, as well as conductivities. The most noteworthy difference is that the 130-nm process does not feature lower- $\kappa$  dielectrics. To ensure a fair

Fig. 17. Effective permittivity as a function of frequency for transmission lines fabricated in the 130-nm process.

comparison, only lines with conductors designed in the top-most metal layers will be considered. These conductors are fabricated with a thickness of 3.3  $\mu$ m in both technologies.

Figs. 15 and 16 show a remarkable agreement between the attenuation versus frequency characteristics of the two technologies. The close match is attributed to the similar thicknesses of corresponding ground planes.

With respect to permittivity, Fig. 17 also shows a clear width dependence, as in Fig. 11. Since the 130-nm process does not have lower- $\kappa$  dielectrics, the extracted values of  $\epsilon_{\rm eff}$  are higher than those of Fig. 11.

#### IV. CONCLUSION

A new de-embedding technique which accurately removes pad parasitics and pad-line discontinuities was presented for the characterization of lossy IC transmission lines. It was found that line pairs as small as 600  $\mu$ m and 100  $\mu$ m provide adequate results if the pad parasitics are minimized. Measurements also indicate that, with the thick top metal layers available in RF-CMOS technologies, ground planes are often the dominant source of high frequency loss. Furthermore, the characteristic impedance and group delay of microstrip transmission lines are strongly frequency dependent up to 10 and 2 GHz, respectively. Therefore, it can be concluded that the dispersive behavior of interconnect lines in broad-band higher-speed digital circuits must be mitigated by periodically loading the signal lines.

#### ACKNOWLEDGMENT

The authors would like to thank the R & D SPICE department at TSMC for providing access to the 90-nm RF-CMOS technology and Quake Technologies for measured data of the transmission lines fabricated in the 130-nm RF-CMOS process. Additional thanks go to A. Hazneci and M. Gordon for the meandering microstrip line design and measurement, and Dr. D. McPherson of Quake Technologies for his many suggestions and insight on transmission lines.

#### REFERENCES

- [1] K. Ohata, K. Maruhashi, M. Ito, S. Kishimoto, K. Ikuina, T. Hashiguchi, N. Takahashi, and S. Iwanaga, "Wireless 1.25 Gb/s transceiver module at 60 GHz-band," in *Proc. IEEE SSCC*, vol. 1, Feb. 3–7, 2002, pp. 298–268.

- [2] T. O. Dickson, E. Laskin, I. Khalid, R. Beerkens, J. Xie, B. Karajica, and S. P. Voinigescu, "An 80-Gb/s, 2<sup>31</sup> – 1 pseudo-random binary sequence generator in SiGe BiCMOS technology," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2735–2745, Dec. 2005.

- [3] S. Reynolds, B. Floyd, U. Pfeiffer, and T. Zwick, "60 GHz transceiver circuits in SiGe bipolar technology," in *Proc. IEEE SSCC*, vol. 1, Feb. 15–19, 2004, pp. 442–538.

- [4] A. Hazneci and S. P. Voinigescu, "A 49-Gb/s, 7-tap transversal filter in 0.18 μm SiGe BiCMOS for backplane equalization," in *Proc. IEEE CSICS*, Oct. 24–27, 2004, pp. 101–104.

- [5] A. Mangan, "Millimeter-Wave Device Characterization for Nano-CMOS IC Design," Master's thesis, Univ. Toronto, ON, Canada, 2005.

- [6] P. J. van Wijnen, H. R. Classen, and E. A. Wolsheimer, "A new straight-forward calibration and correction procedure for "on wafer" high frequency S-parameter measurements (45 MHz-18 GHz)," in *Proc. IEEE BCTM*, Sep. 1987, pp. 70–73.

- [7] W. R. Eisenstadt and Y. Eo, "S-parameter-based 1C interconnect transmission line characterization," *IEEE Trans. Comp., Hybrids, Manufact. Technol.*, vol. 15, no. 4, pp. 483–490, Aug. 1992.

- [8] P. Heymann, H. Prinzler, and F. Schnieder, "De-embedding of MMIC transmission-line measurements,", vol. 2, pp. 23–27, May 2005.

- [9] J. Song, F. Ling, G. Flynn, W. Blood, and E. Demircan, "A de-embedding technique for interconnects," in *Proc. IEEE Electr. Perf. Electron. Packag. Meeting*, Oct. 29–31, 2001, p. 129 132.

- [10] N. R. Franzen and R. A. Speciale, "A new procedure for system calibration and error removal in automated S-parameter measurements," in *Proc. 5th Eur. Microw. Conf.*, Sep. 1–4, 1975, pp. 69–73.

- [11] R. B. Marks and D. F. Williams, "Characteristic impedance determination using propagation constant measurement," *IEEE Microw. Guided Wave Lett.*, vol. 1, no. 6, pp. 141–143, Jun. 1991.

- [12] T.-M. Winkel, L. S. Dutta, and H. Grabinski, "An accurate determination of the characteristic impedance of lossy lines on chips based on high frequency S-parameter measurements," in Proc. IEEE MultiChip Module Conf., Feb. 6–7, 1996, pp. 190–195.

- [13] D. F. Williams, U. Arz, and H. Grabinski, "Accurate characteristic impedance measurement on silicon," MTT-S IMS Dig., vol. 3, pp. 1917–1920, Jun. 7–12, 1998.

- [14] A. Bracale, D. Pasquet, J. L. Gautier, N. Pel, V. Ferlet, and J. L. Pelloie, "A new method for characteristic impedance determination on lossy substrate," MTT-S IMS Dig., vol. 3, pp. 1481–1484, Jun. 11–16, 2000.

- [15] J.-H. Kim and D.-H. Han, "Hybrid method for frequency-dependent lossy coupled transmission line characterization and modeling," in *Proc. IEEE 12th Electr. Perf. Electron. Packag. Meeting*, Oct. 27–29, 2003, pp. 239–242.

- [16] L. N. Dworsky, Modern Transmission Line Theory and Applications. New York: Wiley, 1979.

- [17] D. M. Pozar, Microwave Engineering, 2nd ed. New York: Wiley, 2005.

- [18] D. S. McPherson, H. Tran, and P. Popescu, "A 10 Gb/s equalizer with integrated clock and data recovery for optical communication systems," *Int. J. High Speed Electron, and Syst.*, vol. 15, no. 3, 2005.

Alain M. Mangan received the B.A.Sc. degree in computer engineering from the University of Ottawa, Ottawa, ON, Canada, in 2003, and the M.A.Sc. degree in electrical and computer engineering from the University of Toronto, Toronto, ON, Canada, in 2005.

In 2001 and 2002, he performed device characterization work on 130-nm RF-CMOS, and 180-nm BiCMOS processes at Quake Technologies, Ottawa, for two work terms. His research interests include mm-wave device characterization for higher-frequency IC design.

**Sorin P. Voinigescu** (S'92-M'91-SM'02) received the M.Sc. degree in electronics from the Polytechnic Institute of Bucharest, Bucharest, Romania, in 1984 and the Ph.D. degree in electrical and computer engineering from the University of Toronto, Toronto, ON, Canada, in 1994.

From 1984 to 1991, he worked in research and development and academia in Bucharest, where he designed and lectured on microwave semiconductor devices and integrated circuits. From 1994 to 2002, he was with Nortel Networks, and Quake Technologies

in Ottawa, ON, Canada, where he was responsible for projects in higher-frequency characterization and statistical scalable compact model development for Si, SiGe, and III-V devices. He also lead the design and product development of wireless and optical fiber building blocks and transceivers in these technologies. In September 2002, he joined the Department of Electrical and Computer Engineering, University of Toronto, as an Associate Professor. He has authored or coauthored over 60 refereed and invited technical papers spanning the simulation, modeling, design, and fabrication of GaAs-, InP-, and Si-based heterostructure devices and circuits. His research and teaching interests focus on nano-scale semiconductor devices and their application in integrated circuits at frequencies beyond 100 GHz.

Dr. Voinigescu received Nortel's President Award for Innovation in 1996. He is a corecipient of the Best Paper Award at the 2001 IEEE Custom Integrated Circuits Conference.

Ming-Ta Yang (S'93–M'99) was born in Tainan, Taiwan, R.O.C., in 1966. He received the B.S and M.S. degrees in physics and applied physics from Chung-Yuan University, Chung-Li, Taiwan, R.O.C., in 1989 and 1992, respectively. He received the Ph.D. degree in electrical engineering from the National Central University, Chung-Li, Taiwan, R.O.C., in 1995. His Ph.D. dissertation was focused on the characterization of AlGaAs/InGaAs doped-channel heterostructure FETs and its application in monolithic microwave integrated circuit (MMICs).

In 1995, he joined the Mosel Vitelic Inc., Hsinchu, Taiwan, R.O.C., where he worked on VLSI advanced technology development. He then joined the Taiwan Semiconductor Manufacture Company, Ltd., in 1998, where he setup a higher-frequency characterization laboratory and organized a team responsible for the development of characterization techniques and SPICE models for both mixed-signal and RF applications. His current research interests include the development of advanced HF characterization and modeling of devices in RF CMOS and higher-speed SiGe HBT BiCMOS technologies.

Dr. Yang has served on the advisory Workshop Committees of Compact Modeling for RF/Microwave Applications (CMRF) in 2004 and 2005.

**Mihai Tazlauanu** received the Ph.D. degree in electrical engineering from the Polytechnic University of Bucharest, Bucharest, Romania, in 1995 and the Ph.D. degree in physics from the University of Montreal, Montreal, QC, Canada, in 1997.

For ten years, he was with the Quality and Reliability Department, Research and Development Institute for Microelectronics, Bucharest. In 1996, he joined Semiconductor Insights, Kanata, Canada, where he was involved in process analysis and the development of leading-edge semiconductor

technologies. Since 2001 he has been with Quake Technologies, Ottawa, ON Canada, where he has been responsible for device evaluation and modeling as well as reliability qualification. His current research interests include RF model extraction for active and passive devices produced in advanced Si, Si-Ge and III-V processes.