# **Dependency of Tunneling Field-Effect Transistor** (TFET) Characteristics on Operation Regions

Min Jin Lee and Woo Young Choi

Abstract—In this paper, two competing mechanisms determining drain current of tunneling field-effect transistors (TFETs) have been investigated such as band-to-band tunneling and drift. Based on the results, the characteristics of TFETs have been discussed in the tunneling-dominant and driftdominant region.

*Index Terms*—Tunneling field-effect transistor, bandto-band tunneling, drift, tunnel resistance, channel resistance

### I. INTRODUCTION

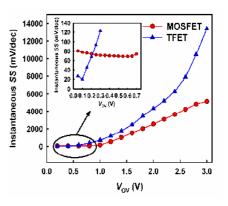

A TFET is considered as one of the most promising candidates to replace a MOSFET. It is because the subtreshold swing (SS) of the TFET can be smaller than 60 mV/dec at room temperature, which is the physical limit of the MOSFET [1-4]. However, the TFET has suffered from smaller on current ( $I_{ON}$ ) than the MOSFET at the same channel length ( $L_{CH}$ ). It is originated from the fact that the SS of the TFET is a function of the gate voltage ( $V_{GS}$ ) unlike that of the MOSFET [2] and the physical reason is the large tunneling barrier. Fig. 1 shows that the TFET has a smaller instantaneous SS than the MOSFET at low overdrive voltage ( $V_{OV}$ ).  $V_{OV}$  is defined as the difference between  $V_{GS}$  and threshold voltage ( $V_T$ ). In this work,  $V_T$  of TFETs is defined as  $V_{GS}$ when drain current ( $I_{DS}$ ) is 10<sup>-15</sup> A/µm. However, at high

Manuscript received Aug. 2, 2011; revised Oct. 18, 2011.

Department of Electronic Engineering, R821A, Sogang University, 35 Baekbeom-ro (Sinsu-dong), Mapo-gu, Seoul 121-742, Korea E-mail : wchoi@sogang.ac.kr  $V_{\rm OV}$ , the instantaneous SS of the TFET increases more abruptly than that of the MOSFET. It is problematic in that  $I_{\rm ON}$  of the TFET cannot exceed that of the MOSFET.

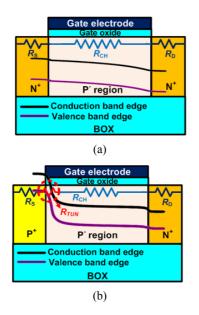

Fig. 2 compares the on resistance  $(R_{ON})$  of the MOSFET and TFET. The  $R_{ON}$  of the MOSFET consists of source resistance  $(R_S)$ , drain resistance  $(R_D)$  and channel resistance ( $R_{\rm CH}$ ). On the other hand, the  $R_{\rm ON}$  of the TFET has an additional tunnel resistance ( $R_{TUN}$ ).  $R_{CH}$ is determined by drift mechanism which is related to channel mobility.  $R_{\text{TUN}}$  is determined by band-to-band tunneling mechanism which is related to the tunneling barrier between the source and channel region. It should be noted that  $R_{ON}$  of the TFET has both  $R_{CH}$  and  $R_{TUN}$ . It means that  $I_{DS}$  of the TFET is determined by both drift and band-to-band tunneling while  $I_{DS}$  of MOSFETs is determined only by drift mechanism. Thus, it can be inferred that TFETs can have two different operating regions depending on the values of  $R_{\rm CH}$  and  $R_{\rm TUN}$ . When  $R_{\text{TUN}}$  is dominant, TFETs are operated in the tunnelingdominant region where band-to-band tunneling determines  $I_{\rm DS}$ . When  $R_{\rm CH}$  is dominant, TFETs are operated in the

**Fig. 1.** Instantaneous *SS* of a 1-µm MOSFET and TFET. Inset figure provides fine-scale resolution.

Fig. 2.  $R_{ON}$  components of (a) a MOSFET and (b) TFET.

drift-dominant region where drift mechanism determines  $I_{\text{DS}}$ .

In this paper, we have adjusted  $R_{\text{TUN}}$  and  $R_{\text{CH}}$  by performing device simulation in order to investigate the electrical characteristics of tunneling-dominant and driftdominant TFETs. This paper consists of two parts. First, the extraction method of  $R_{\text{TUN}}$ ,  $R_{\text{CH}}$  and  $R_{\text{SD}}$  is explained.  $R_{\text{SD}}$  is defined as the sum of  $R_{\text{S}}$  and  $R_{\text{D}}$ . Second, the electrical characteristics of TFETs will be discussed in the tunneling-dominant and drift-dominant region.

# II. EXTRACTION METHOD OF R<sub>on</sub> Components

Single-gate silicon-on-insulator (SOI) TFETs have been simulated by using Silvaco ATLAS [5]. Nonlocal band-to-band tunneling [6], doping and temperature dependent mobility model, band-gap narrowing, Fermi-Dirac and Shockley-Read-Hall recombination model have been used in the simulation. The simulated TFET has a gate oxide thickness of 2 nm, a channel width  $(W_{CH})$  of 1 µm, a buried oxide thickness of 150 nm and an SOI layer thickness of 50 nm. N<sup>+</sup> poly-Si gate is used. The doping concentrations of the channel  $(N_B)$ , source  $(N_S)$  and drain region  $(N_D)$  are 5 x 10<sup>17</sup>, 1 x 10<sup>19</sup> and 1 x 10<sup>19</sup> cm<sup>-3</sup>, respectively. Quantum mesh has been used at the surface of the SOI layer.

For quantitative analysis, each component of  $R_{\rm ON}$  has

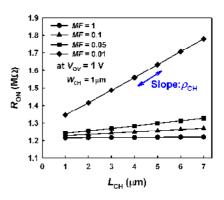

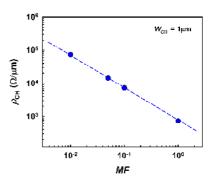

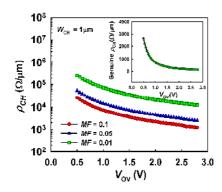

been extracted. In the first place, Fig. 3 shows the extraction method of  $R_{CH}$ .  $R_{ON}$  is plotted by dividing  $I_{DS}$  by the drain voltage ( $V_{DS}$ ) from TFETs with various  $L_{CH}$ 's.  $V_{OV}$  and  $V_{DS}$  are fixed at 1 and 0.1 V, respectively. The line slope in Fig. 3 indicates  $R_{CH}$  per  $L_{CH}$  ( $\rho_{CH}$ ). However, the problem of this method is that the line slope is too small to measure because the ratio of  $R_{CH}$  to  $R_{ON}$  is extremely small. It makes the accurate extraction of  $R_{CH}$  difficult. Thus, for higher accuracy, we have decreased channel mobility by a factor of 1, 0.1, 0.05 and 0.01. Those factors are defined as mobility factor (*MF*) in this paper. It means that  $R_{CH}$  increases by a factor of 1, 10, 20 and 100 because  $R_{CH}$  is inversely proportional to channel mobility. By adjusting *MF*,  $\rho_{CH}$  can be extracted accurately as shown in Fig. 4.

For example, at the same  $V_{\rm OV}$ , when channel mobility decreases by a factor of 10,  $\rho_{\rm CH}$  becomes 10x larger. In order to extract the genuine value of  $\rho_{\rm CH}$  which is defined as  $\rho_{\rm CH}$  when *MF* is 1, the extracted  $\rho_{\rm CH}$  needs to be calibrated by the reciprocal of *MF*. Fig. 5 shows extracted  $\rho_{\rm CH}$ 's with various *MF*'s. When calibrated by the reciprocal of *MF*'s, genuine  $\rho_{\rm CH}$ 's are located in the

**Fig. 3.**  $R_{\rm ON}$  vs.  $L_{\rm CH}$  graph in order to extract  $R_{\rm CH}$ .

**Fig. 4.**  $\rho_{\rm CH}$  with the variation of *MF*.

same curve as shown in the inset of Fig. 5. It confirms the validity of the proposed extraction method. Next,  $R_{SD}$ is extracted. We use the fact that *MF*'s affect  $R_{CH}$  and  $R_{SD}$  regardless of  $R_{TUN}$ . Depending on the value of *MF*,  $R_{ON}$ 's are written as

$$R_{\text{ON}(MF=1.0)} = R_{\text{CH}(MF=1.0)} + R_{\text{SD}(MF=1.0)} + R_{\text{TUN}}$$

(1a)

$$R_{\text{ON}(MF=0.5)} = R_{\text{CH}(MF=0.5)} + R_{\text{SD}(MF=0.5)} + R_{\text{TUN}}$$

=  $2R_{\text{CH}(MF=1.0)} + 2R_{\text{SD}(MF=1.0)} + R_{\text{TUN}}$  (1b)

When Eq. (1a) is subtracted from Eq. (1b),  $R_{TUN}$  disappears while  $R_{CH}$  and  $R_{SD}$  remain as follows:

$$R_{\text{ON}(MF=0.5)} - R_{\text{ON}(MF=1.0)} = R_{\text{CH}(MF=1.0)} + R_{\text{SD}(MF=1.0)}(2)$$

$R_{\rm SD}$  is derived as

$$R_{\text{SD}(MF=1.0)} = R_{\text{ON}(MF=0.5)} - R_{\text{ON}(MF=1.0)} - R_{\text{CH}(MF=1.0)} (3)$$

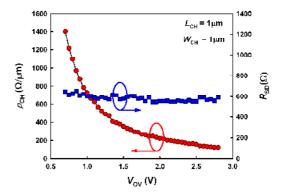

Fig. 6 shows that the average value of extracted  $R_{\rm SD}$  is 588  $\Omega$  and constant regardless of  $V_{\rm OV}$ . Also, as  $V_{\rm OV}$ increases,  $R_{\rm CH}$  decreases, which makes  $R_{\rm SD}$  larger than  $R_{\rm CH}$ . Finally,  $R_{\rm TUN}$  is extracted as follows:

$$R_{\rm TUN} = R_{\rm ON} - R_{\rm CH} - R_{\rm SD} \tag{4}$$

Based on the abovementioned results, we defined intrinsic  $R_{ON}$  ( $R_{ON int}$ ), which excludes  $R_{SD}$  as

$$R_{\rm ON int} = R_{\rm ON} - R_{\rm SD} = R_{\rm TUN} + R_{\rm CH}$$

(5)

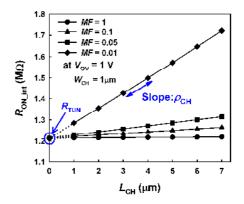

Fig. 7 shows  $R_{\rm ON int}$  as a function of  $L_{\rm CH}$  for the

**Fig. 5.**  $\rho_{\text{CH}}$  with the variation of  $V_{\text{OV}}$  at  $V_{\text{DS}} = 0.1$  V. Also, inset figure shows genuine  $\rho_{\text{CH}}$  which is calibrated by the reciprocal of *MF*.

**Fig. 6.** Comparison of  $\rho_{\rm CH}$  and  $R_{\rm SD}$  extracted from a 1-µm TFET at  $V_{\rm DS} = 0.1$  V.

Fig. 7.  $R_{ON_{int}}$  vs.  $L_{CH}$  graph in order to extract  $R_{TUN}$ .

extraction of  $R_{\text{TUN}}$ . Unlike Fig. 3, every line meets at one y-intercept which indicates  $R_{\text{TUN}}$  because *MF*'s only affect  $R_{\text{CH}}$  rather than  $R_{\text{TUN}}$ . In order to confirm the validity, we compared extracted  $R_{\text{TUN}}$  with theoretical values which is calculated by the following equation [7]:

$$R_{TUN} = A \frac{4\pi^{3} \hbar^{2} W_{TUN}}{\sqrt{2m^{*} q^{3} \sqrt{E_{G}}}} \exp(\frac{4\sqrt{2m^{*} W_{TUN}} \sqrt{E_{G}}}{3q\hbar})$$

(6)

where A is constant, q is elementary charge,  $m^*$  is electron tunneling effective mass,  $W_{\text{TUN}}$  is tunneling barrier width,  $E_{\text{G}}$  is bandgap energy and  $\hbar$  is Dirac constant. For the calculation of theoretical values, As  $V_{\text{OV}}$  increases,  $W_{\text{TUN}}$  decreases and its decreasing rate becomes smaller as shown in Fig. 8(a).  $W_{\text{TUN}}$  have been extracted automatically at each  $V_{\text{OV}}$  by using device simulation as follows. From the simulated energy band diagrams, the minimum distance between valence band and conduction band has been extracted as shown in inset of Fig. 8(a). A and  $m^*$  have been calibrated carefully to fit extracted  $R_{\text{TUN}}$  with the theoretical value. Fig. 8(b) shows

**Fig. 8.** (a) Extracted  $W_{\text{TUN}}$  with the variation of  $V_{\text{OV}}$  at  $V_{\text{DS}} = 0.1$  V. Inset figure shows the definition of  $W_{\text{TUN}}$ . (b)  $R_{\text{TUN}}$  compared with theoretical values and inset figure shows the ratio of  $R_{\text{TUN}}$  to  $R_{\text{CH}}$  with the variation of  $V_{\text{OV}}$  at  $V_{\text{DS}} = 0.1$  V.

that the extracted  $R_{\text{TUN}}$  fits theoretical  $R_{\text{TUN}}$  within 5.4%. Thus, it is confirmed that  $R_{\text{TUN}}$  is related only to tunneling mechanism rather than drift mechanism.

Although  $R_{\text{TUN}}$  is not a function of  $V_{\text{TUN}}$  from Eq. (6),  $V_{\text{TUN}}$  affects  $W_{\text{TUN}}$  and  $R_{\text{TUN}}$  actually.  $V_{\text{TUN}}$  means the voltage drop across the tunneling junction which is defined as

$$V_{TUN} = \frac{R_{TUN}}{R_{SD} + R_{TUN} + R_{CH}} V_{DS}$$

(7).

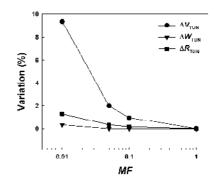

As *MF* decreases,  $R_{\text{CH}}$  increases and  $V_{\text{TUN}}$  decreases. It increases  $W_{\text{TUN}}$  and  $R_{\text{TUN}}$ . In order to further confirm the validity of the extraction method, we have observed  $\Delta V_{\text{TUN}}$ ,  $\Delta W_{\text{TUN}}$  and  $\Delta R_{\text{TUN}}$  with the variation of *MF* at  $V_{\text{OV}} = 1$  V. Inset of Fig. 8(b) shows the ratio of  $R_{\text{TUN}}$  to  $R_{\text{CH}}$ . As shown in inset of Fig. 8(b), the ratio of  $R_{\text{TUN}}$  to  $R_{\text{CH}}$  is minimum at  $V_{\text{OV}} = 1$  V, which is the worst case.  $V_{\text{TUN}}$  at MF = 0.01 is 91% of  $V_{\text{TUN}}$  at MF = 1 as shown in Fig. 9. However,  $\Delta W_{\text{TUN}}$  and  $\Delta R_{\text{TUN}}$  are smaller than  $\Delta V_{\text{TUN}}$ . Because  $W_{\text{TUN}}$  is nearly saturated at  $V_{\text{OV}} = 1$  V as

**Fig. 9.**  $\Delta V_{\text{TUN}}$ ,  $\Delta W_{\text{TUN}}$  and  $\Delta R_{\text{TUN}}$  with the variation of *MF*.

shown in Fig. 8(a),  $W_{\text{TUN}}$  shows little change with the variation of  $V_{\text{TUN}}$ . Thus,  $\Delta R_{\text{TUN}}$  is 1% and it confirms the validity of the proposed extraction method.

# III. TUNNELING-DOMINANT TFETS VS. DRIFT-DOMINANT TFETS

From now on, the electrical characteristics of TFETs will be investigated in the tunneling-dominant and driftdominant region. In the first place, tunneling-dominant TFETs will be discussed because most of TFETs from literature are classified into tunneling-dominant TFETs. Simulation conditions of tunneling-dominant TFETs are summarized in Table 1. It is observed that in the case of tunneling dominant TFET,  $R_{\text{TUN}}$  is ~2000x larger than  $R_{\text{CH}}$  as shown inset of Fig. 8(b). In the case of tunnelingdominant TFETs,  $R_{\text{TUN}}$  is a dominant factor determining  $R_{\text{ON}}$  and instantaneous *SS* becomes larger as  $V_{\text{OV}}$ increases. It means that the tunneling-dominant TFET may have lower  $I_{\text{ON}}$  than the MOSFET even if the former has lower instantaneous *SS* than the latter at low  $V_{\text{OV}}$ . The  $I_{\text{ON}}$  of the TFET is lower than the MOSFET with the

Table 1. Simulation conditions of tunneling-dominant and drift-dominant TFET

|                                        | Tunneling-dominant                                               | Drift-dominant |

|----------------------------------------|------------------------------------------------------------------|----------------|

| MF                                     | 1                                                                | 1              |

| m <sup>*</sup> factor                  | 1                                                                | 0.15           |

| L <sub>CH</sub>                        | 1 μm                                                             |                |

| Gate oxide thickness                   | 2 nm                                                             |                |

| Channel width                          | 1 μm                                                             |                |

| Buried oxide<br>thickness              | 150 nm                                                           |                |

| SOI layer thickness                    | 50 nm                                                            |                |

| Gate material                          | $N^+$ poly-Si                                                    |                |

| $N_{\rm B}, N_{\rm S}$ and $N_{\rm D}$ | 5 x $10^{17}$ , 1 x $10^{19}$ and 1 x $10^{19}$ cm <sup>-3</sup> |                |

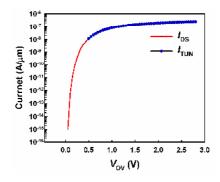

same  $L_{CH}$ , which due to  $R_{TUN}$  rather than  $R_{CH}$  because  $I_{DS}$  of the tunneling-dominant TFET is determined only by band-to-band tunneling. Fig. 10 shows that  $I_{DS}$  matches the tunneling current ( $I_{TUN}$ ) well which is defined as

$$I_{\rm TUN} = V_{\rm DS} / R_{\rm TUN} \tag{8}$$

As explained in Eq. (6),  $R_{\text{TUN}}$  is a strong function of  $W_{\text{TUN}}$ . As  $V_{\text{OV}}$  increases,  $W_{\text{TUN}}$  decreases and its decreasing rate becomes smaller as shown in Fig. 8a. It makes  $R_{\text{TUN}}$  and  $R_{\text{ON}}$  decrease less abruptly as  $V_{\text{OV}}$  increases, which causes  $I_{\text{DS}}$  saturation at high  $V_{\text{OV}}$ .

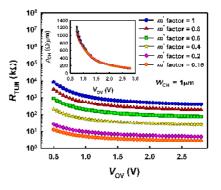

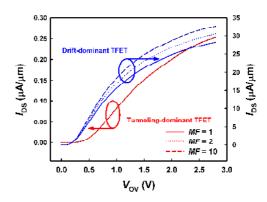

Conventional TFETs have suffered from low  $I_{ON}$ because they are operated in the tunneling-dominant region. Thus, the best way of boosting  $I_{\rm ON}$  is reducing  $R_{\text{TUN}}$ . Some pioneering research results have been reported for the purpose of low  $R_{\text{TUN}}$  [3, 8]. As a result, recently,  $I_{\rm ON}$  of TFETs have risen at a steady pace [9, 10]. In particular, III-V TFETs may achieve larger tunneling current compared with Si TFETs due to their smaller bandgap energy and smaller electron mass [11, 12]. Further, TFETs with gate-drain overlap structures to suppress ambipolar behavior will have larger  $R_{\rm CH}$  than MOSFETs, which makes drift-dominant TFETs more feasible [13]. If  $R_{TUN}$  is reduced successfully down to the  $R_{\rm CH}$  in the future, TFETs will be operated in the driftdominant region where  $I_{DS}$  is determined by drift mechanism unlike tunneling-dominant TFETs. In the drift-dominant region, TFETs show electrical characteristics similar to MOSFETs. For the investigation of driftdominant TFETs,  $m^*$  has been 1x, 0.8x, 0.6x, 0.4x, 0.2x and 0.15x decreased. Fig. 11 shows that  $R_{\text{TUN}}$  decreases as  $m^*$  factor decreases while inset of Fig. 11 shows that  $\rho_{\rm CH}$  is constant regardless of  $m^*$  factor. According to

**Fig. 10.**  $I_{\text{DS}}$  compared with  $I_{\text{TUN}}$  of a tunneling-dominant TFET at  $V_{\text{DS}} = 0.1$  V.

**Fig. 11.** Extracted  $R_{\text{TUN}}$  with the variation of  $m^*$ . Also, inset figure shows  $\rho_{\text{CH}}$  of the reference TFET with the variation of  $m^*$ .

simulation results, when  $m^*$  factor is 0.15, the ratio of  $R_{\text{TUN}}$  to  $R_{\text{CH}}$  is ~10. It implies that  $I_{\text{DS}}$  is greatly affected by drift mechanism. Thus, in this work, the TFET whose  $m^*$  factor is less than 0.15 is defined as a drift-dominant TFET as shown in Table 1.

Drift-dominant TFETs are distinguished from tunneling-dominant TFETs in three viewpoints. First, drift-dominant TFETs are dominated by  $R_{CH}$ . Fig. 12(a)

**Fig. 12.** Extracted  $R_{\rm ON}$  and  $R_{\rm TUN}$  (a) in the case of tunnelingdominant and drift-dominant TFETs, (b) Extracted  $R_{\rm CH}$ compared with  $R_{\rm ON\_int}$  -  $R_{\rm TUN}$  in the drift-dominant TFETs shown in (a).

compare  $R_{\text{TUN}}$  with  $R_{\text{ON}}$  in the case of tunnelingdominant and drift-dominant TFETs. The drift-dominant

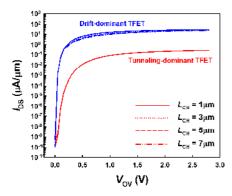

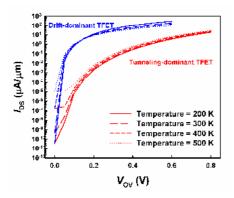

TFET shows considerable difference which is equal to  $R_{CH}$  as shown in Fig. 12(b). It proves that drift mechanism plays an important role in determining  $I_{DS}$  in the case of drift-dominant TFETs. Second,  $I_{DS}$  of tunneling-dominant TFETs is independent of  $L_{CH}$  while  $I_{DS}$  of drift-dominant TFETs is dependent on  $L_{CH}$  as shown in Fig. 13. Finally, tunneling-dominant and drift-dominant TFETs show different temperature dependence [14]. Fig. 14 shows that  $I_{DS}$  of tunneling-dominant TFETs increases as temperature increases. It is because of  $E_{G}$  reduction at elevated temperature. On the other hand,  $I_{DS}$  of drift-dominant TFETs decreases as temperature increases. It is because channel mobility is reduced with increasing temperature.

To sum up, currently, the best way of achieving large  $I_{\text{ON}}$  is the reduction of  $R_{\text{TUN}}$  because most of TFETs operate in the tunneling-dominant region. However,

**Fig. 13.** Dependence of transfer curves on  $L_{CH}$  in the case of tunneling-dominant and drift-dominant TFETs.

Fig. 14. Dependence of transfer curves on temperature in the case of tunneling-dominant and drift-dominant TFETs at  $V_{DS} = 0.9 \text{ V}.$

**Fig. 15.** Improvement of channel mobility in the case of tunneling-dominant and drift-dominant TFETs.

continuous reduction of  $R_{\text{TUN}}$  makes tunneling-dominant TFETs drift-dominant. Thus, for more  $I_{\text{ON}}$  boosting of drift-dominant TFETs, higher channel mobility will be necessary as in the case of conventional MOSFETs. Fig. 15 shows that channel mobility has no influence on  $I_{\text{DS}}$  in the tunneling-dominant TFET. However, in the case of the drift-dominant TFET,  $I_{\text{ON}}$  is affected by channel mobility.

### **IV. SUMMARY**

The extraction method of  $R_{\rm CH}$  and  $R_{\rm TUN}$  has been proposed for TFETs. Based on the results, we classified the operation region of TFETs into two categories: the tunneling-dominant and drift-dominant region. In the tunneling-dominant region, because  $I_{\rm DS}$  is dominated by  $R_{\rm TUN}$  rather than  $R_{\rm CH}$ , the instantaneous SS increases with increasing  $V_{\rm OV}$  which is related to  $W_{\rm TUN}$  saturation. The reduction of  $R_{\rm TUN}$  makes tunneling-dominant TFETs drift-dominant. In the drift-dominant region, like MOSFETs, mobility engineering will be necessary for higher  $I_{\rm ON}$ .

#### **ACKNOWLEDGMENTS**

This work was supported in part by the National Research Foundation (NRF) of Korea funded by the Ministry of Education, Science and Technology (MEST) under Grants 2011-0019107 (Development of Future-Oriented Technology) and 2011-0027471 (Mid-Career Researcher Program), in part by the Ministry of Knowledge Economy (MKE) of Korea under Grant NIPA-2011-C1090-1101-0003 (University ITRC support

program supervised by the National IT Industry Promotion Agency), in part by the IT R&D program of MKE/KEIT under Grant 10039174 (Technology Development of 22 nm level Foundry Device and PDK) and in part by the Sogang University Research Grant of 2010.

#### REFERENCES

- W. Y. Choi, B.-G. Park, J. D. Lee, T.-J. K. Liu, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec," *Electron Device Letters, IEEE*, Vol.28, No.8, pp.743-745, Aug., 2007.

- [2] Q. Zhang, W. Zhao, A. Seabaugh, "Lowsubtreshold-swing tunnel transistors," *Electron Device Letters, IEEE*, Vol.27, No.4, pp.297-300, Apr., 2006.

- [3] V. Nagavarapu, R. Jhaveri, J. C. S. Woo, "The tunnel source (PNPN) n-MOSFET: A novel high performance transistor," *Electron Devices, IEEE Transactions on*, Vol.55, No.4, pp.1013-1019, Apr., 2008.

- [4] S. Cho, M-C. Sun, G. Kim, T. I. Kamins, B-G. Park, J. S. H. Jr, "Design optimization of a type-I heterojunction tunneling field-effect transistor (I-HTFET) for high performance logic technology," *Journal of Semiconductor Technology and Science*, Vol.11, No.3, pp.182-189, Sep., 2011.

- [5] Atlas User's Manual, Silvaco, Santa Clara, CA, Jul., 2010.

- [6] E. O. Kane, "Theory of tunneling", J. Appl. Phys., Vol.32, No.1, pp.83-91, Jan., 1961.

- [7] R. B. Fair, H. W. Wivell, "Zener and avalanche breakdown in As-implanted low-voltage Si n-p junctions," *Electron Devices, IEEE Transactions* on, Vol.23, No.5, pp.512-518, May, 1976.

- [8] K. K. Bhuwalka, J. Schulze, I. Eisele, "Performance enhancement of vertical tunnel field-effect transistor with SiGe in the δp+ Layer," *Japanese Journal of Applied Physics*, Vol.43, No.7A, pp.4073-4078, Jul., 2004.

- [9] W.-Y. Loh, K. Jeon, C. Y. Kang, J. Oh, P. Patel, C. Smith, J. Barnett, C. Park, T.-J. King, H.-H. Tseng, P. Majhi, R. Jammy, C. Hu, "The sub-60 nm Si tunnel field effect transistors with Ion>100 μA/μm," in *Proc. Eur. Solid-State Device Res. Conf.*, pp.162-165, Sep., 2010.

- [10] H. Zhao, Y. Chen, Y. Wang, F. Zhou, F. Xue, J. Lee, "InGaAs tunneling field-effect-transistors with atomic-layer-deposited gate oxides," *Electron Devices, IEEE Transactions on*, Vol.58, No.9, pp.2990-2995, Sep., 2011.

- [11] S. Datta, "Compound semiconductor as CMOS channel material: Déjàvu or new paradigm?" in *Proc. 66th IEEE Device Res. Conf.*, pp.33-36, Jun., 2008.

- [12] A. Zubair, S. A. Siddiqui, O. F. Shoron, Q. D. M. Khosru, "Impact of bandgap and effective mass on the transport characteristics of tunneling FET," in *Proc. IEEE NMDC*, pp.47-51, Oct., 2010.

- [13] A. S. Verhulst, W. G. Vandenberghe, K. Maex, G. Groeseneken, "Tunnel field-effect transistor without gate-drain overlap," *Appl. Phys. Lett.*, Vol.91, No.5, p.053102, Jul., 2007.

- [14] P. F. Guo, L. T. Yang, Y. Yang, L. Fan, G. Q. Han, G. S. Samudra, Y. C. Yeo, "Tunneling field-effect transistor: Effect of strain and temperature on tunneling current," *Electron Device Letters, IEEE*, Vol.30, No.9, pp.981-983, Sep., 2009.

Min Jin Lee was born in Seoul, Korea, in 1987. She received the B.S. degree in 2010 from Sogang University, Seoul, Korea, where she is currently working toward the M.S. degree in the Department of Electronic Engineering. Her current research

interests include tunneling field-effect transistor (TFET), nanoscale novel devices and anti-fuse memory.

**Woo Young Choi** was born in Incheon, Korea, in 1978. He received the B.S., M.S. and Ph. D. degrees in the School of Electrical Engineering from Seoul National University, Seoul, Korea in 2000, 2002 and 2006, respectively. From 2006 to 2008, he

was with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, USA as a post-doctor. Since 2008, he has been a member of the faculty of Sogang University (Seoul, Korea), where he is currently an Assistant Professor with the Department of Electronic Engineering. He has authored or coauthored over 110 papers in international journals and conference proceedings and holds 15 Korean patents. His current research interests include fabrication, modeling, characterization and measurement of CMOS/ CMOS-compatible semiconductor devices and nanoelectromechanical (NEM) memory cells.