The Pennsylvania State University The Graduate School

#### DESIGN AND ANALYSIS OF SCHEDULING TECHNIQUES FOR THROUGHPUT PROCESSORS

A Dissertation in Computer Science and Engineering by Adwait Jog

$\bigodot$  2015 Adwait Jog

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

August 2015

The dissertation of Adwait Jog was reviewed and approved<sup>\*</sup> by the following:

Chita R. Das Distinguished Professor of Computer Science and Engineering Dissertation Advisor, Chair of Committee

Mahmut T. Kandemir Professor of Computer Science and Engineering Dissertation Co-Advisor

Yuan Xie Professor of Computer Science and Engineering

W. Kenneth Jenkins Professor of Electrical Engineering Department

Ravishankar Iyer Senior Principal Engineer, Intel Labs Special Member

Onur Mutlu Associate Professor of Electrical and Computer Engineering Carnegie Mellon University Special Member

Lee D. Coraor Associate Professor of Computer Science and Engineering Director of Academic Affairs

<sup>\*</sup>Signatures are on file in the Graduate School.

### Abstract

Throughput Processors such as Graphics Processing Units (GPUs) are becoming an inevitable part of every computing system because of their ability to accelerate applications consisting of abundant parallelism. They are not only used to accelerate big data analytics in cloud data centers or high-performance computing (HPC) systems, but are also employed in mobile and wearable devices for efficient execution of multimedia rich applications and smooth rendering of display. In spite of the highly parallel structure of GPUs and their ability to execute multiple threads concurrently, they are far from achieving their theoretically achievable peak performance. This is attributed to several reasons such as contention for limited shared resources (e.g., caches and memory), high control-flow divergence, and limited off-chip memory bandwidth. Another reason for the low utilization and subpar performance is that the current GPUs are not well-equipped to efficiently and fairly execute multiple applications concurrently, potentially originating from different users. This dissertation is focused on managing contention in GPUs for shared cache and memory resources caused by concurrently executing threads. This contention causes severe loss in performance, fairness, locality, and parallelism. To manage this contention, this dissertation proposes techniques that are employed at two different places: core and *memory*. First, this dissertation shows that by intelligently scheduling the threads at the *core*, the generated memory request patterns can be more amenable for existing resource management techniques such as cache replacement and memory scheduling as well as performance enhancement techniques such as data prefetching. Second, this dissertation shows that considering criticality and other application characteristics to schedule memory requests at the memory controller is an effective way to manage contention at the *memory*.

## **Table of Contents**

| List o     | of Fi | gures                                                         | x    |

|------------|-------|---------------------------------------------------------------|------|

| List o     | of Ta | bles                                                          | xv   |

| Ackn       | owle  | dgments                                                       | cvii |

| Chap<br>In |       | uction                                                        | 1    |

| Chap<br>Gı |       | cs Processing Units (GPUs): A Primer                          | 7    |

| Chap       | ter 3 | 6                                                             |      |

| Ca         | ache  | and Memory Aware Warp Scheduling Techniques                   | 12   |

| 3.1        | In    | roduction                                                     | 13   |

| 3.2        | 2 M   | otivation and Workload Analysis                               | 16   |

| 3.3        | B TI  | e OWL Scheduler                                               | 18   |

|            | 3.    | B.1 CTA-Aware: CTA-aware two-level warp scheduling            | 18   |

|            | 3.    | B.2 CTA-Aware-Locality: Locality aware warp scheduling        | 20   |

|            | 3.3   | 3.3 <i>CTA-Aware-Locality-BLP</i> : BLP aware warp scheduling | 24   |

|               | 3.3.4   | Opportu   | unistic Prefetching                                                   | 28 |

|---------------|---------|-----------|-----------------------------------------------------------------------|----|

|               | 3.3.5   | Hardwar   | re Overheads                                                          | 30 |

| 3.4           | Exper   | imental N | fethodology                                                           | 31 |

|               | 3.4.1   | Workloa   | ds and Metrics                                                        | 31 |

| 3.5           | Exper   | imental R | esults                                                                | 32 |

|               | 3.5.1   | Perform   | ance Results                                                          | 33 |

|               | 3.5.2   | Sensitivi | ty Studies                                                            | 36 |

| 3.6           | Relate  | ed Work   |                                                                       | 37 |

| 3.7           | Chapt   | er Summa  | ary                                                                   | 40 |

| Chapte<br>Pre | fetch A |           | arp Scheduling Techniques                                             | 41 |

| 4.1           | Introd  | uction .  |                                                                       | 42 |

| 4.2           |         |           | Scheduling and Prefetching: Motivation and Basic                      | 46 |

|               | 4.2.1   | Shortcon  | nings of the State-of-the-Art Warp Schedulers                         | 47 |

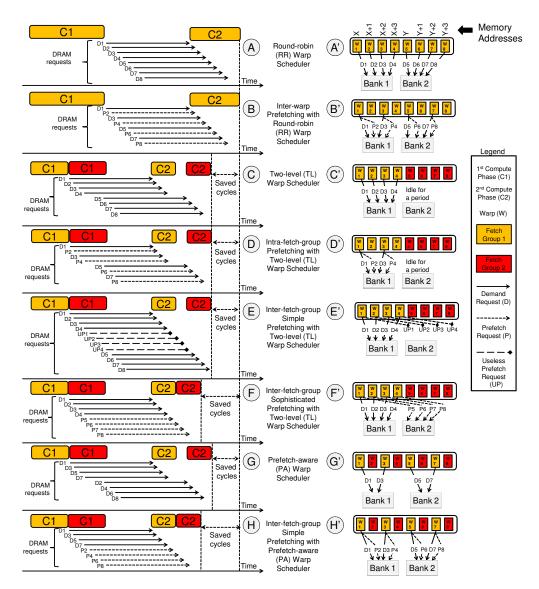

|               |         | 4.2.1.1   | Round-robin (RR) warp scheduling                                      | 47 |

|               |         | 4.2.1.2   | Round-robin (RR) warp scheduling and inter-warp prefetching           | 48 |

|               |         | 4.2.1.3   | Two-level (TL) warp scheduling                                        | 49 |

|               |         | 4.2.1.4   | Two-level (TL) warp scheduling and intra-fetch-<br>group prefetching  | 50 |

|               |         | 4.2.1.5   | Two-level (TL) warp scheduling and inter-fetch-<br>group prefetching  | 50 |

|               | 4.2.2   | Orchesti  | cating Warp Scheduling and Data Prefetching                           | 51 |

|               |         | 4.2.2.1   | Prefetch-aware (PA) warp scheduling                                   | 51 |

|               |         | 4.2.2.2   | Prefetch-aware (PA) warp scheduling and inter-fetch-group prefetching | 52 |

| 4.3          | Mecha  | anism and Implementation                            | 53 |

|--------------|--------|-----------------------------------------------------|----|

|              | 4.3.1  | Prefetch-Aware Scheduling Mechanism                 | 53 |

|              | 4.3.2  | Spatial Locality Detection Based Prefetching        | 54 |

|              | 4.3.3  | Hardware Overhead                                   | 57 |

| 4.4          | Evalu  | ation Methodology                                   | 58 |

| 4.5          | Exper  | imental Results                                     | 59 |

| 4.6          | Relate | ed Work                                             | 64 |

| 4.7          | Chapt  | er Summary                                          | 66 |

| Chapt<br>Cri |        | Aware Memory Scheduling Techniques                  | 68 |

| 5.1          | Introd | luction                                             | 69 |

| 5.2          | Backg  | round and Motivation                                | 72 |

| 5.3          | Core   | Criticality: Basic Ideas and Metrics                | 74 |

|              | 5.3.1  | Latency Tolerance as a Measure of Core-Criticality  | 74 |

|              | 5.3.2  | Understanding Variation of Criticality Across Cores | 76 |

|              |        | 5.3.2.1 Analysis of the PCC metric                  | 77 |

| 5.4          | Analy  | zing Criticality in the Memory System               | 78 |

| 5.5          | CLAN   | AS: Design and Implementation                       | 81 |

|              | 5.5.1  | Design Challenges of CLAMS                          | 81 |

|              | 5.5.2  | Design Overview of CLAMS                            | 82 |

|              | 5.5.3  | Design of Static-CLAMS Memory Scheduler             | 84 |

|              | 5.5.4  | Design of Semi-Dyn-CLAMS Memory Scheduler           | 85 |

|              | 5.5.5  | Design of Dyn-CLAMS Memory Scheduler                | 87 |

|              | 5.5.6  | Hardware Overheads                                  | 89 |

| 5.6          | Evalu  | ation Methodology                                   | 91 |

| 5.7         | Experi | imental Results                                             | 91 |

|-------------|--------|-------------------------------------------------------------|----|

| 5.8         | Relate | d Work                                                      | 96 |

| 5.9         | Chapt  | er Summary                                                  | 98 |

| apte<br>Con | curren | nt Kernel Execution in GPUs: Problems and Some<br>Solutions | 99 |

| 6.1         | Introd | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$             | 00 |

| 6.2         | Backg  | round and Experimental Methodology                          | 02 |

|             | 6.2.1  | Baseline GPU Architecture                                   | 03 |

|             | 6.2.2  | Evaluation Methodology                                      | 04 |

|             | 6.2.3  | Evaluation Metrics                                          | 05 |

| 6.3         | Concu  | rrent Kernel Execution Challenges                           | 06 |

|             | 6.3.1  | Fairness considerations                                     | 07 |

|             | 6.3.2  | Throughput considerations                                   | 09 |

| 6.4         | Applic | ation-Aware Memory Scheduling                               | 10 |

|             | 6.4.1  | Designing Application-aware Memory Scheduler 1              | 11 |

|             | 6.4.2  | Hardware Complexity                                         | 12 |

| 6.5         | Experi | imental Results                                             | 13 |

|             | 6.5.1  | Fairness Results                                            | 13 |

|             | 6.5.2  | Performance Results                                         | 14 |

| 6.6         | Relate | d Work                                                      | 15 |

| 6.7         | Chapt  | er Summary                                                  | 18 |

| apte<br>Ana |        | of Multi-Application Execution in GPUs 11                   | 19 |

| 7.1         | Introd | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $12$             | 20 |

| 7.2         | Backg  | round $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $12$     | 22 |

|    |       | 7.2.1   | Baseline Architecture                                              |

|----|-------|---------|--------------------------------------------------------------------|

|    |       | 7.2.2   | Evaluation Metrics and Application Suite                           |

|    | 7.3   | Perform | mance Characterization of Many-threaded Architectures $\ldots$ 124 |

|    |       | 7.3.1   | A Model for Many-threaded<br>Architectures                         |

|    |       | 7.3.2   | Application Characterization                                       |

|    | 7.4   | Analyz  | king Memory System Interference                                    |

|    |       | 7.4.1   | The Problem: Application Interference                              |

|    |       | 7.4.2   | Limitations of Existing Memory Schedulers                          |

|    | 7.5   | A Perf  | formance Model for Concurrently Executing Applications 133         |

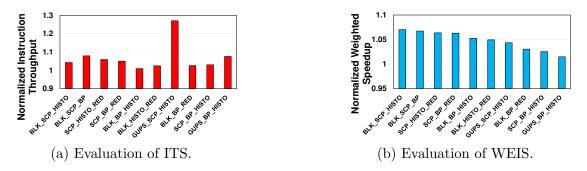

|    |       | 7.5.1   | Analyzing Instruction Throughput                                   |

|    |       | 7.5.2   | Analyzing Weighted Speedup                                         |

|    | 7.6   | Mecha   | nism and Implementation Details                                    |

|    | 7.7   | Infrast | ructure and Evaluation Methodology                                 |

|    | 7.8   | Experi  | mental Results                                                     |

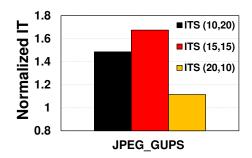

|    |       | 7.8.1   | Evaluation of ITS                                                  |

|    |       | 7.8.2   | Evaluation of WEIS                                                 |

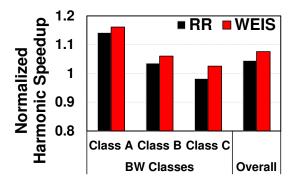

|    |       | 7.8.3   | Performance Summary                                                |

|    |       | 7.8.4   | Scalability Analysis                                               |

|    | 7.9   | Relate  | d Work                                                             |

|    | 7.10  | Chapte  | er Summary                                                         |

| Cł | napte |         |                                                                    |

|    | Con   | clusior | ns and Future Research Directions 151                              |

|    | 8.1   | Summ    | ary of Dissertation Contributions                                  |

|    | 8.2   | Future  | Research Directions                                                |

#### Bibliography

156

# **List of Figures**

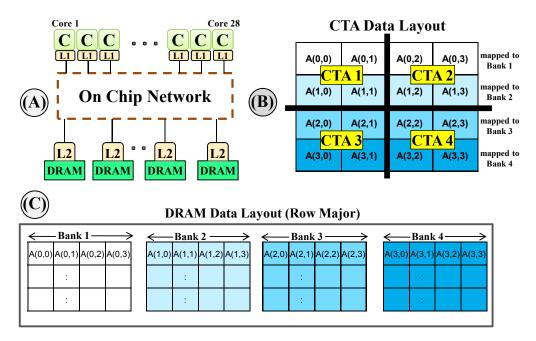

| 2.1 | (A) GPGPU architecture, (B) CTA data layout, and (C) Main memory layout with CTA's data mapped.                                                                                                                                                                                                                                                                                                                                        | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

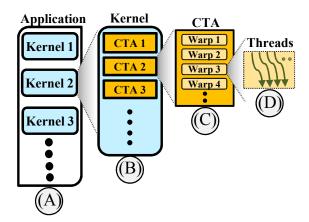

| 2.2 | GPGPU application hierarchy                                                                                                                                                                                                                                                                                                                                                                                                            | 9  |

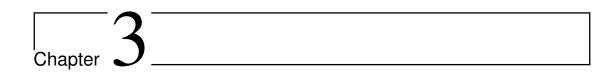

| 3.1 | Fraction of total execution cycles (of all the cores) during which <i>all</i> the warps launched on a core are waiting for their respective data to come back from L2 cache/DRAM. This chapter defines the number of cycles where all warps are stalled due to memory as <i>MemoryBlockCycles</i> . AVG-T1 is the average (arithmetic mean) value across all Type-1 applications. AVG is the average value across all 38 applications. | 16 |

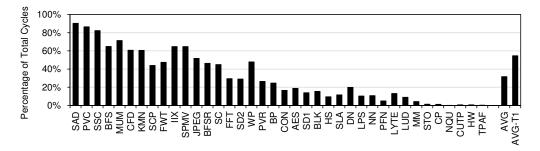

| 3.2 | An illustrative example showing the working of (A) CTA-aware two-level warp scheduling ( <i>CTA-Aware</i> ) (B) Locality aware warp scheduling ( <i>CTA-Aware-Locality</i> ). Label in each box refers to the corresponding CTA number.                                                                                                                                                                                                | 21 |

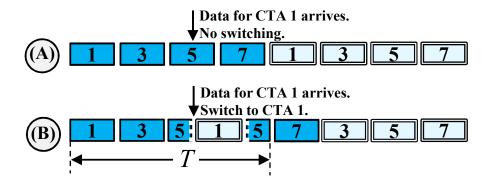

| 3.3 | An example illustrating (A) the under-utilization of DRAM banks<br>with <i>CTA-Aware-Locality</i> , (B) improved bank-level parallelism<br>with <i>CTA-Aware-Locality-BLP</i> , (C1, C2) the positive effects of<br><i>Opportunistic Prefetching</i>                                                                                                                                                                                   | 25 |

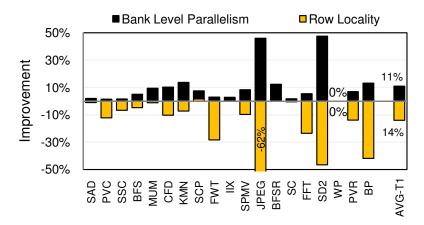

| 3.4 | Effect of <i>CTA-Aware-Locality-BLP</i> on DRAM bank-level parallelism and row locality, compared to <i>CTA-Aware-Locality</i>                                                                                                                                                                                                                                                                                                         | 27 |

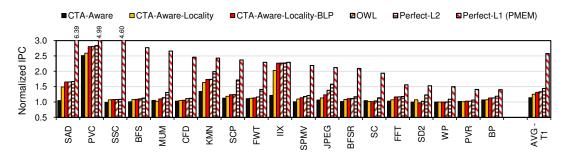

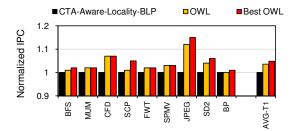

| 3.5 | Performance impact of the schemes on Type-1 applications. Results are normalized to RR.                                                                                                                                                                                                                                                                                                                                                | 27 |

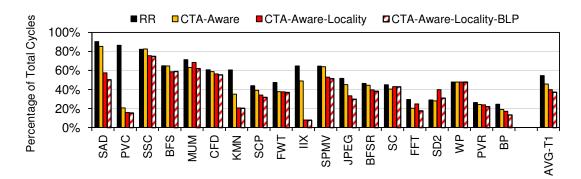

| 3.6 | Impact of different scheduling schemes on <i>MemoryBlockCycles</i> for Type-1 applications. Results are normalized to the total execution cycles with baseline RR scheduling.                                                                                                                                                                                                                                                          | 33 |

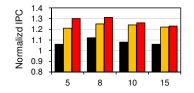

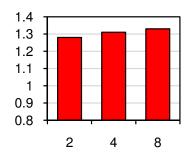

| 3.7 | Sensitivity of IPC to group size (normalized to RR)                                                                                                                                                                                                                                                                        | 37 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.8 | Sensitivity of IPC to the number of banks (normalized to RR)                                                                                                                                                                                                                                                               | 37 |

| 3.9 | Prefetch degree and throttling threshold sensitivity                                                                                                                                                                                                                                                                       | 38 |

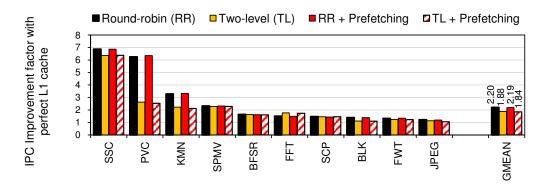

| 4.1 | IPC improvement when L1 cache is made perfect on a GPGPU that<br>employs (1) round-robin (RR) warp scheduling policy, (2) two-level<br>(TL) warp scheduling policy, (3) data prefetching together with RR,<br>and (4) data prefetching together with TL. Section 4.4 describes the<br>evaluation methodology and workloads | 43 |

| 4.2 | An illustrative example showing the working of various scheduling<br>and prefetching mechanisms, motivating the need for the design of<br>the prefetch-aware warp scheduler.                                                                                                                                               | 48 |

| 4.3 | The distribution of main memory requests, averaged across all fetch groups, that are to macro-blocks that have experienced, respectively, 1, 2, and 3-4 unique cache misses. Section 4.4 describes the methodology and workloads                                                                                           | 55 |

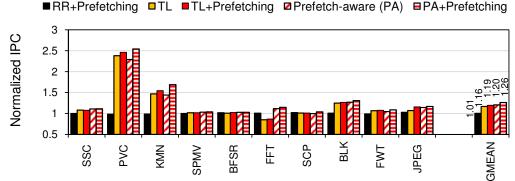

| 4.4 | IPC performance impact of different scheduling and prefetching strategies. Results are normalized to the IPC with the RR scheduler.                                                                                                                                                                                        | 59 |

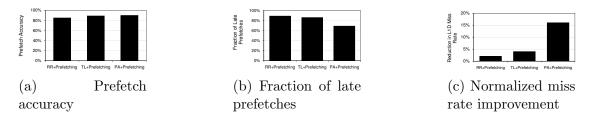

| 4.5 | (a) Prefetch accuracy, (b) Fraction of late prefetches, and (c)<br>Reduction in L1 data cache miss rate when prefetching is<br>implemented with each scheduler. The results are averaged across<br>all applications                                                                                                        | 60 |

| 4.6 | Effect of various scheduling strategies on DRAM bank-level parallelism (BLP)                                                                                                                                                                                                                                               | 60 |

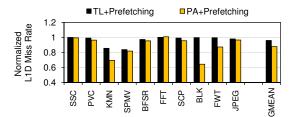

| 4.7 | Effect of various scheduling and prefetching strategies on L1D miss rate. Results are normalized to miss rates with the TL scheduler.                                                                                                                                                                                      | 61 |

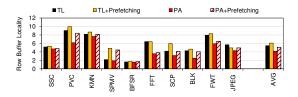

| 4.8 | Effect of different scheduling and prefetching strategies on DRAM row buffer locality                                                                                                                                                                                                                                      | 62 |

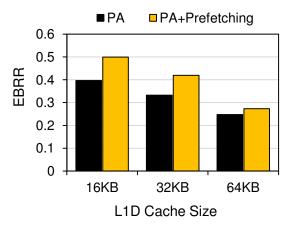

| 4.9 | Effect of prefetching on Evicted Block Reference Rate (EBRR) for various L1 data cache sizes                                                                                                                                                                                                                               | 62 |

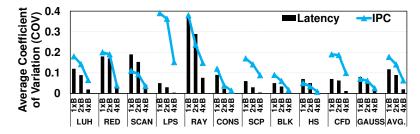

| 5.1 | Average Coefficient of Variation (COV) in average memory access<br>latencies and IPCs across different GPU cores                                                                                                                                                                                                           | 73 |

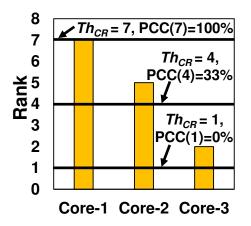

| 5.2  | Illustrative example to demonstrate PCC                                                                                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3  | Variation of criticality across cores with different criticality-rank thresholds. This variation is measured using the PCC metric 78                                                                                                        |

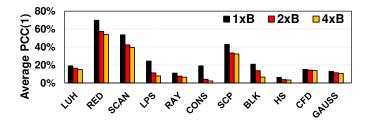

| 5.4  | Effect of increase in peak memory bandwidth on PCC                                                                                                                                                                                          |

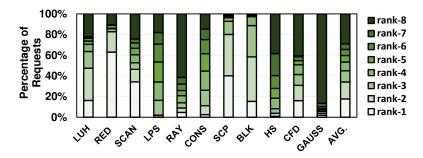

| 5.5  | Variation of criticality across requests at different levels of criticality-rank thresholds. This variation is measured using the PCR                                                                                                       |

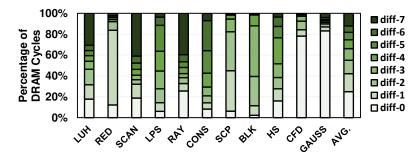

| 5.6  | Distribution of criticality-rank differences across requests 80                                                                                                                                                                             |

| 5.7  | Distribution of requests in different criticality-rank states 85                                                                                                                                                                            |

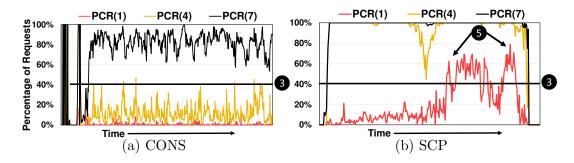

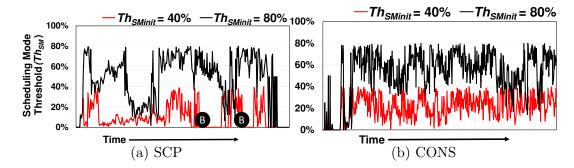

| 5.8  | Execution of CONS and SCP to illustrate the working of Semi-Dyn-<br>CLAMS. $Th_{CR}$ values are calculated dynamically. $\dots \dots \dots$ |

| 5.9  | Execution of CONS and SCP to illustrate the working of Dyn-<br>CLAMS. $Th_{SM}$ is dynamically updated based on $Th_{CR}$                                                                                                                   |

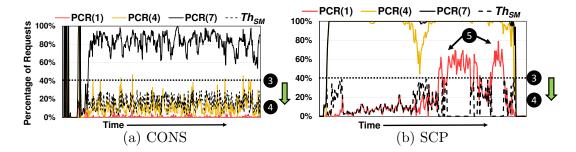

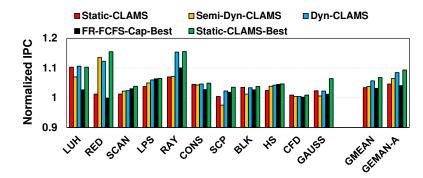

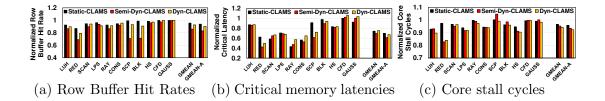

| 5.10 | Performance results normalized to FR-FCFS                                                                                                                                                                                                   |

| 5.11 | Effect on (a) DRAM page hit rates, (b) memory latencies for critical requests, (c) core stall cycles. Results are normalized to FR-FCFS. 93                                                                                                 |

| 5.12 | Changes in $Th_{CR}$ are observed when Semi-Dyn-CLAMS is<br>employed. When $Th_{CR}=8$ , scheduler is in locality mode 93                                                                                                                   |

| 5.13 | Changes in $Th_{SM}$ are observed with Dyn-CLAMS                                                                                                                                                                                            |

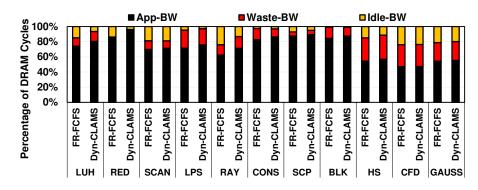

| 5.14 | Effect of Dyn-CLAMS on DRAM bandwidth distribution 96                                                                                                                                                                                       |

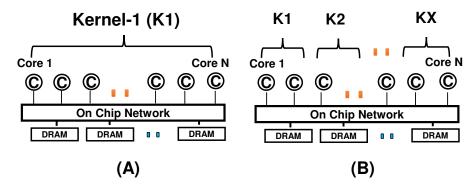

| 6.1  | Baseline GPU architecture executing: (A) Single kernel, (B)<br>Multiple kernels concurrently                                                                                                                                                |

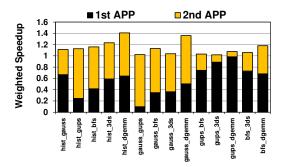

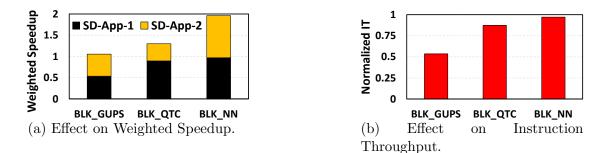

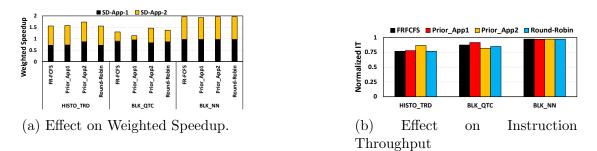

| 6.2  | Weighted speedup (Application throughput) for the evaluated workloads. The 1st APP and 2nd APP are the first and second applications in the workload, respectively, as mentioned in Table 6.3. 107                                          |

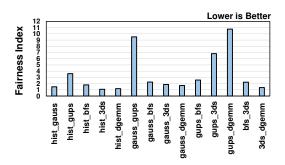

| 6.3  | Fairness Index for the evaluated workloads when the memory scheduler adopts the baseline FR-FCFS scheduling policy 107                                                                                                                      |

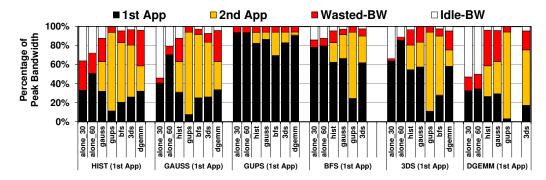

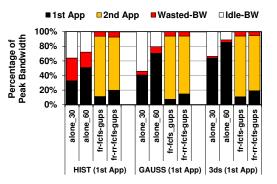

| 6.4  | DRAM bandwidth utilization distribution across various<br>workloads when memory scheduler adopts the baseline FR-FCFS<br>memory scheduling policy                                                                                           |

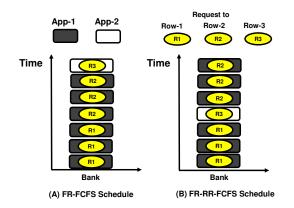

| 6.5  | Conceptual example showing the working of (A) baseline<br>FR-FCFS memory scheduling, (B) proposed FR-RR-FCFS<br>memory scheduling                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

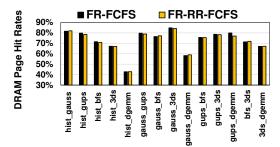

| 6.6  | Effect on DRAM page hit rates. The proposed scheduler FR-RR-<br>FCFS preserves the DRAM page hit rates obtained by the baseline<br>FR-FCFS memory scheduler                                   |

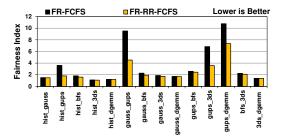

| 6.7  | Fairness index (FI) of the evaluated workloads when memory scheduler adopts FR-FCFS (baseline, 1st bar) and FR-RR-FCFS (proposed, 2nd bar) scheduling techniques                              |

| 6.8  | DRAM bandwidth utilization distribution across selected workloads<br>when memory scheduler adopts FR-FCFS (baseline, 3rd bar) and<br>FR-RR-FCFS (proposed, 4th bar) scheduling techniques 115 |

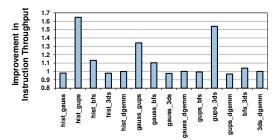

| 6.9  | Improvement in instruction throughput (IT) across the evaluated workloads. Results are normalized to the case when memory scheduler adopts the baseline FR-FCFS scheduling policy 116         |

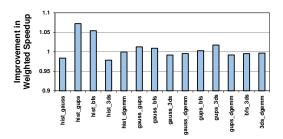

| 6.10 | Improvement in weighted speedup (WS) across the evaluated workloads. Results are normalized to the case when memory scheduler adopts the baseline FR-FCFS scheduling policy 116               |

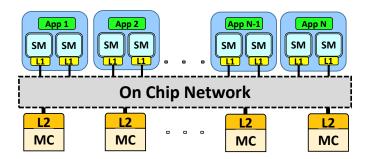

| 7.1  | Overview of the baseline architecture capable of executing multiple applications                                                                                                              |

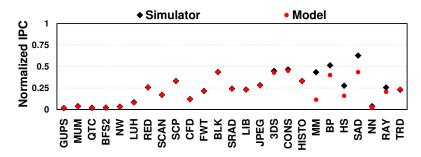

| 7.2  | Application performance obtained via simulation and the model.<br>IPC is normalized with respect to the maximum achievable IPC<br>supported by the architecture                               |

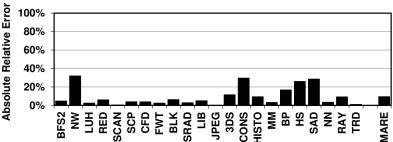

| 7.3  | Absolute relative error between IPCs obtained from real hardware (NVIDIA Kepler K20m) and the model                                                                                           |

| 7.4  | Different performance slowdowns obtained when BLK is<br>co-scheduled with three different applications: GUPS, QTC, and NN.<br>Memory scheduling policy is FR-FCFS                             |

| 7.5  | Different performance slowdowns experienced when different memory scheduling schemes are employed                                                                                             |

| 7.6  | An illustrative example showing $IT$ and $WS$ for two applications<br>running together. The shaded boxes represent system and<br>application properties. The peak memory bandwidth is 50 units.<br>Application 1 and 2 use 30 and 40 units bandwidth, respectively,<br>when they execute alone. Their $MPKIs$ are 20 and 5, respectively. 133 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

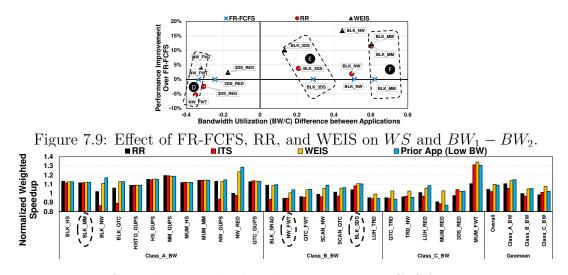

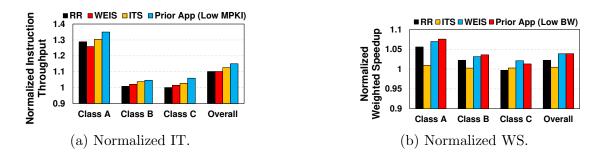

| 7.7  | The effect of FR-FCFS, RR, and ITS on $BW_1 - BW_2$ and $MPKI_1 - MPKI_2$                                                                                                                                                                                                                                                                     |

| 7.8  | IT results normalized with respect to FR-FCFS for 25 representative workloads                                                                                                                                                                                                                                                                 |

| 7.9  | Effect of FR-FCFS, RR, and WEIS on $WS$ and $BW_1 - BW_2$ 144                                                                                                                                                                                                                                                                                 |

| 7.10 | WS results normalized with respect to FR-FCFS for 25 representative workloads                                                                                                                                                                                                                                                                 |

| 7.11 | Summary IT and WS results for 100 workloads, normalized with respect to FR-FCFS                                                                                                                                                                                                                                                               |

| 7.12 | HS results for 100 workloads normalized with respect to FR-FCFS. 146 $$                                                                                                                                                                                                                                                                       |

| 7.13 | Core partitioning results                                                                                                                                                                                                                                                                                                                     |

| 7.14 | Evaluation of ITS and WEIS with three GPU applications 147                                                                                                                                                                                                                                                                                    |

## **List of Tables**

| 3.1        | GPGPU application characteristics: (A) PMEM: IPC<br>improvement with perfect memory (All memory requests are<br>satisfied in L1 caches), Legend: $H = High (>= 1.4x)$ , $L = Low$<br>(< 1.4x); (B) CINV: The ratio of inactive cycles to the total<br>execution cycles of all the cores. | 15       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2        | Reduction in L1 miss rates with the proposed warp scheduling mechanisms over baseline RR scheduling                                                                                                                                                                                      | 19       |

| 3.3        | GPGPU application characteristics: <i>Consecutive CTA row sharing</i> :<br>Fraction of consecutive CTAs (out of all CTAs) accessing the same<br>DRAM row. <i>CTAs/Row</i> : Average number of CTAs accessing the<br>same DRAM row                                                        | 24       |

| 3.4        | Baseline configuration                                                                                                                                                                                                                                                                   | 32       |

| 4.1<br>4.2 | Simulated baseline GPGPU configuration                                                                                                                                                                                                                                                   | 57<br>59 |

| 5.1        | Pseudo code for the proposed schemes                                                                                                                                                                                                                                                     | 88       |

| 5.2        | Key configuration parameters of the simulated GPU configuration                                                                                                                                                                                                                          | 90       |

| 5.3        | Evaluated applications. Table also shows: 1) Average occupancy (occ) in terms of warps, 2) Average $Th_{CR}$ and $Th_{SM}$ calculated using Semi-Dyn-CLAMS and Dyn-CLAMS, respectively, and 3) % of critical requests (%-cri) served in the criticality-mode                             | 90       |

| 6.1        | Simulated baseline GPU configuration                                                                                                                                                                                                                                                     | .03      |

| 6.2 | Evaluated applications, along with their DRAM bandwidth<br>utilization when they are executed alone on the entire baseline                                            |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | GPU architecture                                                                                                                                                      |

| 6.3 | Evaluated 2-application GPU workloads                                                                                                                                 |

| 7.1 | Application characteristics: (A) MPKI: L2 cache misses per kilo-<br>instructions. (B) $BW/C$ : The ratio of attained bandwidth to the<br>peak bandwidth of the system |

| 7.2 | Key configuration parameters of the simulated GPU configuration.<br>See GPGPU-Sim v3.2.1 [116] for full list                                                          |

### Acknowledgments

This dissertation would not have been possible without the help and support of many people with whom I regularly interacted throughout my Ph.D. tenure. First and foremost, I would like to thank my dissertation advisor, Prof. Chita Das. He has been a constant source of inspiration for me. He always inspired me to do excellent research, submit papers in the best venues, take challenging courses, and most importantly to be a humble citizen. I am highly indebted to him for what he has given me so far. I also thank his entire family for their unconditional support.

I would like to thank my dissertation co-advisor, Prof. Mahmut Kandemir, for his constant support. He has been a great critic of my work. I deeply admire his dedication towards research and I hope to imitate that as I continue my career in academia. The chats over coffee with him along with Prof. Das, Prof. Sivasubramaniam, and other HPCL members on a variety of topics (sometimes also on research) were refreshing, and I will remember them for long time.

My first interaction with Prof. Mutlu was during my internship at Intel back in 2012. Since then, we have been involved in many fruitful research collaborations. I deeply admire his work ethics and care towards making the research work polished and more accessible to the readers. I appreciate the time he spent in making this dissertation stronger, clearer, and more readable, in addition to making me more methodical and organized in doing research. I deeply thank Prof. Xie and Dr. Iyer for serving on my committee. I appreciate their support and guidance during my entire Ph.D. tenure. I also thank Prof. Jenkins, Prof. Narayanan, and Prof. Sampson for commenting on my work and sharing their thoughts.

My internship experiences at Intel and NVIDIA had been great learning experiences for me. I would like to thank my internship mentors for providing a lively environment for me to work. In this regard, I thank Ramadass Nagarajan, Xiaowei Jiang, Li Zhao, Ravi Iyer, Srihari Makineni, Evgeny Bolotin, Zvika Guz, Mike Parker, and Steve Keckler. In addition, I would like to thank all my research collaborators and colleagues with whom I have interacted.

My Ph.D. journey had been incredibly enjoyable because of the support and a friendly environment provided by my lab mates. I have developed a real camaraderie with Onur Kayiran after collaborating with him on so many research projects. His research acumen really helped in making this dissertation stronger. I do not even remember how many impossible ideas I have brainstormed with him. I admire his patience to listen those and more importantly his patience to provide really good feedback on all of that. I deeply thank Asit Mishra for being my first research mentor and teaching me how to do research. My overlap with Bikash Sharma was for four years. Although we never collaborated on the same research project, we used to talk through the obstacles as they came in our respective projects. We were apartment-mates for four years, and I thank him for his friendship. I also thank Nachiappan CN for being a good friend of mine and giving his dollars (not 2 cents) whenever I was stuck at something. The great company of Kashyap Dixit and Ashutosh Pattnaik helped me sail thorough the end years of my Ph.D. Also, special thanks to Neha Sharma for all her support during my Ph.D. tenure.

Much of my research was at the mercy of the compute clusters hosted by my department. I thank the entire CSE department technical staff for managing those clusters. In particular, I thank Eric Prescott for helping me with my requests even at the wee hours on the weekends. I also thank the entire administrative staff of CSE department for being so efficient and getting my paper-work going. Special thanks to Annie Royer for patiently handling tons of my travel reimbursement paper-work.

There have been lots of other people whose company made my experience at Penn State memorable. In this regard, I would like to thank Reetuparna Das, Seung-Hwan Lim, Sai Prashanth, Akbar Sharifi, Niranjan Soundararajan, Abhradeep Guha Thakurta, Shrawan C. Surendar, Emre Kultursay, Prashanth Thinakaran, Tulika Parija, Xulong Tang, Haibo Zhang, Jihyun Ryoo, Mahshid Sedghi, Tuba Kesten, Jagadish Kotra, Diana Guttman, Amin Jadidi, Di Wang, Karthik Swaminathan, Narges Shahidi, Harshal Patanakar, Vivek Kaushal, Abhishek Kar, Anushree Dash, Debanjan Das, Shashank Singhai, Suchismita Sarangi, Berkey Cellik, Giuseppe Salento, Nandhini Chandramoorthy, Nirupama Talele, Cong Xu, Bhaskar Prabhala, Praveen Yedlapalli, Sushama Karumanchi. If you are reading this page and think that your name is missing, excuse me for that and assume it is written with an invisible ink.

Finally, I am running short of words in thanking my parents, grandparents,

cousins, and other family members for providing unconditional support.

Thank you all.

## Dedication

To my dear parents and grandparents for being a constant source of inspiration and support.

### Introduction

Graphics Processing Units (GPUs) have recently emerged as a cost-effective throughput computing paradigm for a wide range of areas such as science, engineering, medicine, social media, gaming, and finance, due to their immense computing power compared to CPUs [1-10]. Many of the world's Top 500 computers [11, 12] use GPUs both for performance and energy-efficiency. Similarly, orders of magnitude improvements in application performance in medical science [13-15], finance [16-18], and social media [19] have been reported recently by offloading computation to GPUs. It is not only expected that GPUs will play a critical role in the foreseeable computing landscape ranging from supercomputing machines to handheld devices, but they also could be a natural choice for processing *biq-data* to advance science and engineering. As an example, US healthcare data reached 150 Exabytes in 2011 and is likely to grow to Zettabytes/Yottabytes soon [20]. Similar trends in data explosion are predicted in many domains such as the environment, traffic control, manufacturing, climate prediction and astrophysics [21]. Mining information in such large datasets requires scalable parallel computing capabilities for which GPUs provide a very promising fit.

Modern GPUs are characterized by numerous programmable computational cores and thousands of simultaneously active fine-grained threads. To facilitate ease of programming on these systems, programming models like CUDA [4, 22, 23] and OpenCL [24] have been developed. GPU applications are typically divided into several kernels, where each kernel is capable of spawning many threads. The threads are usually grouped together into *thread blocks*, also known as *cooperative thread arrays (CTAs)*. When an application starts its execution on a GPU, the CTA scheduler initiates scheduling of CTAs onto the available GPU cores. All the threads within a CTA are executed on the same core typically in groups of 32 threads. This collection of threads is referred to as a *warp* and all the threads within a warp typically share the same instruction stream, which forms the basis for the term *single instruction multiple threads*, SIMT [3,25,26].

**The Problem:** In spite of having numerous resident threads and theoretically high thread-level parallelism (TLP), GPU cores still suffer from high periods of idle times, resulting in under-utilization of hardware resources. These idle times are primarily a result of the inability of the commonly-employed warp scheduling policies in facilitating a GPU core to completely tolerate the long memory fetch latencies, which are primarily attributed to: (1) contention in caches caused by multiple concurrent threads, (2) DRAM contention caused by various concurrent threads from multiple GPU cores, and (3) limited off-chip DRAM bandwidth available in GPUs. With the commonly-employed warp scheduling policies, for example, round-robin (RR) scheduler, the GPGPU core becomes *inactive* because there may be no warps that are *not* stalling due to a memory operation, which significantly reduces the capability of hiding long memory latencies. Such inactive periods are especially prominent in memory-intensive applications. It is observed that out of 38 applications covering various GPGPU application benchmark suites, 19 applications suffer from very high core inactive times (on average 62% of total cycles are spent with no warps executing). In addition to the inefficiencies in warp schedulers, the modern memory access schedulers in GPUs (for example, first-ready, first-come-first-serve (FR-FCFS)) also possess limitations. Typically, they are only optimized for DRAM access locality to enhance memory bandwidth utilization, and implicitly assume all requests from different GPU cores are equally important. Hence, these schedulers do not prioritize critical memory requests over non-critical requests, thereby exhibiting sub-optimal performance.

**Dissertation Contributions:** This dissertation research addresses the above issues by focusing on the problem of cache and memory resource contention. In this context, this dissertation proposes techniques that are employed at two different places: *core* and *memory*. First, this dissertation shows that by intelligently scheduling the threads at the *core*, the generated memory request patterns can be more amenable for existing resource management techniques such as cache replacement and memory scheduling as well as performance enhancement techniques such as data prefetching. Second, this dissertation shows that considering criticality and other application characteristics to schedule memory requests at the memory controller is an effective way to manage contention at the *memory*.

#### (A) Managing Contention from Cores via Warp Scheduling

This dissertation shows that the existing warp scheduling techniques employed at the core are oblivious to the underlying shared resource management policies, and therefore, the warp scheduling decisions taken at the core might not always be in harmony with the shared resource management scheduling policies. In this context, this dissertation proposes two warp scheduling techniques: 1) cache and memory-aware warp scheduling; and 2) data prefetching-aware warp scheduling. Both of these schedulers exploit an important property of GPUs that there is no ordering restriction among the execution of warps and the warp scheduler can efficiently choose the desired warps without incurring significant overhead.

Contribution I: Cache and Memory-Aware Warp Scheduling [7]. The key problem with the traditional round-robin warp scheduling policy is that it allows a large number of warps to concurrently access the cache. This makes it harder for the underlying cache management policies to leverage the locality present in many CUDA applications. In order to manage the contention in caches, this dissertation proposes a *cache-aware* warp scheduler that essentially reduces the number of warps that can benefit from caches in a given time interval. Although this scheduler improves the cache hit rates significantly, it turns out that it is not aware of the warp scheduling decisions taken at the *other* cores. This unawareness causes the schedulers at different cores to schedule warps such that they happen to concurrently access a limited set of global memory banks, consequently leading to inefficient utilization of the available memory bandwidth. To this end, this dissertation proposes a *memory-aware* warp scheduler called OWL by extending the cache-aware warp scheduler such that it can facilitate better coordination between warp scheduling decisions taken at different cores. OWL enabled the warps across different cores to collectively access a larger number of memory banks concurrently, thereby improving the memory-level parallelism and easing the job of the memory scheduler in managing contention at the banks.

**Contribution II: Prefetch-Aware Warp Scheduling** [27]. Effectiveness of data prefetching is dependent on the prefetching accuracy as well as timeliness of prefetches. The analyses of the existing warp schedulers show that they do not coordinate well with the prefetching mechanisms because they happen to schedule consecutive warps accessing nearby cache blocks in close succession. Therefore, a simple prefetcher that could have prefetched nearby cache blocks with high accuracy will not contribute significantly to the performance because many of them will be tagged as late prefetches. To this end, this dissertation proposes a *prefetch-aware* warp scheduling policy that can coordinate with prefetching decisions in GPUs to better tolerate long memory latencies. This scheduler separates the scheduling of consecutive warps in time, and by not executing them in close succession, it enables effective incorporation of simple prefetching techniques for improving the overall GPU performance.

#### (B) Managing Contention at Memory via Memory Scheduling

Memory access schedulers employed in GPUs implicitly assume that all requests from different cores are equally important. This dissertation shows that this assumption does not necessarily help in achieving: 1) the best performance when GPU cores concurrently execute threads belonging to a *single* application; and 2) the best system throughput and fairness when GPU cores concurrently execute threads belonging to *multiple* applications. To address these two scenarios, this dissertation proposes criticality-aware and application-aware memory scheduling techniques, respectively.

#### Contribution III: Criticality-Aware Memory Scheduling. Shared resource

contention causes significant variation in average memory latencies experienced by individual GPU cores. Due to this variation, the number of stalling warps belonging to the cores that suffer from higher memory access latencies is typically higher than that of other cores, making the former type of cores less latency tolerant, i.e., more *critical*. This implies that because different GPU cores have varying degrees of tolerance to latency during the execution of an application, their corresponding memory requests have varying degrees of criticality. Based on this observation, this dissertation proposes a criticality-aware scheduler that takes into account the criticality of memory requests, i.e., the latency-tolerance of the cores that generate memory requests, thereby improving the overall GPU performance over existing schedulers.

Contribution IV: Application-Aware Memory Scheduling [28, 29]. This dissertation finds that an uncoordinated allocation of GPU resources among concurrently executing multiple applications can lead to significant degradation in system throughput and fairness. Therefore, it is imperative to make the GPU memory system aware of the application characteristics. To this end, this dissertation proposes two different application-aware memory scheduling policies. The first scheduler is developed with the aim of sharing the memory bandwidth across concurrent applications in a fair and efficient manner. The second scheduler is more sophisticated and is based on an analytical performance model for GPUs. This dissertation proposes that the common use of misses-per-instruction (MPI) as a proxy for performance is not accurate for many-threaded architectures and memory scheduling decisions based on both MPI and attained DRAM bandwidth are more effective in enhancing system throughput and fairness. This dissertation evaluates both schedulers on a newly-developed simulated GPU platform supporting execution of multiple applications.

The rest of this dissertation is organized as follows. Chapter 2 provides preliminaries for GPU architectures. Then, the OWL warp scheduler is presented in Chapter 3. Prefetch-aware warp scheduler is discussed in Chapter 4, followed by the description of the criticality-aware memory scheduler in Chapter 5. Chapters 6 and 7 looks at application-aware memory system design issues for GPUs. Chapter 7 concludes this dissertation and presents a few directions for future work.

# Graphics Processing Units (GPUs): A Primer

This chapter provides preliminaries for GPU architectures, application design, and typical scheduling and prefetching strategies employed in GPUs.

**GPU Architecture:** A General Purpose Graphics Processing Unit (GPGPU) consists of many simple cores (streaming multiprocessors), with each core typically having a SIMT width of 8 to 32 (NVIDIA's Fermi series has 16 streaming multiprocessors with a SIMT width of 32 [4]). A typical GPU architecture (as shown in Figure 2.1 (A)) consists of many shader cores connected to memory controllers via an on-chip interconnect. This configuration is similar to the ones studied in prior works [30,31]. Each core is associated with a private L1 data cache and read-only texture and constant caches along with a low latency shared memory (scratchpad memory). Every memory controller is associated with a slice of the shared L2 cache for faster access to the cached data.

**Canonical GPGPU Application Design:** A typical CUDA application consists of many kernels (or grids) as shown in Figure 2.2 (A). These kernels implement specific modules of an application. Each kernel is divided into groups of threads, called cooperative thread arrays (CTAs) (Figure 2.2 (B)). A CTA is an abstraction which encapsulates all synchronization and barrier primitives

Figure 2.1: (A) GPGPU architecture, (B) CTA data layout, and (C) Main memory layout with CTA's data mapped.

among a group of threads [1]. Having such an abstraction allows the underlying hardware to relax the execution order of the CTAs to maximize parallelism. The underlying architecture in turn, sub-divides each CTA into groups of threads (called warps) (Figure 2.2 (C) and (D)). This sub-division is transparent to the application programmer and is an architectural abstraction.

**CTA**, **Warp**, and **Thread Scheduling:** Execution on GPGPUs starts with the launch of a kernel. All kernels can either execute sequentially or concurrently. In case kernels are executed sequentially, after a kernel is launched, the CTA scheduler schedules available CTAs associated with the kernel in a round-robin and load balanced fashion on all the cores [31]. For example, CTA 1 is assigned to core 1, CTA 2 is assigned to core 2 and so on. After assigning at least one CTA to each core (provided that enough CTAs are available), if there are still unassigned CTAs, more CTAs can be assigned to the same core in a similar fashion. The maximum number of CTAs per core (N) is limited by core resources (number of threads, size of shared memory, register file size, etc. [1,31]). Given a baseline architecture, N may vary across kernels depending on how much resources are needed by a CTA of a particular kernel. If a CTA of a particular kernel needs

Figure 2.2: GPGPU application hierarchy.

more resources, N will be smaller compared to that of another kernel whose CTAs need fewer resources. For example, if a CTA of kernel X needs 16KB of shared memory and the baseline architecture has 32KB of shared memory available, a maximum of 2 CTAs of kernel X can be executed simultaneously.

The above CTA assignment policy is followed by per-core GPGPU warp scheduling. Warps associated with CTAs are scheduled in a round-robin (RR) fashion on the assigned cores [8, 31] and get *equal* priority. In traditional GPU architecture, every 4 cycles, a warp ready for execution is selected in a round-robin fashion and fed to the 8-way SIMT pipeline of a GPGPU core. At the memory stage of the core pipeline, if a warp gets blocked on a long latency memory operation, the entire warp (32 threads) is scheduled out of the pipeline and moved to the pending queue. At a later instant, when the data for the warp arrives, it proceeds to the write-back stage, and then fetches new instructions.

When multiple *kernels* from multiple *applications* are executed concurrently on a GPU, they can be assigned to the SMs using an equal partitioning mechanism. If two kernels from different applications are concurrently executed, this mechanism assigns half of the SMs to the first application and the second half to the other application. The CTA assignment for each kernel follows the same load-balanced distribution strategy as described before; the only difference is that each kernel is now assigned to only half of the SMs of the baseline GPU architecture.

CTA Data Layout: Current GPU chips support  $\sim 10 \times$  higher memory

bandwidth compared to CPU chips [7]. In order to take full advantage of the available DRAM bandwidth and to reduce the number of requests to DRAM, a kernel must arrange its data accesses so that each request to the DRAM is for a large number of consecutive DRAM locations. With the SIMT execution model, when all threads in a warp execute a memory operation, the hardware typically detects if the threads are accessing consecutive memory locations; if they are, the hardware coalesces all these accesses into a single consolidated access to DRAM that requests all consecutive locations at once. To understand how data blocks used by CTAs are placed in the DRAM main memory, consider Figure 2.1 (B). This figure shows that all locations in the DRAM main memory form a single, consecutive address space. The matrix elements that are used by CTAs are placed into the linearly addressed locations according to the row major convention as shown in Figure 2.1 (B). That is, the elements of row 0 of a matrix are first placed in order into consecutive locations (see Figure 2.1 (C)). The subsequent row is placed in another DRAM bank. Note that, this example is simplified for illustrative purposes only, and the data layout may vary across applications.

Memory Scheduling in GPUs: First-ready FCFS (FR-FCFS) [32–34] is the commonly employed memory scheduling technique in GPUs. This scheme is targeted at improving DRAM row hit rates, so request prioritization order is as follows: 1) row-hit requests are prioritized over other requests; then 2) older requests are prioritized over younger requests. Among row-hit requests, older requests are prioritized over younger requests.

**Prefetching in GPGPUs:** Inter-thread L1 data prefetching [35] was recently proposed as a latency hiding technique in GPGPUs. In this technique, a group of threads prefetch data for threads that are going to be scheduled later. This inter-thread prefetcher can also be considered as an inter-warp prefetcher, as the considered baseline architecture attempts to coalesce the memory requests of all the threads in a warp as a single cache block request (e.g., 4B requests per thread  $\times$  32 threads per warp = 128B request per warp, which equals the cache block size). The authors propose that prefetching data for other warps (in turn, threads) can eliminate cold misses, as the warps for which the data is prefetched will find

their requested data in the cache. In the case where the threads demand their data before the prefetched data arrives, the demand requests can be merged with the already-sent prefetch requests (if accurate) via miss status handling registers (MSHRs). In this case, the prefetch can partially hide some of the memory latency.

In the next sections, this dissertation will detail the developed warp and memory scheduling techniques.

# Cache and Memory Aware Warp Scheduling Techniques

Emerging GPGPU architectures, along with programming models like CUDA and OpenCL, offer a cost-effective platform for many applications by providing high thread level parallelism at lower energy budgets. Unfortunately, for many generalpurpose applications, available hardware resources of a GPGPU are not efficiently utilized, leading to lost opportunity in improving performance. A major cause of this is the inefficiency of current warp scheduling policies in tolerating long memory latencies.

This chapter identifies that the scheduling decisions made by such policies are agnostic to thread-block, or cooperative thread array (CTA), behavior, and as a result inefficient. This chapter presents a coordinated CTA-aware scheduling policy that utilizes four schemes to minimize the impact of long memory latencies. The first two schemes, CTA-aware two-level warp scheduling and locality aware warp scheduling, enhance per-core performance by effectively reducing cache contention and improving latency hiding capability. The third scheme, bank-level parallelism aware warp scheduling, improves overall GPGPU performance by enhancing DRAM bank-level parallelism. The fourth scheme employs opportunistic memory-side prefetching to further enhance performance by taking advantage of open DRAM rows. Evaluations on a 28-core GPGPU platform with highly memory-intensive applications indicate that the proposed mechanism can provide 33% average performance improvement compared to the commonly-employed round-robin warp scheduling policy.

#### **3.1** Introduction

The goal of this work is to tackle the under-utilization of cores for improving the overall GPGPU performance. In this context, the c(O) operative thread array a(W) are warp schedu(L)ing policy, called OWL<sup>1</sup> is developed. OWL is based on the concept of focused CTA-aware scheduling, which attempts to mitigate the various components that contribute to long memory fetch latencies by focusing on a selected subset of CTAs scheduled on a core (by always prioritizing them over others until they finish). The proposed OWL policy is a four-pronged concerted approach and the associated **contributions** are:

• First, a CTA-aware two-level warp scheduler is developed that exploits the architecture and application interplay to intelligently schedule CTAs onto the cores. This scheme groups all the available CTAs (N CTAs) on a core into smaller groups (of n CTAs) and schedules all groups in a round-robin fashion. As a result, it performs better than the commonly-used baseline RR warp scheduler because 1) it allows a smaller group of warps/threads to access the L1 cache in a particular interval of time, thereby reducing cache contention, 2) improves latency hiding capability and reduces inactive periods as not all warps reach long latency operations around the same time. This technique improves the average L1 cache hit rate by 8% over RR for 19 highly memory intensive applications, providing a 14% improvement in IPC performance.

• Second, a locality aware warp scheduler is developed to improve upon the CTAaware two-level warp scheduler, by further reducing L1 cache contention. This is achieved by *always* prioritizing a group of CTAs (n CTAs) in a core over the rest

<sup>&</sup>lt;sup>1</sup>Owl is a bird known for exceptional *vision* and *focus* while it hunts for food. The proposed scheduling policy also follows an owl's philosophy. It intelligently selects (*visualizes*) a subset of CTAs (out of many CTAs launched on a core) and *focuses* on them to achieve performance benefits.

of the CTAs (until they finish). Hence, unlike the base scheme, where each group of CTAs (consisting of *n* CTAs) is executed one after another and thus, does not utilize the caches effectively, this scheme always prioritizes one group of CTAs over the rest whenever a particular group of CTA is ready for execution. The major goal is to take advantage of the locality between nearby threads and warps (associated with the same CTA) [36]. With this scheme, average L1 cache hit rate is further improved by 10% over the CTA-aware two-level warp scheduler, leading to an 11% improvement in IPC performance.

• Third, the first two schemes are aware of different CTAs but do not exploit any properties common among different CTAs. Across 38 GPGPU applications, there is significant DRAM page locality between consecutive CTAs. On average, the same DRAM page is accessed by consecutive CTAs 64% of the time. Hence, if two *consecutive* CTA groups are scheduled on two different cores and are *always* prioritized according to the locality aware warp scheduling, they would access a *small* set of DRAM banks more frequently. This increases the queuing time at the banks and reduces memory bank level parallelism (BLP) [37]. On the other hand, if non-consecutive CTA groups are scheduled and *always* prioritized on two different cores, they would concurrently access a larger number of banks. This reduces the contention at the banks and improves BLP. This proposed scheme (called the bank-level parallelism aware warp scheduler), increases average BLP by 11% compared to the locality aware warp scheduler, providing a 6% improvement in IPC performance.

• Fourth, a drawback of the previous scheme is that it reduces DRAM row locality. This is because rows opened by a CTA cannot be completely utilized by its consecutive CTAs since consecutive CTAs are not scheduled simultaneously any more. To recover the loss in DRAM row locality, an opportunistic prefetching mechanism is developed, in which some of the data from the opened row is brought to the nearest on-chip L2 cache partition. The mechanism is opportunistic because the degree of prefetching depends upon the number of pending demand requests at the memory controller.

The performance of the OWL scheduler is evaluated on a 28-core GPGPU platform simulated via GPGPU-Sim [31] and a set of 19 highly memory intensive

applications. The results show that OWL improves GPGPU performance by 33% over the baseline RR warp scheduling policy. OWL also outperforms the recently-proposed two-level scheduling policy [8] by 19%.

Table 3.1: GPGPU application characteristics: (A) PMEM: IPC improvement with perfect memory (All memory requests are satisfied in L1 caches), Legend: H = High (>= 1.4x), L = Low (< 1.4x); (B) CINV: The ratio of inactive cycles to the total execution cycles of all the cores.

| #  | App. Suite | Type-1 Applications      | Abbr. | PMEM     | CINV |

|----|------------|--------------------------|-------|----------|------|

| 1  | Parboil    | Sum of Abs. Differences  | SAD   | H(6.39x) | 91%  |

| 2  | MapReduce  | PageViewCount            | PVC   | H(4.99x) | 93%  |

| 3  | MapReduce  | SimilarityScore          | SSC   | H(4.60x) | 85%  |

| 4  | CUDA SDK   | Breadth First Search     | BFS   | H(2.77x) | 81%  |

| 5  | CUDA SDK   | MUMerGPU                 | MUM   | H(2.66x) | 72%  |

| 6  | Rodinia    | CFD Solver               | CFD   | H(2.46x) | 66%  |

| 7  | Rodinia    | Kmeans Clustering        | KMN   | H(2.43x) | 65%  |

| 8  | CUDA SDK   | Scalar Product           | SCP   | H(2.37x) | 58%  |

| 9  | CUDA SDK   | Fast Walsh Transform     | FWT   | H(2.29x) | 58%  |

| 10 | MapReduce  | InvertedIndex            | IIX   | H(2.29x) | 65%  |

| 11 | Parboil    | Sparse-Matrix-Mul.       | SPMV  | H(2.19x) | 65%  |

| 12 | 3rd Party  | JPEG Decoding            | JPEG  | H(2.12x) | 54%  |

| 13 | Rodinia    | Breadth First Search     | BFSR  | H(2.09x) | 64%  |

| 14 | Rodinia    | Streamcluster            | SC    | H(1.94x) | 52%  |

| 15 | Parboil    | FFT Algorithm            | FFT   | H(1.56x) | 37%  |

| 16 | Rodinia    | SRAD2                    | SD2   | H(1.53x) | 36%  |

| 17 | CUDA SDK   | Weather Prediction       | WP    | H(1.50x) | 54%  |

| 18 | MapReduce  | PageViewRank             | PVR   | H(1.41x) | 46%  |

| 19 | Rodinia    | Backpropogation          | BP    | H(1.40x) | 33%  |

| 20 | CUDA SDK   | Separable Convolution    | CON   | L(1.23x) | 20%  |

| 21 | CUDA SDK   | AES Cryptography         | AES   | L(1.23x) | 51%  |

| 22 | Rodinia    | SRAD1                    | SD1   | L(1.17x) | 20%  |

| 23 | CUDA SDK   | Blackscholes             | BLK   | L(1.16x) | 17%  |

| 24 | Rodinia    | HotSpot                  | HS    | L(1.15x) | 21%  |

| 25 | CUDA SDK   | Scan of Large Arrays     | SLA   | L(1.13x) | 17%  |

| 26 | 3rd Party  | Denoise                  | DN    | L(1.12x) | 22%  |

| 27 | CUDA SDK   | 3D Laplace Solver        | LPS   | L(1.10x) | 12%  |

| 28 | CUDA SDK   | Neural Network           | NN    | L(1.10x) | 13%  |

| 29 | Rodinia    | Particle Filter (Native) | PFN   | L(1.08x) | 10%  |

| 30 | Rodinia    | Leukocyte                | LYTE  | L(1.08x) | 15%  |

| 31 | Rodinia    | LU Decomposition         | LUD   | L(1.05x) | 64%  |

| 32 | Parboil    | Matrix Multiplication    | MM    | L(1.04x) | 4%   |

| 33 | CUDA SDK   | StoreGPU                 | STO   | L(1.02x) | 3%   |

| 34 | CUDA SDK   | Coulombic Potential      | CP    | L(1.01x) | 4%   |

| 35 | CUDA SDK   | N-Queens Solver          | NQU   | L(1.01x) | 95%  |

| 36 | Parboil    | Distance-Cutoff CP       | CUTP  | L(1.01x) | 2%   |

| 37 | Rodinia    | Heartwall                | HW    | L(1.01x) | 9%   |

| 38 | Parboil    | Angular Correlation      | TPAF  | L(1.01x) | 6%   |

Figure 3.1: Fraction of total execution cycles (of all the cores) during which *all* the warps launched on a core are waiting for their respective data to come back from L2 cache/DRAM. This chapter defines the number of cycles where all warps are stalled due to memory as *MemoryBlockCycles*. AVG-T1 is the average (arithmetic mean) value across all Type-1 applications. AVG is the average value across all 38 applications.

#### **3.2** Motivation and Workload Analysis

Round robin (RR) scheduling of warps causes almost all warps to execute the same long latency memory operation (with different addresses) at roughly the same time, as previous work has shown [8]. For the computation to resume in the warps and the core to become active again, these long-latency memory accesses need to be completed. This inefficiency of RR scheduling hampers the latency hiding capability of GPGPUs. To understand it further, let us consider 8 CTAs that need to be assigned to 2 cores (4 CTAs per core). According to the load-balanced CTA assignment policy described in Section 2, CTAs 1, 3, 5, 7 are assigned to core 1 and CTAs 2, 4, 6, 8 are assigned to core 2. With RR, warps associated with CTAs 1, 3, 5 and 7 are executed with equal priority on core 1 and are executed in a round-robin fashion. This execution continues until all the warps are blocked (when they need data from main memory). At this point, there may be no ready warps that can be scheduled, making core 1 inactive. Typically, this inactive time is very significant in memory intensive applications, as multiple requests are sent to the memory subsystem by many cores in a short period of time. This increases network and DRAM contention, which in turn increases queuing delays, leading to very high core inactive times.

To evaluate the impact of RR scheduling on GPGPU applications, this

chapter first characterizes the application set. This work quantifies how much IPC improvement each application gains if *all* memory requests magically hit in the L1 cache. This improvement, called PMEM, is depicted in Table 3.1, where the 38 applications are sorted in descending order of PMEM. Applications that have high PMEM ( $\geq 1.4 \times$ ) are classified as Type-1, and the rest as Type-2. This work observed that the warps of highly memory intensive applications (Type-1) wait longer for their data to come back than warps of Type-2 applications. If this wait is eliminated, the performance of SAD, PVC, and SSC would improve by  $6.39 \times$ ,  $4.99 \times$  and  $4.60 \times$ , respectively (as shown by the PMEM values for these applications).

Across Type-1 applications, average core inactive time (CINV) is 62% of the total execution cycles of all cores (Table 3.1). During this inactive time, no threads are being executed in the core. The primary reason behind this high core inactivity is *MemoryBlockCycles*, which is defined as the number of cycles during which all the warps in the core are stalled waiting for their memory requests to come back from L2 cache/DRAM (i.e., there are warps on the core but they are all waiting for memory). Figure 3.1 shows the fraction of *MemoryBlockCycles* of all the cores out of the total number of cycles taken to execute each application. Across all 38 applications, *MemoryBlockCycles* constitute 32% of the total execution cycles, i.e., 70% of the total inactive cycles. These results clearly highlight the importance of reducing the *MemoryBlockCycles* to improve the utilization of cores, and thus GPGPU performance.

Another major constituent of inactive cycles is NoWarpCycles, which is defined as number of cycles during which a core has no warps to execute, but an application has not completed its execution as some other cores are still executing warps. This might happen due to two reasons: (1) availability of a small number of CTAs within an application (due to an inherently small amount of parallelism) [9] or (2) the CTA load imbalance phenomenon [31], where some of the cores finish their assigned CTAs earlier than the others. This work finds that NoWarpCycles is prominent in LUD and NQU, which are Type-2 applications. Table 3.1 shows that although core inactive time is very high in LUD and NQU (64% and 95%, respectively), MemoryBlockCycles is very low (Figure 3.1). Note that Type-1 applications are present across all modern workload suites like MapReduce, Parboil, Rodinia, and CUDA SDK, indicating that memory stalls are a fundamental bottleneck in improving the performance of these applications. This work finds that Type-1 applications are most affected by limited off-chip DRAM bandwidth, which leads to long memory stall times. The goal of this work is to devise new warp scheduling mechanisms to both reduce and tolerate long memory stall times in GPGPUs.

## 3.3 The OWL Scheduler

This section describes OWL, c(O) operative thread array a(W) are warp schedu(L)ing policy, which consists of four schemes: CTA-aware two-level warp scheduling, locality aware warp scheduling, bank-level parallelism aware warp scheduling, and opportunistic prefetching, where each scheme builds on top of the previous.

### 3.3.1 CTA-Aware: CTA-aware two-level warp scheduling

To address the problem posed by RR scheduling, a CTA-aware two-level warp scheduler is proposed, where all the available CTAs launched on a core (N CTAs) are divided into smaller groups of n CTAs. Assume that the size of each CTA is k warps (which is pre-determined for an application kernel). This corresponds to each group having  $n \times k$  warps. CTA-Aware selects a single group (having nCTAs) and prioritizes the associated warps ( $n \times k$ ) for execution over the remaining warps ( $(N - n) \times k$ ) associated with the other group(s). Warps within the same group have equal priority and are executed in a round-robin fashion. Once all the warps associated with the first selected group are blocked due to the unavailability of data, a group switch occurs giving opportunity to the next CTA group for execution (and this process continues in a round-robin fashion among all the CTA groups). This is an effective way to hide long memory latencies, as now, a core can execute the group(s) of warps that are not waiting for memory while waiting for the data for the other group(s).

| #  | App. | CTA-Aware | CTA-Aware-Locality | #  | App.   | CTA-Aware | CTA-Aware-Locality |

|----|------|-----------|--------------------|----|--------|-----------|--------------------|

| 1  | SAD  | 6%        | 42%                | 11 | SPMV   | 0%        | 8%                 |

| 2  | PVC  | 89%       | 90%                | 12 | JPEG   | 0%        | 0%                 |

| 3  | SSC  | 1%        | 8%                 | 13 | BFSR   | 2%        | 16%                |

| 4  | BFS  | 1%        | 17%                | 14 | SC     | 0%        | 0%                 |

| 5  | MUM  | 1%        | 2%                 | 15 | FFT    | 1%        | 1%                 |

| 6  | CFD  | 1%        | 2%                 | 16 | SD2    | 0%        | 0%                 |

| 7  | KMN  | 27%       | 49%                | 17 | WP     | 0%        | 0%                 |

| 8  | SCP  | 0%        | 0%                 | 18 | PVR    | 1%        | 2%                 |

| 9  | FWT  | 0%        | 0%                 | 19 | BP     | 0%        | 0%                 |

| 10 | IIX  | 27%       | 96%                |    | AVG-T1 | 8%        | 18%                |

Table 3.2: Reduction in L1 miss rates with the proposed warp scheduling mechanisms over baseline RR scheduling.