### **Edith Cowan University**

## **Research Online**

ECU Publications Pre. 2011

2007

# Design and Characterization of CMOS/SOI Image Sensors

Igor Brouk

Kamal Alameh Edith Cowan University

Yael Nemirovsky

Follow this and additional works at: https://ro.ecu.edu.au/ecuworks

Part of the Computer Sciences Commons

#### 10.1109/TED.2006.890585

This is an Author's Accepted Manuscript of: Brouk, I., Alameh, K., & Nemirovsky, Y. (2007). Design and Characterization of CMOS/SOI Image Sensors. IEEE Transactions on Electron Devices, 54(3), pp. 468-475. Available

© 2007 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

This Journal Article is posted at Research Online.

https://ro.ecu.edu.au/ecuworks/1498

# Design and Characterization of CMOS/SOI Image Sensors

Igor Brouk, Kamal Alameh, Senior Member, IEEE, and Yael Nemirovsky, Fellow, IEEE

Abstract—The design, operation, and characterization of CMOS imagers implemented using: 1) "regular" CMOS wafers with a 0.5- $\mu$ m CMOS analog process; 2) "regular" CMOS wafers with a 0.35- $\mu$ m CMOS analog process; and 3) silicon-oninsulator (SOI) wafers in conjunction with a 0.35- $\mu$ m CMOS analog process, are discussed in this paper. The performances of the studied imagers are compared in terms of quantum efficiency, dark current, and optical bandwidth. It is found that there is strong dependence of quantum efficiency of the photodiodes on the architecture of the image sensor. The results of this paper are useful for designing and modeling CMOS/SOI image sensors.

*Index Terms*—CMOS integrated circuits, image sensors, photodiodes, silicon-on-insulator (SOI) technology.

#### I. INTRODUCTION

MOS image sensors are currently drawing much attention because they have the potential to compete with charge-coupled device cameras. Camera-on-a-CMOS chips will be an inevitable component for future intelligent systems and are currently under intensive research worldwide because of their enormous market potential. Therefore, investigating and developing better imagers on a chip is highly important. This research focuses on new camera-on-chip architectures based on novel silicon-on-insulator (SOI) technology.

Currently, SOI technology is considered the most promising technology for improving the performance of CMOS devices without reducing dimensions. This technology offers the possibility of building electronic devices in a thin layer of silicon that is electrically isolated from the thick semiconductor substrate through the use of a buried insulating layer [1]. In the standard silicon technology, the semiconductor substrate is associated with undesirable effects, such as parasitic capacitances, high leakage currents, parasitic bipolar components, and, more importantly, interference between individual active devices or circuits built in the same integrated chip [1]–[4].

The well-known important advantages of SOI technology are the following: more effective isolation between adjacent devices implemented within SOI top (device) layer, reduced parasitic capacitances and short-channel effects, and immunization from ionization by atoms and radiations. In addition, the

Manuscript received August 1, 2006. The review of this paper was arranged by Editor J. Tower.

- I. Brouk and Y. Nemirovsky are with the Department of Electrical Engineering, Kidron Microelectronics Center, Technion—Israel Institute of Technology, Haifa 32000, Israel (e-mail: nemirov@ee.technion.ac.il).

- K. Alameh is with the Centre of Excellence for MicroPhotonic Systems, Edith Cowan University, WA 6027, Australia.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2006.890585

SOI technology provides the relative simplicity of the etching process, allowing chip back-side illumination.

The proposed new chip architecture, based on SOI and using the back-side illumination of back-side etched substrate, allows, in principle, to increase the fill factor (theoretically to 100%), to separate the photodiodes and electronics and, therefore, to eliminate the interaction between them, to implement more functions at the focal-plane pixel level and, finally, to separate the design and process optimization of photodiodes and analog readout.

This paper reports on the comparison of the performances of six CMOS image sensor architectures with front-side illumination fabricated at Tower Semiconductor Ltd. [5] using "regular" CMOS and SOI wafers, in conjunction with 0.5 and 0.35  $\mu$ m processes [6].

#### II. DESIGN

In general, the design of CMOS camera is based on the concept of active pixel sensors (APS) ([7]–[17] and references within). A typical block diagram of the camera is presented in [18] and [19] and includes a 2-D matrix of pixels, two addressing decoders for pixel selection during the reading phase ("Read column" and "Read row"), one decoder for reset of whole column, 1-D array of row switches and readout circuits, and analog buffers.

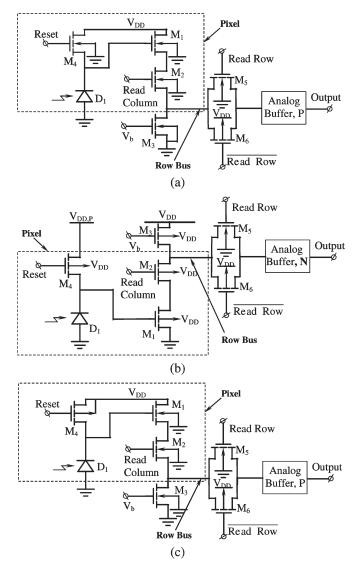

The matrix is organized as a square of pixels. APS can be designed on the base of n-channel MOS (nMOS) transistors, p-channel MOS (pMOS) transistors, or both nMOS and pMOS transistors (Fig. 1). Each pixel consists of one photodiode and three transistors, namely: 1) transistor M4 that performs the reset of photodiode; 2) transistor M1 that operates as a source follower; and 3) transistor M2 that operates as an analog selection switch. In addition to these elements, there are several elements, which are common within each row of APS, such as transistor M3 that provides current for the source follower and transistors M5 and M6 that operate as a pass-gate. Pixel selection is achieved by means of the row and column decoders. When activated, the selection switch connects the associated photodiode to the corresponding row bus. For the reading operation, the row decoder selects one row at a time, thereby connecting each pixel of addressed row to the matrix output. More specifically, the rows can be divided into several groups, where each group has the separate output and is served by a separate analog buffer. In this case, the row decoder selects the several rows simultaneously, one row in each group. The subsequent processing of the signal coming from the different outputs is performed by means of an analog multiplexer.

Fig. 1. Different designs of APS based on (a) nMOS transistors, (b) pMOS transistors, and (c) both nMOS and pMOS transistors.

In addition to the transistor types, APS can be designed with arbitrary dimensions, can use different types of the photodiodes, and can be fabricated using different processes. Two technologies provided by Tower Semiconductor Ltd. [5] have been attempted. The 0.5- $\mu$ m technology, which is the most established "Tower's" CMOS image sensor technology, was used as a starting point of the research. The second "Tower's" technology process (0.35  $\mu$ m) was run twice: for "regular" CMOS and SOI wafers, correspondingly. The "regular" CMOS wafers are p-type silicon epitaxial wafers ( $\sim$ 16–24  $\Omega$  · cm for 0.35- $\mu$ m process and  $\sim$ 24–36  $\Omega$  · cm for 0.5- $\mu$ m process) with epilayer thickness of  $\sim 5.5$ - $\mu$ m, whereas SOI wafers are characterized by the thickness of  $\sim$ 675  $\mu$ m,  $\sim$ 1- $\mu$ m-thick buried oxide layer and  $\sim 2-\mu$ m-thick p-type top (device) layer with resistivity of  $\sim$ 8–22  $\Omega \cdot$  cm, compatible with 0.35- $\mu$ m process. The substrates SOI were supplied by CANON and prepared using the ELTRAN process [20], [21] that involves oxidized wafer bonding and water-jet separation using a predefined porous silicon layer.

The CMOS analog process 0.5  $\mu$ m (twin-well on p-type epitaxial substrate, with single or double poly) of Tower Semiconductor Ltd. [5] is characterized by gate oxide of  $\sim$ 115 Å, corresponding to the core voltage of 5.0 V, n-well/p-well depth of  $\sim$ 1.15/1.6  $\mu$ m, correspondingly, n<sup>+</sup>/p<sup>+</sup> source/drain depth of  $\sim$ 0.3  $\mu$ m, and LOCOS isolation. The main highlights of the twin-well CMOS analog process (0.35  $\mu$ m) (with single or double poly) of Tower Semiconductor Ltd. are listed as follows: gate oxide of  $\sim$ 70 Å, corresponding to the core voltage of 3.3 V, n-well/p-well depth of  $\sim$ 1.2/0.9  $\mu$ m, correspondingly, n<sup>+</sup>/p<sup>+</sup> source/drain depth of  $\sim$ 0.2  $\mu$ m, and using dense poly buffered LOCOS isolation. In both processes, no microlens array or color filter array had been used.

In accordance with the diode model corresponding to 0.5- $\mu$ m process of Tower Semiconductor Ltd. [5], the leakage current density of n<sup>+</sup> imp./P-sub. diodes of large area (335  $\times$  335  $\mu$ m) is  $\sim$ 0.12  $\mu$ A/m² at room temperature. The maximum value of the leakage current density for 0.35- $\mu$ m process is 1 mA/m² both for n<sup>+</sup> imp./P-sub. and n-well/P-sub. diodes at room temperature.

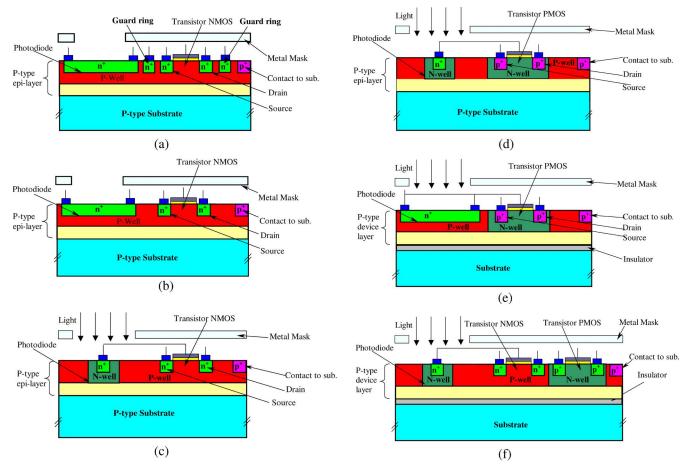

In this paper, the several APS implementations with the different combinations of design parameters as discussed below are compared. The total number of the imagers, which are understudy here, is six [18]. The first group of imagers is fabricated using 0.5  $\mu$ m technology process within "regular" CMOS wafers and includes the matrix of  $128 \times 128$  pixels ("Imager-1") and the matrix of  $64 \times 64$  pixels ("Imager-2") [18]. Both "Imager-1" and "Imager-2" are based on the pixels, consisting of nMOS transistors [Fig. 1(a)] and photodiode implemented by n<sup>+</sup> imp./P-sub. junction, while the photodiode occupies the area, which is free from the rest of electronics. The pixel size for both imagers is  $20 \times 20 \mu m$ , while the fill factor is  $\sim$ 35% for "Imager-1" and  $\sim$ 47% for "Imager-2." The difference between the fill factors is due to the additional guard ring surrounding the transistors within each pixel of "Imager-1" [see pixel cross sections in Fig. 2(a) and (b)]. This guard ring is implemented by the n<sup>+</sup> imp./P-sub. junction, connected to  $V_{\rm dd}$  and intended for elimination of the interaction between photodiodes and transistors within the

The advantage of the design with a large photodiode area is that the quantum efficiency is maximized, because the generated photocarriers have the higher probability to reach the p-n junction and to contribute to the photocurrent [22], [23]. On the other hand, a large area photodiode results in higher integration capacitance and significant leakage current, which can be the major limitation for this design.

The second group of imagers is fabricated using 0.35- $\mu$ m technology process within "regular" CMOS wafers and includes a matrix of  $256 \times 256$  pixels [18]. The first imager of this group ("Imager-3") is based on pixels consisting of nMOS transistors [see Fig. 1(a)], whereas the second one ("Imager-4") uses pixels based on pMOS transistors [see Fig. 1(b)]. The pixel size for both imagers is  $20 \times 20 \ \mu$ m, while the fill factors are  $\sim 53\%$  and  $\sim 37\%$  for "Imager-3" and "Imager-4," respectively [Fig. 2(c) and (d)]. All pixels have no guard ring. Each of the two types of APS has the photodiode implemented by n-well/P-sub. of minimal area (see Table I). The advantage of this

Fig. 2. Cross sections of the pixels (a–b) fabricated using 0.5-μm technology process within CMOS wafer and based on nMOS transistors with additional guard ring, (a) "Imager-1," and without guard ring, (b) "Imager-2;" (c–d) fabricated using 0.35-μm technology process within CMOS wafer and based on nMOS transistors, (c) "Imager-3," and pMOS transistors, (d) "Imager-4;" and (e–f) fabricated using 0.35-μm technology process within SOI wafer and based on pMOS transistors, (e) "Imager-5," and both nMOS transistors and pMOS transistors, (f) "Imager-6."

design is the minimal leakage current resulting from minimizing the photodiode area. On the other hand, the main disadvantage of this design is the lower quantum efficiency due to the minimal photodiode area [22], [23].

The third group of imagers is fabricated using 0.35- $\mu$ m technology process within SOI wafers and also includes a matrix of  $256 \times 256$  pixels [18], [19]. The first imager of this group ("Imager-5") is based on pMOS transistors [see Fig. 1(b)], whereas the second one ("Imager-6") is based on both nMOS and pMOS transistors [see Fig. 1(c)]. Both imagers have a pixel size of  $10 \times 10~\mu$ m, while the fill factor is  $\sim 20\%$  for "Imager-5" and  $\sim 23\%$  for "Imager-6." Fig. 2(e) and (f) exhibit the cross sections of these pixels. Each type of APS also has no guard ring. "Imager-5" and "Imager-6" are based on the photodiodes implemented by n<sup>+</sup> imp./P-sub. and n-well/P-sub. junctions, correspondingly, while each photodiode has an area close to the minimal allowed value (shown in Table I).

Thus, the different designs are classified into three groups according to the applied process and wafer type, namely: 1) 0.5- $\mu$ m process in "regular" CMOS wafers; 2) 0.35- $\mu$ m process in "regular" CMOS wafers; and 3) 0.35- $\mu$ m process in SOI wafers. In addition, the different designs based on nMOS and pMOS transistors are compared. The main design parameters are summarized in Table I, which also specifies the

structure of the designed photodiodes. Table I also summarizes measured results discussed in Section III.

#### III. MEASUREMENT RESULTS

The results reported in this paper include the measurements of photodiode quantum efficiency and leakage current, and the photos are captured by the studied imagers.

The quantum efficiency was measured using a monochromator SpectraPro-150, comprising a light source, the monochromator itself, and an analog-to-digital converter. In general, the quantum efficiency is expressed as

$$\eta = \frac{hcI_{\lambda}}{\lambda q P_{\text{opt}} FF} \tag{1}$$

where  $I_{\lambda}=C_{d}\Delta V_{d}/t_{\rm int}$  is the measured photocurrent,  $\lambda$  is the wavelength, h is Plank's constant, c is the light velocity, q is the electron charge,  $P_{\rm opt}$  is the total optical power, irradiating each pixel,  $C_{d}$  is the effective integration capacitance at the photodiode node,  $\Delta V_{d}$  is the photodiode voltage discharging due to the light illumination,  $t_{\rm int}$  is the integration time, and FF is the fill factor. The system was calibrated by illuminating a calibrated large-area p-i-n photodiode connected to Optical Power Meter 1830-C (New Port).

Dark Imager type Camera Process Photo-Photo-Peak Comments description diode diode current quantum type area. density at efficiency  $[\mu m^2]$ ~300°K, (Q.E.) [fA/µm²] CMOS, based on n<sup>+</sup> imp. . 0.041 ~70% High Q.E. and low dark "Imager-1"  $0.5 \, \mu m$ 143 1-st group) NMOS transistors P-type at ~520nm current density due to with guard ring the large photodiode area and process quality CMOS, based on 188 0.037 High Q.E. and low dark 'Imager-2' 0.5 µm n<sup>+</sup> imp. / ~70% 1<sup>-st</sup> group) NMOS transistors P-type at ~520nm current density due to without guard ring the large photodiode area and process quality 'Imager-3' CMOS, based on 0.35 µm N-well / ~40% Reduced O.E. due to 2<sup>-nd</sup> group) at ~460-530 VMOS transistors P-type lower junction area (see [24]) nm CMOS, based on 0.15 'Imager-4"  $0.35 \mu m$ N-well / 4 ~6% Lower Q.E. due to the PMOS transistors 2<sup>-nd</sup> group) P-type at ~460-520 large area N-well including three PMOS nm ransistors, which competes in collecting photo-generated carriers 'Imager-5' SOI, based on 0.35 μm n<sup>+</sup> imp. / 1 <<1 ~2% Low Q.E. due to the (3<sup>-d</sup> group) PMOS transistors P-type at ~390-450 large area N-well including three PMOS nm ransistors, which competes in collecting photo-generated carriers "Imager-6" SOI, based on  $0.35 \, \mu m$ N-well / 3.2 15 ~40% The exact mechanism both NMOS and 3<sup>-a</sup> group) P-type at ~430-520 causing the high dark PMOS transistors current for "Imager-6" needs to be further investigated

TABLE I

SUMMARY OF THE MAIN DESIGN PARAMETERS AND MEASUREMENT RESULTS

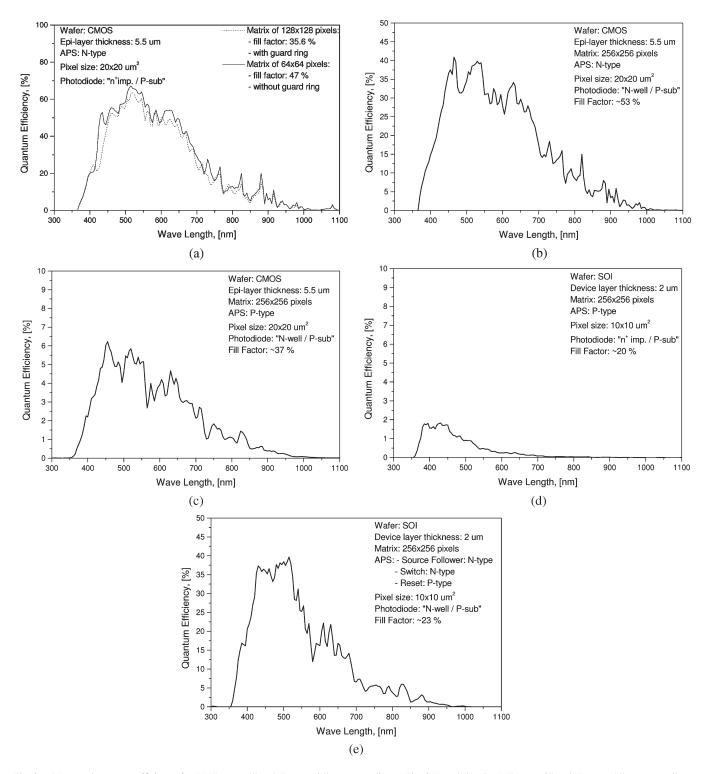

Fig. 3 shows the measured quantum efficiency spectra for all types of imagers. First of all, it is noticed that the quantum efficiency spectra for both "Imager-1" and "Imager-2" are very similar [Fig. 3(a)]. This proves that the additional guard ring surrounding the transistors within each pixel does not collect the photocarriers and, hence, does not prevent the transistors from diffusing the photocarriers. This phenomenon is due to the small depth of n<sup>+</sup> implantation region, which has insignificant interaction with photocarriers diffusing toward the transistors region. The second important observation is that both "Imager-1" and "Imager-2" exhibit a high peak quantum efficiency ( $\sim$ 70%) around the 520-nm wavelength and also a broad optical "bandwidth" (~400-700 nm). These experimental results are in good agreement with previously reported structures having a relatively large thickness epilayer ( $\sim$ 5.5  $\mu$ m) and a large photodiode area [22], [23].

Fig. 3(b) and (c) shows the measured quantum efficiency spectra for "Imager-3" and "Imager-4." It is noticed that for these imagers, the optical "bandwidth" and the wavelength at the maximum quantum efficiency are similar to those of "Imager-1" and "Imager-2." This is the result of using the same epilayer thickness for "Imager-1" to "Imager-4." On the other hand, the measured maximum quantum efficiencies for "Imager-3" and "Imager-4" ( $\sim$ 40% and  $\sim$ 6%, correspondingly) have lower values in comparison to "Imager-1" and "Imager-2," mainly because of the smaller areas of the photodiodes of "Imager-3" and "Imager-4" [22], [23] (see Table I).

The significant difference between the values of the quantum efficiency of "Imager-3" and "Imager-4" can be explained as follows. Since the pMOS transistors are implemented within n-well, each pixel of "Imager-4" has two n-wells: the first n-well forms the photodiode and the second is the n-well that includes the three pMOS transistors. The junction area of the photodiode is negligible in comparison to the area of the second n-well. Both "Imager-3" and "Imager-4" have the photodiodes of the same type and dimensions (Table I) and, therefore, the contribution of photoholes generated within n-well (as a part of the photodiode) is the same for "Imager-3" and "Imager-4." However, in "Imager-4," a substantial portion of the photoelectrons generated within the p-type epilayer contributes to the current through the second n-well, where the pMOS electronics is implemented, rather than to the photodiode current.

Fig. 3(d) and (e) displays the measured quantum efficiency for "Imager-5" and "Imager-6." First of all, one can see that the wavelengths corresponding to the maximum quantum efficiency are moved toward shorter wavelengths (in comparison to all previous imagers). The second observation is that the optical "bandwidth" is narrower both for "Imager-5" and for "Imager-6" ( $\sim$ 400–550 nm). These results are attributed to the lower thickness of the silicon top layer of SOI wafer in comparison with the thickness of the epilayer of CMOS wafer. As for the maximum value of the quantum efficiency, it reaches  $\sim$ 40% for "Imager-6," which is similar to "Imager-3," and  $\sim$ 2% for "Imager-5." The last value is very low, and

Fig. 3. Measured quantum efficiency for (a) "Imager-1" and "Imager-2," corresponding to Fig. 2(a) and (b); (b–c) "Imager-3" and "Imager-4," corresponding to Fig. 2(c) and (d); and (d–e) "Imager-5" and "Imager-6," corresponding to Fig. 2(e) and (f).

it is caused by the n-well including the pMOS transistors, which occupies most part of the pixel area. In addition, one can see that the wavelength region corresponding to the maximum quantum efficiency of "Imager-5" is shifted toward shorter wavelengths in comparison to the same parameter of "Imager-6" (Table I). The reason of this phenomenon is the n<sup>+</sup> implantation/p-type implementation of the photodiode in "Imager-5" [23], [24]. The relatively high quantum efficiency

of "Imager-6" corresponds to that of "Imager-3," which is implemented by nMOS transistors only. This demonstrates that a relatively small-area second n-well per pixel, having a single pMOS transistor, almost has no influence on the photocarriers contribution.

Table I presents a summary of leakage (dark) current measurements [18]. For this experiment, one pixel from each matrix was chosen constantly by means of addressing

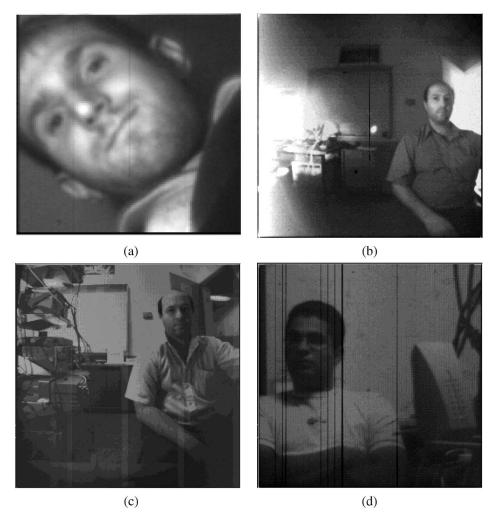

Fig. 4. Several photos that have been done by means of (a) "Imager-1," (b) "Imager-3," (c) "Imager-4," and (d) "Imager-6."

decoders, while the "Reset" transistors were connected to the low-frequency square wave with a duty cycle of 50%. When the reset signal was low, integration was performed. Knowing the integration time, voltage change, and integration capacitance at the photodiode node, it was possible to calculate the leakage current through the photodiode node. First of all, one can see that both "Imager-1" and "Imager-2" demonstrate the best results in terms of leakage current density. This was due to the large area of the photodiodes, which reduced the effect of periphery regions around the photodiode on the dark current density [22], as well as the process quality, as manifested by the reported low dark current. Second, regarding the pixel implementation (Fig. 1), the pixels based on pMOS transistors have a lower dark current density in comparison with the pixels, which are based on nMOS transistors. The reason for this result is the fact that the area of the peripheral regions contributing to the dark current was smaller for the architectures based on pMOS transistors. As explained earlier, the additional n-well required for implementing the pMOS transistor competes with the collection of the generated carriers, with the photodiodes. Thus, both the quantum efficiency as well as the dark current are reduced in this architecture, including "Imager-5" (realized using SOI wafers), which exhibits the same results as "Imager-4" based on "regular CMOS wafer. Third, the photodiodes implemented using n-well/p-type device layers fabricated within SOI wafers and referred to as "Imager-6" in Table I exhibit the highest dark current. "Imager-6" is unique in two aspects, namely: 1) it is implemented in SOI wafers and 2) it includes both nMOS and pMOS transistors. We have already demonstrated that the presence of pMOS transistors reduces the dark current. Hence, we attribute the higher dark current either to the additional interface between the p-type device layer and the buried oxide or the crystalline quality of the SOI wafers. The exact mechanism causing the high dark current for "Imager-6" needs to be further investigated.

Fig. 4 shows several photos made by the aforementioned imagers. It should be noted that the optimization of the optics was not properly done. One can see that the best quality photo corresponds to "Imager-1" (designed and fabricated using 0.5  $\mu$ m process), demonstrating high quantum efficiency, wide optical "bandwidth," low leakage current density, and a relatively large number of the pixels within the matrix. This result was achieved due to the following: 1) the large area of the photodiodes; 2) the APS architecture based on only nMOS transistors, leading to the highest quantum efficiency; 3) the relatively thick epitaxial layer of the "regular" CMOS wafers

(around 5.5  $\mu$ m), leading to the wider optical bandwidth; and 4) the "quality" of technology process 0.5  $\mu$ m.

#### IV. CONCLUSION

This paper presents the electrooptical characterization of three groups of CMOS image sensors with front-side illumination based on the different technologies, namely: 1) CMOS 0.35  $\mu \rm m$ -technology; 2) novel CMOS/SOI 0.35  $\mu \rm m$ -technology; and 3) CMOS 0.5  $\mu \rm m$ -technology. The performances of image sensor architectures fabricated using the above technology processes have been compared in terms of quantum efficiency, dark current, and photo quality. Measured results have been compared with the quality of images captured using these image sensors with simple optics and low illumination.

It has been found that there is strong dependence of quantum efficiency of the photodiodes on the architecture of the image sensor. The maximum value of peak quantum efficiency was obtained for the architectures based on nMOS transistors, which do not contain additional n-wells. The second important factor that affected the value of quantum efficiency was the photodiode area (the larger the photodiode area, the higher the quantum efficiency). For the value of optical bandwidth, the best results were obtained for the architectures fabricated within a "regular" CMOS wafer, of epilayer thickness around 5.5  $\mu$ m. SOI wafers with a device layer thickness of 2  $\mu$ m exhibited a narrower optical bandwidth for all the studied imager architectures. The dark current is strongly affected by the pixel architecture, photodiode structure and dimensions, as well as the technology process. Using a state-of-the-art characterization facility, the best results were obtained for the image sensors designed and fabricated using process 0.5  $\mu$ m. The measured lowest dark current correlates with transistor noise measurements, which were carried out earlier [22].

The results presented in this paper are in good agreement with [22]–[33] for CMOS APS within "regular" and SOI wafers. The single most significant feature of CMOS Image Sensors on SOI, compared to bulk, besides the shift in quantum efficiency to shorter wavelengths, is related to the leakage current. While leakage currents in various circuit designs in SOI were studied and reported [34], the specific designs reported here need to be further studied and optimized to reduce the leakage current.

#### REFERENCES

- M. L. Alles, "Thin-film SOI emerges," *IEEE Spectr.*, vol. 34, no. 6, pp. 37–45, Jun. 1997.

- [2] D. Tsoukalas, C. Tsamis, D. N. Kouvatsos, P. Revva, and E. Tsoi, "Reduction of the reverse short channel effect in thick SOI MOSFETs," *IEEE Electron Device Lett.*, vol. 18, no. 3, pp. 90–92, 1997.

- [3] E. P. Ver Ploeg, T. Watanabe, N. A. Kistler, J. C. S. Woo, and J. D. Plummer, "Elimination of bipolar induced breakdown in fully-depleted SOI MOSFET's," in *IEDM Tech. Dig.*, 1992, pp. 337–340.

- [4] A. Afzalian and D. Flandre, "Modeling of the bulk versus SOI CMOS performances for the optimal design of APS circuits in low-power low-voltage applications," *IEEE Trans. Electron Devices*, vol. 50, no. 1, pp. 106–110, Jan. 2003.

- [5] Migdal Haemek, Israel: Tower Semicond. Ltd. [Online]. Available: http://www.towersemi.com

- [6] I. Brouk and Y. Nemirovsky, "Noise characterization of the 0.35  $\mu$ m CMOS analog process implemented in regular and SOI wafers," in *Proc.*

- 11th IEEE Int. Conf. Electron., Circuits and Syst., Dec. 13–15, 2004, pp. 171–174.

- [7] E. R. Fossum, "CMOS image sensor: Electronic camera-on-a-chip," *IEEE Trans. Electron Devices*, vol. 44, no. 10, pp. 1689–1698, Oct. 1997.

- [8] S. Mendis, S. Kemeny, and E. R. Fossum, "A 128 × 128 CMOS active pixel image sensor for highly integrated imaging systems," in *IEDM Tech. Dig.*, 1993, pp. 583–586.

- [9] —, "CMOS active pixel image sensor," *IEEE Trans. Electron Devices*, vol. 41, no. 3, pp. 452–453, Mar. 1994.

- [10] S. K. Mendis, S. E. Kemeny, R. C. Gee, B. Pain, Q. Kim, and E. R. Fossum, "CMOS active pixel image sensors for highly integrated imaging systems," *IEEE J. Solid-State Circuits*, vol. 32, no. 2, pp. 187– 197, Feb. 1997.

- [11] A. Simoni, G. Torelli, F. Maloberti, A. Sartori, M. Gottardi, and L. Gonzo, "256 × 256 Pixel CMOS digital camera for computer vision with 32 algorithmic ADCs on board," *Proc. Inst. Electr. Eng.—Circuits Devices System*, vol. 146, no. 4, pp. 184–190, Aug. 1999.

- [12] T. Chen, P. Catrysse, A. El Gamal, and B. Wandell, "How small should pixel size be?" in *Proc. SPIE—Sensors and Camera System Scientific, Industrial, and Digital Photography Applications*, M. M. Blouke, N. Sampat, G. M. Williams, Jr., and T. Yeh, Eds., 2000, vol. 3965, pp. 451–459.

- [13] A. Sartori, F. Maloberti, A. Simoni, and G. Torelli, "2-D photosensor array with integrated charge amplifier," *Sens. Actuators A, Phys.*, vol. 46/47, no. 1–3, pp. 247–250, Jan. 1995.

- [14] T. Danov, I. Shcherback, and O. Yadid-Pecht, "Study of CMOS APS responsivity enhancement: Ring-shaped photodiode," *IEEE Trans. Electron Devices*, vol. 52, no. 1, pp. 126–129, Jan. 2005.

- [15] P. Lee, A. Simoni, A. Sartori, and G. Torelli, "A photosensor array for spectrophotometry," *Sens. Actuators A, Phys.*, vol. 46/47, no. 1–3, pp. 449–452, Mar. 1995.

- [16] A. Simoni, G. Torelli, F. Maloberti, A. Sartori, S. E. Plevridis, and A. N. Birbas, "A single-chip optical sensor with analog memory for motion detection," *IEEE J. Solid-State Circuits*, vol. 30, no. 7, pp. 800– 806, Jul. 1995.

- [17] S. Decker, D. McGrath, K. Brehmer, and C. G. Sodini, "A 256 × 256 CMOS imaging array with wide dynamic range pixels and column-parallel digital output," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 2081–2091, Dec. 1998.

- [18] I. Brouk, "Silicon-on-insulator (SOI) CMOS image sensor with front and back-side illumination," Ph.D. research thesis, Technion—Israel Institute Technology, Haifa, Israel, 2005. supervised by Prof. Y. Nemirovsky.

- [19] I. Brouk and Y. Nemirovsky, "CMOS SOI image sensor," in *Proc.* 11th IEEE Int. Conf. Electron., Circuits and Syst., Dec. 13–15, 2004, pp. 156–159.

- [20] ELTRAN Business Center, Canon Inc., ELTRAN (Epitaxial Layer Transfer), Technology for Manufacturing SOI Wafers. [Online]. Available: http://www.canon.com

- [21] E. Socher, S. M. Beer, and Y. Nemirovsky, "Temperature coefficient of current of CMOS SOI transistors for sensing applications," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2784–2790, 2005.

- [22] I. Brouk, "Study of CMOS photodiodes and low noise analog readout for visible photon detection," M.Sc. research thesis, Technion—Israel Institute Technology, Haifa, Israel, 2000. supervised by Prof. Y. Nemirovsky and Dr. I. Bloom.

- [23] I. Brouk, A. Ezion, and Y. Nemirovsky, "Characterization of CMOS photodiodes for image sensors," in *Proc. 11th Int. Meeting Electro-Opt. and Microelectron.*, Tel Aviv, Israel, Nov. 9–11, 1999, pp. 225–227.

- [24] I. Brouk and Y. Nemirovsky, "Dimensional effects in CMOS photodiodes," *Solid State Electron.*, vol. 46, no. 1, pp. 19–28, Jan. 2002.

- [25] W. Zhang, M. Chan, and P. K. Ko, "Performance of floating gate/body tied SOI NMOSFET photo-detector on SOI substrate," *IEEE Trans. Electron Devices*, vol. 47, no. 7, pp. 1375–1384, Jul. 2000.

- [26] H. Yamamoto, K. Taniguchi, and C. Hamaguchi, "High sensitivity SOI MOS photodetector with self-amplification," *Jpn. J. Appl. Phys.*, vol. 35, no. 2B, pp. 1382–1386, Feb. 1996.

- [27] C. Xu, W. Zhang, and M. Chan, "A low voltage hybrid bulk/SOI CMOS active pixel image sensor," *IEEE Electron Device Lett.*, vol. 22, no. 5, pp. 248–250, May 2001.

- [28] C. Shen, C. Xu, R. Huang, W. Zhang, P. K. Ko, and M. Chan, "A new active pixel sensor (APS) architecture on SOI substrate for low voltage operation," in *Proc. 9th Int. Symp. IC Technol., Syst. and Appl.*, Singapore, Sep. 3–5, 2001, pp. 275–278.

- [29] W. Zhang, M. Chan, S. K.-H. Fung, and P. K. Ko, "A high responsivity photodetector on SOI substrate," in *Proc. IEEE Workshop Charge-Coupled Devices and Adv. Image Sens.*, Bruges, Belgium, Jun. 5–7, 1997, pp. P91–P94.

- [30] N. Ricquier and B. Dierickx, "Active pixel CMOS image sensor with onchip nonuniformity correction," in *Proc. IEEE Workshop CCD's and Adv. Image Sens.*, Dana Point, CA, Apr. 20–22, 1995, pp. 20–21.

- [31] R. H. Nixon, S. E. Kemeny, B. Pain, C. O. Staller, and E. R. Fossum, "256 × 256 CMOS active pixel sensor camera-on-a-chip," *IEEE J. Solid-State Circuits*, vol. 31, no. 12, pp. 2046–2050, Dec. 1996.

- [32] I. Shcherback and O. Yadid-Pecht, "Prediction of CMOS APS design enabling maximum photoresponse for scalable CMOS technologies," *IEEE Trans. Electron Devices*, vol. 51, no. 2, pp. 285–287, Feb. 2004.

- [33] O. Yadid-Pecht and R. Etienne-Cummings, "Guest editorial, special issue on smart sensors," *Analog Integr. Circuits Signal Process. J.*, vol. 39, no. 3, pp. 223–224, Jun. 2004.

- [34] A. Marshall and S. Natarajan, SOI Design: Analog, Memory and Digital Techniques. Boston, MA: Kluwer, 2002.

Igor Brouk was born in Moscow, Russia, on January 17, 1968. He received the electronic engineer degree (with honors) from the Moscow Institute of Aircraft Technology, in 1990 and the degree of M.Sc. in electrical engineering and the Ph.D. degree from the Technion—Israel Institute of Technology, Haifa, Israel, in 2000 and 2005, respectively. His M.Sc. thesis has included the study of CMOS photodiodes and low noise analog readout for visible photon detection. His Ph.D. degree has focused on the investigation of the different architectures of image

sensors based on new CMOS/SOI technology in comparison to regular CMOS image sensors. This research has concentrated on the physical, the design, and the noise issues associated with active pixel sensors in CMOS/SOI technology.

His research interests include CMOS photodiodes, image sensors, low noise analog readout, and analog electronics in VLSI.

**Kamal Alameh** (S'89–M'92–SM'04) received the Ph.D. degree in photonics from the University of Sydney, Sydney, Australia, in 1993.

He is currently a Professor of MicroPhotonics and the Director of the Electron Science Research Institute, Edith Cowan University, Joondalup, Australia. He is also the Director of the Western Australia (WA) Centre of Excellence for MicroPhotonic Systems. He formerly occupied the post of Senior Research Fellow with the Photonics Group at the University of Sydney, where he worked for

ten years. He has filed 15 patents in MicroPhotonics. His research interests include MicroPhotonics, Opto-VLSI, optical interconnects, RF photonic signal processing, magnetophotonic crystals, MicroPhotonics-based sensors, and reconfigurable photonic systems for future MAN, LAN, and fiber-to-the-home applications.

Dr. Alameh has won more than \$10 million in competitive grants and external research contracts.

Yael Nemirovsky (SM'86–F'99) received the D.Sc. degree from the Technion—Israel Institute of Technology, Haifa, Israel.

She is a Faculty Member of the Department of Electrical Engineering, Kidron Microelectronics Center, Technion—Israel Institute of Technology. She had been involved in II–VI compounds and devices for Infra Red Focal Plane Arrays (IRFPAs) and medical imaging. She is a pioneer of microelectromechanical systems research in Israel and, in the last decade, her research has focused on microop-

toelectromechanical systems. She has published approximately 170 papers in refereed journals, copresented over 200 talks in conferences, and filed for several patents.

Prof. Nemirovsky received the Israeli national "Award for the Security of Israel" and Technion awards for "Best Teacher" and "Novel Applied Research." She also received the Kidron Foundation award for "Innovative Applied Research" and the U.S.-based R&D 100 2001 award recognizing the top 100 new inventions and products of the year.