Received November 15, 2020, accepted January 19, 2021, date of publication January 25, 2021, date of current version January 29, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3054001

# **Design and Implementation of Seventeen Level Inverter With Reduced Components**

C. DHANAMJAYULU<sup>101,2</sup>, (Member, IEEE), DEVALRAJU PRASAD<sup>101</sup>, SANJEEVIKUMAR PADMANABAN<sup>102</sup>, (Senior Member, IEEE), PANDAV KIRAN MAROTI<sup>102</sup>, (Member, IEEE), JENS BO HOLM-NIELSEN<sup>102</sup>, (Senior Member, IEEE), AND FREDE BLAABJERG<sup>103</sup>, (Fellow, IEEE)

<sup>1</sup>School of Electrical Engineering, Vellore Institute of Technology (VIT) University, Vellore 632014, India

Corresponding authors: C. Dhanamjayulu (dhanamjayulu.c@vit.ac.in) and Sanjeevikumar Padmanaban (san@et.aau.dk)

This work was supported by the Danida Mobility Grant, responsible for the Ministry of Foreign Affairs of Denmark (MFA), Act 7 on Denmark's International Development Cooperation, under Project 19-MG06AAU.

**ABSTRACT** The multilevel inverters (MLI) are resourceful in producing a voltage waveform with superior-quality staircase counterfeit sinusoidal and depressed harmonic distortion (THD). Several conventional topologies are proposed to realize the MLI however, the limitations of these topologies may involve more DC sources and power-switching devices, and less THD, which in turn, increases the cost and size of the inverter. These drawbacks can be eliminated with the proposed hybrid Cascaded H-Bridge Multilevel Inverter with reduced components topology. As compared with the established MLI topologies the recommended topology having a reduced number of DC sources, power-switching devices, component count level factor, lesser TSV, more efficient, lesser THD, and cost-effective. The proposed MLI is a blend of a single-phase T-Type inverter and an H-Bridge module made of sub switches. This article incorporates the design and simulation of the multilevel inverter with staircase PWM technique. Further, the 9-level and 17-level MLI is examined with different combinational loads. The proposed inverter is stable during nonlinear loads, and it is well suited for FACTS and renewable energy grid-connected applications. An operational guideline has been explained with correct figures and tables. The Output voltage wave is realized in numerical simulation. Finally, the experimental demonstrations were performed by implementing a hardware prototype setup for both linear and nonlinear loads using the dSPACE controller laboratory.

**INDEX TERMS** Hybrid cascaded H-bridge multilevel inverter with reduced components, pulse width modulation (PWM), total harmonics distortion (THD).

#### I. INTRODUCTION

Present in many industrial applications has bid higher power appliances in the last couple of years. A couple of medium voltage service appliance requires high-power and medium voltage level; it is challenging directly connect only one power electronic switch to the medium power grid. To overcoming this, the multilevel inverters (MLIs) were developed in 1975 as a substitute in medium voltage high-power circumstances [1]. MLIs are turning into a well-known option to two-level inverters in the view of their several advantages,

The associate editor coordinating the review of this manuscript and approving it for publication was Jenny Mahoney.

such as lesser harmonic distortion, simplified filters, better wave capability taking after a sinusoidal output, and reduced voltage stress dv/dt up on the switches, because of excellent power quality, MLIs are broadly used in all disciplines of electrical engineering, for example, renewable energy conversion, high voltage DC transmission, distributed generation (DG) system, modern drive applications, uninterruptible power supplies, and so on [2]. MLI's incorporate with power semiconductor components and various DC links to build up staircase waveform tends towards sinusoidal. Mainly three traditional multilevel inverter topologies have existed: they are neutral point clamped (NPC), cascaded H-bridge (CHB), and flying capacitors (FCs). Out of these, because of modular

<sup>&</sup>lt;sup>2</sup>Center for Bioenergy and Green Engineering, Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark

<sup>&</sup>lt;sup>3</sup>Center of Reliable Power Electronics (CORPE), Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark

topology CHB-MLI having high voltage and power levels also more reliable, it requires more power semiconductor switches [3], hence switching losses increase and increasing the size, and overall cost of the circuit. In the view of these demerits, considerable MLIs were originated with the particularized objective of minimizing the quantity of power electronic devices, such topologies are called as reduced device count MLIs [4]. The topology in [5] suggested a basic structure with eight unidirectional and one bidirectional switch to produce 15 levels, authors in [6] proposed the symmetric configuration to produce higher levels but it requires more capacitors and the design suffers from higher standing voltages across the devices. The circuit in [7] is a nine-level inverter with twelve switches; three different frames are cascaded in [9] to get the desired nine-level output with ten switches, authors in [10] developed an S<sup>3</sup>CM with twelve switches, two capacitors, and one DC source to synthesize nine levels. A modified S<sup>3</sup>CM was proposed in [11] to produce nine levels with seven switches and two capacitors; however, it needs two DC voltage sources. To overcome the demerits in [10] and [11] a compact switched capacitor multilevel inverter was proposed in [12]. A Square T-Type topology was proposed in [13] to produce seventeen levels with four DC power sources. A modified ST-type topology known as K-type structure in [14] uses two additional switches to deliver thirteenlevels and reduces the DC sources to two by changing two capacitors. T-Type inverter topology without H-Bridge was proposed in [15] to achieve different higher levels at various load conditions with ten power switches, including two bidirectional switches. A generalized symmetric cascaded topology to reduce the total standing voltage was presented in [16] it uses a new h-type topology for both symmetric and asymmetric configuration. A higher-level inverter topology suitable for both high and low switching frequencies was proposed in [17]. Besides this [22]-[25] have been presented the reduced MLI topologies to minimize the devices count and stress voltage of the power switches.

This article highlights the reestablish framework of hybrid CHB-MLI topology with the prime objective of a minimized number of switches and increased output levels. Hence, the introduced design is named 'Hybrid Cascaded H-Bridge Multilevel Inverter with Reduced Components'. The remnant of the work is systematized: the proposed 9 level and seventeen levels Hybrid CHB-MLI topology are enlightened in Section II, in Section III calculated the power losses of the proposed multilevel inverter, homogeneity of parameters between the proposed MLI and standardized topologies are summarized in Section IV, Simulation, and test-based prototype results of proposed topology were executed in Section V, and at the end, conclusions are made in Section VI.

# II. PROPOSED HYBRID CASCADED H-BRIDGE MULTILEVEL INVERTER

#### A. BASIC 9 LEVEL INVERTER TOPOLOGY

In this section, various issues related to Cascaded H-Bridge MLIs are addressed and the proposed hybrid Cascaded

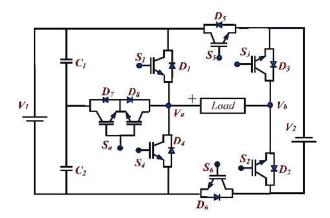

H-Bridge Multilevel Inverter with reduced components is presented by improvisation of CHB-MLI [8] for the valuation of quality output voltage with lower THD, reduced number of switches, and minimized the dv/dt stress on switches. The structure of the proposed 9 level inverters is incorporated with two DC sources  $V_1,\,V_2,\,$  and six unidirectional switches from S<sub>1</sub> to S<sub>6</sub> along with bidirectional switch S<sub>a</sub> and two Capacitors C<sub>1</sub>, C<sub>2</sub> which are connected in a blend of single-phase T-Type inverter and a module of H-Bridge made of sub switches are depicted in FIGURE 1. The specific arrangement reduces the additional DC source requirement also simplifies the number of switches needed. For a superior comprehension of working and the functioning of the introduced topology, various working modes have been represented along with conducting power electronic devices and path of load current I<sub>0</sub> as depicted in FIGURE 2.

FIGURE 1. Proposed hybrid cascaded H-Bridge multilevel inverter topology.

#### 1) OPERATING MODES

In this portion, the proposed inverter operation is explained through the various modes of output voltage levels produced in a steady-state. In this, the DC source voltage  $(V_{DC})$  is equally shared by the two DC link capacitors  $C_1$  and  $C_2$  with equal magnitudes, i.e.,  $V_{C1} = V_{C2} = V_{DC}/2$ .

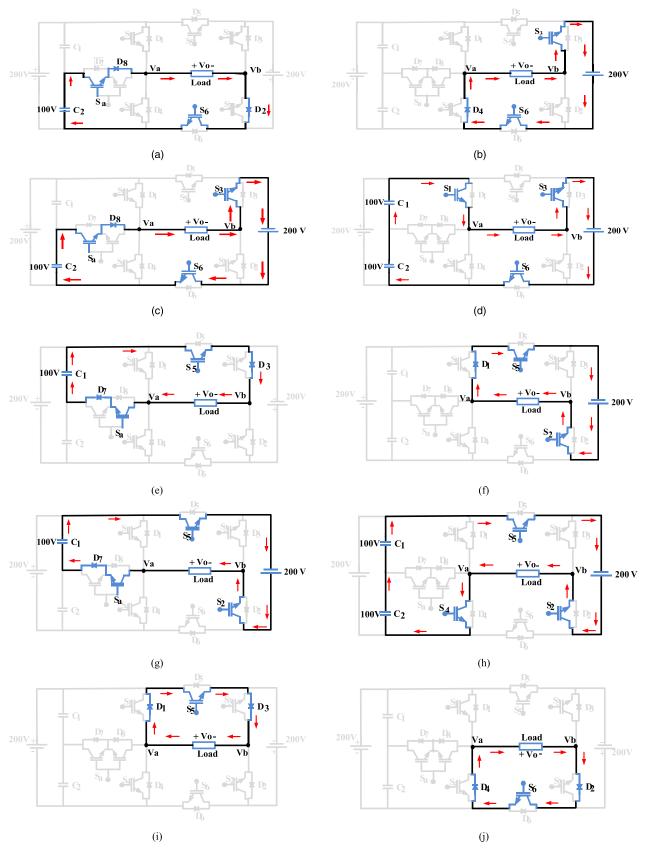

*Mode 1:* Capacitor,  $C_2$  acts as a voltage source, and bidirectional switch  $S_a$ , Switches  $S_2$ ,  $S_6$  are in conduction state hence the path of load current ( $I_0$ ) is through  $C_2$ -  $S_a$ -  $D_8$ -load-  $D_2$ - $S_6$ - $C_2$ , the output voltage level is +  $V_{DC}/2$ , i.e. +100V.

*Mode 2:* Operation voltage source  $V_2$  and switches  $S_6$ ,  $S_4$ ,  $S_3$  are in conduction state; hence the path of load current  $I_0$  is through  $V_2$ - $S_6$ - $D_4$ -load- $S_3$ - $V_2$ , the output voltage level is +  $V_{DC}$ , i.e. +200V.

*Mode 3:* Voltage source  $V_2$ , capacitor  $C_2$  acts as voltage sources, and bidirectional switch  $S_a$ , switches  $S_6$ ,  $S_3$  are in conduction state hence the path of load current  $I_0$  is through  $V_2$ - $S_6$ - $C_2$ - $S_a$ - $D_8$ -load- $S_3$ - $V_2$ , the output voltage level is +3  $V_{DC}/2$ , i.e. +300 volts.

*Mode 4:* Voltage source  $V_2$ , capacitors  $C_1$ , and  $C_2$  acts as voltage sources, and switches  $S_6$ ,  $S_1$ ,  $S_3$  are in conduction state hence the path of load current  $I_0$  is through

FIGURE 2. Operating modes (a) Mode-1, (b) Mode-2, (c) Mode-3, (d) Mode-4, (e) Mode-5, (f) Mode-6, (g) Mode-7, (h) Mode-8, (i) Mode-9, (j) Mode-10.

$V_2$ - $S_6$ - $C_2$ - $C_1$ -  $S_1$ -load- $S_3$ - $V_2$ , the output voltage level is  $+2V_{DC}$ , i.e. +400V.

*Mode 5:* Capacitor,  $C_1$  acts as voltage sources and bidirectional switch  $S_A$ , switches  $S_5$ ,  $S_3$  are in conduction state hence the path of load current  $I_0$  is through  $C_1$ - $S_5$ - $D_3$ -load- $S_a$ - $D_7$ - $C_1$ , the output voltage level is  $(-V_{DC}/2)$ , i.e. (-100V).

*Mode 6:* Voltage source  $V_2$  and switches  $S_2$ ,  $S_1$ ,  $S_5$  are in conduction state hence the path of load current  $I_0$  is through  $V_2$ - $S_2$ -load- $D_1$ - $S_5$ - $V_2$ , the output voltage level is  $(-V_{DC})$ , i.e. (-200V)

*Mode 7:* Voltage source  $V_2$ , capacitor  $C_1$  acts as voltage sources, and bidirectional switch  $S_a$ , switches  $S_2$ ,  $S_5$  are in conduction state hence the path of load current  $I_0$  is through  $V_2$ - $S_2$ -load- $S_a$ - $D_7$ - $C_1$ - $S_5$ - $V_2$ , the output voltage level is  $(-3\ V_{DC}/2)$ , i.e.  $(-300\ V)$ .

*Mode* 8: Voltage source  $V_2$ , capacitors  $C_1$  and  $C_2$  act as voltage sources and, switches  $S_2$ ,  $S_4$ ,  $S_5$  are in conduction state hence the path of load current Io is through  $V_2$ - $S_2$ -load- $S_4$ - $C_2$ - $C_1$ - $S_5$ - $V_2$ , the output voltage level is  $(-2\ V_{DC})$ , i.e.  $(-400\ V)$ .

Mode 0: Switches  $S_2$ ,  $S_6$ ,  $S_4$  are in the conduction state, and the output voltage level is 0 volts during positive zero-crossing and switches  $S_5$ ,  $S_3$ ,  $S_1$  are in the conduction state, and the output voltage level is 0 V during negative zero-crossing, and the expected 9 level waveform of the proposed topology is shown in FIGURE 3.

FIGURE 3. Expected 9 level waveform of the proposed topology proposed.

The operation of the proposed nine-level inverters is easily visualized from the information present in the switching

table. If the switch is in the "1" state at that point, it is viewed as that switch is directing. Likewise, if the switch is in a "0" state at that point, it is viewed as that switch is not directing. TABLE 1 represents the switching states according to which the voltage is produced. The operation of the proposed 9 level inverters is divided into nine modes based on the inverter output. This structure is made of two equal DC sources  $V_1 \& V_2$  owing a magnitude of 200V each and capacitors  $C_1$  and  $C_2$  100 V each. Therefore, 400V is the peak output voltage; hence the inverter is asymmetrical.

**TABLE 1.** Switching states of 9 level inverter.

| Switching<br>Levels | $S_a$ | $S_1$ | S <sub>2</sub> | $S_3$ | $S_4$ | $S_5$ | $S_6$ | Output<br>voltage<br>(V <sub>ab</sub> ) |

|---------------------|-------|-------|----------------|-------|-------|-------|-------|-----------------------------------------|

| L <sub>1</sub>      | 0     | 1     | 0              | 1     | 0     | 0     | 1     | +400                                    |

| $L_2$               | 1     | 0     | 0              | 1     | 0     | 0     | 1     | +300                                    |

| L <sub>3</sub>      | 0     | 0     | 0              | 1     | 1     | 0     | 1     | +200                                    |

| L <sub>4</sub>      | 1     | 0     | 1              | 0     | 0     | 0     | 1     | +100                                    |

| L <sub>5</sub>      | 0     | 0     | 1              | 0     | 1     | 0     | 1     | 0+                                      |

|                     | 0     | 1     | 0              | 1     | 0     | 1     | 0     | 0-                                      |

| $L_6$               | 1     | 0     | 0              | 1     | 0     | 1     | 0     | -100                                    |

| $L_7$               | 0     | 1     | 1              | 0     | 0     | 1     | 0     | -200                                    |

| $L_8$               | 1     | 0     | 1              | 0     | 0     | 1     | 0     | -300                                    |

| L <sub>9</sub>      | 0     | 0     | 1              | 0     | 1     | 1     | 0     | -400                                    |

For the asymmetric source configuration in the proposed topology, the generalized mathematical expressions are let the input DC sources are  $V_{DC1}$  and  $V_{DC2}$ , the voltages across capacitors  $C_1$  and  $C_2$  are  $V_{C1}$  and  $V_{C2}$  which is half of the input DC voltage  $V_{DC2}$ .

$$V_{DC1} = V_{DC2} \tag{1}$$

$$V_{DC2} = V_{C1} + V_{C2} \tag{2}$$

$$V_{C1} = V_{C2} = 0.5V_{DC2} (3)$$

The expressions for the number of DC sources n, number of output levels  $N_{Lev}$ , the required number of power switches  $N_S$ , necessary number of diodes  $N_d$ , number of DC-link capacitors required  $N_{cap}$ , peak voltage (VDC)<sub>max</sub> are

$$n = \frac{(N_{Lev} - 1)}{4} \tag{4}$$

$$N_S = \frac{7(N_{Lev} - 1)}{8} \tag{5}$$

$$N_d = N_{lev} - 1 \tag{6}$$

$$N_{cap} = \frac{(N_{Lev} - 1)}{4} \tag{7}$$

$$(V_{DC})_{\text{max}} = V_{DC} \sum_{k=1}^{n} k = nV_{DC}$$

(8)

In this aspect to generate 9 level output Inverter requires 2 DC sources, 7 power switches IGBTs, 8 diodes, and 2 DC-link capacitors, the magnitude of peak DC voltage is 400 V.

TABLE 2. Operating modes of proposed 17 level inverter.

| Modes   | Path of load current I <sub>0</sub>                                                                                                                             | Output voltage ( $V_{ab}$ ) |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Mode-1  | $V_{2a} - S_{6a} - C_{2a} - C_{1a} - S_{1a} - V_{aa} - Load - V_{bb} - S_{3b} - V_{2b} - S_{6b} - C_{2b} - C_{1b} - S_{1b} - V_{ab} - V_{ba} - S_{3a} - V_{2a}$ | + 400                       |

| Mode-2  | $V_{2a} - S_{6a} - C_{2a} - S_{Aa} - V_{aa} - Load - V_{bb} - S_{3b} - V_{2b} - S_{6b} - C_{2b} - C_{1b} - S_{1b} - V_{ab} - V_{ba} - S_{3a} - V_{2a}$          | + 350                       |

| Mode-3  | $V_{2a} - S_{6a} - D_{4a} - V_{aa} - Load - V_{bb} - S_{3b} - V_{2b} - S_{6b} - C_{2b} - C_{1b} - S_{1b} - V_{ab} - V_{ba} - S_{3a} - V_{2a}$                   | + 300                       |

| Mode-4  | $C_{2a} - S_{Aa} - V_{aa} - Load - V_{bb} - S_{3b} - V_{2b} - S_{6b} - C_{2b} - C_{1b} - S_{1b} - V_{ab} - V_{ba} - D_{2a} - S_{6a} - C_{2a}$                   | + 250                       |

| Mode-5  | $V_{2b} - S_{6b} - C_{2b} - C_{1b} - S_{1b} - V_{ab} - V_{ba} - D_{2a} - S_{6a} - D_{4a} - V_{aa} - Load - V_{bb} - S_{3b} - V_{2b}$                            | + 200                       |

| Mode-6  | $C_{2b} - S_{Ab} - V_{ab} - V_{ba} - D_{2a} - S_{6a} - D_{4a} - V_{aa} - Load - V_{bb} - S_{3b} - V_2 - S_{6b} - C_{2b}$                                        | + 150                       |

| Mode-7  | $V_{2b} - S_{6b} - D_{4b} - V_{ab} - V_{ba} - D_{2a} - S_{6a} - D_{4a} - V_{aa} - Load - V_{bb} - S_{3b} - V_{2b} \\$                                           | + 100                       |

| Mode-8  | $C_{2b} - S_{Ab} - V_{ab} - V_{ba} - D_{2a} - S_{6a} - D_{4a} - V_{aa} - Load - V_{bb} - D_{2b} - S_{6b} - C_{2b}$                                              | + 50                        |

| Mode-9  | $V_{aa}-Load - V_{bb} - D_{2b} - S_{6b} - D_{4b} - V_{ab} - V_{ba} - D_{2a} - S_{6a} - D_{4a} - V_{a1} \\$                                                      | 0                           |

| Mode-10 | $C_{1a} - S_{5a} - D_{3a} - V_{ba} - V_{ab} - S_{4b} - D_{6b} - S_{2b}$ - $V_{bb}$ - Load - $V_{aa} - S_{Aa} - C_{1a}$                                          | - 50                        |

| Mode-11 | $C_{2a} - C_{1a} - S_{5a} - D_{3a} - V_{ba} - V_{ab} - S_{4b} - D_{6b} - S_{2b} - V_{bb} - Load - V_{aa} - S_{4a} - C_{2a}$                                     | - 100                       |

| Mode-12 | $V_{2a} - S_{2a} - V_{ba} - V_{ab} - S_{4b} - D_{6b} - S_{2b} - V_{bb} - Load - V_{aa} - S_{Aa} - C_{1a} - S_{5a} - V_{2a}$                                     | -150                        |

| Mode-13 | $V_{2a} - S_{2a} - V_{ba} - V_{ab} - S_{4b} - D_{6b} - S_{2b} - V_{bb} - Load - V_{aa} - S_{4a} - C_{2a} - C_{1a} - S_{5a} - V_{2a}$                            | -200                        |

| Mode-14 | $V_{2a} - S_{2a} - V_{ba} - V_{ab} - S_{Ab} - C_{2b} - D_{6b} - S_{2b} - V_{bb} - Load - V_{aa} - S_{4a} - C_{2a} - C_{1a} - S_{5a} - V_{2a}$                   | -250                        |

| Mode-15 | $V_{2a} - S_{2a} - V_{ba} - V_{ab} - D_{1b} - C_{1b} - C_{2b} - D_{6b} - S_{2b} - V_{bb} - Load - V_{aa} - S_{4a} - C_{2a} - C_{1a} - S_{5a} - V_{2a}$          | -300                        |

| Mode-16 | $V_{2a} - S_{2a} - V_{ba} - V_{ab} - S_{Ab} - C_{1b} - S_{5b} - V_{2b} - S_{2b} - V_{bb} - Load - V_{aa} - S_{4a} - C_{2a} - C_{1a} - S_{5a} - V_{2a}$          | -350                        |

| Mode-17 | $V_{2a} - S_{2a} - V_{ba} - V_{ab} - S_{4b} - C_{2b} - C_{1b} - S_{5b} - V_{2b} - S_{2b} - V_{bb} - Load - V_{aa} - S_{4a} - C_{2a} - C_{1a} - S_{5a} - V_{2a}$ | -400                        |

**TABLE 3.** Switching states of proposed 17 level inverter.

| Levels          | $S_{Aa}$ | $S_{1a}$ | $S_{2a}$ | $S_{3a}$ | $S_{4a}$ | $S_{5a}$ | $S_{6a}$ | $S_{Ab}$ | $S_{1b}$ | $S_{2b}$ | $S_{3b}$ | $S_{4b}$ | $S_{5b}$ | $S_{6b}$ | Output voltage (V <sub>ab</sub> ) |

|-----------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-----------------------------------|

| L <sub>1</sub>  |          | Y        |          | Y        |          |          | Y        |          | Y        |          | Y        |          |          | Y        | + 400                             |

| L <sub>2</sub>  | Y        |          |          | Y        |          |          | Y        |          | Y        |          | Y        |          |          | Y        | + 350                             |

| L <sub>3</sub>  |          |          |          | Y        | Y        |          | Y        |          | Y        |          | Y        |          |          | Y        | + 300                             |

| L <sub>4</sub>  | Y        |          | Y        |          |          |          | Y        |          | Y        |          | Y        |          |          | Y        | + 250                             |

| $L_5$           |          |          | Y        |          | Y        |          | Y        |          | Y        |          | Y        |          |          | Y        | + 200                             |

| $L_6$           |          |          | Y        |          | Y        |          | Y        | Y        |          |          | Y        |          |          | Y        | + 150                             |

| $L_7$           |          |          | Y        |          | Y        |          | Y        |          |          |          | Y        | Y        |          | Y        | + 100                             |

| L <sub>8</sub>  |          |          | Y        |          | Y        |          | Y        | Y        |          | Y        |          |          |          | Y        | + 50                              |

| L <sub>9</sub>  |          |          | Y        |          | Y        |          | Y        |          |          | Y        |          | Y        |          | Y        | 0                                 |

| L <sub>10</sub> |          | Y        |          | Y        |          | Y        |          |          |          | Y        |          | Y        |          | Y        | - 50                              |

| L11             |          |          |          | Y        | Y        | Y        |          |          |          | Y        |          | Y        |          | Y        | - 100                             |

| L <sub>12</sub> | Y        |          | Y        |          |          | Υ        |          |          |          | Y        |          | Y        |          | Y        | -150                              |

| L <sub>13</sub> |          |          | Y        |          | Y        | Y        |          |          |          | Y        |          | Y        |          | Y        | -200                              |

| L 14            |          |          | Y        |          | Y        | Y        |          | Y        |          | Y        |          |          |          | Υ        | -250                              |

| L <sub>15</sub> |          |          | Y        |          | Y        | Y        |          |          | Y        | Y        |          |          |          | Y        | -300                              |

| L <sub>16</sub> |          |          | Y        |          | Y        | Υ        |          | Y        |          | Y        |          |          | Υ        |          | -350                              |

| L <sub>17</sub> |          |          | Y        |          | Y        | Υ        |          |          |          | Y        |          | Y        | Υ        |          | -400                              |

Y=ON state of the switches

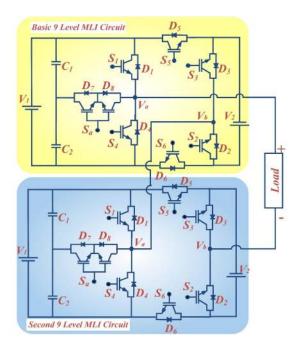

## B. SEVENTEEN LEVEL INVERTER TOPOLOGIES

The proposed 17-level MLI is designed with two developed 9 level units in cascaded without additional circuit components. This topology consists of two unit's 'A' and 'B' having bidirectional and twelve switches with four DC sources and four capacitors as shown in FIGURE 4. The power quality issues like THD, fewer switches, dv/dt stress are minimized with this developed multilevel inverter.

#### 1) OPERATING MODES

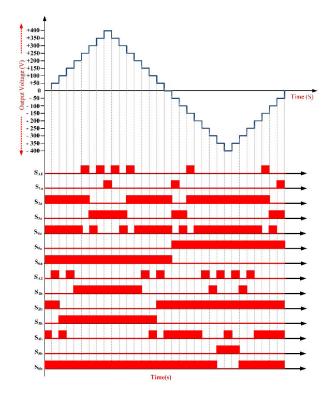

In this portion, the proposed inverter operation is explained through the various modes of output voltage levels produced in a steady-state. Multiple modes of operation are described in TABLE 2, and the expected 17 level waveform of the proposed topology is shown in FIGURE 5. The function of the proposed 17 level inverters is easily visualized from the switching table's information. If the switch is in "Y" state at that point, it is viewed as that switch is directing, otherwise, it is considered as that switch is not directing. TABLE 3 represents switching states according to which the voltage is produced.

#### **III. POWER LOSS CALCULATION**

The crucial power loss of switches in MLIs are conduction and switching losses [19] conduction losses are more effective in low switching frequency, whereas the switching loss

FIGURE 4. Seventeen level cascaded H-Bridge multilevel inverter topology.

FIGURE 5. Expected 17 level waveform of the proposed topology proposed.

is dominating in high switching frequencies. Conduction loss of IGBT with antiparallel diode is for the on-state condition of resistance and voltages of both transistors and diode. Let  $V_S$  is on-state voltage,  $R_S$  is the resistance of the transistor,

and  $V_d$  is on-state voltage,  $R_d$  is the diode's resistance. The conduction losses of diode  $P_{CD}$  and transistor  $P_{CS}$  are determined as follows [21]

$$P_{CD}(t) = V_d i(t) + R_d i^2(t)$$

(9)

$$P_{CS}(t) = V_S i(t) + [R_S i^{\beta}(t)] i(t)$$

(10)

where  $\beta$  is a constant calculated from characteristics of a power switch. Assuming there are  $N_{S,ON}$  switches, and  $N_{d,ON}$  diodes, are conduction at the time of instant 't' then the multilevel average conduction power losses are

$$P_{CU} = \frac{1}{\pi} \int_{0}^{\pi} \left[ N_{S,ON}(t) P_{CS}(t) + N_{d,ON}(t) P_{CD}(t) \right] dt$$

$$P_{CU} = \frac{1}{\pi} \int_{0}^{\pi} \left[ N_{S,ON}(t) \left\{ V_{S}i(t) + R_{S}i^{\beta}(t) \right\} + N_{d,ON}(t) \left\{ V_{d}i(t) + R_{d}i(t) \right\} \right] i(t) dt \quad (11)$$

In the proposed topology there is a bi-directional switch Sa, and it conducts at the time of instant 't' then the average conduction losses are

$$P_{CB} = \frac{1}{\pi} \int_{0}^{\pi} \left[ V_{S}(t) + V_{d}(t) + R_{S}i^{\beta}(t) + R_{d}i(t) \right] i(t)dt \quad (12)$$

Consider the output current is sinusoidal then

$$i(t) = i_m \sin(t) \tag{13}$$

The simplified average conduction losses of a bi-directional switch can be calculated from (12) and (13)

$$P_{CB} = \frac{2}{\pi} i_m \left[ V_S(t) + V_d(t) \right] + \frac{R_d i_m^2}{2} + \frac{R_s i_m^{\beta+1}}{2} \int_0^{\pi} \sin^{\beta+1}(t) dt$$

(14)

Therefore, total conduction losses Pc of the proposed topology is got as

$$P_C = P_{CII} + P_{CR} \tag{15}$$

The switching losses occur, based on the energy losses, especially during on-state and off-state of the switches. For a switching period of a switch, there is a linear variation in voltage and current are related as follows [18]

$$P_{SW,on} = \frac{1}{T} \int_{0}^{t_{ON}} V(t)i(t)dt$$

$$= \frac{1}{T} \int_{0}^{t_{ON}} \left(\frac{V_{SW}}{t_{ON}}t\right) \left(-\frac{I}{t_{ON}}(t-t_{ON})\right)dt$$

$$P_{SW,ON} = \frac{1}{6T} [V_{SW}It_{ON}]$$

$$P_{SW,OFF} = \frac{1}{T} \int_{0}^{t_{OFF}} V(t)i(t)dt$$

(16)

| Components required                       | CHB                    | NPC                    | FC                      | [10]                    | [13]                    | [9]                     | [11]                    | Proposed                 |

|-------------------------------------------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|

| Switches (N <sub>s</sub> )                | $2(N_{Lev}-1)$         | 2(N <sub>Lev</sub> -1) | $2(N_{Lev}-1)$          | $(N_{Lev}+3)$           | $(N_{Lev}+2)$           | $(N_{Lev}+1)$           | $(N_{Lev}-1)$           | $7(N_{Lev}-1)/8$         |

| Diodes (N <sub>d</sub> )                  | 2(N <sub>Lev</sub> -1) | 2(N <sub>Lev</sub> -1) | 2(N <sub>Lev</sub> -1)  | $(N_{Lev}+3)$           | $(N_{Lev}+2)$           | $(N_{Lev}+1)$           | (N <sub>Lev</sub> -1)   | (N <sub>Lev</sub> -1)    |

| Dc link capacitors<br>(N <sub>cap</sub> ) | 0                      | (N <sub>Lev</sub> -1)  | $(N_{Lev}-1)$           | (N <sub>Lev</sub> -1)/4  |

| Dc sources (n)                            | $(N_{Lev}$ -1)/2       | $(N_{Lev}$ -1)/8       | (N <sub>Lev</sub> -1)/8 | $(N_{Lev}$ -1)/8        | $(N_{Lev}$ -1)/8        | (N <sub>Lev</sub> -1)/8 | $(N_{Lev}-1)/4$         | $(N_{Lev}-1)/4$          |

| Driver board circuits (N <sub>dk</sub> )  | 2(N <sub>Lev</sub> -1) | 2(N <sub>Lev</sub> -1) | 2(N <sub>Lev</sub> -1)  | $(N_{Lev}+3)$           | $(N_{Lev}+2)$           | $(N_{Lev}+1)$           | $(N_{Lev}$ -2)          | 7(N <sub>Lev</sub> -1)/8 |

TABLE 4. Variance of variant MLI topologies with regards number of output levels N<sub>Lev.</sub>

**TABLE 5.** Variance of variant 9 level MLI topologies.

| Compo<br>requi      |       | СНВ   | NPC  | FC   | [7]  | [9]  | [10] | [11]  | [12]  | [13]  | [22] | [26] | [28] | Proposed |

|---------------------|-------|-------|------|------|------|------|------|-------|-------|-------|------|------|------|----------|

| N,                  | s     | 16    | 16   | 16   | 12   | 10   | 12   | 8     | 11    | 9     | 8    | 10   | 10   | 7        |

| No                  | d     | 16    | 16   | 16   | 12   | 10   | 12   | 8     | 11    | 11    | 8    | 10   | 10   | 8        |

| N <sub>C</sub>      | ар    | 0     | 8    | 8    | 4    | 2    | 2    | 2     | 2     | 0     | 2    | 0    | 2    | 2        |

| n                   |       | 4     | 1    | 1    | 2    | 1    | 1    | 2     | 1     | 4     | 1    | 4    | 1    | 2        |

| N <sub>d</sub>      | k     | 16    | 16   | 16   | 12   | 10   | 12   | 7     | 11    | 9     | 8    | 10   | 10   | 7        |

| Fc                  | С     | 5.77  | 6.33 | 6.33 | 4.22 | 3.66 | 4.33 | 3     | 4     | 3.66  | 3.11 | 3.77 | 3.66 | 2.88     |

| TS                  | V     | 16    | 16   | 16   | 1    | -    | -    | 9     | 11    | 11    | 10   | 16   | 24   | 5        |

| TH                  | D     | -     | -    | -    | -    | 19.4 | -    | 9.30  | -     | -     | -    | 8.0  | -    | 8.7      |

| CF/N <sub>Lev</sub> | α=0.5 | 6.666 | 7.22 | 7.22 | 5.27 | -    | -    | 3.5   | 4.611 | 4.278 | 3.55 | 4.66 | 5    | 3.166    |

| OI /IVLev           | α=1.5 | 8.44  | 9    | 9    | 6.5  | -    | -    | 4.833 | 5.833 | 5.5   | 4.66 | 6.44 | 7.66 | 3.722    |

$$= \frac{1}{T} \int_{0}^{t_{OFF}} \left(\frac{V_{SW}}{t_{OFF}}t\right) \left(-\frac{I}{t_{OFF}}(t - t_{OFF})\right) dt$$

$$P_{SW,OFF} = \frac{1}{6T} \left[V_{SW}I_{t_{OFF}}\right]$$

(17)

where T is a total period and  $P_{(SW,ON)}$ ,  $P_{(SW,OFF)}$  are onstate, and off-state switching losses of the switch,  $t_{ON}$ ,  $t_{OFF}$  are the ON-state and OFF-state periods of the switch respectively and  $V_{SW}$  is the peak voltage of the switch. Hence, total-switching losses  $P_{SW}$  of multilevel inverter is expressed as

$$P_{SW} = P_{SW ON} + P_{SW OFF}$$

(18)

Thus, the total power losses  $P_L$  of a multilevel inverter is the sum of conduction and switching losses; it can be expressed as

$$P_{L} = P_{C} + P_{SW} \tag{19}$$

Further, the efficiency  $\eta$  of the proposed MLI can be calculated as

$$\eta = \frac{P_{out}}{P_{in}} = \frac{P_{out}}{P_{out} + P_L} \tag{20}$$

The output power can be got as follows;

$$P_{out} = V_{rms} \times I_{rms} \tag{21}$$

## **IV. COMPARISON STUDY**

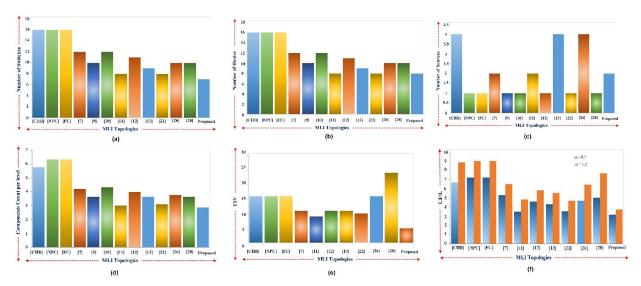

The asymmetrical configuration of the presented inverter topology is compared with the asymmetrical structure of Cascaded H-bridge (CHB) multilevel inverter, Neutral point clamped (NPC) multilevel inverter, flying capacitors (FC) multilevel inverter, and some other similar multilevel inverter topologies. The number of various components required regarding output voltage levels for correspondent topologies considered is calculated from the equations in TABLE 4 and tabulated in TABLE 5, and the components count per level factor F<sub>CCL</sub> is calculated from (22).

$$F_{CCL} = \frac{N_S + N_d + N_{cap} + N_{dk} + n}{N_{Lev}}$$

(22)

The total standing voltage (TSV) is an essential factor for the selection of switches. TSV is the addition of the maximum blocking voltage across each semiconductor device.

The voltage stress of the switches in different units is given as:

$$V_{Sbi} = V_i$$

$i = 1, 2, \dots, n$

$V_{Suni} = 2V_i$   $i = 1, 2, \dots, n$

where n is the number of complimentary switches.

The voltage stress across each unilateral (uni) and bilateral (bi) switch can be calculated based on the circuitry.

Therefore, the generalized relation for the TSV calculation is

$$TSV = 2[VS1 + VS3 + VS5 + \dots VS(2n+1)]$$

(23)

TABLE 6. Variance of variant 17 level MLI topologies.

| Components re       | equired | СНВ  | NPC  | FC   | [3]  | [9]  | [10] | [11] | [13] | [23] | [26] | [29] | Proposed |

|---------------------|---------|------|------|------|------|------|------|------|------|------|------|------|----------|

| N <sub>s</sub>      |         | 32   | 32   | 32   | 10   | 20   | 24   | 16   | 14   | 10   | 20   | 10   | 14       |

| $N_d$               |         | 32   | 32   | 32   | 10   | 20   | 24   | 16   | 20   | 10   | 20   | 12   | 16       |

| N <sub>cap</sub>    |         | 0    | 16   | 16   | 4    | 4    | 4    | 4    | 4    | 0    | 0    | 0    | 4        |

| n                   |         | 8    | 2    | 2    | 2    | 2    | 2    | 4    | 8    | 4    | 8    | 2    | 4        |

| N <sub>dk</sub>     |         | 32   | 32   | 32   | 20   | 20   | 24   | 14   | 14   | 10   | 20   | 10   | 14       |

| Fcc                 |         | 6.11 | 6.70 | 6.70 | 3.88 | 3.88 | 4.48 | 3.17 | 3.52 | 2    | 4    | 2    | 3.05     |

| TSV                 |         | 32   | 32   | 32   | -    | -    | -    | 11   | 22   | 36   | 36   | 40   | 11       |

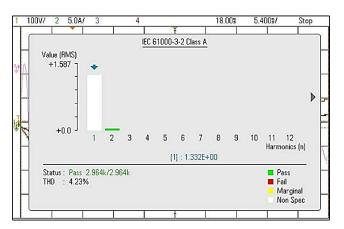

| THD                 |         | -    | -    | -    | -    | -    | -    | -    | -    | 7.1  | 3.7  | -    | 4.23     |

| CF/N <sub>Lev</sub> | α=0.5   | 7.05 | 7.64 | 7.64 | -    | -    | -    | 3.5  | 4.17 | 4.94 | 5.05 | 5.18 | 3.38     |

| OT /TVLev           | α=1.5   | 8.94 | 9.52 | 9.52 | -    | -    | -    | 4.14 | 5.47 | 9.18 | 7.17 | 9.88 | 4.02     |

FIGURE 6. Comparison of proposed 9 level inverter topology with other topologies (a) Number of switches (b) Number of diodes (c) Number of sources (d) Components count per level (e) Total standing voltage (f) Cost factor per level.

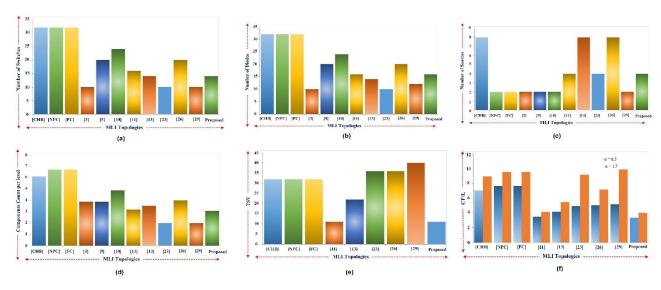

From TABLE 5 and TABLE 6, the number of power switches needed to produce nine-level and seventeen level staircase outputs for designed topology is less than considered with other topologies. Hence, required gate driver circuits for the switches are reduced, reducing the inverter's ambiguousness. Considering that the components count per level factor F<sub>CCL</sub> value is more, hence the topology requires more components to build the desired voltage level. In the recent investigations, the primary objective is to decrease components count per level factor in the design of multilevel inverter. It is noticed that the proposed inverter is having fewer components count per level factor F<sub>CCL</sub> as related to the other nine-level multilevel inverter topologies. The introduced topology uses fewer switches compared to similar topologies. FIGURE 6 presents the comparison of the proposed nine-level inverter with similar topologies. The minimization of switches reduces the requirement of gate driver circuits for switches and limits components count per level factor FCCL hence reducing the inverter's complexity and the cost factor. FIGURE 7 represents the comparison result of the proposed seventeen level

MLI with other topologies. From FIGURE 7, the proposed topology uses fewer components count per level factor  $F_{CCL}$ ; hence the cost factor reduces and the cost factor (CF) is calculated by using the below equation

$$CF = (n + N_s + N_d + N_{dk} + N_{cap} + \alpha TSV)$$

(24)

where  $\alpha$  is a current coefficient factor

# **V. SIMULATION AND EXPERIMENTAL RESULTS**

#### A. SIMULATION RESULTS

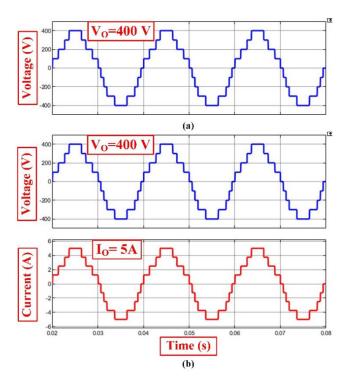

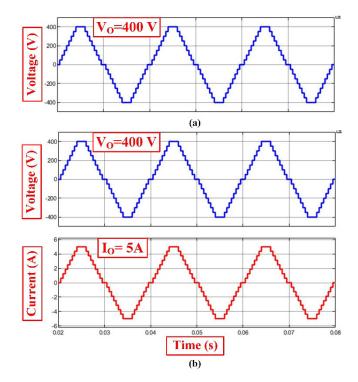

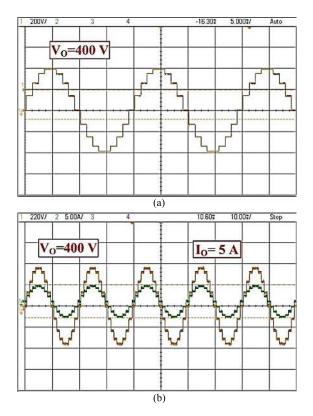

MATLAB/Simulink carries out the validation and practicability of the presented inverter. TABLE 7 describes various MLI parameters used for analysis. In the simulation pulses are actualized at 10 kHz carrier frequency, the design is tested for  $80\Omega$  resistive load and an inductive load of 98mH having  $50\Omega$  internal resistance. FIGURE 8(a) shows the Simulation results of output Voltage, FIGURE 8(b) shows the Simulation results of output Voltage and Current waveforms for proposed 9 level Inverter topologies. In asymmetric source configuration the magnitude of source voltages  $V_{dc1},\,V_{dc2}$  considers

FIGURE 7. Comparison of proposed 17 level inverter topologies with other topologies (a) Number of switches (b) Number of diodes (c) Number of sources (d) Components count per level (e) Total standing voltage (f) Cost factor per level.

FIGURE 8. (a) Simulation result of voltage (b) Simulation result of voltage and current for proposed 9 level inverter topologies.

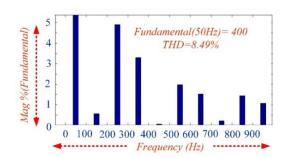

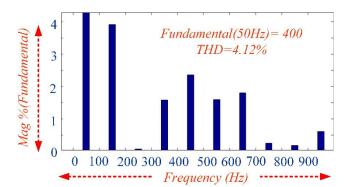

as 200V each, the capacitor ratings ( $C_1=C_2$ ) are 4700  $\mu F$  with 80 V. The inverter allows to deliver nine-level output with a maximum voltage of 400V and load current of 5A. The output waveform is enhanced with THD of 8.49% shown in FIGURE 9 and FIGURE 10(a) shows the Simulation results of output Voltage, FIGURE 10(b) shows the Simulation results of output Voltage and Current waveforms for proposed seventeen level Inverter topologies. In asymmetric source configuration the magnitude of source voltages  $V_{adc1}$ ,

FIGURE 9. Simulation result of voltage harmonic spectrum for the proposed 9 level inverter topology.

$V_{adc2}$  and  $V_{bdc1}$ ,  $V_{bdc2}$  consider as 100V each, the capacitor ratings ( $C_{a1}=C_{a2}=C_{b1}=C_{b2}$ ) are 4700  $\mu F$  with 80 V, and the inverter allows to deliver seventeen level output with a maximum voltage of 400V and load current of 5A, the output waveform is enhanced with THD of 4.12% shown in FIGURE 11.

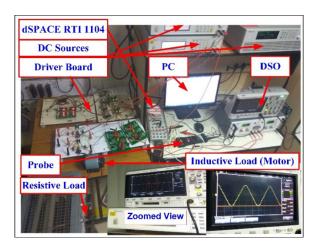

# B. EXPERIMENTAL RESULTS

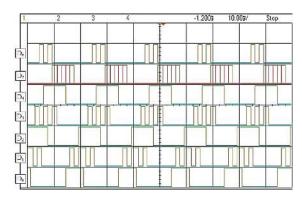

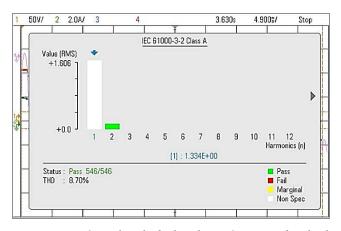

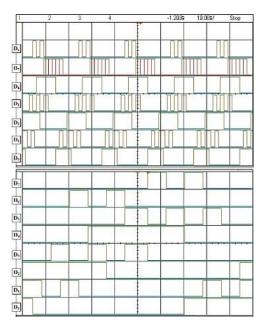

To justifying the presented inverter topology, for asymmetrical configuration, an experimental setup is accomplished in a laboratory as depicted in FIGURE 12. The inverter setup comprises seven IGBT's CM75DU-12H incited by MCT2E optocouplers, dual DC supplies with the same magnitude of 200V, and a resistive load of  $80\Omega$ , an inductive load of 98mH with  $50\Omega$  internal resistance, and dSPACE1104 is used for generating switching pulse. The waveforms of experimental gate pulses, current, and voltage are observed on the digital storage oscilloscope (DSO) shown in FIGURE 13 and FIGURE 14(a)&(b) respectively. Using a power analyzer, voltage harmonic is measured, and the voltage THD spectrum is illustrated in FIGURE 15 and the voltage THD of the proposed modulation technique is 9.85%.

| TARIF 7 | Various system | narameters for | nronosed | tonology |

|---------|----------------|----------------|----------|----------|

|         |                |                |          |          |

| Parameter            | Simu           | ulation            | Experimental          |                 |  |  |

|----------------------|----------------|--------------------|-----------------------|-----------------|--|--|

| Faranielei           | 9 – Level      | 17 - Level         | 9 – Level             | 17 – Level      |  |  |

| Voltage Source       | 200V           | 100 V              | 200V                  | 100 V           |  |  |

| Capacitor ratings    | 80V, 4700μF    | 80V, 4700μF        | 80V, 4700μF           | 80V, 4700μF     |  |  |

| Load Resistance      | 80Ω            | 80Ω                | 80Ω                   | 80Ω             |  |  |

| Inductive load       | 98mH           | 98mH               | 98mH                  | 98mH            |  |  |

| Motor load           | 230V, 0.5HP    | 230V, 0.5HP        | 230V, 0.5HP           | 230V, 0.5HP     |  |  |

| Output Voltage (Vo)  | Vrms = 282.84V | Vrms = 282.84 V    | <i>Vrms = 282.84V</i> | Vrms = 282.84 V |  |  |

| Output Current (Io)  | Irms=3.53A     | <i>Irms=3.53 A</i> | Irms=3.53A            | Irms=3.53 A     |  |  |

| Carrier Frequency    | 10 KHz         | 10 KHz             | 10 KHz                | 10 KHz          |  |  |

| Modulation Frequency | 50Hz           | 50Hz               | 50Hz                  | 50Hz            |  |  |

FIGURE 10. (a) Simulation result of voltage (b) Simulation result of voltage and current for proposed 17 level inverter topologies with asymmetric source configuration.

FIGURE 11. Simulation result of voltage harmonic spectrum for the proposed 17 level inverter topology.

Ruderman *et al.* [20] proposed the mathematical formulae for theoretical calculations of voltage THD, the derived value

FIGURE 12. Experimental setup for the proposed topology.

FIGURE 13. Experimental gate pulses of 9MLI.

of% THD is expressed as

$$%THD = 1/(\sqrt{3(N_{Lev} - 1)m_i})$$

(25)

where  $N_{Lev}$  is the output level and  $m_i$  is the modulation index. For  $m_i=0.9$  and  $N_{Lev}=9$ , voltage THD's theoretical value is 8.01% very near to simulation and experimental THD presented in TABLE 8.

From the experimental setup,  $V_{rms}$  is 282.84V &  $I_{rms}$  is 3.53A from (21) the output power is 998.425 W. The parameter values are taken from the IGBT CM75DU-12H,  $R_s$  is 0.4-ohm, turn-on delay time as 100 ns, turn-on rising time is 250 ns, turn off delay time is 200 ns and turn off fall time

FIGURE 14. (a) Experimental result of output Voltage (b) Experimental result of output voltage and Current for 9 level inverter topologies with asymmetric source configuration.

FIGURE 15. Experimental result of voltage harmonic spectrum for 9 level inverter topology.

**TABLE 8.** Voltage THD for 9 levels and 17 levels.

|             | Voltage % THD (Mi=0.9) |              |  |  |  |  |  |  |  |

|-------------|------------------------|--------------|--|--|--|--|--|--|--|

| 9 level     |                        |              |  |  |  |  |  |  |  |

| Theoretical | Simulation             | Experimental |  |  |  |  |  |  |  |

| 8.01        | 8.49                   | 8.70         |  |  |  |  |  |  |  |

|             | 17 level               |              |  |  |  |  |  |  |  |

| Theoretical | Simulation             | Experimental |  |  |  |  |  |  |  |

| 4           | 4.12                   | 4.23         |  |  |  |  |  |  |  |

as 300 ns,  $V_{SW}$  is 0.6V taken from performance characteristics. In the proposed inverter design, there are 17 steps

FIGURE 16. Experimental gate pulses of 17 MLI.

in one full cycle for 7 switches. From (10), the conduction losses are 49.71W and  $P_{sw,on}, P_{sw, off}$  is calculated from (16), (17) and the values are 0.0415W, and 0.0594W, respectively. From (18) switching losses are the sum of  $P_{sw,on}$ , and  $P_{sw, off}$ . Hence the switching losses are  $0.0415 + 0.0594 = 0.1009 \, W$ . Therefore, the total losses are calculated during the conduction time and switching time by using (19) is 49.81W, finally from (20) efficiency  $\eta$  is 95.27% is nearly 2% more than compared to [9] and 15% compared to [10].

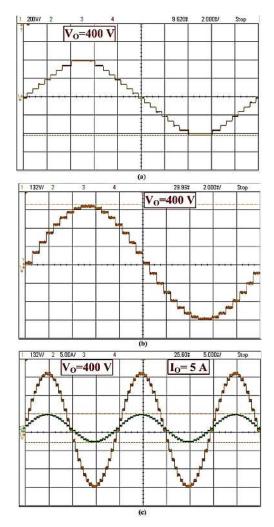

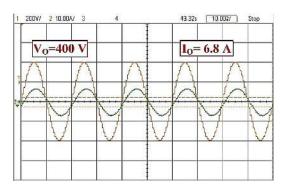

The proposed seventeen levels cascaded Inverter setup comprises fourteen IGBT's CM75DU-12H, incited by MCT2E optocouplers, four DC supplies with the same magnitude of 100V, a resistive load of  $80\Omega$ , an inductive load of 98mH with  $50\Omega$  internal resistance, and dSPACE1104 is used for generating switching pulse. The waveforms of gate pulse, current, and voltage are observed on the digital storage oscilloscope (DSO) shown in FIGURE 16, and FIGURE 17(a), (b) & (c) respectively. Using a power analyzer voltage harmonic is measured, and the voltage THD spectrum is illustrated in FIGURE 18 and the voltage THD of the proposed modulation technique is 4.23%. The output waveform of voltage and current for nonlinear loads is shown in FIGURE 19.

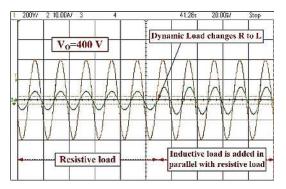

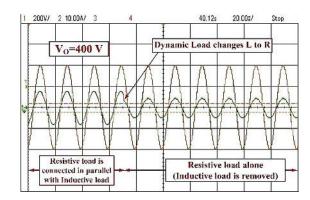

The dynamic responses of voltage and current when the load changes from resistance to inductance by adding an inductive load of 98mH having  $50\Omega$  internal resistance in parallel with  $80\Omega$  resistance is clearly shown in FIGURE 20, and The dynamic responses of voltage and current when the load changes from inductive load to inductive resistance load by adding a resistance load of  $80\Omega$  in parallel with an inductive load of 98mH having  $50\Omega$  internal resistance is clearly shown in FIGURE 21. The experimental Vrms is 282.8 V & I<sub>rms</sub> is 3.53 A form (21) the output power is 998.284 W.

FIGURE 17. (a) & (b) Experimental result of output voltage (c) Experimental result of output voltage and current for 17 level inverter topology with R load.

FIGURE 18. Experimental result of voltage harmonic spectrum for 17 level inverter topologies.

The parameter values are taken from the IGBT CM75DU-12H,  $R_s$  is 0.4 ohm, turn-on delay time as 100 ns, turn-on rising time is 250 ns, turn off delay time is 200 ns

FIGURE 19. Experimental result of voltage and current waveform for 17 level inverter topology with motor load.

FIGURE 20. Experimental result of voltage and current waveforms for 17 level inverter topology with RL load.

FIGURE 21. Experimental result of voltage and current waveforms for 17 level inverter topology with LR load.

and turn off fall time as 300 ns,  $V_{sw}$  is 0.6V taken from performance characteristics. In the proposed inverter design there are 33 steps in one full cycle for 14 switches. From (10), the conduction losses are 99.432 W and  $P_{sw, on}$ ,  $P_{sw, off}$  is calculated from (16), (17) and the values are 0.276W and 0.394 W respectively, from (18) switching losses are the sum of  $P_{sw, on}$ , and  $P_{sw, off}$ . Hence the switching losses are 0.276+ 0.394 = 0.67 W; therefore, the total losses are calculated during the conduction time, and the switching time by using (19) is 100.102 W, finally from (20) efficiency  $\eta$  is 90.87%. TABLE 9 represents the proposed MLI's efficiency with resistive load and with dynamic load for seventeen levels.

FIGURE 22. Comparison of efficiency to the proposed inverter with other topologies (a) 9 Levels (b) 17 Levels.

TABLE 9. Power and efficiency of proposed nine and 17 level MLI.

| Parameters            | 9 level | 17 Level<br>with R load | 17 Level with<br>RL load |

|-----------------------|---------|-------------------------|--------------------------|

| Vrms (v)              | 282.84  | 282.84                  | 282.84                   |

| Irms (A)              | 3.53    | 3.53                    | 4.80                     |

| Conduction losses (W) | 49.71   | 99.462                  | 135.204                  |

| Switching losses (W)  | 0.1009  | 0.67                    | 0.911                    |

| Total losses (W)      | 49.81   | 101.102                 | 136.1                    |

| Output power (W)      | 998.42  | 998.42                  | 1330.08                  |

| Efficiency (%)        | 95.27   | 90.87                   | 90.67                    |

TABLE 10. Cost of the proposed 17 level MLI.

| Components                | Rating         | Unit<br>price *(\$) | Number of units | Total<br>cost *(\$) |

|---------------------------|----------------|---------------------|-----------------|---------------------|

| IGBT<br>CM75DU-12H        | 1200 V,<br>75A | 33.48               | 14              | 468.72              |

| MCT2E<br>optocouplers     | -              | 0.354               | 16              | 4.602               |

| Capacitor<br>B41231A9128M | 1.2 mF         | 1.51                | 2               | 3.02                |

|                           | Overall co:    | st *(\$)            |                 | 476.342             |

Courtesy: www.yaspro.com, www.nevonexpress.com, in.element14.com, \*prices are subject to change

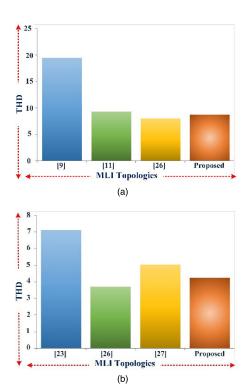

FIGURE 22 (a) & (b) shows the comparison of efficiency between the proposed inverter topology with other inverter topologies. The comparison of THD of proposed topology to the various nine-level and seventeen level inverter topologies

FIGURE 23. Comparison of THD (a) Proposed 9MLI with other topologies and (b) Proposed 17MLI and other similar topologies.

are shown in FIGURE 23(a) & (b). The proposed inverter is stable during nonlinear loads, and it is well suited for FACTS and renewable energy grid-connected applications. The proposed 17 level MLI analysis cost is carried out In TABLE 10. It requires fourteen IGBT's CM75DU-12H, which are incited by MCT2E opto-couplers and two capacitors.

#### VI. CONCLUSION

In this article, a hybrid Cascaded H-Bridge Multilevel Inverter with reduced components topology was presented. The proposed basic MLI builds a voltage with nine levels and extended to seventeen levels by cascading. This topology uses lesser power switches that reduce the price and volume of the inverter and improves efficiency. The proposed inverter requires relatively less power electronic components to generate the desired output than other similar topologies. Comparative analysis shows that the proposed topology has a superior cost factor per level. In the output, the proposed inverter's harmonic content is comparatively less than similar Cascaded H-Bridge MLI for both linear and nonlinear loads with nearly more efficiency  $\eta$ . The proposed inverter is stable during nonlinear loads, and it is well suited for FACTS and renewable energy grid-connected applications. To authenticate the proposed inverter satisfactory simulation is done in MATLAB/Simulink. The experimental setup is assembled in the laboratory confirmations unique with more significant output voltage levels, having lower harmonic content and reduced power switches, and greater efficiency. Subsequently

proposed inverter appears some encouraging properties when compared with various similar topologies.

#### **REFERENCES**

- P. Omer, J. Kumar, and B. S. Surjan, "A review on reduced switch count multilevel inverter topologies," *IEEE Access*, vol. 8, pp. 22281–22302, 2020.

- [2] C. Dhanamjayulu, S. R. Khasim, S. Padmanaban, G. Arunkumar, J. B. Holm-Nielsen, and F. Blaabjerg, "Design and implementation of multilevel inverters for fuel cell energy conversion system," *IEEE Access*, vol. 8, pp. 183690–183707, 2020, doi: 10.1109/ACCESS.2020.3029153.

- [3] C. Dhanamjayulu and S. Meikandasivam, "Implementation and comparison of symmetric and asymmetric multilevel inverters for dynamic loads," *IEEE Access*, vol. 6, pp. 738–746, 2018.

- [4] C. Dhanamjayulu and S. Meikandasivam, "Performance verification of symmetric hybridized cascaded multilevel inverter with reduced number of switches," in *Proc. Innov. Power Adv. Comput. Technol. (i-PACT)*, Vellore, India, Apr. 2017, pp. 1–5.

- [5] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, and M. A. Memon, "A new multilevel inverter topology with reduce switch count," *IEEE Access*, vol. 7, pp. 58584–58594, 2019.

- [6] M. Khenar, A. Taghvaie, J. Adabi, and M. Rezanejad, "Multi-level inverter with combined T-type and cross-connected modules," *IET Power Elec*tron., vol. 11, no. 8, pp. 1407–1415, 2018.

- [7] S. S. Lee, C. S. Lim, and K.-B. Lee, "Novel active-neutral-point-clamped inverters with improved voltage-boosting capability," *IEEE Trans. Power Electron.*, vol. 35, no. 6, pp. 5978–5986, Jun. 2020.

- [8] A. P. Patel, V. J. Rupapara, and A. R. Gauswami, "Design and simulation of 9-level hybrid cascaded H-bridge multilevel inverter with reduced components," in *Proc. Int. Conf. Current Trends Towards Converging Technol.* (ICCTCT), Coimbatore, India, Mar. 2018, pp. 1–7.

- [9] A. Tirupathi, K. Annamalai, and V. Tirumala, "A new hybrid flying capacitor-based single-phase nine-level inverter," *Int. Trans. Elect. Energy* Syst., vol. 29, no. 12, 2019, Art. no. e12139.

- [10] S. S. Lee, "Single-stage switched-capacitor module (S<sup>3</sup>CM) topology for cascaded multilevel inverter," *IEEE Trans. Power Electron.*, vol. 33, no. 10, pp. 8204–8207. Oct. 2018.

- [11] P. Bhatnagar, R. Agrawal, and K. K. Gupta, "Reduced device count version of single-stage switched-capacitor module for cascaded multilevel inverters," *IET Power Electron.*, vol. 12, no. 5, pp. 1079–1086, May 2019.

- [12] J. S. M. Ali and V. Krishnasamy, "Compact switched capacitor multilevel inverter (CSCMLI) with self-voltage balancing and boosting ability," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4009–4013, May 2019.

- [13] E. Samadaei, A. Sheikholeslami, S. A. Gholamian, and J. Adabi, "A square T-type (ST-Type) module for asymmetrical multilevel inverters," *IEEE Trans. Power Electron.*, vol. 33, no. 2, pp. 987–996, Feb. 2018.

- [14] E. Samadaei, M. Kaviani, and K. Bertilsson, "A 13-levels module (K-type) with two DC sources for multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 66, no. 7, pp. 5186–5196, Jul. 2019.

- [15] A. Khodaparast, J. Adabi, and M. Rezanejad, "A step-up switched-capacitor multilevel inverter based on 5-level T-type modules," *IET Power Electron.*, vol. 12, no. 3, pp. 483–491, Mar. 2019.

- [16] J. S. M. Ali, D. J. Almakhles, S. A. A. Ibrahim, S. Alyami, S. Selvam, and M. S. Bhaskar, "A generalized multilevel inverter topology with reduction of total standing voltage," *IEEE Access*, vol. 8, pp. 168941–168950, 2020.

- [17] M. D. Siddique, S. Mekhilef, M. Rawa, A. Wahyudie, B. Chokaev, and I. Salamov, "Extended multilevel inverter topology with reduced switch count and voltage stress," *IEEE Access*, vol. 8, pp. 201835–201846, 2020.

- [18] M. H. Mondol, M. R. Tur, S. P. Biswas, M. K. Hosain, S. Shuvo, and E. Hossain, "Compact three phase multilevel inverter for low and medium power photovoltaic systems," *IEEE Access*, vol. 8, pp. 60824–60837, 2020.

- [19] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 655–667, Feb. 2012.

- [20] A. Ruderman, G. Mehlmann, and B. Reznikov, "PWM voltage quality bounds of a single-phase multilevel converter," in *Proc. 13th Int. Conf. Optim. Electr. Electron. Equip. (OPTIM)*, Brasov, Romania, 2012, pp. 783–789.

- [21] E. Babaei, S. Alilu, and S. Laali, "A new general topology for cascaded multilevel inverters with reduced number of components based on developed H-Bridge," *IEEE Trans. Ind. Electron.*, vol. 61, no. 8, pp. 3932–3939, Aug. 2014.

- [22] B. S. Naik, Y. Suresh, J. Venkataramanaiah, and A. K. Panda, "A hybrid nine-level inverter topology with boosting capability and reduced component count," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 1, pp. 316–320, Jan. 2021.

- [23] J. S. M. Ali, R. S. Alishah, N. Sandeep, S. H. Hosseini, E. Babaei, K. Vijayakumar, and U. R. Yaragatti, "A new generalized multilevel converter topology based on cascaded connection of basic units," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 4, pp. 2498–2512, Dec. 2019.

- [24] K. P. Panda, P. R. Bana, and G. Panda, "A reduced device count single DC hybrid switched-capacitor self-balanced inverter," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, early access, Aug. 20, 2020, doi: 10.1109/TCSII.2020.3018333.

- [25] M. A. Hosseinzadeh, M. Sarebanzadeh, M. Rivera, E. Babaei, and P. Wheeler, "A reduced single-phase switched-diode cascaded multilevel inverter," *IEEE J. Emerg. Sel. Topics Power Electron.*, early access, Jul. 21, 2020, doi: 10.1109/JESTPE.2020.3010793.

- [26] M. N. Hamidi, D. Ishak, M. A. A. M. Zainuri, and C. A. Ooi, "Multilevel inverter with improved basic unit structure for symmetric and asymmetric source configuration," *IET Power Electron.*, vol. 13, no. 7, pp. 1445–1455, May 2020.

- [27] A. Taheri and H. Samsami, "New topology of a switched-capacitor-based multilevel inverter with a single DC power supply," *IET Power Electron.*, vol. 12, no. 6, pp. 1571–1584, May 2019.

- [28] R. Barzegarkhoo, M. Moradzadeh, E. Zamiri, H. M. Kojabadi, and F. Blaabjerg, "A new boost switched-capacitor multilevel converter with reduced circuit devices," *IEEE Trans. Power Electron.*, vol. 33, no. 8, pp. 6738–6754, Aug. 2018.

- [29] R. S. Alishah, S. H. Hosseini, E. Babaei, M. Sabahi, and G. B. Gharehpetian, "New high step-up multilevel converter topology with self-voltage balancing ability and its optimization analysis," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7060–7070, Sep. 2017.

**C. DHANAMJAYULU** (Member, IEEE) received the B.Tech. degree in electronics and communication engineering from JNTU University, Hyderabad, India, the M.Tech. degree in control and instrumentation systems from IIT Madras, Chennai, India, and the Ph.D. degree in power electronics from the Vellore Institute of Technology, Vellore, India. He is currently a Postdoctoral Researcher with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark.

He is also a Faculty Member and a member with the Control and Automation Department, School of Electrical Engineering, Vellore Institute of Technology. He is also a Senior Assistant Professor with the School of Electrical Engineering, Vellore Institute of Technology. Since 2010, he has been a Senior Assistant Professor with the Vellore Institute of Technology. He was invited as a Visiting Researcher with the Department of Energy Technology, Aalborg University, Esbjerg, funded by the Danida Mobility Grant, Ministry of Foreign Affairs of Denmark on Denmark's International Development Cooperation. His research interests include multilevel inverters, power converters, active power filters, power quality, grid-connected systems, smart grid, electric vehicle, electric spring, and tuning of memory elements and controller parameters using soft-switching techniques for power converters, average modeling, steady-state modeling, and small-signal modeling stability analysis of the converters and inverters.

**DEVALRAJU PRASAD** received the B.Tech. degree in electrical engineering and the M.Tech. degree from JNTUA, India, in 2009 and 2015, respectively. He is currently pursuing the Ph.D. degree in power electronics with VIT, India. His research interests include multilevel inverters, power converters, and active power filters and power quality.

**SANJEEVIKUMAR PADMANABAN** (Senior Member, IEEE) received the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012.

He was an Associate Professor with VIT University, from 2012 to 2013. In 2013, he joined the National Institute of Technology, India, as a Faculty Member. In 2014, he was invited as a Visiting Researcher with the Department of Electrical Engineering, Qatar University, Doha, Qatar,

funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Dublin, Ireland, in 2014. He has served as an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, Johannesburg, South Africa, from 2016 to 2018. Since 2018, he has been a Faculty Member with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. He has authored more than 300 scientific articles. He is a Fellow of the Institution of Engineers, India, and the Institution of Engineering and Technology, U.K. He was a recipient of the Best Paper Cum Most Excellence Research Paper Award from IET-SEISCON 2013, IET-CEAT 2016, IEEE-EECSI 2019, and IEEE-CENCON 2019, and five best paper awards from ETAEERE 2016 sponsored Lecture Notes in Electrical Engineering, Springer book. He is an Editor/Associate Editor/Editorial Board of refereed journals, in particular the IEEE Systems JOURNAL, IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, IEEE ACCESS, IET Power Electronics, IET Electronics Letters, and International Transactions on Electrical Energy Systems (Wiley), a Subject Editorial Board Member of Energy Sources-Energies journal (MDPI), and the Subject Editor of the IET Renewable Power Generation, IET Generation, Transmission and Distribution, and FACTS journal, Canada.

PANDAV KIRAN MAROTI (Member, IEEE) received the bachelor's degree in electronics and telecommunication from Dr. Babasaheb Ambedkar Marathwada University, Aurangabad, India, in 2011, and the Master of Technology degree (Hons.) in power electronics and drives from the Vellore Institute of Technology, Vellore, India, in 2014. He is currently pursuing the Ph.D. degree in power electronics with the University of Johannesburg, South Africa. He was as Assistant

Professor with the Marathwada Institute of Technology, Aurangabad, from 2014 to 2016. He is currently a Visiting Researcher with Qatar University. He has published scientific papers in *Power Electronics* (Multilevel dc/dc and dc/ac converter, multiphase open winding inverter). He is an active professional member of IEEE, Industrial Electronics, Power Electronics, Industrial Application, and Young Professionals societies. He is also an active Reviewer Member of various reputed international conferences and journals, including IEEE and IET. He received the Global Experience Scholarship (GES). He also received the Best Paper Award from ETAEERE in 2016 sponsored Lecture Notes in Electrical Engineering Springer Book Series.

JENS BO HOLM-NIELSEN (Senior Member, IEEE) currently works with the Department of Energy Technology, Aalborg University, and the Head of the Esbjerg Energy Section. His research activities established at the Center for Bioenergy and Green Engineering in 2009 and served as the Research Group's Head. He has vast experience in Biorefinery concepts and Biogas production—Anaerobic Digestion, and implementation projects of bio-energy systems in Denmark

with provinces and European states. He has served as the Technical Advisory for many industries in this field. He has executed many large-scale European Union and United Nations projects in research aspects of bioenergy, biorefinery processes, the full chain of biogas, and green engineering. He has authored more than 300 scientific articles. He was a member of the invitation with various capacities in the committee for more than 500 various international conferences and an Organizer of international conferences, workshops, and training programs in Europe, Central Asia, and China. His research interests include renewable energy, sustainability, and Green jobs for all.

**FREDE BLAABJERG** (Fellow, IEEE) received the Ph.D. degree in electrical engineering from Aalborg University, in 1995.

He was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. In 2017, he became a Villum Investigator. He is a Honoris Causa at the University Politehnica Timisoara (UPT), Romania, and Tallinn Technical

University (TTU) in Estonia. His current research interests include power electronics and its applications, such as in wind turbines, PV systems, reliability, harmonics, and adjustable speed drives. He has published more than 600 journal articles in the fields of power electronics and its applications. He is a coauthor of four monographs and editor of ten books in power electronics and its applications.

Dr. Blaabjerg has received 32 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award in 2014, the Villum Kann Rasmussen Research Award in 2014, the Global Energy Prize in 2019, and the 2020 IEEE Edison Medal. He was the Editor-in-Chief of the IEEE Transactions on Power Electronics from 2006 to 2012. He has been a Distinguished Lecturer of the IEEE Power Electronics Society from 2005 to 2007 and the IEEE Industry Applications Society from 2010 to 2011 and 2017 to 2018. From 2019 to 2020, he serves as the President of the IEEE Power Electronics Society. He is also the Vice-President of the Danish Academy of Technical Sciences. He is nominated in 2014–2019 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world. In 2017, he became Honoris Causa at UPT.