# Design and Verification of Reversible Logic Gates using Quantum Dot Cellular Automata

Shaik Shabeena Department of E.C.E Lovely Professional University Jalandhar, India

#### ABSTRACT

This paper portrays the designing of Reversible Logic gates through the use of Quantum Dot Cellular Automata (QCA) which is a nanotechnology concept and also a striking substitute for transistor based technologies. This technology helps us to rise above the confines of CMOS technology. It also gives better results in terms of digital and analog waveform, Quantum cost, garbage output. The fundamental logic in QCA is the logic state that does not compute with voltage level; rather it measures the polarity of electrons in a quantum cell. Basically Reversible logic gates are an essential building block of various computing system. Comparing with standard gates, the reversible logic gate lower the information bits use loss by reusing the logic information bits logically and realizes the goal of lowering power consumption of logic circuits. A QCAdesigner tool is used for simulation of different kinds of Reversible logic gates such as Toffoli gate, Fredkin gate and some others.

#### **Keywords**

QCA, Reversible gates, Majority gate, clock, NANO-Technology

#### **1. INTRODUCTION**

As it seems to be a major concern of energy dissipation with the increment in the circuit complexity. Some portion of energy is from real time switching elements while some are from every irreversible bit operation which is depicted as KTln2, which was negligible for multi-billion incoming electrons passing through various gates [1]. This trouncing of energy can be diminished through the application of reversibility principle on digital circuits and it enables the circuit functioning with a minute fraction of energy [5]. Therefore, this reversible computing concept act as energy solution to many budding fields of nanotechnology in relation to quantum computing [1]. The gates which agree to regeneration of inputs from the detected outputs are the reversible logic gates. It has same number of input and output lines whereas the output line which was not utilize in any circuit was considered to be a garbage signal and the fan-out of each output line is one [2].

The aim behind reversible computing is the storage cells having electric charge with the transistor in it and not allows emerging out when the switching operation actively performed in transistor. Then it will be capable of use again through reversible computing, which ultimately lowered down the energy utilization with not any loss of digital data bits and such systems are known as reversible systems [3]. As logic is designed to be reversible but the cause of this act that information must not be wipe out. This concludes that general gates like "AND" and "OR" cannot be implemented through reversibility as multiple inputs bring down to a single output which was not in accordance to a reversibility concept as there is loss of information. The circuits with extremely less power Jyotirmoy Pathak Department of E.C.E Lovely Professional University Jalandhar, India

consumption and doesn't need any sort of regular interconnections are an advantage [7].

This paper focuses upon the various architectures of reversible gates designed in QCADesigner tool with their graphical output waveforms while logic verification through the traditional truth table based methods.

#### 2. REVERSIBLE LOGIC GATES

A circuit is said to be reversible if the input vector can be uniquely recovered from the output vector and there is a one to one correspondence between its input and output vectors, i.e. not only the outputs can be uniquely determined from the inputs and vice versa[8]. Thus the number of inputs and outputs in reversible gates are equal. Any arithmetic logic unit [6] must be able to produce a variety of logic outputs based on inputs determined by the programmer for implementation in an instruction set architecture. Therefore, reversible logic devices used in an environment must have both fixed select input lines that receive op-code signals manipulated by the programmer and permanent output lines where the result of the logical output is produced [3].

For an n input/output logic gate, if there is a one-to-one correspondence between its inputs and outputs, then this logic gate is reversible. The subsequent expressions are [8]:

$$I_{v} = I_{(n-1)!} \tag{1}$$

$$O_v = O_{(n-1)!} \tag{2}$$

Where the  $I_v$  is input vector and  $O_v$  is the output vector. That is to say, a reversible gate has the same number of inputs and outputs. Commonly used reversible gates are NOT gate, CNOT gate, CCNOT gate (Toffoli gate), Peres gate, Fredkin gate, Feynman gate [9].

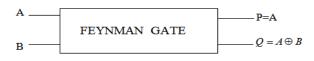

#### 2.1 Feynman gate

It is a 2\*2 reversible gate with  $I_v = (A, B)$  and  $O_v = (P, Q)$  where  $I_v$  and  $O_v$  are the input and output vectors respectively. Quantum cost of Feynman gate is 1.

#### Fig. 1. Block diagram of feynman gate [3]

#### 2.2 Toffoli Gate

It is a 3\*3 gate with inputs (A, B, C) and outputs (P, Q, R) where P=A, Q=B and R=AB XOR C. It has quantum cost 4.

Fig. 2. Block diagram of Toffoli gate [3]

#### 2.3 Fredkin Gate

It is a 3\*3 gate with inputs (A, B, C) and outputs (P, Q, R) where P=A, Q=A'B+AC, R=AB+A'C having quantum cost 4.

| A   | 4            | P=A          |

|-----|--------------|--------------|

| В — | FREDKIN GATE | Q = A'B + AC |

| С — |              | R = A'C + AB |

Fig. 3. Block diagram of Fredkin gate [3]

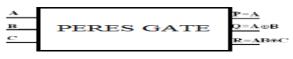

#### 2.4 Peres Gate

It is a 3\*3 gate having inputs (A, B, C) and outputs (P, Q, R) where P= A; Q = A XOR B; R = AB XOR C. It has Quantum cost four.

Fig. 4. Block diagram of Peres gate [3]

# 3. QCA DESIGN OF REVERSIBLE GATES

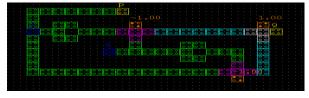

#### 3.1 Feynman Gate

Fig. 5. QCA based Feynman gate

This gate is designed with two inverters, two AND gate and one OR gate.

#### 3.2 Toffoli Gate

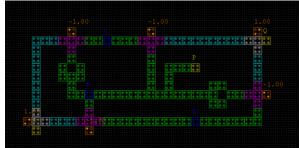

Fig. 6. QCA based Toffoli gate

This gate is designed with two inverters, two AND gates and one OR gate.

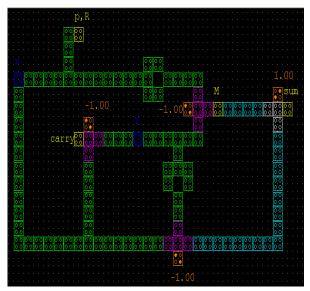

# 3.3 Fredkin Gate

Fig. 7. QCA based Fredkin gate

This gate is designed with two inverters, four AND gates and two OR gates.

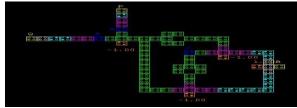

#### 3.4 Peres gate

Fig. 8. QCA based Peres gate

This gate is designed with four inverters, five AND gates and two OR gates

#### 4. RESULT VERIFICATION

The result has been verified by comparing the graphical result obtained from QCADesigner tool with the truth table of these Reversible logic gates.

#### 4.1 Feynman Gate

Table 1. Truth Table for Feynman gate

| Input |   | Output |   |  |

|-------|---|--------|---|--|

| А     | В | Р      | Q |  |

| 0     | 0 | 0      | 0 |  |

| 0     | 1 | 0      | 1 |  |

| 1     | 0 | 1      | 1 |  |

| 1     | 1 | 1      | 0 |  |

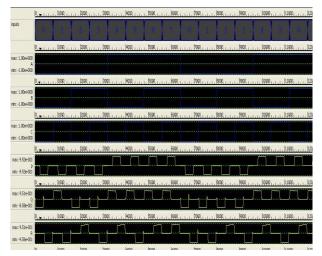

Fig 9. QCA output of Feynman gate

# 4.2 Toffoli Gate

Table 2. Truth table for Toffoli gate

| Input |   |   | Output |   |   |  |

|-------|---|---|--------|---|---|--|

| А     | В | С | Р      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 0 | 1 |  |

| 0     | 1 | 0 | 0      | 1 | 0 |  |

| 0     | 1 | 1 | 0      | 1 | 1 |  |

| 1     | 0 | 0 | 1      | 0 | 0 |  |

| 1 | 0 | 1 | 1 | 0 | 1 |

|---|---|---|---|---|---|

| 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 |

|                                             | 0.1.1.1.1.1.1000   | 1.1.1. 2000.1.1.       | .,  9990,                | 000                                      | 16000 | . 17040                     | 1.1.1. MP.1.1.     | , hoop, , hoop,         | 111.12     |

|---------------------------------------------|--------------------|------------------------|--------------------------|------------------------------------------|-------|-----------------------------|--------------------|-------------------------|------------|

| A                                           |                    |                        | 0                        |                                          |       |                             | ł                  |                         | 0          |

|                                             | 0.1.1.1.1. (1991   | 1.1.1. (2000, 1.1.     | 1, 13999, 1, 1, 1, 1, 14 | 000, 1                                   | KOQ0, | 17040                       | 1.1.1. 900.1.1.    | 1, 100001,, 100001      | 1.1.1      |

| 8                                           |                    | ()                     |                          | ļ:                                       |       | 9                           |                    | 1                       | Į          |

|                                             | b                  | 1.1.1. (2000, 1.1.     | L. 19990. L. L. L. H     | QQQ, <u>1</u>                            |       | , 17000, 1., 1., 1., 18000, | 1.1.1.1900.1.1.    | , boop, buop,           | 111.12     |

| C                                           | Q                  | 1                      | 0                        | 1                                        | 0     | 1                           | 0                  | 1                       | 0          |

|                                             | 0.1.1.1.1.1.1.1000 | 1.1.1. 2000.1.1.       | 1, 19990, 1, 1, 1, 1, 1  | 000, <u>1. 1. 1. 1</u> 5000, <u>1. 1</u> |       | , 17000, 1 1 1 19000,       | 1.1.1. 9000,1.1.   | , hoop, , hitop,        | 111.12     |

| P                                           | 0                  | 0                      | 0                        | -{0}                                     | 0     | 1                           | 1                  |                         | 1          |

|                                             | 0.1.1.1.1.1.1.1000 | 1.1.1. 2000, 1.1.      | .   1000 H               | 990,                                     |       | . 17000. 1 1 1 BOOD         | 1.1.1. 9000,1.1.   | , (10000                | . 1. 1. 12 |

| Q                                           | 0 }                | 0                      | 0                        | 1                                        | 1     | 0                           | 0                  | 1                       | 1          |

|                                             | b                  | L. L. L. (2000), L. L. | ., 19990, H              | 999, 1                                   |       | . 17000                     | 1.1.1.1.19990.1.1. | , þogp, , , , , , þugo, |            |

| R                                           | 1                  | 0                      | 1                        | 0                                        | 1     | 0                           | 1                  | 1                       | 0          |

|                                             | 0                  | 1.1.1. 2000, 1.1.      | , 19990, H               | 000, <u>1.1.1.</u> 15000, <u>1.1</u>     |       | 17040 BOOD                  | 1.1.1. 900, 1.1.   | , (1000) (1100) .       | 111.12     |

| max: 9.80e-022<br>Clock 0<br>min: 3.80e-023 |                    |                        |                          |                                          |       |                             |                    |                         |            |

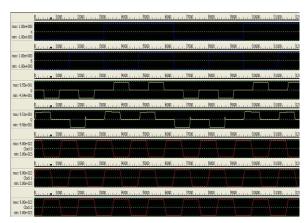

Fig. 10. QCA output of Toffoli gate

#### 4.3 Fredkin Gate

Table 3. Truth Table for Fredkin Gate

| Input |   |   | Output |   |   |  |

|-------|---|---|--------|---|---|--|

| А     | В | С | Р      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 0 | 1 |  |

| 0     | 1 | 0 | 0      | 1 | 0 |  |

| 0     | 1 | 1 | 0      | 1 | 1 |  |

| 1     | 0 | 0 | 1      | 0 | 0 |  |

| 1     | 0 | 1 | 1      | 1 | 0 |  |

| 1     | 1 | 0 | 1      | 0 | 1 |  |

| 1     | 1 | 1 | 1      | 1 | 1 |  |

Fig. 11. QCA output of Fredkin gate

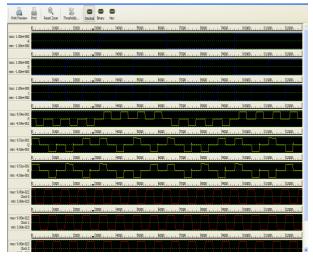

# 4.4 Peres Gate

Table 4. Truth Table for Peres Gate

| Input |   |   | Output |   |   |  |

|-------|---|---|--------|---|---|--|

| А     | В | С | Р      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 0 | 1 |  |

| 0     | 1 | 0 | 0      | 1 | 0 |  |

| 0     | 1 | 1 | 0      | 1 | 1 |  |

| 1     | 0 | 0 | 1      | 1 | 0 |  |

| 1     | 0 | 1 | 1      | 1 | 1 |  |

| 1     | 1 | 0 | 1      | 0 | 1 |  |

| 1     | 1 | 1 | 1      | 0 | 0 |  |

Fig. 12. QCA output of Peres gate

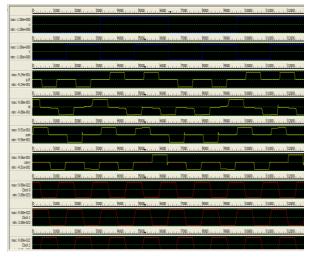

# 5. HALF ADDER

A Half adder has been designed using reversible logic gates namely Feynman and Fredkin gate.

Fig. 13. QCA layout of Half-Adder

Fig. 14. QCA output of Half-Adder

# 6. CONCLUSION

The reversible circuits form the basic building block of quantum computers. Here, the primitive reversible gates which are gathered from literature and it helps researches/designers in designing circuits using reversible gates. Although reversible logic gates needs more cell count as compared to regular gates designed in QCA. The fundamental reversible logic gates has been tested and verified on the QCA Designer tool with minimum delay latency. Also it has wide scope in the fields of DNA computing, Digital signal processor and nano based bioinformation services.

# 7. ACKNOWLEDGMENTS

We are grateful to Lovely Professional University, faculty members teaching and non-teaching for their support in carrying out this work within stipulated time frame.

# 8. REFERENCES

- M. Mahapatro, S. K. Panda, J. Satpathy, and M. Saheel, "Design of Arithmetic Circuits Using Reversible Logic Gates and Power Dissipation Calculation", International Symposium on Electronic System Design. pp. 85-90, Dec 2010.

- [2] Md.B.Ali, H.A. Rahman, Md.M. Rahman, "Design of a High Performance Reversible Multiplier", International Journal of Computer Sciences Issues. Vol.8, NO.1, pp. 134-141, Nov 2011.

- [3] B.S. Premanda, Y.M. Ravomdranath, "Design and Synthesis of 16-bit ALU using Reversible Logic Gates", International Journal of Advanced Research in Computer and Communication Engineering.Vol.2, Issue 10, pp. 4137-4141, Oct 2013.

- [4] J.W.David, K.Izzet, "Using Positive Feedback Adiabatic Logic to implement Reversible Toffoli Gates", NORCHIP, IEEE. pp. 5-8, Nov 2008.

- [5] G.W. Manisha, P.K. Dakhole, "Design and implementation of 4-Bit Arithmetic Logic Unit using Quantum Dot Cellular Automata", Advance Computing Conference, IEEE. pp. 1022-1029, Feb 2013.

- [6] S. Hashemi, M.R. Azghadi, Z. Ali, "A Novel QCA Multiplexer Design", International Symposium on Telecommunications, IEEE. pp. 692-698, Aug 2008.

- [7] H.R. Aradhya, B.V.P. Kumar, K.N. Muralidhara, " Design of Control Unit for Low Power ALU using Reversible Logic", International Journal of Scientific & Engineering Research. Vol.2, Issue 9, pp. 1-7, Sep 2011.

- [8] D. Akanksha, K. Vinod, "Arithmetic & Logic Unit (ALU) Design using Reversible Control Unit", International Journal of Engineering and Innovative Technology (IJEIT). Vol.1, Issue 6, pp. 55-60, June 2012.

- [9] B. Dehghan, "Design of Asynchronous sequential circuits using Reversible Logic gates", International Journal of Engineering and Technology. Vol.4, NO.4, pp.213-219, Aug 2012.