# DESIGN OF 16-BIT LOW POWER ALU - DBGPU

Dhanabal R<sup>1</sup>,Bharathi V<sup>2</sup>,Saira Salim<sup>3</sup>, Bincy Thomas<sup>4</sup>, Hyma Soman<sup>5</sup>, Dr Sarat Kumar Sahoo<sup>6</sup>

<sup>1</sup>Assistant Professor (Senior Grade) ,VLSI division,SENSE, VIT University,

<sup>2</sup>Assistant Professor, GGR College of Engineering , Vellore,

<sup>3,4,5</sup>Student,SENSE, VIT University,

<sup>6</sup>Professor, VIT University, Vellore- 632014, Tamil Nadu, India

rdhanabal@vit.ac.in,bharathiveerappan@yahoo.co.in,salimsaira@gmail.com, bincythomas1989@gmail.com, hymasoman@gmail.com

### Abstract

Arithmetic and Logic Unit (ALU) is one of the common and the most crucial components of an embedded system. Power consumption is a major design issue in the case of embedded systems. Usually ALU's consists of a number of functional units for different arithmetic and logic operations which are realised using combinational circuits. Each of the functional unit performs a specific arithmetic or logic operation. In this paper the main concern is given for reducing the power of the adder and multiplier modules which are important functional units of ALU thereby reducing the overall power consumption without compromising the speed of the processor. The ALU circuit ensures the execution of either arithmetic or logic operation only at a time so that only one set of circuits is active at a time thus ensuring low power consumption. The entire ALU circuit is realised using Verilog HDL and power analysis is obtained through same.

Keywords: Adder/Subtractor, Column Bypassing, Compressor

# 1. ALU

### **1.1 Introduction**

The design of low power and high speed microprocessors requires that its components should consume less power. Arithmetic and Logic Unit (ALU) is one of the most power consuming components in a microprocessor. So, to reduce the power consumption of the entire ALU each of its components should consume less power.

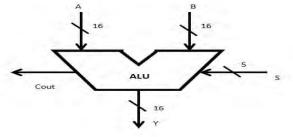

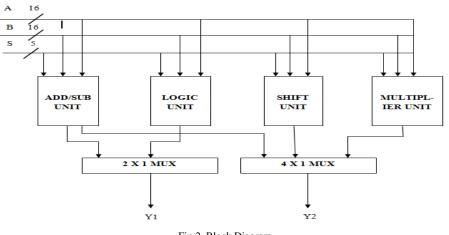

Here we concentrate on a 16 bit ALU implementation which includes an ADDER/SUBTRACTOR module using carry look ahead adder, a MULTIPLIER module using column bypassing with inbuilt compressor, a SHIFTER with 8 different shift operations and a LOGIC unit.

Carry Look Ahead adder module consumes very less power and is much faster compared to Ripple Carry Adder. Likewise the multiplier module using compressor has reduced the usage of full adders for column wise addition, thereby reducing power consumption effectively.

Fig 1. Symbol

#### Fig 2. Block Diagram

## 1.2 ALU Operations

|              |      | Control sig | nals         |              |                            |

|--------------|------|-------------|--------------|--------------|----------------------------|

| <b>S</b> [4] | S[3] | S[2]        | <b>S</b> [1] | <b>S</b> [0] | OPERATION                  |

| 0            | 0    | 0           | 0            | 0            | Half Adder                 |

| 0            | 0    | 0           | 0            | 1            | Half Subtractor            |

| 0            | 0    | 0           | 1            | 0            | Full Adder                 |

| 0            | 0    | 0           | 1            | 1            | Full Subtractor            |

| 0            | 0    | 1           | 0            | 0            | Logical AND                |

| 0            | 0    | 1           | 0            | 1            | Logical OR                 |

| 0            | 0    | 1           | 1            | 0            | XOR                        |

| 0            | 0    | 1           | 1            | 1            | Compliment                 |

| 0            | 1    | 0           | 0            | 0            | No Shift                   |

| 0            | 1    | 0           | 0            | 1            | Arithmetic Left Shift      |

| 0            | 1    | 0           | 1            | 0            | Arithmetic Right Shift     |

| 0            | 1    | 0           | 1            | 1            | Logical Left Shift         |

| 0            | 1    | 1           | 0            | 0            | Rotate Left                |

| 0            | 1    | 1           | 0            | 1            | Rotate Right               |

| 0            | 1    | 1           | 1            | 0            | Rotate Left Through Carry  |

| 0            | 1    | 1           | 1            | 1            | Rotate Right Through Carry |

| 1            | 0    | 0           | 0            | 0            | Multiplication             |

Control logic of control unit :Table 1

# 2. 16-bit Carry Look Ahead Adder/Subtractor

The carry look ahead adder reduces the consumption of power without compromising the speed of the adder. This is achieved by generating carry simultaneously from all the bits. An n-bit carry look-ahead adder is formed from n stages, where each stage is a full adder modified by replacing its carry output line  $C_i$  by two auxiliary signals, generate (G) and propagate (P), where

| $G_i = X_i Y_i$                                       | (1) |

|-------------------------------------------------------|-----|

| $\mathbf{P}_i = \mathbf{X}_i \wedge \mathbf{Y}_i$     |     |

| The carry in $i^{th}$ stage, $C_i = G_i + P_iC_{i-1}$ | (2) |

| Similarly $C_{i-1} = G_{i-1} + P_{i-1}C_{i-2}$        | (3) |

Substituting, equation (3) in equation (2),

$C_i = G_i + P_i G_{i-1} + P_i P_{i-1} C_{i-2}$

(4)

That is, C<sub>i</sub> can be expressed as function of the P and G outputs of all the previous stages.

Carry look-ahead can be extended to larger adders. For example, four 1bit adder can be connected to form a 4bit adder and such four 4-bit adders can be connected to form the 16-bit adder.

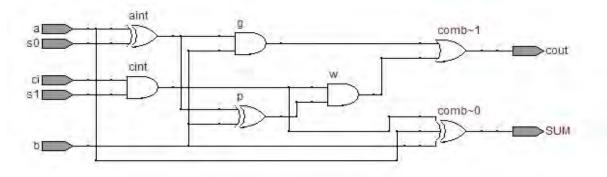

In our ALU we have used the concept of adder-subtractor where the same circuit performs the functions of both adder and subtractor. The adder functions based on the concept of look ahead carry adder. The subtractor just uses an xor gate as an extra circuitry. The block diagram for an adder-subtractor circuit thus can be as below.

Fig 3. RTL view of adder subtractor

This is extended to 16 bits of data. The use of a single circuit for both adder and subtractor reduces power consumption and also area. The operation of the adder-subtractor is based on the S1 and S0 control bits.

| S1 | <b>S0</b> | Operation       |

|----|-----------|-----------------|

| 0  | 0         | Half Adder      |

| 0  | 1         | Half Subtractor |

| 1  | 0         | Full Adder      |

| 1  | 1         | Full Subtractor |

Table 2

## 3.8\*8 Multiplier

The multiplier can multiply two 8 bit numbers resulting in a 16 bit product. We use coloumn bypass technique which reduces power consumption. A compressor module is used to calculate each bit in the product. This helps to reduce power. Thus power reduction is obtained through the two methods.

#### 3.1 Column Bypassing

The column bypassing technique is advantageous over row bypassing in power reduction. It does not perform shifting and use partial products as in row bypassing. The circuit of the column bypassing scheme is smaller than that of the row bypassing scheme. We perform normal multiplication of two 8 bit numbers. First multiply each bit of the multiplier with that of the multiplicand and displayed as in usual multiplication. Then last bit position is taken as the LSB of the product. All other bits are obtained by addition using full adder and compressor along with carry propagated from previous states.

|          |      | A3B0 | A2B0 | A1B0 | A0B0 |

|----------|------|------|------|------|------|

|          | A3B1 | A2B1 | A1B1 | A0B1 |      |

| A3B2     | A2B2 | A1B2 | A0B2 |      |      |

| <br>4002 | A1B3 | 1002 |      |      |      |

### **3.2 Compressor**

Most digital signal processing (DSP) circuits use adder compressors for low power and high performance. Compressors can be used in multiplier architectures also. Multipliers are usually structured into three functions: partial-product generation, partial-product accumulation and final addition. The main source of power, delay and area is the partial-product accumulation stage .Compressors reduce the number of adders required at the final stage and thus reduces power consumption. Also it contributes to reduce the critical path and thus maintains the performance of the circuit. Here we have used a 4-2 compressor and 5-2 compressor to perform addition.

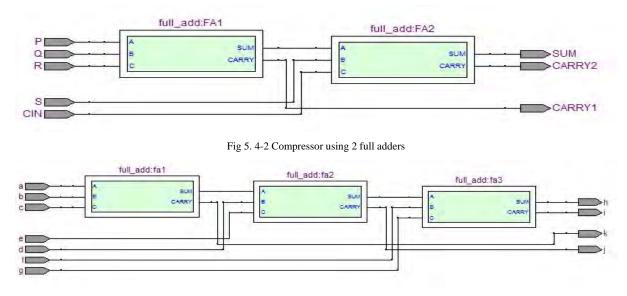

### 3.3 4-2 Compressor

The 4-2 Compressor has 5 inputs P, Q, R,S and Cin and has 3 outputs Sum, Carry1 and Carry2 as shown in Figure 4. The input Cin is the output from a previous lower significant compressor and the Cout output is input for the compressor in the next significant stage. The 4-2 compressors is with 2 full adders connected serially as shown in Figure 4.

Fig 6. 5-2 Compressor using 3 full adders

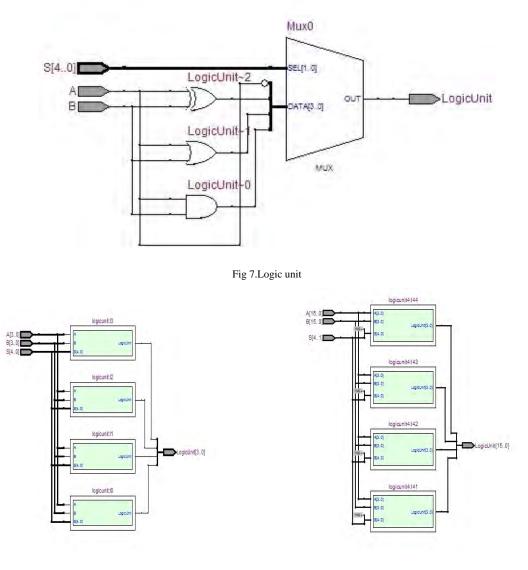

### 4. Logic Unit

The logical functions performed are AND, OR, XOR and NOT. Bitwise operation is performed on the two inputs. The operation to be performed is decided by the 2 least significant bits of the decoder output.

| <b>S</b> [1] | S[0] | Logical Operation |

|--------------|------|-------------------|

| 0            | 0    | A.B               |

| 0            | 1    | A+B               |

| 1            | 0    | A^B               |

| 1            | 1    | ~A                |

Table 3

Fig 8. 4 bit logic unit

Fig 9. 16bit logic unit

### 5. Shifter

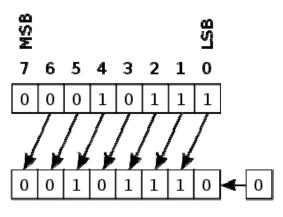

The ALU designed performs 7 Shift/Rotate Operations namely arithmetic left shift(same as logical left shift), arithmetic right shift, logical right shift, rotate and rotate through carry. The logical shift operation shifts each bit of the operand. In logical shift a number's sign bit is not preserved. and each bit in the operand is moved a specified number of bit positions. The vacant bit-positions are filled with zeros. In arithmetic shifts, the shifted bit is retained.

Logical shift is an efficient way to perform division and multiplication of integers by powers of two. Shifting left by k bits on a binary number is equivalent to multiplying it by  $2^k$ . Similarly shifting right by k bits on an binary number is equivalent to dividing it by  $2^k$ .

For example, consider the binary number 0001 0111.

Fig 10. Logical left shift

Fig 11. Logical Right Shift

The shift/rotate operation is performed based on the 3 lower significant bits of the select line **5.1 Shift Operations**

| ··· ··· ··· ··· |              |      |                               |

|-----------------|--------------|------|-------------------------------|

| S[2]            | <b>S</b> [1] | S[0] | OPERATION                     |

| 0               | 0            | 0    | No Shift                      |

| 0               | 0            | 1    | Arithmetic(logical)Left Shift |

| 0               | 1            | 0    | Arithmetic Right Shift        |

| 0               | 1            | 1    | Logical Right Shift           |

| 1               | 0            | 0    | Rotate left shift             |

| 1               | 0            | 1    | Rotate Right shift            |

| 1               | 1            | 0    | Rotate left through carry     |

| 1               | 1            | 1    | Rotate right through carry    |

Table 4

# 6. Simulation Results

6.1 Adder/Subtractor

| Norm     00010       0     5     00010       0     6     8 101     101011001111       0     23     0     8 111     111000101011100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Master 1       | TimeBac | 15 075 | en: | + + Powler       | 4.34     | 64      | Interval | -1074 m       | Slat    |          | End      |         |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|--------|-----|------------------|----------|---------|----------|---------------|---------|----------|----------|---------|-----|

| Image: Bit A     8 101     3010110011100111       Image: Bit A     8 101     1110001030111100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | Naces   |        | Pos | 854 pa           | 1.388 ns | 2.08214 | 2.77Ens  | 147rs         | a séana | 4.253 rs | 5.552 /8 | 6246 no | 5.9 |

| Image: Second | -              |         | -      |     | 00010            |          |         |          |               |         |          |          |         | _   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1006           | E A     | 8 101  |     |                  |          |         |          |               |         |          |          |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10-23          | B é     | 8 111  |     | 1110001030111100 |          |         |          |               |         |          |          |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10-41<br>10-52 | E SUM   | 8 100  |     |                  |          |         | -        | 1000111110100 | 91      |          |          |         |     |

# 6.2 Multiplier

| Dps     556 ps     1.112 ns     1.668 ns     2.224 ns     2.78 ns     3.336 ns       IIII+0     ck |                  | Master II | me Bar: | 8.0 ns |        | • • Pointer:    | 25 pt    | Inte     | svat     | -7.98 ns | Start       |          |

|----------------------------------------------------------------------------------------------------|------------------|-----------|---------|--------|--------|-----------------|----------|----------|----------|----------|-------------|----------|

| III-0 ck                                                                                           | 1011111101000000 |           | Name    |        | Ops    | 556 ps          | 1.112 ns | 1.668 ns | 2 224 ns | 2.78 ns  | 3.336 ms    | 3.892 ni |

|                                                                                                    | 1011111101000000 | 0         | clk     |        |        | L.              |          |          |          |          |             |          |

| P B 101 (00000000000000000000000000000000                                                          |                  | 1         | € p     | B 101  | 000000 | 000000000000000 |          |          |          | 10111    | 11101000000 |          |

# 6.3 Logic Unit -AND-operation

| Name 0 ps 10.0 ns 20.0 ns 30.0 ns 40.0 ns 50.0 ns 60.0 ns 70.0 ns 80.0 ns 15.025 ns                     | Start:  |

|---------------------------------------------------------------------------------------------------------|---------|

| Name 0 ps 10.0 ns 20.0 ns 30.0 ns 40.0 ns 50.0 ns 60.0 ns 70.0 ns 80.0 ns 15.025 ns 15.025 ns 15.025 ns | Start:  |

| Name 15.025 ns                                                                                          |         |

|                                                                                                         | 90.0 ns |

| T T                                                                                                     |         |

| 0 🗃 S 00000                                                                                             |         |

| 🗃 6 🖂 A 🛛 B 000 🤇 00000000001111                                                                        |         |

| ■ 23 E B B111 111000011110000                                                                           |         |

| ØP40 Ide LogicUnit   B 000 O0000000000000000000000000000                                                |         |

## 6.4 Shifter-Left Shift

|    | Master T   | Time Bar:  |       | 0 ps     |         |          | 764 ps  | Interval: | 764 ps            | Start   |         |   |

|----|------------|------------|-------|----------|---------|----------|---------|-----------|-------------------|---------|---------|---|

|    |            |            |       | 0 ps     | 10.0 ns | 20.0 ris | 30.0 ns | 40.0 ns   | 50.0 ns           | 60.0 ns | 70.0 ns | 8 |

|    |            | Name       |       | 0 ps     |         |          |         |           |                   |         |         |   |

|    | <b>@</b> 0 | AluNoShift | B 111 | <u> </u> |         |          |         |           | 11111111111111110 |         |         |   |

| â. | 17         | c [        |       |          |         |          |         |           |                   |         |         |   |

|    | <b>1</b> 8 | ₽S         |       | <u> </u> |         |          |         |           | 00001             |         |         |   |

| 1  | 24         | ΞY         | B 111 | (        |         |          |         |           | 11111111111111100 |         |         |   |

|    | 10 41      | shiftout   |       | -        |         |          |         |           |                   |         |         |   |

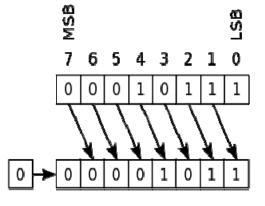

### 7. POWER ANALYSIS

| MODULE           | Dynamic power(mW) | Static power (mW) |

|------------------|-------------------|-------------------|

| Adder/subtractor | 13.76             | 48.31             |

| Logic Unit       | 2.61              | 48.20             |

| Multiplier       | 15.80             | 47.41             |

| Shifter          | 6.04              | 47.57             |

Table 5

Total power consumption split up for ALU

#### 8. Conclusion

The proposed ALU is designed with low power performance. The individual blocks within the ALU such as the adder, multiplier, logical unit and the shifter are low power units thereby reducing the power of the entire ALU unit. The adder used is a carry look ahead adder performing both addition and subtraction operations thus avoiding the need of a separate block for subtractor as in usual ALU designs. Power analysis and simulation was done on each block and found that power is low for each block. Integrating all the blocks in an ALU thus reduces the overall power.

#### 9. Future Enhancement

Multiplier-Accumulator(MAC) is the essential elements of the digital signal processing. Multiplication involves two basic operations: the generation of partial products and their accumulation. The addition and multiplication of two binary numbers is the fundamental and most often used arithmetic operation in microprocessors, digital signal processors, and data processing application-specific integrated circuits. . Since multiplication dominates the execution time of most DSP algorithms, so there is a need of high speed multiplier. In this MAC architecture a new Radix-4 modified booth algorithm is used for high speed multiplication. The Radix-4 MBA reduce N-bits of partial products to n/2 partial products. The parallel multipliers like Radix-4 modified booth multiplier do the computations using lesser adders and lesser iterative steps. This is very important criteria because in the fabrication of chips and high performance system requires components which has area as small as possible. The Multiplier and Accumulator can be adapted to various fields requiring high performance such as signal processing areas. Thus in above ALU ,MAC unit can be included for fast multiplication processing.

#### 10. References

- [1] R Dhanabal, V Bharathi, Anand N, George Joseph, Suwin Sam Oommen, Dr Sarat Kumar Sahoo, "Comparison of Existing Multipliers and Proposal of a New Design for Optimized Performance ", International Journal of Engineering and Technology (IJET) 2013.

- R Dhanabal, Ushashree," Implementation of a High Speed Single Precision Floating Point Unit using Verilog", International Journal of Computer Applications (0975 – 8887),2013.

- [3] T. Esther Rani, M. Asha Rani, Dr. Rameshwar rao. "AREA OPTIMIZED LOW POWER ARITHMETIC AND LOGIC UNIT". IEEE 2011

- [4] Patanjali Prakash Saksena A K . SMIEE "Design Of Low Power High Speed ALU Using Feedback Switch Logic" IEEE 2009

- [5] Thushar V More, Dr.R.V.Kshirsagar "Design of Low Power Coloumn Bypass Multiplier using FPGA" IEEE 2011

- [6] Jeong Beom Kim, Dong Whee Kim. "Low-Power Carry Look-Ahead Adder With Multithreshold Voltage Cmos Technology" IEEE 2007

- Jorge Tonfat, Ricardo Reis Universidade Federal do Rio Grande do Sul (FRGS), "Low Power 3-2 and 4-2 Adder Compressors [7] Implemented Using ASTRAN" 2011

- "N. Weste and K.Eshragian, Principles of CMOS VLSI Design: A Systems Perspective", Pearson/ Addison -Wesley Publishers, 2005. [8]

- [9] "Jan M Rabaey, "Digital Integrated Circuits" (A Design Perspective), Prentice-Hall, Englewood Cliffs, NJ, 1999.

#### **AUTHOR PROFILES:**

R.DHANABAL, Assistant Professor (Sr Grade) in SENSE, Vellore Institute of Technology, Vellore, received the B.E. degree in Electronics and Communication Engineering from Bharathidasan University, Tiruchirappalli, Tamil Nadu, India in 2001, and M.Tech degree in VLSI Design from SASTRA University, Tanjore, Tamilnadu, India in 2002. His research interests are in the area of Low power VLSI design and Mixed Signal IC Design. He is a Life Time member in **BES** (Broadcast Engineering Society) of India.

V.BHARATHI Assistant Professor in CSE Department, GGR College of Engineering, Vellore, Anna University received the B.E. degree in Computer Science and Engineering from Madras University, Chennai, Tamil Nadu, India in 2004, and M.E degree in Computer Science and Engineering from Anna University, Chennai, Tamilnadu, India in 2009.

HYMA SOMAN pursuing M.Tech in VLSI Design in VIT UNIVERSITY, Vellore, India. Graduate in BTech Degree in Electronics and Communication From TKM College Of Engineering, University Of Kerala, Kerala, India in 2011

SAIRA SALIM pursuing MTech in VLSI Design in VIT UNIVERSITY, Vellore, India. Studied Graduate in BTech Degree in Electronics and Communication from College of Engineering Perumon, Cochin University Of Science & Technology (CUSAT) in 2011.

BINCY THOMAS- Graduate in BTech Degree in Electronics and Communication from Mahatma Gandhi University College Of Engineering, Mahathma Gandhi University, Kerala in 2011.