# Design of a Very High Frequency dc-dc Boost Converter

by

Anthony Sagneri

B.S., Rensselaer Polytechnic Institute (1999)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of Master of Science

at the

## Massachusetts Institute of Technology February 2007

© Massachusetts Institute of Technology, MMVII. All rights reserved.

| Author       |                                                           |

|--------------|-----------------------------------------------------------|

|              | Department of Electrical Engineering and Computer Science |

|              | February 2, 2007                                          |

| Certified by |                                                           |

| J            | David J. Perreault                                        |

|              | Associate Professor of Electrical Engineering             |

|              | Thesis Supervisor                                         |

| Accepted by  |                                                           |

| <u> </u>     | Arthur C. Smith                                           |

|              | Chairman, Department Committee on Graduate Students       |

### Design of a Very High Frequency dc-dc Boost Converter

Anthony Sagneri

Submitted to the Department of Electrical Engineering and Computer Science on February 2, 2007, in partial fulfillment of the requirements for the degree of

Master of Science

#### Abstract

Passive component volume is a perennial concern in power conversion. With new circuit architectures operating at extreme high frequencies it becomes possible to miniaturize the passive components needed for a power converter, and to achieve dramatic improvements in converter transient performance. This thesis focuses on the development of a Very High Frequency (VHF, 30 - 300 MHz) dc-dc boost converter using a MOSFET fabricated from a typical power process.

Modeling and design studies reveal the possibility of building VHF dc-dc converters operable over the full automotive input voltage range (8 - 18 V) with transistors in a 50 V power process, through use of newly-developed resonant circuit topologies designed to minimize transistor voltage stress. Based on this, a study of the design of automotive boost converters was undertaken (e.g., for LED headlamp drivers at output voltages in the range of 22 - 33 V.)

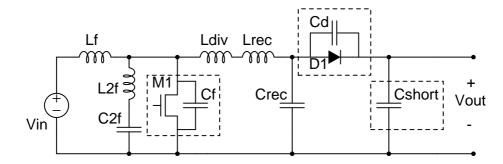

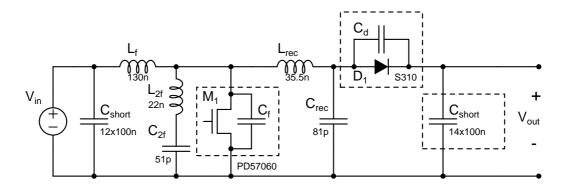

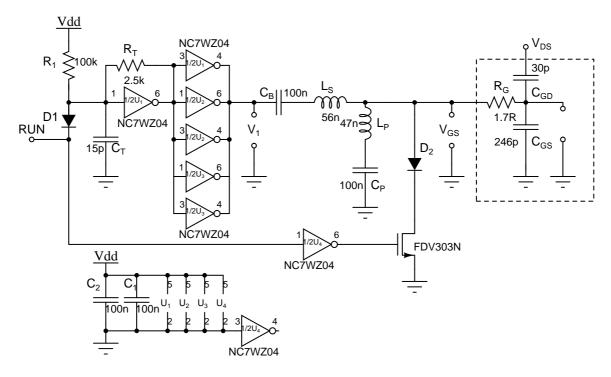

Two VHF boost converter prototypes using a  $\Phi_2$  resonant boost topology were developed. The first design used an off the shelf RF power MOSFET, while the second uses a MOSFET fabricated in a BCD process with no special modifications. Soft switching and soft gating of the devices are employed to achieve efficient operation at a switching frequencies of 75 MHz in the first case and 50 MHz in the latter.

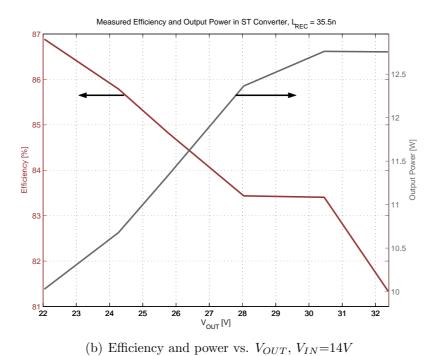

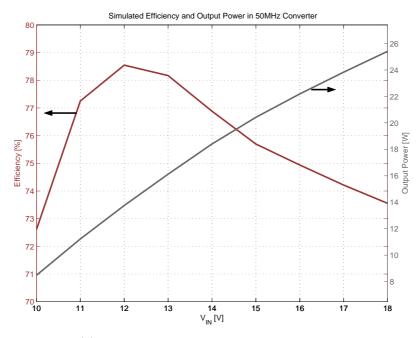

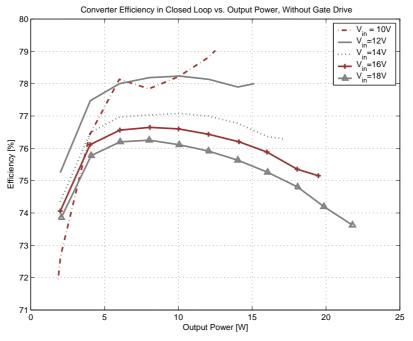

In the 75 MHz case, efficiency ranges to 82%. The 50 MHz converter, has efficiencies in the high 70% range. Of note is low energy storage requirement of this topology. In the case of the 50 MHz converter, in particular, the largest inductor is 56 nH. Finally, closed-loop control is implemented and an evaluation of the transient characteristics reveals excellent performance.

Thesis Supervisor: David J. Perreault

Title: Associate Professor of Electrical Engineering

# Acknowledgements

My thanks are due to the National Science Foundation, National Semiconductor, and the MIT EECS department for sponsorship. To Prof. Dave Perreault, my research advisor, and tacit instructor in all things power electronics, who somehow always seems to stay grounded. To Juan Rivas, also a tremendous source of knowledge, and emissary of laboratory shenanigans along with Jackie Hu and Grace who help to keep the atmosphere light. To Draper Dave, whose ability to warp space-time with his mere presence very nearly caused me to miss yet another degree cycle. To Olivia, Yehui, and Robert who have been helpful at various times over the course of things (and John Ranson who measured some stuff for me), and Brandon Pierquet, without whom I probably never would have found LEES. The rest of LEES also has my thanks, including the giant cockroaches and sewer rats in 10-082, for making things what they are.

I can't help but acknowledge the USAF (United States Air Force or you non-separated military folk), as I probably wouldn't be here if it weren't for the collusion of a whole lot of things that happened there. My fellow MSI cadre: Jeff Painter (also a groomsman, thanks!), Lupe Sabala, Gary Ayers, Dee Melendez, and even Dean, who shared many thrashings, triumphs, and curse words (like, "those !bleeps! at INYR"). It's doubtful I would be here if I didn't have you guys as a team to make me look good to the admissions folks. I still think that Hanscom SRGH should report to MGH for a cleaning. Is 10.2 up and running yet?

Of course, all my friends from other places who have helped me over the years deserve explicit thanks: Lester Pangilinan, my best man, Abe Chayya (charlie india), Manger, Christie, Deano Busch, George, Monica, Matt, Bill, Jess, Jerry Wilson, everyone who is married to one of these people, unless I don't know you, and everybody I forgot…you know who you are.

To Wendy, my wife, who has been a great help when I need distraction, I love you. Thanks!

To Mom and Dad who managed (by dumb luck!) to bring me into the world, and then (not by dumb luck) helped me find my way all the way here (which is about 4.5 hours from where I started). Thanks! Oh, and to my brothers and sisters, who have been useful at times.

# Contents

| 1 | Intr | roduction                                                    | 17 |

|---|------|--------------------------------------------------------------|----|

|   | 1.1  | Losses in hard switched converters                           | 18 |

|   | 1.2  | Resonant Power Conversion                                    | 24 |

|   | 1.3  | Contributions and Organization of the Thesis                 | 27 |

| 2 | The  | $\Phi_2$ $Inverter$                                          | 31 |

|   | 2.1  | The class $\Phi$ Inverter                                    | 31 |

|   | 2.2  | The class $\Phi_2$ Inverter                                  | 35 |

|   |      | 2.2.1 Basic Operating Principles                             | 37 |

|   |      | 2.2.2 Tuning the $\Phi_2$ Inverter                           | 43 |

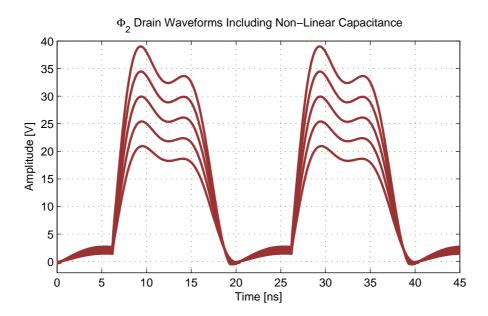

|   |      | 2.2.3 Nonlinear Capacitance Effects on the $\Phi_2$ Inverter | 57 |

| 3 | The  | $\Phi_2$ dc-dc Converter                                     | 59 |

|   | 3.1  | A Resonant Rectifier                                         | 60 |

|   | 3.2  | The Power Stage                                              | 67 |

|   |      | 3.2.1 Important Device Characteristics                       | 68 |

|   |      | 3.2.2 Linking the Inverter and Rectifier                     | 72 |

| 4 | Con  | averter Prototypes                                           | 79 |

|   | 4.1  | The First Prototype                                          | 79 |

|   | 12   | A Second Prototype                                           | 80 |

#### Contents

| 5            | Clos | sed-Loop Operation            | 99  |

|--------------|------|-------------------------------|-----|

|              | 5.1  | Control Scheme                | 99  |

|              | 5.2  | A Resonant Gate Drive         | 101 |

|              | 5.3  | The Controller                | 106 |

|              | 5.4  | Closing the Loop              | 108 |

| 6            | Con  | aclusion                      | 115 |

|              | 6.1  | Thesis Summary                | 115 |

|              | 6.2  | Thesis Conclusions            | 116 |

|              | 6.3  | Future Work                   | 117 |

| $\mathbf{A}$ | SPI  | CE DECKS AND COMPONENT VALUES | 119 |

|              | A.1  | Chapter 1 Data                | 119 |

|              |      | A.1.1 Fig. 1.4 data:          | 119 |

|              | A.2  | Chapter 2 Data                | 121 |

|              |      | A.2.1 Fig. 2.3 data:          | 121 |

|              |      | A.2.2 Fig. 2.4 data:          | 122 |

|              |      | A.2.3 Fig. 2.7 data:          | 123 |

|              |      | A.2.4 Fig. 2.11 data:         | 124 |

|              |      | A.2.5 Fig. 2.13 data:         | 126 |

|              |      | A.2.6 Fig. 2.14 data:         | 128 |

|              |      | A.2.7 Fig. 2.15 data:         | 129 |

|              |      | A.2.8 Fig. 2.17 data:         | 132 |

|              |      | A.2.9 Fig. 2.19 data:         | 134 |

|              | A.3  | Chapter 3 Data                | 136 |

|              |      | A.3.1 Fig. 3.4 data:          | 136 |

|              |      | A.3.2 Fig. 3.5 data:          | 137 |

|              |      | A.3.3 Fig. 3.6 data:          | 138 |

|                                   |       | Cont                             | tents |

|-----------------------------------|-------|----------------------------------|-------|

| A.4                               | Chapt | er 4 Data                        | 139   |

|                                   | A.4.1 | ST Converter Final Spice Deck    | 139   |

|                                   | A.4.2 | 50MHz Converter Final Spice Deck | 145   |

|                                   | A.4.3 | SPICE Model Libraries            | 151   |

| B PCB Layout Masks and Schematics |       | 159                              |       |

| Bibliog                           | raphy |                                  | 167   |

# List of Figures

| 1.1  | Synchronous Buck Converter Active vs. Passive Volume          | 19 |

|------|---------------------------------------------------------------|----|

| 1.2  | Buck-Boost Converter Illustrating Energy Storage Requirements | 20 |

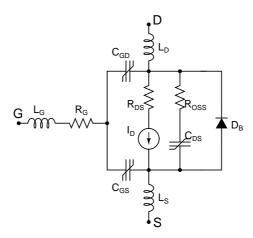

| 1.3  | MOSFET Model                                                  | 22 |

| 1.4  | Class E Inverter Performance vs. Load Resistance              | 25 |

| 1.5  | VHF Converter Under On-Off Modulation                         | 26 |

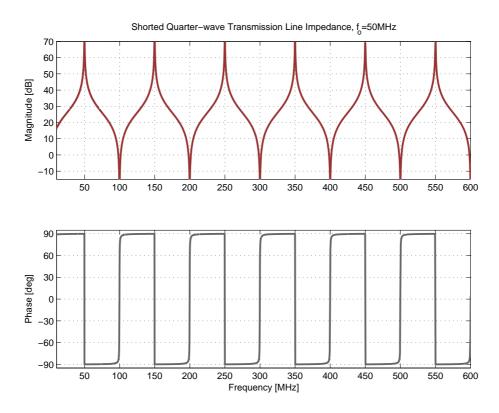

| 2.1  | Shorted quarter-wave line                                     | 32 |

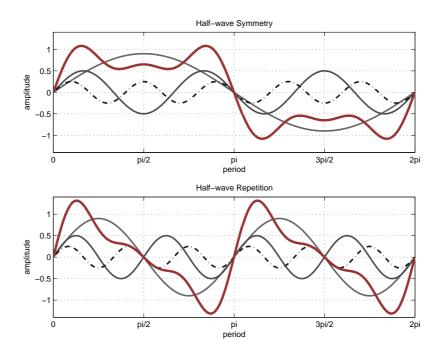

| 2.2  | Half-wave symmetry/repetition                                 | 33 |

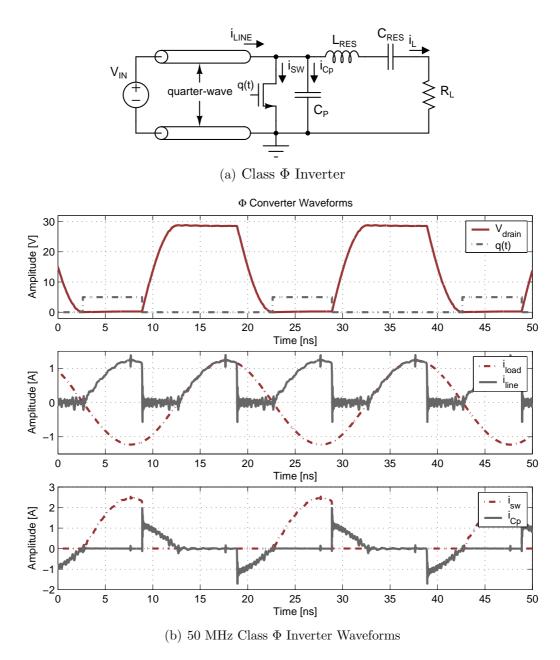

| 2.3  | Class- $\Phi$ Inverter and waveforms                          | 34 |

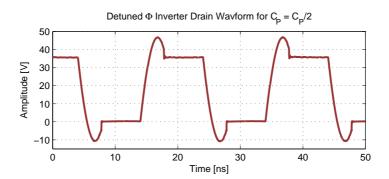

| 2.4  | $\Phi$ Waveforms when inverter is purposefully detuned        | 35 |

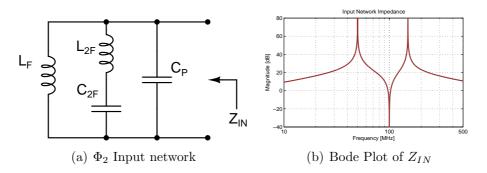

| 2.5  | The $\Phi_2$ Input network and its bode plot                  | 36 |

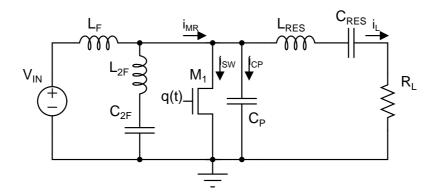

| 2.6  | The $\Phi_2$ Inverter                                         | 37 |

| 2.7  | $\Phi_2$ Inverter waveforms                                   | 38 |

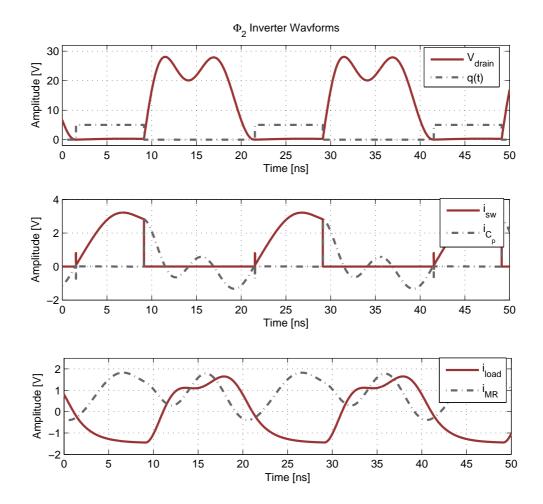

| 2.8  | $\Phi_2$ and transmission line responses                      | 39 |

| 2.9  | Block diagram of source substitution method                   | 40 |

| 2.10 | $\Phi_2$ inverter split for harmonic balance analysis         | 40 |

| 2.11 | $\Phi_2$ network response to initial conditions               | 42 |

| 2.12 | Duty ratio vs. harmonic composition                           | 44 |

| 2.13 | $\Phi_2$ drain-source impedance effects on drain voltage      | 47 |

| 2.14 | Tuning sequence to increase peakiness                         | 48 |

| 2.15 | Tuning characteristic impedance                               | 49 |

| 2.16 | Controlling power in $\Phi_2$ inverter                        | 50 |

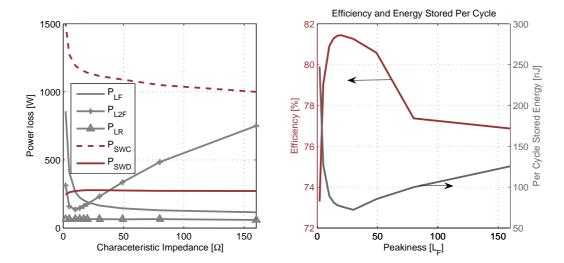

| 2.17 | Loss vs. tuning in $\Phi_2$                                   | 52 |

| 2.18 | Efficiency vs. tuning in $\Phi_2$                                           | 53 |

|------|-----------------------------------------------------------------------------|----|

| 2.19 | Tuning vs. transient response                                               | 54 |

| 2.20 | Efficiency vs. characteristic impedance                                     | 56 |

| 2.21 | $\Phi_2$ inverter with nonlinear capacitance                                | 58 |

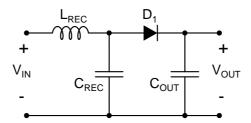

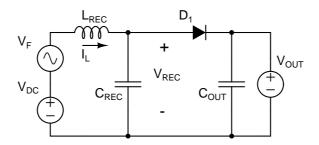

| 3.1  | Series-loaded resonant rectifier                                            | 60 |

| 3.2  | $\Phi_2$ boost converter                                                    | 31 |

| 3.3  | Series-loaded resonant rectifier in SPICE                                   | 52 |

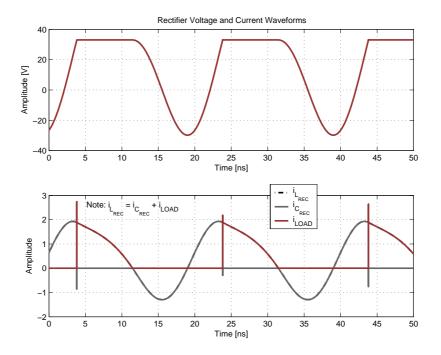

| 3.4  | Rectifier waveforms                                                         | 3  |

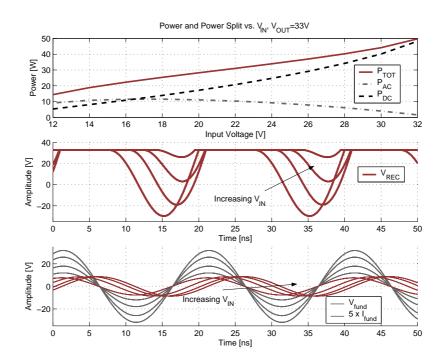

| 3.5  | AC-DC power split in rectifier                                              | 64 |

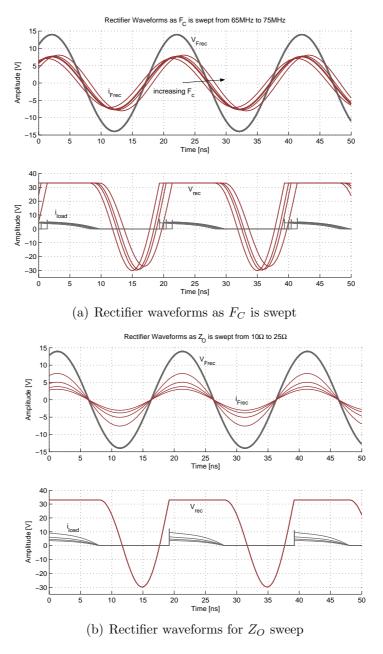

| 3.6  | Tuning rectifier by controlling $F_C$ and $Z_O$                             | 66 |

| 3.7  | MOSFET parasitic mechanisms                                                 | 68 |

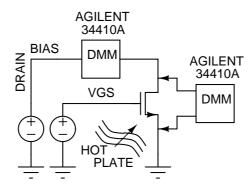

| 3.8  | Measurement Setup for $R_{DS-ON}$ vs. $V_{GS}$ and Temperature              | 70 |

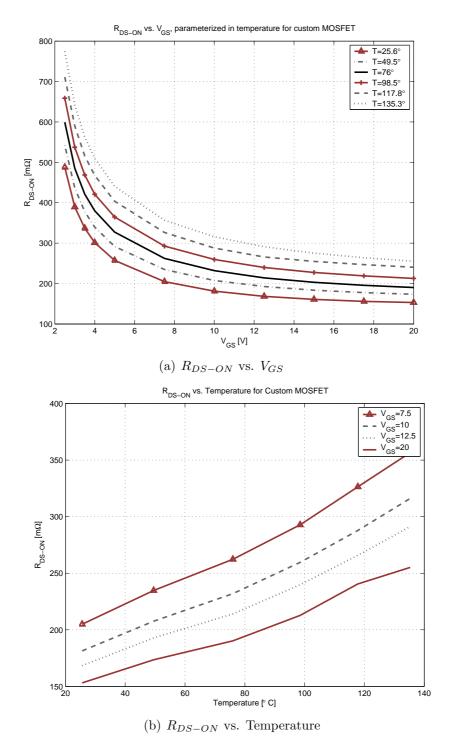

| 3.9  | Temperature dependence of MOSFET channel resistance                         | 71 |

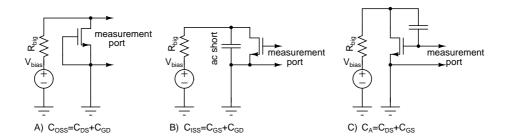

| 3.10 | Capacitance Measurement Setup                                               | 72 |

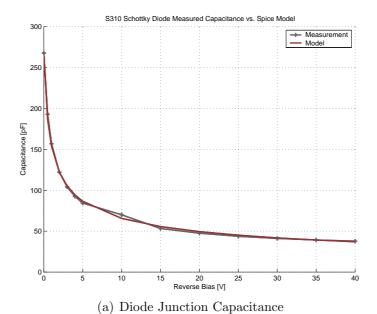

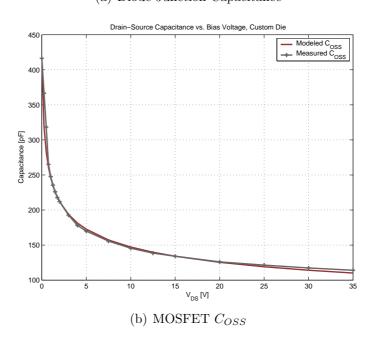

| 3.11 | Device capacitance models compared to measurement                           | 73 |

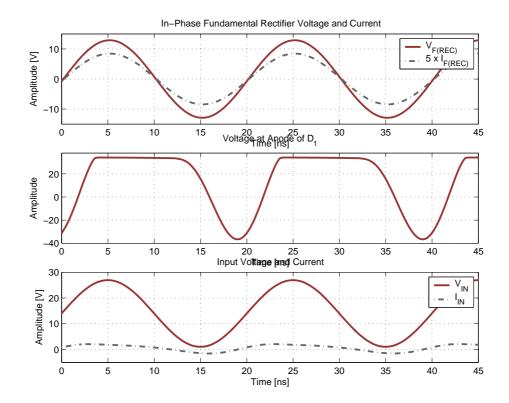

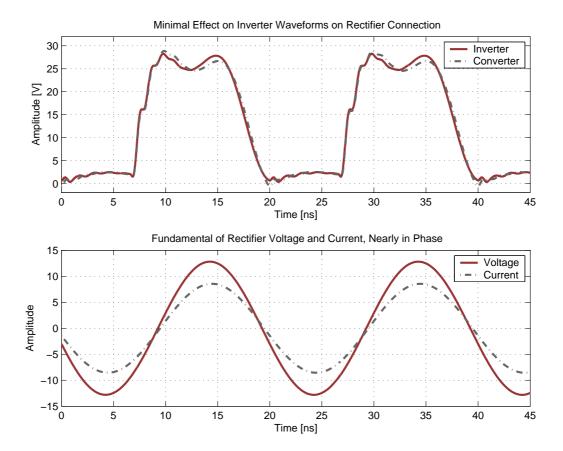

| 3.12 | Rectifier waveforms                                                         | 74 |

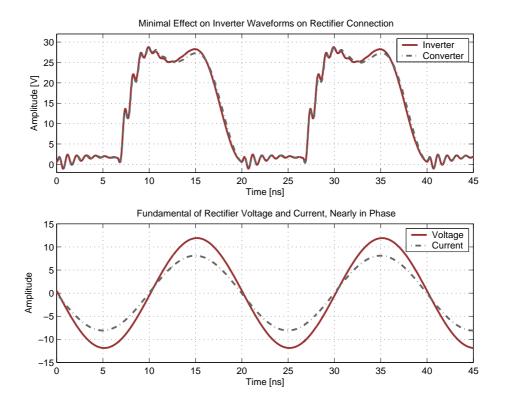

| 3.13 | Inverter and Converter Waveform Overlay                                     | 75 |

| 3.14 | Inverter and Converter Waveform Overlay                                     | 77 |

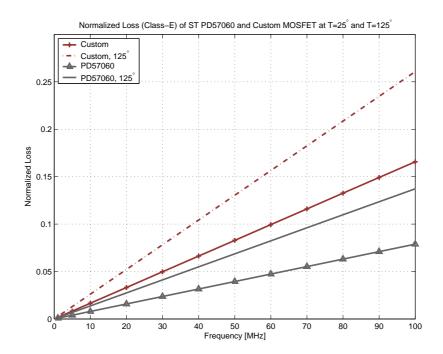

| 4.1  | Ranking of devices based on class-E performance                             | 30 |

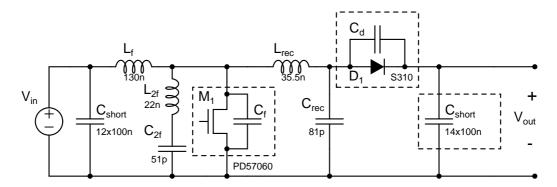

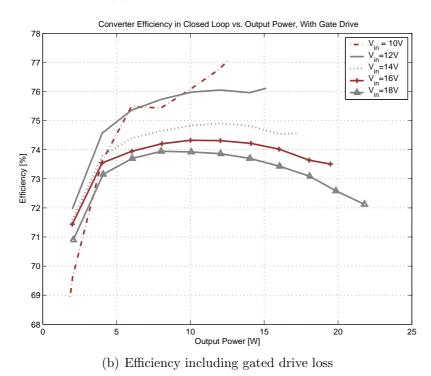

| 4.2  | $\Phi_2$ converter schematic                                                | 32 |

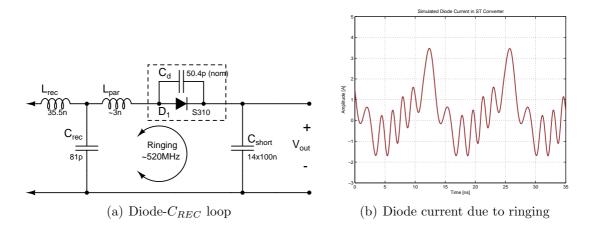

| 4.3  | Diode current ringing around $C_{REC}$ -diode loop                          | 33 |

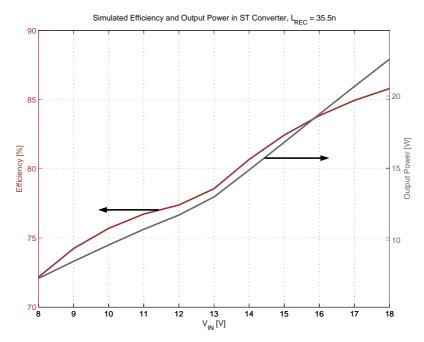

| 4.4  | ST PD57060 $\Phi_2$ converter simulation results                            | 35 |

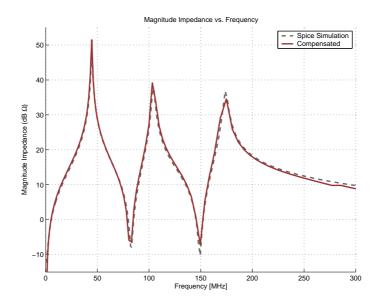

| 4.5  | Simulated and measured impedance match                                      | 36 |

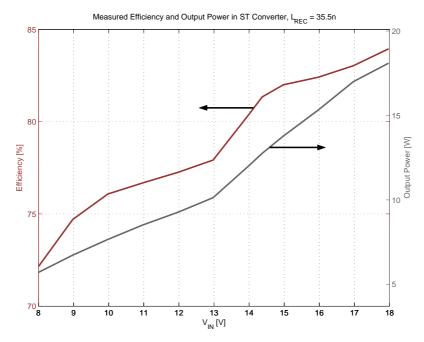

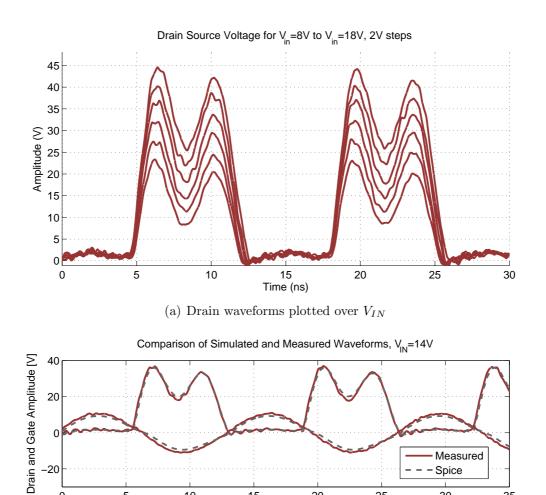

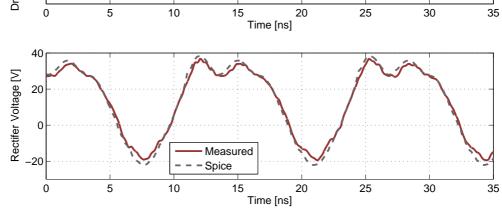

| 4.6  | ST PD57060 $\Phi_2$ converter measurements                                  | 37 |

| 4.7  | ST PD57060 $\Phi_2$ converter experimental waveforms compared to simulation | 38 |

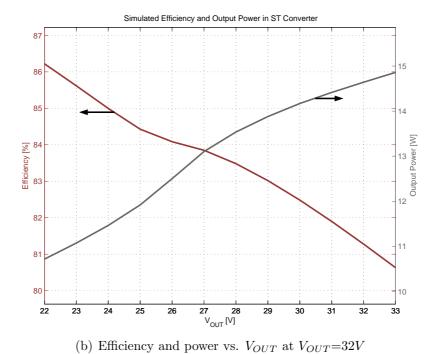

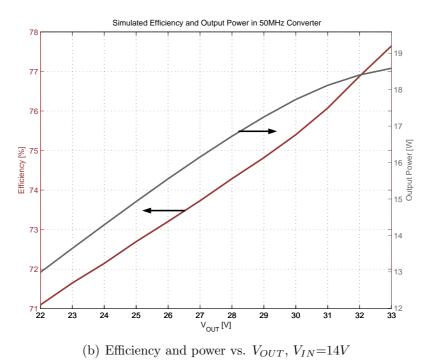

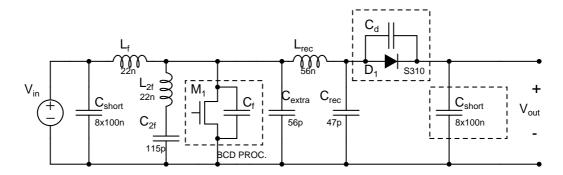

| 4.8  | $50MHz \Phi_2$ converter simulation results                                 | 90 |

| 4.9  | $\Phi_2$ schematic with component values for BCD process              | 91  |

|------|-----------------------------------------------------------------------|-----|

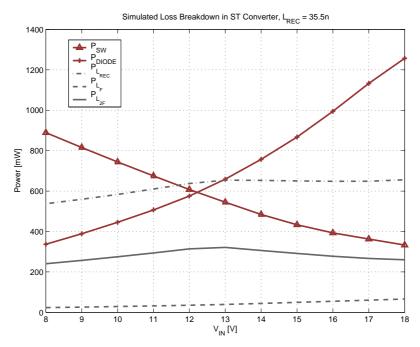

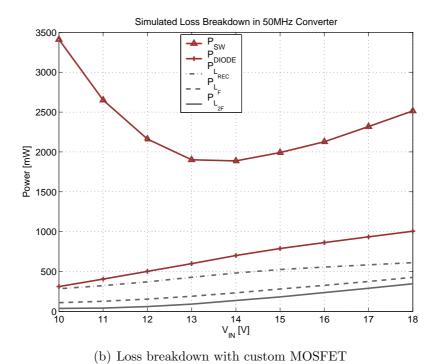

| 4.10 | Breakdown of important loss mechanisms for each prototype (simulated) | 92  |

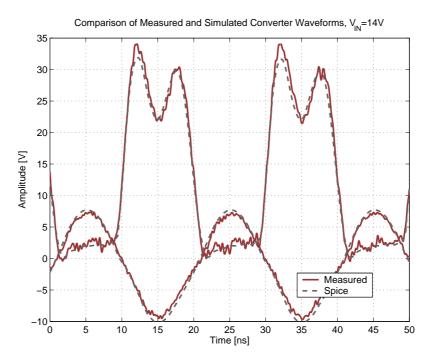

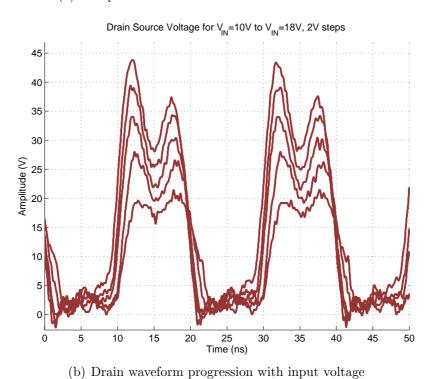

| 4.11 | Experimental waveforms for the $50MHz$ converter                      | 94  |

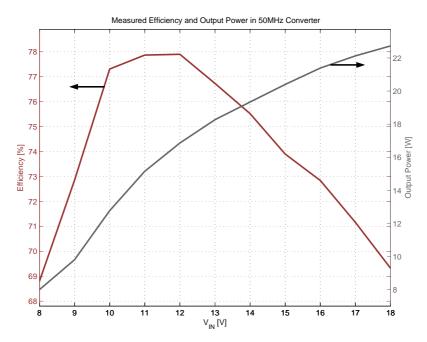

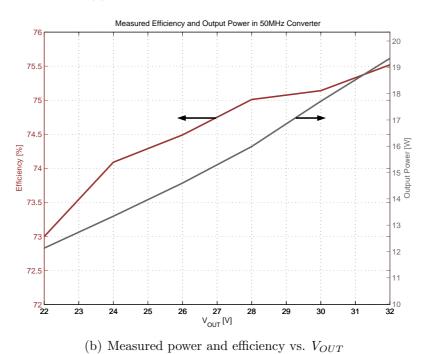

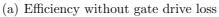

| 4.12 | Experimental output power and efficiency                              | 95  |

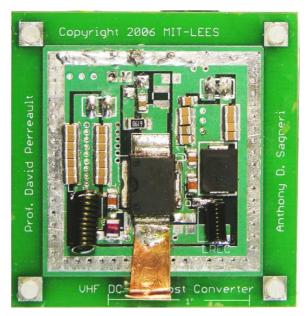

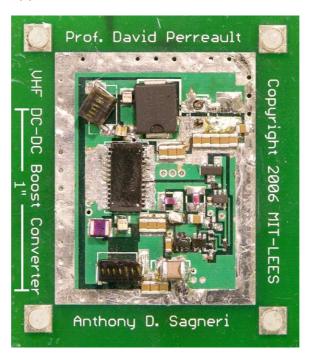

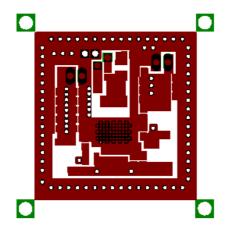

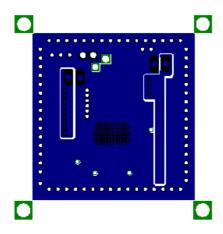

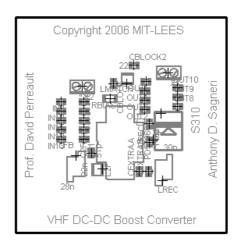

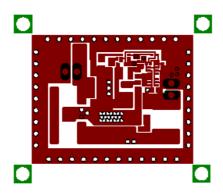

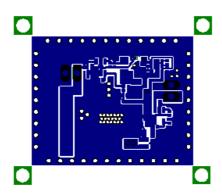

| 4.13 | Converter photographs                                                 | 96  |

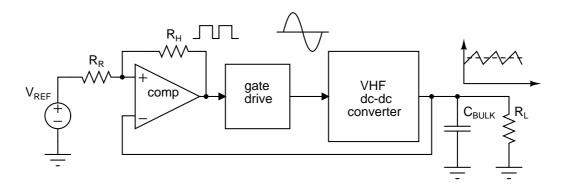

| 5.1  | VHF Converter Under On-Off Modulation                                 | 100 |

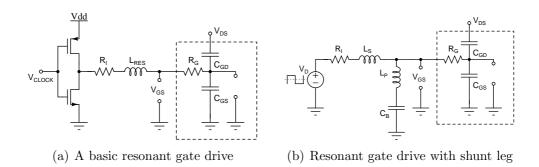

| 5.2  | Basic resonant gate drive                                             | 102 |

| 5.3  | Gate drive with shunt leg                                             | 103 |

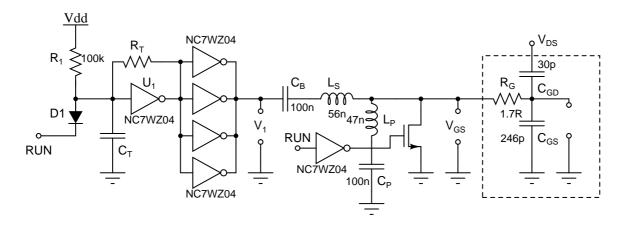

| 5.4  | Final gate drive circuit                                              | 104 |

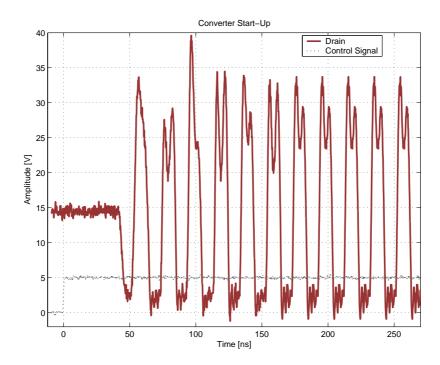

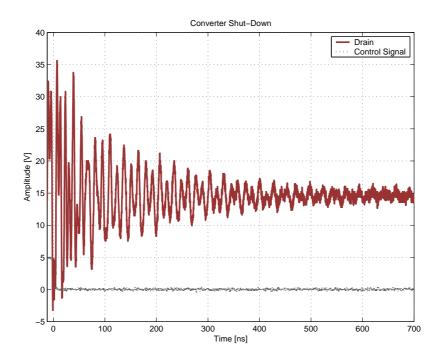

| 5.5  | Converter start-up transient                                          | 105 |

| 5.6  | Converter shut-down transient                                         | 106 |

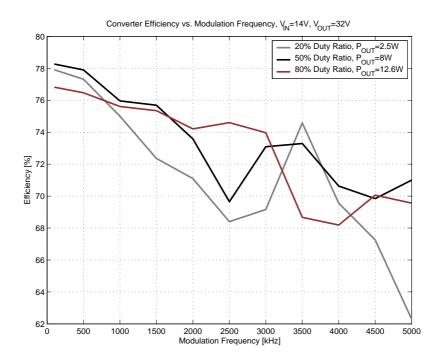

| 5.7  | Converter efficiency vs. on-off modulation                            | 107 |

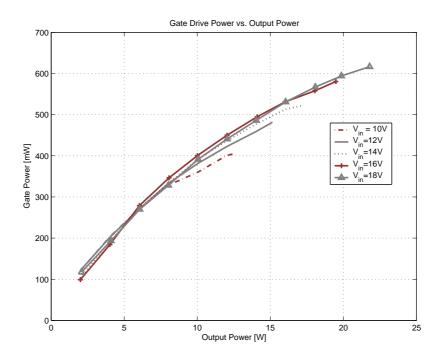

| 5.8  | Gate drive power vs. output power                                     | 108 |

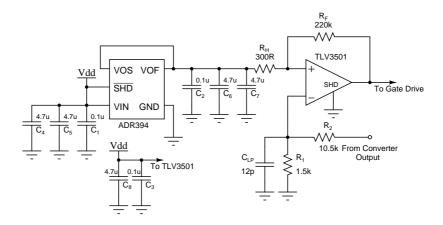

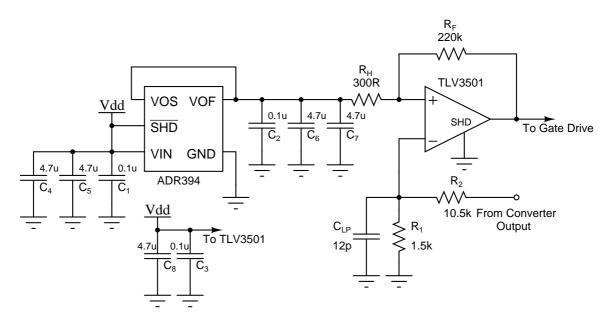

| 5.9  | Controller Schematic Diagram                                          | 109 |

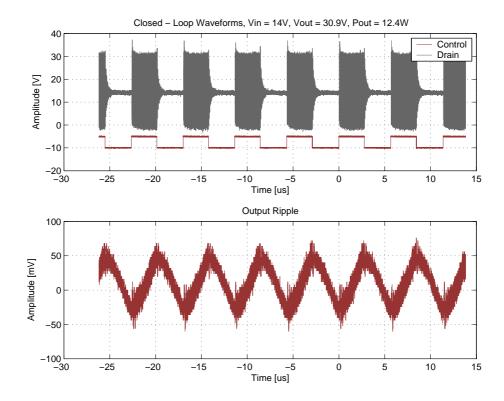

| 5.10 | Closed Loop Operation                                                 | 10  |

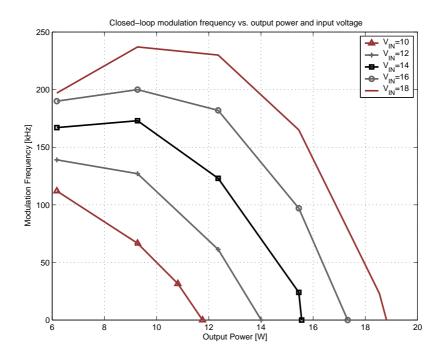

| 5.11 | Modulation frequency dependence on load and $V_{IN}$                  | 11  |

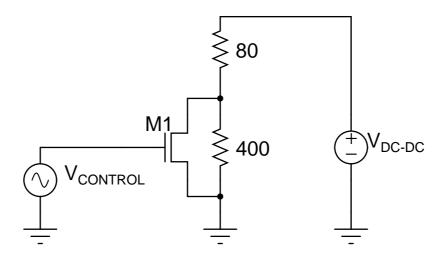

| 5.12 | Schematic of load for load-step test                                  | 11  |

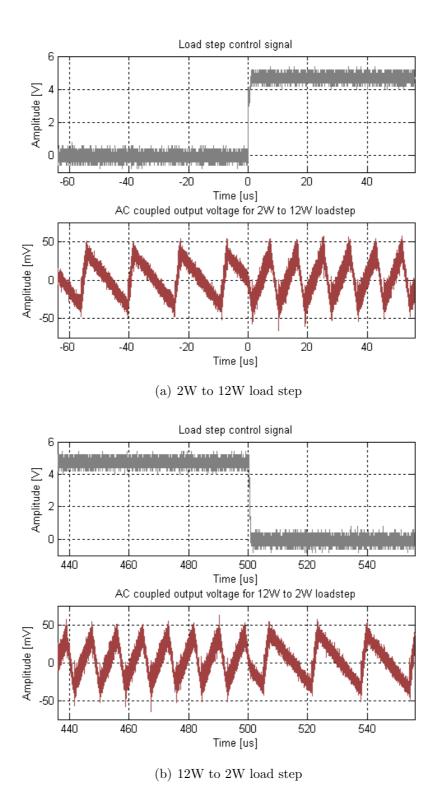

| 5.13 | Transient response to a load step                                     | 12  |

| 5.14 | Closed-loop efficiency measurements                                   | 13  |

| B.1  | Schematic of $\Phi_2$ converter with ST part                          | 159 |

| B.2  | $\Phi_2$ schematic with component values for BCD process              | 160 |

| В.3  | Complete gate drive schematic                                         | 61  |

| B.4  | Complete controller schematic                                         | 62  |

| B.5  | ST board layout masks                                                 | 163 |

| B.6  | ST board layout masks                                                 | 64  |

| B.7  | BCD board layout masks                                                | 165 |

| B.8  | BCD board layout masks                                                | 166 |

# List of Tables

| 3.1 | Phase Shift differs for the ideal and non-ideal rectifiers when input bias voltage and amplitude are adjusted separately. Opposing effects of the junction capacitance cancel for the case when both bias voltage and amplitude are adjusted simultaneously | 67  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | The components of the dc-dc converter examples are listed in this table. More detailed information including the full spice models and values of parasitic inductances may be found in appendix A                                                           | 76  |

| 4.1 | MOSFET parameters                                                                                                                                                                                                                                           | 81  |

| 4.2 | Faichild S310, 100V, 3A Schottky diode parameters                                                                                                                                                                                                           | 81  |

| 5.1 | Hard gating requires more than twice as much power for the custom MOSFET even when the larger gate drive amplitude is accounted for                                                                                                                         | 102 |

| B.1 | Component values and part numbers for ST-based $\Phi_2$ boost converter                                                                                                                                                                                     | 160 |

| B.2 | Component values and part numbers for Custom-MOSFET-based $\Phi_2$ boost converter                                                                                                                                                                          | 160 |

| В.3 | Component values and part numbers for gate drive circuit                                                                                                                                                                                                    | 161 |

| B.4 | Component values and part numbers for controller circuit                                                                                                                                                                                                    | 162 |

## Chapter 1

## Introduction

NIATURIZATION has become the pursuit of modern technology. Ubiquitous use of the term "nano-", while often cloying, underscores the importance attached to the search for the smaller. The integrated circuit stands as the benchmark to the nano-world, a stark example of how economic power can be harnessed through control of the tiny. While seedling ICs were analog circuits, the shrinking of digital systems occurred much more rapidly as a relentless march on Moore's law <sup>1</sup>. Today, a common theme in analog circuit design is the development of circuit topologies and techniques that allow the realization of traditional analog building blocks—op-amps, comparators, and the like—on the ever-shrinking CMOS processes. To the extent that more functionality can be realized by adding analog systems to a digital substrate or shrinking analog systems in general, there is money to be made. Take as an example the cellular telephone. The integration of the RF power amplifier along with a host of digital front-end signal processing has fueled the explosion of cell phone usage. While the goal is to have everything on a single chip realizing cost, reliability, performance, and functionality enhancements, some systems are challenging to integrate.

One particular area where integration remains largely a stymied endeavor is power conversion. Here, the issue centers around energy storage. Most switched mode power converters will use inductors and capacitors to fulfill the requirement. The amount of energy storage, and therefore the numerical values of the inductors and capacitors, is a function of the power processed, the switching frequency, and the details of the power processing scheme [1]. Typical converters like the boost or buck converter operating at a few tens of watts require too much energy storage to be integrated given current process constraints. While the statement may seem cavalier, consider that typical inductor and capacitor values for dc-dc converters on the scale of a few tens of watts

<sup>&</sup>lt;sup>1</sup>Moore's law is mentioned only casually here. The fact is that analog circuits require fewer devices and benefit more from larger feature sizes and the better transistor parameters they engender. Digital circuits, however, rely on massive numbers of iterated structures that switch as rapidly as possible. The result has been an emphasis on shrinking the digital transistor to improve density.

are measured in microhenries and microfarads, whereas integrated inductances and capacitances are more likely to be measured in nanohenries and picofarads. Assuming that three orders of magnitude in energy storage cannot be absorbed in an arbitrarily small volume, and that the techniques that are the subject matter of this thesis are not operating, the assertion is safe.

Typical inductors that might be realized on chip are in the range of a few 10s of nanohenries and capacitors in the 10s of picofarads. The main roadblock to achieving such small values with a conventional converter is loss. The balance of this thesis will explore converter designs intended to circumvent typical loss mechanisms in a manner compatible with integration and co-packaging.

#### 1.1 Losses in hard switched converters

A switched mode power converter constructed of ideal elements has no intrinsic loss mechanism. Rather, they arise inevitably from the use of real components. These losses, distributed among the active and passive components constrain not only the efficiency of the SMPS (switched mode power supply), but the size, cost, form-factor, and even converter responsiveness. Finding ways to beat these losses is, in a sense, tantamount to miniaturization.

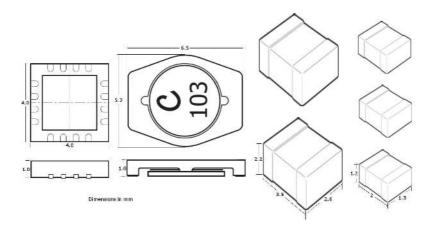

On considering a typical dc-dc converter, one fact that becomes obvious is that the bulk of the system, that is its weight and volume, comprises the passive energy storage elements. Semiconductor devices, having benefited from tremendous improvement since their inception, occupy only a small fraction of a typical converter footprint. This is made clear in figure 1.1 showing a common implementation of a synchronous buck converter where switches, gate drives, controller, startup and protection circuits, and the housekeeping power systems are integrated onto a die and placed in a QFN (quad flat-pack, no-lead) package. The remainder of the components are the energy storage devices which require roughly an additional four times the board area (not accounting for interconnect) and nearly six times the volume. It is not surprising, then, that techniques to reduce converter footprint might be aimed at minimizing or eliminating passive energy storage.

Where the goal is to reduce the size of the energy storage components, there are two primary ways to proceed. Either energy density may be increased or total converter

Figure 1.1: The synchronous buck converter components pictured will supply 7.5 W into 5 V. The QFN on the left encompasses the active switches, gate drive, control, and housekeeping functions. The remaining passive elements require 4 times the board area and 6 times the volume, not accounting for board interconnect.

energy storage reduced. Increasing the energy density implies shrinking a device for a constant amount of storage. Even if this can be accomplished, given the physical constraints imposed by power dissipation, the increased losses that result often cannot be reconciled with good converter performance. Considering a solenoidal inductor, it is demonstrated in [2] that fundamental scaling between linear dimensions and flux- or current-carrying area causes inductor Q to decrease as  $\alpha^2$  where  $\alpha < 1$ is a constant scaling each linear dimension. Similar relationships are enumerated in [3] for other geometries. In the case of capacitors, analogous problems arise. Where a given dielectric material is available, a lower bound exists on the capacitor plate separation for a set working voltage. Further, plate resistance also increases as plate thickness is decreased or plate area is increased, both are necessary to improve energy density. These conditions imply that the capacitor Q will become unacceptably low with continued scaling at a constant capacitance. Thus a host of factors — Q, dielectric breakdown, and dissipation — impose a maximum energy density on passive components. Unfortunately, practical densities leave something to be desired for converter size.

With very limited leeway to increase energy density, we turn our attention to reducing the required energy storage. The classic solution is to raise the switching frequency [1], thereby reducing the amount of energy processed per cycle, a condition that leads directly to smaller numerical values of inductance and capacitance. The buck-

Figure 1.2: In the buck-boost converter,  $L_F$  acts as temporary storage. In the first part of the cycle  $L_F$  is charged by current  $I_{CH}$  while  $C_{OUT}$  holds up the output. In the second portion of the cycle  $L_F$  discharges into the load while replenishing  $C_{OUT}$ .

boost converter in figure 1.2 is a convenient means to an explanation. The buckboost converter is an indirect converter. This type of converter transfers energy from the source to intermediate storage in the first portion of a cycle and then from intermediate storage to the load in the second portion of the cycle. The intermediate storage in the buck-boost converter is the inductor,  $L_F$ . As the switching frequency is increased and the amount of energy processed each cycle gets smaller, the numerical value of  $L_F$  can be reduced and the inductor made physically smaller for constant energy density. The same applies to the capacitors  $C_{IN}$  and  $C_{OUT}$ . For instance,  $C_{OUT}$  must hold up the output voltage during the half of the cycle when  $L_F$  is charging. The holdup time is inversely proportional to frequency as is the associated RC time constant for a constant droop in output voltage. Another way to see that  $C_{OUT}$  can be reduced is to consider that  $R_L$  and  $C_{OUT}$  form a low-pass filter which attenuates the switching ripple. As the switching frequency increases the low-pass corner frequency moves up for a given attenuation, relaxing the capacitance requirement.

Though increased switching frequency attends less energy storage, it is not a tech-

nique that may be used haphazardly: A cohort of loss mechanisms arise rapidly to place limits on the operating frequency. While not necessarily the largest of these, important frequency dependent losses in passive elements are limited almost exclusively to inductors and their magnetic materials. Most magnetic materials, used to increase inductance per unit volume, operate well at low frequency but have losses that rise rapidly otherwise. The basic trend is captured by the Steinmetz equation:

$$\overline{P_v(t)} = k f^{\alpha} B^{\beta} \tag{1.1}$$

where  $\overline{P_v(t)}$  is the time-average loss per unit volume  $[kW/m^2]$ , B is the peak ac flux amplitude [Gauss], f is the frequency of sinusoidal excitation [Hz], and the constants k,  $\alpha$ , and  $\beta$  are found by curve fitting. Examining 1.1 it is clear that for  $\alpha$  greater than one (it's often in the range of 1-3) that the loss will rise briskly with frequency. Another important implication is that the core volume may be increased to reduce the flux density, trading increased size for higher frequency—the opposite of the desired effect<sup>2</sup>. In truth, the Steinmetz equation is only valid in a narrow range of situations, primarily where the excitation is sinusoidal and relatively low frequency. At high frequencies and under the non-sinusoidal excitation typical of power converters, the losses tend to be greater than predicted in the Steinmetz model and many different modeling approaches have been undertaken to get a more accurate prediction (for instance, [4]). The upshot, however, is that most bulk magnetic materials are not suitable for operation at frequencies much higher than a few megahertz.

One way of avoiding magnetic core losses is to do away with the magnetic core. The lower energy density demands even higher operating frequencies, but to the extent that the frequency can be increased, the magnetic loss picture looks much better. For a simple air core inductor, the inductance and resistance are determined primarily by geometry and the choice of conductor. Inductor quality factor Q is:

$$Q = \frac{\omega L}{R} \tag{1.2}$$

In this simple relationship, expressing the ratio of energy stored to energy lost per

<sup>&</sup>lt;sup>2</sup>Often loss becomes the limiting factor at high frequency and flux derating is necessary to avoid excessive heat build up. Thus at high frequency cored inductors can actually get *larger*.

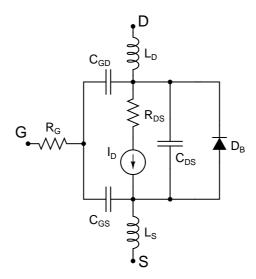

Figure 1.3: A MOSFET including parasitic elements usually important in hard switched dc-dc converter design

cycle, Q increases with reactance and decreases with resistance. The frequency dependence of R and L are very difficult to calculate for any geometry other than isolated straight wires. In general, skin effect, proximity effect, and interwinding capacitance affect both L and R [3]. If the proximity effect and the interwinding capacitance are ignored, the skin effect results in approximately a square-root increase in resistance with frequency. Since reactance rises linearly under these assumptions, then Q will increase  $\propto \sqrt{f}$ . Measurements of inductor Q and information available from manufacturers of air-core RF inductors indeed show that Q increases with frequency as a general trend.

The seemingly synergistic effect of increasing Q with frequency for air-core inductors is only advantageous provided that the other frequency dependent loss factors are dealt with. These losses are associated with active semiconductor devices. Semiconductor losses can be divided into three main mechanisms for MOSFETs: conduction loss, switching loss, and gating loss. A MOSFET model including the parasitic elements usually considered in dc-dc converter design is shown in fig. 1.3.

Conduction loss, due to the effective resistance of the channel, the lightly doped drain region (LDD), and metal/bondwire resistance, is only slightly frequency dependent<sup>3</sup>. Switching loss, however, depends significantly on frequency. It is helpful

<sup>&</sup>lt;sup>3</sup>At typical operating frequencies the quasistatic assumptions for MOSFETs are valid, so the

to further divide switching loss into overlap loss and losses resulting from discharge of the drain-source capacitance,  $C_{DS}$ . Overlap loss refers to the condition where the MOSFET supports simultaneous voltage and current at its drain-source port and thereby dissipates power. This condition arises from the need to charge or discharge the device channel through finite source impedance (whether this impedance arises externally or as a result of device parasitic resistance and inductance) which imposes a minimum on switch transition times. Simplified models of overlap loss parameterized in converter nominal voltage  $(V_O)$  and current  $(I_O)$ , and MOSFET rise  $(\tau_r)$  and fall  $(\tau_f)$  times are readily available [5, 1]:

$$E_r + E_f = kV_O I_O(\tau_r + \tau_f) \tag{1.3}$$

The constant k reflects the circuit in which the device is used and varies between 1/6 and 1/2 depending on whether the load is purely resistive or clamped inductive. Since this result is basically fixed once the device and circuit are chosen, the energy per transition  $(E_r + E_f)$  is also fixed. Therefore, as switching frequency rises, so does overlap loss.

The loss due to  $C_{DS}$  occurs at device turn on, when the energy stored on the output capacitance is dumped into the switch yielding a loss than can be roughly approximated as:  $\frac{1}{2}C_{DS}V_{DS-PK}^2f$ . This effect can be significant even at frequencies well below a megahertz— $C_{DS}$  is usually fully charged just before turn-off.

Gating loss results from charging and discharging the input capacitance,  $C_{ISS} = C_{GS} + C_{GD}$ . Calculating the gating loss is somewhat complicated by the presence of  $C_{GD}$  which is multiplied according to the Miller effect during transitions. In lateral MOSFETs where  $C_{GD}$  tends to be very small and its effects can be ignored, the gating loss is approximately expressed as:

$$P_{GATE} = C_{GS} V_{GATE_{PK}}^2 f (1.4)$$

This reflects that the loss is associated with the loss of charging a capacitor from a dc voltage through a resistor,  $\frac{1}{2}CV^2$ , and the subsequent dumping of the stored energy

channel and LDD components of  $R_{DS-ON}$  are constant. Bondwire resistance is usually a small enough component that skin effect only accounts for a small change in the total  $R_{DS-ON}$ .

once per cycle. In other types of MOSFETs, such as vertical DMOS and even some lateral devices,  $C_{GD}$  is a significant portion of  $C_{ISS}$  and the effects can't be ignored. Then the gate power is usually expressed in terms of the total charge required per cycle to enhance the device:

$$P_{GATE} = Q_G V_{GATE_{PK}} f (1.5)$$

In both cases the frequency dependence is clearly linear. This mechanism becomes important at switching frequencies of a few megahertz and beyond where gating loss for typical devices can range from hundreds of milliwatts to several watts.

Diodes also account for a fraction of the converter loss budget. All diodes have an associated forward voltage drop,  $V_F$ , that combines with the forward current,  $I_F$ , and resistive losses in the bulk regions to result in diode conduction loss. This mechanism is not explicitly frequency dependent. PN-junction diodes and PIN diodes, however, do have a frequency dependent loss mechanism - reverse recovery. Reverse recovery names the process in which stored minority carriers are removed during commutation. During the reverse recovery time,  $\tau_{RR}$ , the carriers are extracted across a constant voltage. Since this time is related to the amount of stored charge and the impedance of the external circuit,  $\tau_{RR}$  is fixed for a given configuration. Therefore, the energy wasted per cycle to reverse recovery is constant implying frequency dependence. Schottky diodes, which are formed as metal-semiconductor junctions are majority carrier devices. They do not suffer heavily from reverse recovery losses, but are only available with breakdown voltages below about 120 volts.

#### 1.2 Resonant Power Conversion

Resonance, usually ascribed to systems with complex poles displaying oscillatory behavior, is of some significance in power conversion. In filtering, for example, it plays a role to develop large immitance in comparatively little volume<sup>4</sup>. Here we look at resonance as a means to push back converter loss mechanisms and realize operation

<sup>&</sup>lt;sup>4</sup>Series and parallel resonant filters can be used to shunt or block ripple in power converters. It was demonstrated in [6] that by using resonance, filter element volume could be reduced by better than a factor of three.

Figure 1.4: Resonant topologies often suffer from limited load range in power conversion applications. Here, the Class E inverter waveforms are pictured as the load is varied from  $\frac{1}{2}R$  to 2R. The properly tuned waveform is displayed in heavy black. The loss of ZVS and negative impact on efficiency are evident.

in the very high frequency regime (VHF, 30 MHz - 300 MHz).

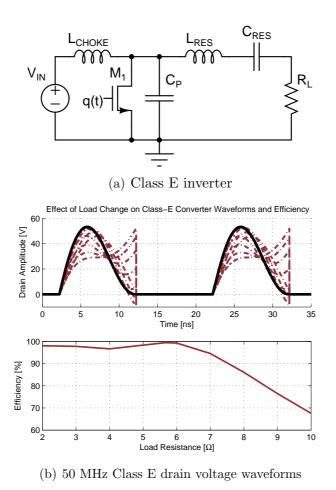

A number of converter topologies exist that draw from RF amplifier techniques to achieve efficient energy conversion [7, 8, 9, 10, 11, 12, 13, 14, 15] at high frequencies. These designs rely on reactive networks to shape the switch voltage and current and reduce switching loss. The class E converter, fig. 1.4(a), is a widely practiced topology whose network enforces a zero-voltage switching (ZVS) opportunity at turn-on. Its basic operation can be classified as indirect. The inductor  $L_{CHOKE}$  is an open at the switching frequency, ensuring that only dc current flows from the source. With no dc path to the load, energy from the source must first be stored on the switch shunt

Figure 1.5: Schematic depiction of VHF converter under on-off modulation. The closed-loop system keeps output voltage constant allowing the converter to deliver a constant power (effectively it sees a constant load) at it's most efficient point. Actual power delivered to the load depends on the duty ratio of the control signal.

capacitor  $C_P$ . The energy stored in  $C_P$  then rings towards the load in a cycle that is determined by the switching function, q(t), and the resonant tank formed by the load,  $L_{RES}$ , and  $C_{RES}$ . It functions by ringing the energy on  $C_{DS}$  to the load once per cycle. When these components are tuned according to [7, 8], the drain voltage will naturally return to zero as the energy in  $C_P$  rings toward the load. At this point, the switch may be turned on with minimal loss. This mode of operation avoids the losses usually ascribed to the switch drain-source capacitance and largely avoids overlap loss, as well.

In practice, the drawbacks of such resonant topologies have prevented them from seeing widespread use. To begin with, the load range is severely restricted when compared with the 100:1 or better range achievable with conventional converters. Resonating losses from circulating reactive currents become significant as the load is reduced, hurting efficiency. The situation is made worse in the many cases where the load is an integral part of the resonance. Then, any change in load disrupts the ZVS condition and switching loss inevitably arises. This situation is depicted in fig. 1.4(b). Further difficulty arises because duty ratio control is often not possible. Instead, control is achieved by varying the switching frequency. The resulting poor dynamics worsen with frequency and place an artificial upper bound on practically achievable switching speed. Many resonant converters also suffer from high peak switch stresses. The class E converter, in particular, has peak drain voltages rising as high as 4.4 times the dc input voltage [16]. This is particularly troublesome where integration is concerned because integrated devices tend to have lower breakdown

voltages.

Several of these issues can be resolved by partitioning the energy storage and control functions [17, 18, 19]. Instead of controlling the output by varying the switching frequency, on-off modulation of the converter determines the fraction of output power delivered (see fig. 1.5). When the converter is on, it delivers a fixed power maintaining ZVS and maximum efficiency. When off, no power is delivered and there are no associated resonating losses. Under these conditions the load range is a function of the minimum achievable modulation index. Such operation allows the network to be tuned to enforce ZVS at one particular operating point. The result is maximum efficiency, better dynamics, and higher achievable operating frequency. The fact that this mode of operation allows much higher switching frequency is self-reinforcing—high frequency means less energy storage so the converter can be started and stopped more rapidly and achieve a wider load range.

## 1.3 Contributions and Organization of the Thesis

Raising the switching frequency is a well known means of reducing required energy storage in power converters. It is precisely this reduction that can put inductor and capacitor values into the range that they might be considered for integration. For inductors, in particular, VHF operation allows magnetic materials to be set aside, avoiding the difficulty and expense of incorporating them on chip. Even so, it is not clear that current techniques, like the planar spiral inductor, can offer high enough Q or reasonable area. Generally, integrated inductors achieve Q's of ten or below with inductance in the neighborhood of 10-20 nH [20, 21]. While the techniques discussed in this thesis result in small value inductors, the Q needs to be at least 50 or better. Capacitors are also a challenge. Typical CMOS processes achieve about 1  $fF/\mu m^2$  metal to metal capacitance. Higher density requires the use of inherently non-linear (and potentially lossy) gate capacitance. Yet these considerations are secondary to the question of whether or not devices available on the existing power processes are suitable to high frequency operation. The exploration and development of techniques that permit this answer to be "yes" is the primary contribution of this thesis.

Breakdown voltage is a key aspect in determining integrated process suitability. While adopting resonant circuit techniques permits low loss and high frequency, it also poses very high switch stresses. The class E converter, for instance, has an idealized peak

voltage stress of 3.6 ranging up to 4.4 in practice. Since integrated processes do not enjoy the luxury of high breakdown voltage, attempting to implement a topology like the class E would significantly limit the input voltage range. Some RF amplifiers like the class F are able to reduce the peak stress by waveshaping [22, 23, 24], but at the expense of relatively high component count. In chapter 2 a new inverter we call class  $\Phi_2$  is introduced along with a tuning method that permits low peak voltage stress. The low voltage stress achieved (2 in simulation, 2.4 in experiment) is critical to implementing a converter with an input voltage up to 18 V on a 50 V power process, which for instance is not possible with a class E topology. The  $\Phi_2$  also has a low component count and eliminates the need for an RF choke. With the few inductors resonant and small, the  $\Phi_2$  has excellent dynamics and makes a good candidate for integration.

Efficient rectification compatible with integration is introduced alongside the  $\Phi_2$  dc-dc converter in chapter 3. Many resonant rectifier topologies exist for RF inverters [13, 25, 26, 27, 28]. The particular topology set forth here offers a low component count. When mated with the inverter the result is a resonant boost converter that transfers power at ac and dc. The dc portion varies with the boost ratio and is advantageous because it does not suffer resonating losses. Almost all the power delivered at ac is delivered at the fundamental, where the rectifier is tuned to appear resistive. Significantly, the rectifier tuning changes with the dc input voltage causing the output power to vary nearly linearly with input voltage. Though this complicates design, it offers an additional degree of freedom to tailor the desired converter behavior.

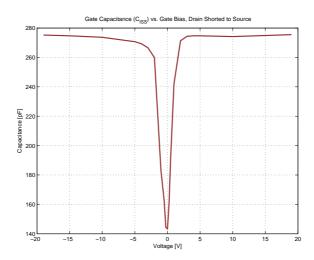

Device characterization and selection are critical. At VHF frequencies, the parasitic components must be embraced rather than avoided. This is a key strength of the  $\Phi_2$ , which can absorb the switch output capacitance as part of the wave shaping network. Both the magnitudes and distribution of the parasitic capacitance, inductance, and resistance are important considerations. Chapter 3 also discusses these particular aspects, and lays out the techniques used in measuring and modeling them.

Chapter 4 presents the design and experimental results of two dc-dc converter power stages. The first converter uses an off-the-shelf power LDMOS normally used in RF power amplifiers. The other converter uses an LDMOS device fabricated in a conventional silicon power process. Comparisons between the converters are drawn that help illustrate the effects of different tuning choices at design time.

The gate drive and closed-loop performance are discussed in chapter 5. In the VHF

regime the gate drive is not a trivial ancillary issue. Hard gating with a totem-pole driver is out of the question. Even ignoring direct path losses in such a circuit, hard gating loss is too high. For that reason a resonant design was employed. The two key factors for a gate drive in this architecture are efficiency and startup time. Resonant schemes will naturally benefit over hard gating where efficiency is considered because some portion of the gate energy is recovered each cycle. On the other hand, direct control of duty ratio and dynamic response are compromised. A topology and specific tuning techniques are discussed that attempt to find the best trade offs.

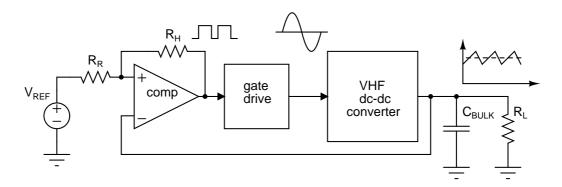

Closed-loop performance is a prerequisite for having a converter, per se. In chapter 5 a voltage-mode hysteretic controller closes the loop. The hysteresis band determines the converter peak to peak voltage ripple. A bulk capacitance in conjunction with the load sets the modulation frequency limits. Dynamic performance is excellent as the bandwidth is determined not by the modulation frequency, but by the delay through the controller and the power stage dynamics, both of which are much faster.

Resonant power conversion with the  $\Phi_2$  resonant boost converter can be accomplished with transistors built from a standard power process. VHF frequencies keep energy storage at a minimum yielding small component values and excellent dynamic performance. This and a discussion of future directions for related work are presented in chapter 6, the conclusion.

## Chapter 2

# The $\Phi_2$ Inverter

HAPTER 1 laid out the basic considerations for conversion at VHF switching frequencies and the attendant miniaturization advantages. While resonant conversion techniques are compelling in this regard, several key aspects make them difficult to integrate. At the top of the list is peak switch voltage stress. In practical implementations of the class E converter, for instance, the main switch must endure peak voltages up to 4.4 times the input voltage. This alone is enough to break an integrated implementation. Designs like the class F converter use wave shaping techniques to reduce the switch stress, but the result is a large component count. Many such converters also suffer from the need for a bulk inductor to function as an rf choke at the input. This limits dynamic performance and poses yet another challenge to integration. While variants like the second harmonic class E converter avoid this problem, no topology yet presented offers the combination of low switch stress, low component count, and minimal energy storage. Such a converter does exist and it is called the  $\Phi_2$  converter.

### 2.1 The class $\Phi$ Inverter

As an aid to our understanding of the  $\Phi_2$  inverter's operation, we briefly digress to examine its progenitor, the class  $\Phi$  inverter [2, 24]. This inverter exploits the symmetrizing properties of a shorted quarter-wave transmission line in order to realize efficient high frequency conversion. The impedance characteristic of such a line is plotted in fig. 2.1 where the poles appear at the odd integral multiples of the fundamental and zeros obtain at the even integral multiples. The symmetrizing properties are exposed naturally on considering the effect of driving the line with a finite-impedance voltage source periodic in the fundamental. High impedance at the odd harmonics blocks current, permitting the source to impress odd harmonic voltages without ef-

Figure 2.1: Impedance characteristic of a shorted quarter-wave transmission line.

fort. The situation is reversed for even harmonics—the line demands large currents, nulling the source voltage. Under these conditions the periodic steady state voltage at the driven port of the line will consist exclusively of odd harmonic components and the current even harmonic components. The signals will then be half-wave symmetric and half-wave repeating respectively, a fundamental result of Fourier analysis. By way of illustration, two signals are constructed with arbitrary combinations of even and odd components in fig. 2.2. In each plot the sum is depicted by the heavy line. The sum in the top plot, composed exclusively of odd components is half-wave symmetric. In the bottom plot, the even components result in a half-wave repeating sum.

The  $\Phi$  inverter, fig. 2.3(a), consists of a shorted quarter-wave transmission line terminating at the drain-source port of its switch and a resonant output tank. While the quarter-wave line enforces drain voltage symmetry in periodic steady state, it is the interaction of the tank with the shunt capacitance,  $C_P$  (usually device parasitic capacitance, although external shunt capacitance may be added), that ultimately

Figure 2.2: Half-wave symmetric and half-wave repeating waveforms.

creates ZVS and high efficiency. Considering the waveforms in fig. 2.3(b) the drain voltage is clearly half-wave symmetric. It has a dc average component equal to the source voltage, a condition of achieving periodic steady state, which also serves as the axis of symmetry. The switch holds the drain node at ground for a portion of the cycle defined by q(t). When the switch turns off, the line current falls abruptly to zero and the load current charges  $C_P$  to the peak drain voltage,  $2V_{IN}$ , a value that results from reflection about the DC average<sup>1</sup>. Once  $C_P$  has charged to  $2V_{IN}$ , the line current again equals the load current, and the drain voltage remains constant. After a period equal to the switch on-time, the line current falls to zero and the load current discharges  $C_P$ , ringing the drain to zero and creating an opportunity for the switch to turn on without loss.

It is important to note that the symmetry in drain voltage does not guarantee ZVS. For instance the waveforms in fig. 2.4 show what would happen if the value of  $C_P$  is halved. The load network draws too much charge out of the capacitor and the

<sup>&</sup>lt;sup>1</sup>One can also consider that the switch effectively launches a voltage wave of  $-V_{IN}$  down the line which must return a half cycle later inverted to satisfy the boundary conditions established by the short. With a dc average of  $V_{IN}$  the additional  $V_{IN}$  from the returning wave adds to the peak voltage,  $2V_{IN}$ .

Figure 2.3: The class  $\Phi$  inverter tuned for soft switching at 50 MHz. The shorted quarter-wave line ensures the drain voltage is half-wave symmetric. The rising and falling edges of the drain voltage are due to the charging and discharging of  $C_p$  each cycle by the difference between  $i_{line}$  and  $i_{load}$ . Important to note is that the ZVS condition is not guaranteed by half-wave symmetric voltage alone. The load network and switch capacitance must interact so that the drain voltage reaches zero at the appropriate moment. See appendix A for component values and simulation files.

Figure 2.4: In the  $\Phi$  inverter, the transmission line enforces half-wave symmetry. When the load network and shunt capacitance  $C_P$  are unmatched, loss results at both transitions. Component values and simulation files can be found in appendix A

drain voltage undershoots zero. The symmetry enforced by the line then causes a corresponding overshoot one half-cycle later. This operating condition forces the switch to dissipate energy from the capacitor each half-cycle, a lossy proposition.

Limits on power delivered to the load at a given  $C_P$ , frequency, and input voltage naturally arise where all the energy stored on  $C_P$  must come from the load side. In steady state, the load current must be exactly the right value to ring the drain to zero. Once the duty ratio has been constrained, the tank current is fixed, and so is the output power because the load resistance necessarily plays a role in determining the tank current. Since  $C_P$  is smallest when composed exclusively of device parasitic capacitance, there is a minimum power delivered to the load for a given switch, switching frequency, and input voltage. The  $\Phi_2$  inverter, having the ability to absorb device capacitance into either the load network or its source network has greater freedom in this regard.

### 2.2 The class $\Phi_2$ Inverter

The class  $\Phi_2$  inverter, like the  $\Phi$  inverter, exploits waveshaping techniques to realize approximate half-wave symmetry and the related benefits. It diverges on the point of how many harmonic-coincident resonances are employed to achieve the effect. Where the ideal  $\Phi$  inverter relies on an infinite number of harmonics, the  $\Phi_2$  network seeks to control only the first three. The resulting *approximate* half-wave symmetry reaps

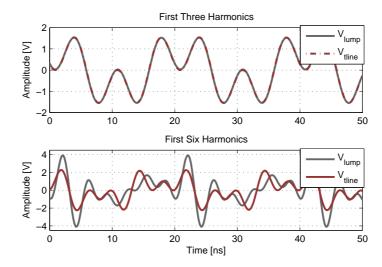

Figure 2.5: The impedance of the  $\Phi_2$  input network can approximate a shorted quarter-wave transmission line.

the rewards of ZVS yet allows greater flexibility in establishing the details of the waveform shape while avoiding need for many resonant elements. Key to meeting the requirements of integration, this flexibility also comes with reduced design complexity. Practical implementations of the class  $\Phi$  inverter control perhaps a dozen harmonics [2, 24]. The associated multi-resonant structures require significant design effort, are sensitive to process variation, and difficult to change. In contrast, the  $\Phi_2$  inverter's low-order lumped network can be readily tuned to establish a desired impedance, reducing the design effort.

For instance, the lumped network depicted in fig. 2.5 has an impedance characteristic that is identical to that of the shorted quarter-wave transmission line for the first three harmonics. When the component values are selected according to eqns. 2.1 the poles occur at the fundamental and third harmonic with a second harmonic zero.

$$L_F = \frac{1}{9\pi^2 f_{SW}^2 C_F}$$

$L_{2F} = \frac{1}{15\pi^2 f_{SW}^2 C_F}$   $C_{2F} = \frac{15}{16} C_F$  (2.1)

This network can be viewed as a parallel combination of series- and parallel-resonant tanks. The series tank,  $L_{2F}$  and  $C_{2F}$ , is tuned to the second harmonic, creating the zero. The inductor  $L_F$  in the parallel tank provides the low-frequency asymptote and resonates with the other elements to create the peak at the fundamental, and the capacitor  $C_F$  provides the high-frequency asymptote resonating with the other elements to create the peak at the third harmonic.

The addition of a parallel switch and an output tank comprised of  $R_L$ ,  $C_{RES}$ , and  $L_{RES}$  in fig. 2.6 establishes the complete  $\Phi_2$  inverter. Here the transmission line of

Figure 2.6: The  $\Phi_2$  Inverter.

the  $\Phi$  inverter is replaced by the lumped network of fig. 2.5(a).  $C_F$  becomes the switch capacitance plus any shunt capacitance added at design time. The output "tank" can be dealt with in several ways. Used as a resonant tank, it may be tuned to look resistive at the fundamental or slightly inductive to aid switching (it could be tuned to look capacitive, but greater circulating currents exacerbate loss). As an alternative, the capacitor  $C_{RES}$  can act as a dc block while  $L_{RES}$  and  $R_L$  function as an impedance divider to control load power.

### 2.2.1 Basic Operating Principles

In the  $\Phi_2$  inverter we have a network with a second harmonic short, and high impedance at the fundamental and third harmonic. Ignoring, for the moment, higher frequency content, the network will support predominantly odd harmonic voltages (fundamental and third) thus sharing the same half-wave symmetric properties as the  $\Phi$  inverter. Each cycle the switch forces the drain voltage to zero for a period DT, where D is the duty ratio. At turn off the network rings to roughly twice the dc average voltage at the drain,  $2 \cdot V_{IN}$ , before heading towards zero and the beginning of the next cycle. Under these conditions, zero voltage switching permits efficient operation.

The simulated waveforms in figure 2.7 indicate the true operation is more complicated. The drain voltage peak is not the mirror-image plateau of the  $\Phi$  inverter. Instead, telltale humps arise as they must where the harmonic content is limited. Half-wave symmetry is exposed as approximate by the same, indicating that some even order

Figure 2.7: The  $\Phi_2$  inverter tuned for operation at 50MHz. The drain voltage displays only approximate half-wave symmetry because the network only controls the first few harmonics. Notice that the switch current is substantially similar to that of the  $\Phi$  inverter (fig. 2.3(b)), but the other currents depart creating the telltale  $\Phi_2$  humps. Component values and simulation files are in appendix A

Figure 2.8: In the top plot both an ideal quarter-wave transmission line and the lumped network process the first three harmonics identically. When higher frequency content is added at equal power, the behaviors diverge. The transmission line still enforces half-wave symmetry, but the lumped circuit does not.

harmonics play a role in determining the drain waveform. Nevertheless, the system's behavior is within a stone's throw of what might be expected: there is *approximate* half-wave symmetry.

Figure 2.8 shows how the  $\Phi_2$  input network and a shorted quarter-wave transmission line compare in handling signals of differing harmonic content. When the drive current is composed solely of the first three harmonics, all equal in amplitude, the resulting voltage is exactly half-wave symmetric just as the shorted quarter-wave transmission line case. When equal amplitude components of the first six harmonics are applied, the response differs substantially from the ideal line. If the assumption of approximate half-wave symmetry is to be valid, most of the energy in the drive signal must be in the first few harmonics.

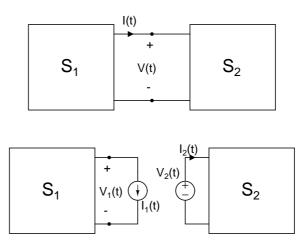

A useful way to define a drive signal in the  $\Phi_2$  inverter is found in methods commonly associated with the harmonic balance technique [29]. The harmonic balance technique, used as a computationally-lightweight means of solving for the steady state response, relies on separating a circuit into a minimum set of linear and nonlinear subcircuits. By then splitting the subcircuits at their common terminals and augmenting them with independent sources, each source can made to produce a drive signal where all the terminal variables are consistent (by means of an optimization

Figure 2.9: Splitting a circuit into two subcircuits.

Figure 2.10:  $\Phi_2$  inverter broken down into subnetworks. The network on the left hand side of figure (b) is the complete drain-source network with drain-source impedance  $Z_{AB}$ . The MOSFET is replaced by a linear independent current source, I(t).

algorithm, for instance), at which point the solution is known. For example, figure 2.9 depicts a circuit consisting of two sub-circuits,  $S_1$  and  $S_2$  that share the variables V(t) and I(t) at their terminals. The network is split as illustrated, where  $S_1$  now has a drive current  $I_1(t)$  and  $S_2$  a drive voltage  $V_2(t)$ . If a unique solution exists among the branch variables of the sub-circuits, when  $I_1(t) = I(t)$  and  $V_2(t) = V(t)$ , then  $I_1(t) = I_2(t) = I(t)$  and  $V_1(t) = V_2(t) = V(t)$ . This amounts to the substitution of sources for subcircuits. In the case where a complete circuit is nonlinear, that portion can be replaced with a linear source and the resulting subcircuit is linear.

When this technique is applied to the  $\Phi_2$  inverter in fig. 2.10, the obvious choice for the nonlinear sub-circuit is the only non-linear element, the MOSFET, outlined in fig 2.10(a). The balance of the circuit forms a completely linear sub-network shown as

$S_{L1}$  in fig. 2.10(b). With the drain voltage as the dependent variable, an independent source I(t) is chosen to augment  $S_{L1}$ . It is evident that this I(t) is the switch current, what remains is to determine its harmonic content.

The harmonic balance technique does not require that the switch is substituted with a current source. A voltage source is equally valid and a convenient means of establishing what I(t) might look like in the frequency domain. Three of the circuit branches contain series inductors and naturally shape a current signal with tapering high-frequency content. Even for a square-wave voltage source equal to the duty ratio (the worst case physically significant source in terms of frequency content) these branches will shape a current with diminishing signal energy above the third harmonic. The capacitor  $C_F$  has an impedance that falls with frequency and will tend to contribute to higher order harmonic currents. However, in any real system the switch will have a finite commutation time, limiting the frequency content. Further, while  $C_F$  may have significant current at higher frequencies, the voltage will be small due to low impedance. The current I(t) is then the sum of the frequency components of the four branch currents. With a network impedance as described above, having a zero at the second harmonic and falling monotonically above the third, the drain voltage bears out the desired characteristics—dominantly fundamental and third harmonic content and approximate half-wave symmetry.

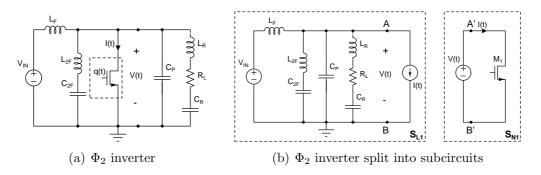

A time-domain view of the  $\Phi_2$  inverter can also be useful. When the switch is opened, the network is identical to  $S_{L1}$  (minus the current source I(t)). Upon switch closure,  $C_P$  is replaced by a short circuit. In each case, the final state of the circuit at the switch transition is passed on as the initial conditions for the next portion of the switching cycle. In periodic steady-state, the switch cycles on to conduct a ramping current through  $L_F$ , the returning load current through  $L_{RES}$ , and current from the second harmonic tank. As the switch opens, the initial conditions established by these currents, along with energy from  $V_{IN}$  causes the network to ring at its modal frequencies, charging and then discharging  $C_P$ . The result is the  $\Phi_2$  drain voltage waveform. In figure 2.11 the complete response of this ringing is identical to the simulated drain voltage waveform for a period (1-D)T, at which point the switch is cycled on to reestablish the initial conditions. The zero-state and zero-input responses in the plot show how stored energy and energy from the source,  $V_{IN}$  contribute to the ringing.

At present, determining the exact component values (whether from time or frequency domain considerations) resulting in zero-voltage, zero dv/dt switching requires nu-

Figure 2.11:  $\Phi_2$  network complete response generated by capturing the initial conditions of each state variable in the circuit of fig 2.6 just before the switch opens. The waveforms are identical over the period the switch is off. Just before departure, the switch closes, reestablishing the initial conditions for the next cycle. Component values and simulation files can be found in appendix A

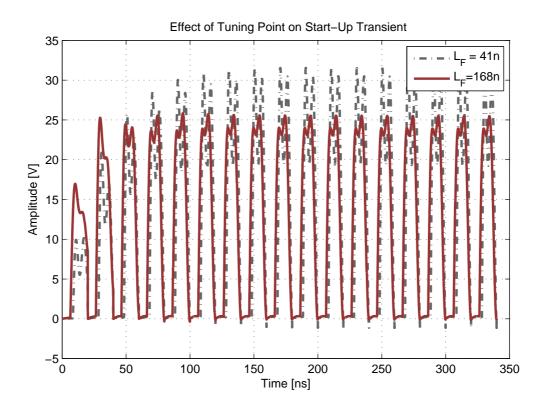

merical simulation. Great flexibility results from the many tuning solutions given a desired output power, switching frequency, and duty ratio. For instance, selecting the appropriate impedance curve and duty ratio adjusts peak voltage. Aside from allowing the use of lower-voltage processes, the RMS values of switch conduction and displacement currents change. Depending on the particular switch process, geometry, and switching frequency this is a significant tradeoff. Likewise, where inductor values are concerned, a range of characteristic impedances are achievable, and for a given load selection of these components influences efficiency. In fact, assuming a fixed inductor Q, load, and switch, an optimum characteristic impedance exists. Yet another factor, transient performance, is related to total energy storage.

In a real inverter, the switch non-linearities complicate tuning, pushing an exact solution ever further from reach. While a blind parameter sweep in SPICE will arrive at a working design, a more informed method is desirable. The approach taken here is to tune the inverter to a rough operating point using its impedance characteristics. The final design, when nonlinear elements are included, is achieved by tweaking component values based on a knowledge of the their specific impact on inverter behavior.

### 2.2.2 Tuning the $\Phi_2$ Inverter

Inverter tuning begins with the notion of approximate half-wave symmetry. While the  $\Phi_2$  input network of fig. 2.5(a) can be tuned to have peak immitances at the first three harmonics, this does not result in zero voltage switching. The presence of higher frequency harmonics, both even and odd, requires adjustment to the network in order to achieve ZVS. The load also affects tuning making the total drain-source impedance,  $Z_{AB}$ , from fig. 2.10(b) the parameter of interest. By controlling this impedance it is possible to tune the inverter over a wide range of operating points.

With a drain voltage signal that is necessarily periodic, the continuum of  $Z_{AB}$  can be largely ignored for tuning purposes. Rather, in as much as the drain voltage and switch current can be represented as Fourier series, the discrete points at each harmonic determine inverter operation. Thus the network need not have modal frequencies at the harmonics. Instead, the magnitude and phase of the network impedance at each harmonic, and more specifically at the fundamental and third harmonics, determine the operational characteristics. This assumes that there is a zero at the second harmonic. While it is possible to achieve ZVS and zero dv/dt when the zero is only near the second harmonic, it is not necessarily desired. Over the range of tuning points explored, pinning the second harmonic with a zero obtains the lowest peak voltages for a given RMS conduction current proving beneficial to efficiency.

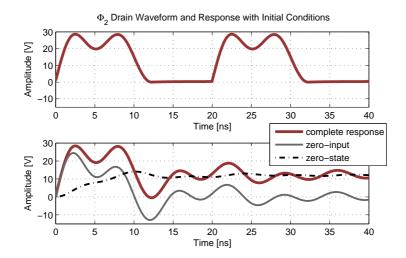

It is useful to think of the drain waveform as its Fourier series. Temporarily ignoring higher frequencies, and remembering that the drain voltage should have no second harmonic component, the signal is composed of a fundamental and its third harmonic along with a dc offset equal to  $V_{IN}$ . The shape is strictly related to the magnitudes and phases of just these two components. In the top plot of fig. 2.12 a simulated  $\Phi_2$  drain waveform is compared with the sum of its fundamental and third harmonics. It is evident that while not exact, the approximation is reasonable. Immediately below, a series of signals constructed with the fundamental and its third harmonic component with zero phase offset is plotted. For each curve, the magnitude of the third harmonic has been varied resulting in larger peaks as the ratio of the third harmonic component increases. If these curves were to represent  $\Phi_2$  drain waveforms, the switch should be on between the close trough-pairs and off between the more distant pairs, as depicted by the notional gate waveforms. This implies that the required duty ratio (for ZVS) and the ratio between the fundamental and its third harmonic is related, a reasonable result. If the drain waveform was purely fundamental the required duty ratio would

Figure 2.12: The  $\Phi_2$  inverter drain waveform is primarily composed of a fundamental and its third harmonic component as evidenced by the close match in the top plot. The ratio of these components partially determines the duty ratio necessary to achieve ZVS; waveforms with less third harmonic require a lower duty ratio. The pulse trains represent the necessary switching function, the actual value is affected by the presence of higher frequency components, but still follows the general trend.

be zero. For a drain waveform of purely third harmonic the duty ratio is close to 66%. These extremes are not desirable. Achievable duty ratios range perhaps from 0.2 - 0.5. Within this range we find acceptable ZVS operation and gate drive requirements that are not too severe.

The duty ratio is not solely related to the magnitudes of the harmonics, phase offset (primarily between the fundamental and third harmonics) plays a role. Though it adds another degree of freedom, keeping the phase offset near zero results in the lowest peak voltage and more symmetrical waveforms. Higher frequency components in the drain waveform also complicate matters. Clearly the construction of fig. 2.12 does not have ZVS when just the first three harmonics are considered. It is possible, however, to achieve ZVS by an appropriate adjustment to the network impedance.

The resulting magnitude, phase offset, and duty ratio attain slightly different values than otherwise predicted. These values may be divined in a numerical simulator like SPICE and remain valid at various values of characteristic impedance<sup>2</sup>, a fact useful when optimizing efficiency, for instance.

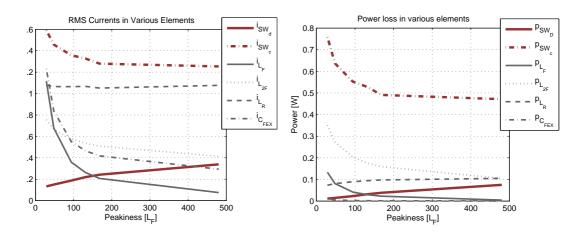

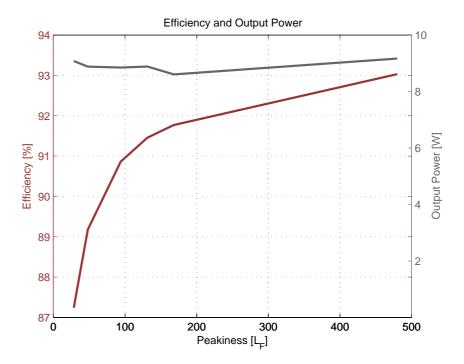

Tuning the  $\Phi_2$  inverter brings to light an array of possible tuning points. Here we consider two main aspects related to the shape of the drain voltage waveform and the drain-source impedance. First, depending on the component values selected, the peak drain voltage can range from just under  $2 \cdot V_{IN}$  to greater than  $4 \cdot V_{IN}$ . The "peakiness" is a very important factor where device breakdown is concerned. In particular, integrated devices tend to have lower breakdown voltages than discrete components, and a factor of two in peak voltage can determine whether or not a design is achievable in a given process. The other issue of primary importance is the characteristic impedance of the network. This can be adjusted up or down within a range while the peak voltage remains constant. The effect is to change the damping of the network. In so doing the resonating losses change, typically reaching a minimum and then increasing as characteristic impedance is further decreased. Component values also change significantly, inductors shrink and capacitors get larger as impedance is lowered. This can be exploited in co-packaging or integrated environments where volume is at a premium. Since capacitors scale better than inductors in terms of Q, trading higher Q capacitance for lower Q inductance is often advantageous where very small size is desired.

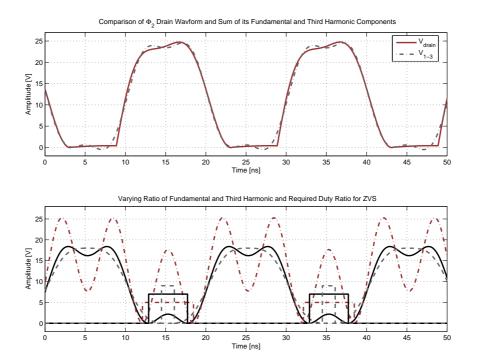

Turning first to the question of peakiness highlights a useful relationship mentioned earlier. That is, the peak drain voltage is largely determined by the ratio of the fundamental and third harmonic magnitudes. The more third harmonic present in the drain voltage waveform, the higher the peak voltage for a given  $V_{IN}$ . In turn, the voltage magnitude ratio is roughly dependent on the drain-source impedance magnitude ratio,  $Z_{AB}$ , at the respective harmonics. Lowering the impedance at the third harmonic relative to the fundamental decreases the peak drain voltage because the impedance decreases faster than the rising drive currents. Further, the impedance relationships among the harmonics are deterministic. If the phase at the fundamental and the magnitude ratio between the fundamental and its third harmonic are held

$<sup>^2</sup>$ The term characteristic impedance is used somewhat loosely here, being only strictly defined for a second order system. In general, in this section it refers to shifting the impedance magnitude up or down, usually by picking the characteristic impedance of the second harmonic leg—where it is well defined—and then reestablishing the magnitude-phase relationships at the fundamental and third harmonics necessary for ZVS.

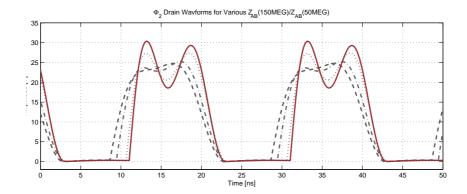

constant, the converter will exhibit the same drain waveform characteristics (i.e. peak voltage and overall shape) for a given duty ratio. It is here that a potential design algorithm begins to emerge. If a set of magnitudes and phases are known that yield acceptable ZVS operation, an impedance curve can be fit that produces a functional converter. While numerical simulation is still required to derive a given set of values, it is rather straight forward to subsequently walk along the locus of solutions and achieve flatter and flatter waveforms. This is precisely the result presented in figure 2.13. After a favorable tuning point is found the converter can be re-tuned by varying only two components,  $L_F$  and  $C_F$ . This does not imply that the other components cannot be varied, rather varying  $L_F$  and  $C_F$  is an effective means of tracing out solutions that achieve different ratios of fundamental and third harmonic.

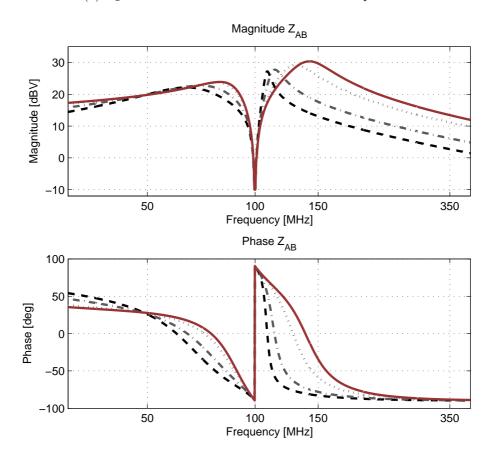

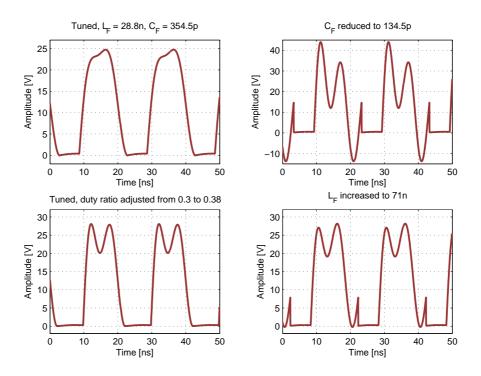

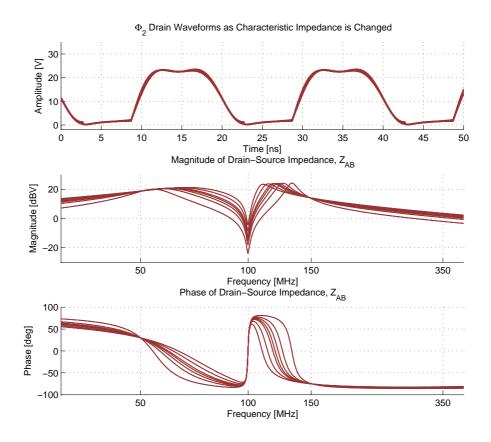

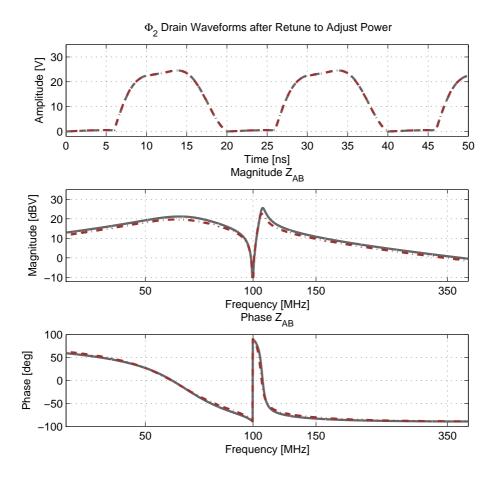

The procedure is demonstrated in fig. 2.14 starting with a tuned inverter at the top left and proceeding clockwise. The waveform in the first plot exhibits ZVS and zero dv/dt characteristics. In the second plot, the capacitor,  $C_F$  has been decreased significantly to increase the level of third harmonic.  $L_F$  is then subsequently increased until the drain waveform just reaches zero dv/dt at zero voltage. In the final plot, the duty ratio has been adjusted (and some slight iteration performed) to get ZVS, zero dv/dt waveforms. The component values and impedance curve that realize the resulting drain waveform are by no means unique. However, the impedance phase at the fundamental and magnitude ratio between the fundamental and third harmonic along with the duty ratio constitute a set of values that when reproduced result in a properly tuned  $\Phi_2$  inverter. This remains true even as the balance of the impedance curve varies over a wide range. As much is shown in the plots of fig. 2.15. Starting with a tuned inverter, the characteristic impedance of the second harmonic tank is varied. Adjusting  $C_F$  and  $L_F$  reestablishes the desired impedance conditions. The result is a set of identical drain waveforms delivering constant power to the load, yet with a circuit that has widely differing component values.

That constant load power is achieved should come as no surprise. For a given drain voltage the current in the load leg (formed by  $L_R$ ,  $R_L$ , and  $C_R$ ) is fixed. It was demonstrated in [19] that when the drain waveform is known, the power may be estimated by assuming most is delivered at the fundamental. Further approximating the drain as a square wave gives a reasonable estimate of the fundamental amplitude. The load power may then be directly calculated. Changing the load to modulate power, however, necessarily affects  $Z_{AB}$ , ruining ZVS. Retuning then affects the desired load power and iteration is necessary. This dependency can be unwound by using the impedance transfer function (eqn. 2.2) to calculate the required component changes.

(a)  $\Phi_2$  drain waveforms obtained at different impedances

(b)  $\Phi_2$  drain source impedance,  $Z_{AB}$ , realizing waveforms of fig. (a)

Figure 2.13: The drain-source impedance controls the magnitude of fundamental and third harmonic that appears in the drain voltage waveform. Lower drain-source impedance,  $Z_{AB}$  at the third harmonic relative to the fundamental results in flatter waveforms. This is useful in meeting peak voltage stress requirements and minimizing loss. Component values and simulation files may be found in appendix A -47 –

Figure 2.14: Tuning sequence to increase drain waveform third harmonic component and reduce overall circulating currents. Component values and simulation files may be found in appendix A

Here a brute-force MATLAB script was used to solve for new component values. By holding the phase angle at the fundamental constant, along with the magnitude ratio between the fundamental and third harmonic, the drain voltage does not change. This leads to a quick method to change the output power of an existing inverter design that avoids iteration. For example, for an existing design, the inductor  $L_R$  was first decreased from 14.1nH to 10nH to increase output power from 9.5W to 10.8W. This change can be calculated a priori given the identical drain voltage. When the new values for  $C_F$  and  $L_F$  (440pF to 497.7pF and 21.5nH to 17.343nH respectively) are inserted in the circuit, the impedance and drain waveforms are as in fig. 2.16. In the event that a large increase in power is required, the characteristic impedance must be lowered. This adds an additional step to the process, but iteration can be avoided if the load impedance is first compared to the drain-source transfer function. As long as the impedance at the second harmonic is significantly lower than the impedance of the load branch (at least 20dB), retuning can be accomplished as described above.

Figure 2.15: Holding the constant the phase at the fundamental and the magnitude ratio between the fundamental and its third harmonic allows characteristic impedance to be changed without changing output power. In this case it varies from  $5\Omega$  to  $50\Omega$ . The component values and simulation files may be found in appendix A

$$Z_{AB} = \frac{num}{den}$$

$$num = L_F L_{2F} L_R C_{2F} s^4 + L_F L_{2F} C_{2F} R_L s^3 + L_F L_R s^2 + L_F R_L s$$

$$den = L_F L_{2F} L_R C_F C_{2F} s^5 + L_F L_R C_F C_{2F} R_L s^4 +$$

$$(L_F L_{2F} C_{2F} + L_R (L_F C_F + L_F C_{2F} + L_{2F} C_{2F})) s^3 +$$

$$R_L (L_F C_F + L_F C_{2F} + L_{2F} C_{2F}) s^2 + (L_F L_R) s + R_L$$

$$(2.2)$$

Directly calculating component values to achieve certain impedance goals extends