Open access • Journal Article • DOI:10.1109/TCSII.2013.2251946

# Design of an Optimal Layout Polyphase Filter for Millimeter-Wave Quadrature LO Generation — Source link

Shailesh Kulkarni, Dixian Zhao, Patrick Reynaert

Institutions: Katholieke Universiteit Leuven

Published on: 27 Mar 2013 - IEEE Transactions on Circuits and Systems li-express Briefs (IEEE)

**Topics:** Integrated circuit layout, Image response, Polyphase system, Bandwidth (signal processing) and Parasitic extraction

Related papers:

- Analysis and Design of Passive Polyphase Filters

- Dual-Band Millimeter-Wave Quadrature LO Generation With a Common-Centroid Floorplan

- A Transformer-Based Poly-Phase Network for Ultra-Broadband Quadrature Signal Generation

- A CMOS-28nm 880-MHz 4 th -order low-pass active-RC filter for 60 GHz transceivers

- 1024-QAM High Image Rejection \$E\$ -Band Sub-Harmonic IQ Modulator and Transmitter in 65-nm CMOS

Process

Share this paper: 🚯 🎽 🛅 🗠

| Citation          | Shailesh Kulkarni, Dixian Zhao, Patrick Reynaert (2013),<br>Design of an Optimal Layout Polyphase Filter for Millimeter-Wave<br>Quadrature LO Generation<br>IEEE Transactions on Circuits and Systems-II, vol.60 no.4, pp.202-206 |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Archived version  | Author manuscript: the content is identical to the content of the published paper, but without the final typesetting by the publisher                                                                                             |  |  |  |

| Published version | http://dx.doi.org/10.1109/TCSII.2013.2251946                                                                                                                                                                                      |  |  |  |

| Journal homepage  | http://ieee-cas.org/                                                                                                                                                                                                              |  |  |  |

| Author contact    | <u>Shailesh.Kulkarni@esat.kuleuven.be</u><br>+ 32 (0)16 321793                                                                                                                                                                    |  |  |  |

|                   |                                                                                                                                                                                                                                   |  |  |  |

(article begins on next page)

# Design of an Optimal Layout Polyphase Filter for mm-Wave Quadrature LO Generation

Shailesh Kulkarni, Dixian Zhao, Patrick Reynaert

*Abstract*—The analysis and design of a two-stage passive RC polyphase filter for mm-wave quadrature LO generation is presented. The layout parasitics which significantly deteriorate the filter performance at mm-wave frequencies are identified with the help of impedance variation and transfer function analysis. To alleviate this parasitic degradation, a new optimal layout structure along with parasitic-compensation technique is proposed which result in 15 dB improvement in image rejection ratio (IRR) compared with conventional layout. Using the proposed techniques more than 35 dB of image rejection over a bandwidth of 7 GHz is demonstrated in an outphasing transmitter at 60 GHz in 40nm CMOS.

Index Terms—image rejection, polyphase filter, quadrature generation, mm-wave, optimal layout, 60 GHz

### I. INTRODUCTION

T HE demand for Gbps data rate is apparent with the applications such as uncompressed video for high definition multimedia interface (HDMI), high-speed file transfer and download kiosk for multimedia. The emerging 60 GHz wireless standard is a promising candidate for such applications because of its 7 GHz unlicensed bandwidth. As bandwidth is an expensive resource, most of the mm-wave tranceivers make use of quadrature radio architectures so that both sides of the spectra can be used for information [1]–[5].

Three common techniques used to generate quadrature signals are, (a) divide by two circuit along with an oscillator at twice the desired LO frequency, (b) quadrature oscillators and (c) single phase oscillator followed by polyphase filter (PPF) [6]. Option (a) has the drawback of double the frequency of operation and therefore low signal levels and high phase noise due to low-quality passives at mm-wave frequencies [7]. Option (b) generates the quadrature LO signal by two coupled oscillators which trades phase noise, tuning range and IQ accuracy [8]. In option (c) a polyphase filter is used which can generally achieve wideband performance with sufficient quadrature accuracy by cascading two or more stages. It also simplifies the on-chip oscillator design compared to previous two techniques [2], [9].

Despite its popularity there has been limited address to the analysis, design and optimization of PPF at mm-wave frequencies [1], [2], [9]. To authors' best knowledge, this is the first brief which does it in a comprehensive way and achieves better performance than previous implementations with the proposed optimal layout and compensation techniques. This brief is organised as follows. In section II, the impact of parasitics and signal loss which become important at high frequencies are discussed. To counter them, an optimal layout is proposed which is more robust against capacitive parasitics

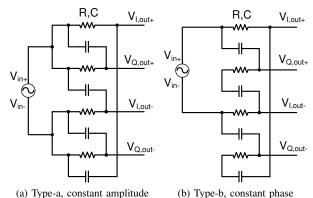

(a) Type-a, constant amplitude (b) Type-b, constant phas

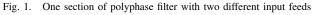

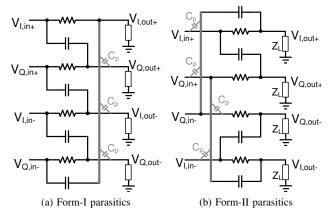

Fig. 2. Polyphase filter, conventional (FORM-I) and symmetric (FORM-II) layout. The long interconnect is highlighted in bold gray

as it is more symmetrical than conventional implementation. In section III one- and two-stage filter are analysed using compensation for inductive parasitics which arise due to long interconnect. Section IV discusses the experimental results and conclusions are drawn in section V.

#### II. POLYPHASE FILTERS AT MM-WAVE

A polyphase filter consists of passive a RC structure which is used for differential quadrature generation. It can easily be cascaded to generate broadband quadrature signal. It can also be used as a complex filter but the focus in this brief is on quadrature generation. The operation of a conventional PPF for low-GHz applications is explained in detail in [10]. Signal loss and influence of parasitics are two important aspects concerning PPFs at mm-wave frequencies. The design concerns at mm-wave frequencies then differ from low-GHz techniques. IRR is a function of quadrature signal amplitude and phase mismatch,  $\alpha$  and  $\theta$  and is defined by (1) [11].

$$IRR = \frac{1 + 2 \cdot \alpha \cos(\theta) + \alpha^2}{1 - 2 \cdot \alpha \cos(\theta) + \alpha^2} \tag{1}$$

#### A. Signal loss

Signal loss in the mm-wave PPF can go relatively high compared with low-GHz applications. It can be relaxed by selecting an optimal input feeding structure and making a compact floorplan to minimize the interconnect length. The latter will be addressed in section IV. There are two input feeding structures for quadrature generation as shown in Fig. 1 and they have an influence on the operation of the PPF. The ratio of transfer function of the differential I and Q of an unloaded filter is given by (2) and (3) for type-*a* and *-b* respectively. Type-*a* has a constant amplitude and type-*b* has a constant phase behaviour [11].

$$H_{type-a} = \frac{\Delta V_{I,out}}{\Delta V_{Q,out}} = \frac{1 - sRC}{1 + sRC}$$

(2)

$$H_{type-b} = \frac{\Delta V_{I,out}}{\Delta V_{Q,out}} = \frac{1}{sRC}$$

(3)

Both types of input feed result in the same IRR as it is a function of both amplitude and phase imbalance. Type*b* has constant phase difference of 90° and the amplitude imbalance can potentially be corrected by limiting amplifiers to improve the IRR. As amplification is a luxury at mm-wave frequencies, type-*b* structure will contribute significantly in the power budget for the LO path. The signal loss of type*a* is 3 dB as compared to 6 dB for type-*b* per stage for an unloaded filter. Therefore type-*a* benefits the power budget and hence this structure is preferred at mm-wave frequencies. In the remaining of the brief, only type-*a* will be considered.

#### **B.** Interconnect parasitics

Most of the PPF implementations [10], [12], [13] have been at relatively lower frequency (sub 10 GHz). As the layout affects its performance the techniques used for optimal layout in these are the use of dummies, relatively large physical dimensions to improve matching, serpentine interconnects to match lengths etc. These are necessary techniques to achieve better than 40 dB of quadrature accuracy at low-GHz. The same cannot be applied at mm-wave. For example, serpentine interconnects are lossy at mm-wave frequencies, large dimensions add parasitic capacitances.

In conventional designs, the layout style followed is shown in Fig. 2(a) which has the highlighted assymetric long interconnect. At mm-wave frequencies (such as 60 GHz) long interconnects can have significant inductance (approximately 600 fH/µm depending on the thickness and width). In a conventional layout, referred to as form-I, the length of the long interconnect is 40 µm (see Fig. 2(a)). The desired pole is shifted due to the dominant inductive interconnect along with other parasitic capacitances. To lessen this effect, the proposed implementation is to distribute it on the differential Q inputs as shown in Fig. 2(b). By doing so, the length is reduced by

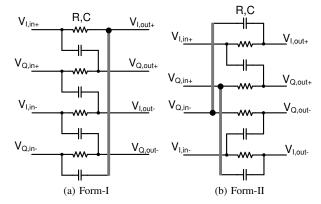

Fig. 3. One-stage PPF with L-compensation and equivalent circuit for nodal analysis. The inductive parasitic interconnect is modelled by the gray inductor

Fig. 4. Simulated image rejection ratio improvement by using one-stage L-compensated PPF (15 pH of parasitic inductance)

40% and the structure is more symmetrical. In this brief it will be referred to as form-II. In addition to it, this structure is more robust than form-I against capacitive parasitics as will be explained in section III-C. It still remains cascadable for broadband operation.

#### III. MM-WAVE PPF WITH COMPENSATION

# A. One-Stage PPF

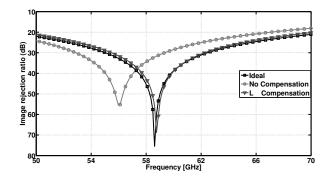

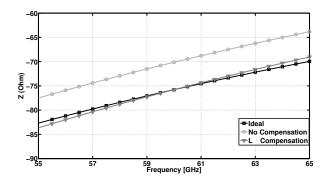

A one-stage form-II polyphase filter with type-*a* input feed as shown in Fig. 3(a) will be analysed in this section. Due to the inductive parasitic effect the susceptance of the outer branch deviates from the ideal and the pole frequency moves off as shown in Fig. 4. To compensate for this, the effective susceptance is made equal to the susceptance of the unaffected capacitor at the pole frequency by reducing the outer C to a new value  $C_n$  given by (4). This technique will be referred to as L-compensation in this brief.

$$\frac{1}{sC} = \frac{1}{sC_n} + sL \tag{4}$$

By this compensation, the susceptance in each of the four branches is equal at the pole frequency. The variation from the ideal case after correction is reduced drastically as shown in Fig. 5. The variation at either side of pole frequency has negligible influence on one-stage form-II PPF but has some effect on two-stage as explained in section III-B. Generally a

Fig. 5. Impedance variation due to parasitic inductance and its compensation. (35fF capacitance with 15 pH of parasitic inductance)

buffer follows a PPF and the load impedance seen by a onestage filter can be considered to be equal for all the outputs. The simplified circuit for nodal analysis of each of the output is shown in Fig. 3(b). Using this the differential I and Q transfer function for one-stage L-compensated PPF is derived as given by (7) and (8).

$$\Delta V_{I,out} = \frac{\left[1 - sC_nR + s^2LC_n\right]Z_L\Delta V_{in}}{\left[R + Z_L + sC_nRZ_L + s^2LC_n\left(R + Z_L\right)\right]} \quad (7)$$

$$\Delta V_{Q,out} = \frac{\left[1 + sCR\right]Z_L\Delta V_{in}}{\left[R + Z_L + sCRZ_L\right]} \tag{8}$$

The ratio of I and Q approaches that of (2). The benefit of compensation (4) is shown in Fig. 4 and it matches very closely with the ideal case.

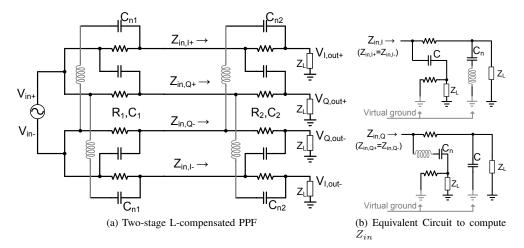

#### B. Two-Stage PPF

A two-stage filter is generally necessary to achieve broadband quadrature LO. A two-stage type-*a* PPF is analysed as shown in Fig. 8(a). The first stage  $(R_1, C_1)$  is similar to the filter analysed in section III-A except that it is loaded with another stage of a form-II filter.

Ideally the input impedance offered by a filter is the same in all the four paths as there exists a virtual ground at the Q input when a balanced input signal is applied to the I input and *vice versa* [11]. At mm-wave frequencies this condition accurately exists only at the pole frequency when a L-compensated PPF is considered. At neighbouring frequencies it can still be treated as a virtual ground for the analysis and the error introduced is negligible. As the structure in Fig. 8(a) is symmetrical, the input impedance  $Z_{in,I+}$  and  $Z_{in,I-}$  are equal and denoted by  $Z_{in,I}$ . Similar argument applies for Q. The load impedance for the first stage are represented by an equivalent circuit by using the concept of virtual ground as shown in Fig. 8(b). Using this

Fig. 6. Simulated image rejection ratio improvement by using two-stage L-compensated PPF (10 pH of parasitic inductance)

Fig. 7. The position of dominant capacitive parasitics  ${\cal C}_p$  in FORM-I and FORM-II layout

the impedances  $Z_{in,I}$  and  $Z_{in,Q}$  are given by (5) and (6). It can be verified that if L = 0 and  $C_n = C$  then  $Z_{in,I} = Z_{in,Q}$ .

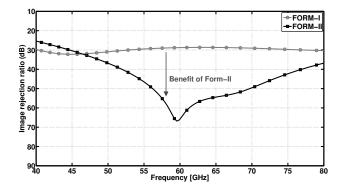

These impedances act as the load to the first stage of a twostage PPF. The transfer function of a two-stage filter can be evaluated by following the procedure of section III-A.  $\Delta V_{I,out}$ of (7) then becomes a function of  $Z_{in,I}$  instead of  $Z_L$ . And similarly  $\Delta V_{Q,out}$  of (8) becomes a function of  $Z_{in,Q}$ . Hence the IRR becomes a function of the load impedance which is not the case at low frequencies, an important mm-wave effect. Fig. 6 compares the image rejection achieved by the two-stage L-compensated method with no-compensation to highlight the benefit. The lower frequency pole is due to second stage and higher frequency pole is due to first stage. The IRR degrades for the pole corrosponding to the first stage because of nonconstant load. The second stage pole is not influenced much and stays at the designed frequency. Hence there is a small buldge at the first stage pole. There is an improvement of 15 dB when the L-compensation is used in comparison to the unused case and matches well with the presented analysis. The simulated amplitude and phase mismatch are below 0.001 dB

Fig. 8. Two-stage L-compensated polyphase filter and the equivalent circuit to compute input impedance

and  $0.2^{\circ}$  over the 10 GHz bandwidth (IRR > 55 dB). The analysis can be similarly applied for 3- and higher stages but the loss will correspondingly go up.

# C. Effect of Capacitive Parasitics

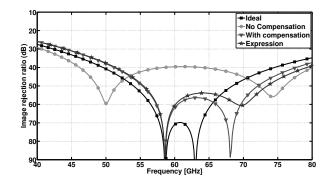

A simple overlap of two metal layers has an overlap parasitic capacitance associated with that crossing. At mmwave frequencies, the effect of all the overlap parasitics has a considerable impact on the performance of the filter. The overlap parasitic capacitances are unavoidable in both the form-I and form-II implementations. But their positions are different in both the cases as shown in Fig. 7. For form-I they occur unevenly due to the inherent asymmetry. Because of this, the amplitude of  $\Delta V_{I,out}$  and  $\Delta V_{Q,out}$  are different from the ideal due to the interaction of signals via the parasitic capacitive path. For form-II they occur more symmetrically and hence their impact is reduced.

It is worth mentioning that the dominant inductive parasitics due to long interconnects as discussed before can also be compensated for form-I. As its length is longer than in form-II, the required compensation is much smaller than in case of form-II. The compensation necessary for form-I is more than 20% of the total capacitance as compared to 10% for form-II [5]. This leads to routing difficulties in form-I. EM field simulations of the complete interconnect structure of both the forms is performed by ADS momentum which enables to model them by S-parameters. Fig. 9 shows the simulation results including effects of all parasitics along with compensation schemes. This shows that even after compensation for form-I it cannot achieve IRR better than 30 dB. The robustness of form-II verses form-I against parasitics is evident.

#### **IV. IMPLEMENTATION AND EXPERIMENTAL RESULTS**

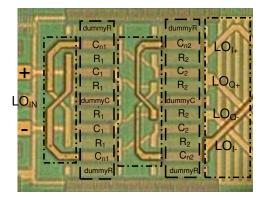

To put the above analysis to test, a two-stage polyphase filter is used to generate mm-wave quadrature signals for a 60 GHz outphasing transmitter (TX) in 40nm CMOS technology. In this design, optimization yields  $R_1$ ,  $C_1$  and  $C_{n1}$  of 75  $\Omega$ , 33.5 fF and 30 fF in the first stage and  $R_2$ ,  $C_2$  and  $C_{n2}$  of 75  $\Omega$ , 36.5 fF and 33 fF in the second stage respectively.  $C_{n1}$ and  $C_{n2}$  are reduced by 3.5 fF for compensation.

Fig. 9. Comparison of the two layouts and the benefit of form-II with respect to parasitics

Salicided p+ resistors and interdigitated metal-oxide-metal (MOM) capacitors are used in the PPF. The size of the salicided resistors are optimized to reduce the impact of mismatch and the associated parasitic capacitance. There exists a trade off between matching and resistor cutoff frequency [10]. The size of the capacitors are also chosen to match the aspect ratio of resistors to minimize the routing overhead. Dummy capacitors are used in between two continuous resistors and dummy resistors are used next to outer capacitors to provide same neighbouring environment and mitigate lithography edge effects. The layout is designed in a compact manner to reduce the 60 GHz interconnect length and hence minimize the signal loss. The active area of the PPF is only 65 µm x 50 µm. The complete TX can be seen in [5] and the PPF photo is shown in Fig. 10. It highlights the interconnects in dotdashed box which are modelled based on field simulations and are used to compute the compensation value  $C_n$ . In the simulations both extracted RC parasitics (dashed box) along with S-parameter model of the interconnect (dot-dashed box) are included. Simulated voltage loss is 6.5 dB for a tuned load of 850  $\Omega$  and 5.3 dB when computed by analytical expression. The 1.2 dB difference is due to the unaccounted loss of interconnects.

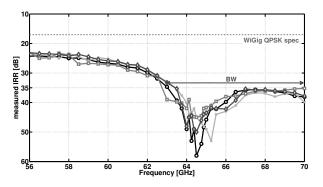

Input single tone baseband signals are upconverted by onchip mixers using the quadrature LO signal generated by

Fig. 10. Two-stage polyphase filter micro photograph. Dot-dash boxes are modelled by EM simulations and dashed box with RC extraction

Fig. 11. Measured Image Rejection Ratio for 4 samples

TABLE I PERFORMANCE COMPARISON WITH PUBLISHED MMWAVE PPFS

| Ref, Technology | $f_0$ | IRR <sub>min</sub> | BW covered below IRR <sub>c</sub> |                       |

|-----------------|-------|--------------------|-----------------------------------|-----------------------|

|                 | (GHz) | (dB)               | BW(GHz)                           | IRR <sub>c</sub> (dB) |

| [2] RX,CMOS     | 60    | 32.0               | 3.9                               | 23.0                  |

| [2] TX,CMOS     | 60    | 23.0               | 5                                 | 18.3                  |

| [3] CMOS        | 20    | 28.0               | -                                 | -                     |

| [9] BiCMOS      | 60    | 28.6               | 2                                 | 28.6                  |

| [14] SiGe:C     | 60    | 32.5               | 7                                 | 24.0                  |

| This work, CMOS | 60    | 58.0               | >7                                | 35.0                  |

the proposed PPF [5]. The IRR is measured using Spectrum Analyzer. The measured I/O imbalance from the transmitter is a combined effect of all the inaccuracies including the PPF, mismatch in the signal path and measurement setup. Therefore the actual PPF performance is equal to or better than the measured IRR. Four samples were measured and results are shown in Fig. 11 with a minimum of 58 dB. The IRR spread is < 5 dB and < 1 GHz which confirms good matching and validates the proposed compensation. Using this PPF, the TX in [5] achieved an EVM of -35 dB for a QPSK/8PSK signal, which confirms the excellent IRR achieved by the proposed PPF. Table I gives the performance comparison of recent implementations of mm-wave PPFs with their bandwidth coverage (IRR<sub>c</sub> is the worst IRR measured over the specified BW). The proposed PPF achieves the highest reported image rejection at mm-wave frequencies by using the proposed optimal symmetrical layout and parasitic aware design technique.

# V. CONCLUSION

In this brief, a two-stage passive RC polyphase filter for 60 GHz quadrature signal generation is presented. Input-feed type with lower loss which is important for mm-wave frequencies is chosen. The dominant inductive parasitic is identified and a corresponding compensation method is proposed. An optimal layout is proposed which reduces the impact of parasitic capacitances which become important at mm-wave frequencies. The improvement of 15 dB in I/Q accuracy over conventional layout is achieved. The measured performance is better than 35 dB across a bandwidth of more than 7 GHz.

#### ACKNOWLEDGMENT

The authors would like to thank Catrene PANAMA project and ST-Ericsson, Zaventem, Belgium. This research is partly supported by the ERC Advanced Grant 227680.

#### REFERENCES

- B. Razavi, "A Millimeter-Wave CMOS Heterodyne Receiver With On-Chip LO and Divider," *Solid-State Circuits, IEEE Journal of*, vol. 43, no. 2, pp. 477 –485, feb. 2008.

- [2] A. Parsa and B. Razavi, "A New Transceiver Architecture for the 60-GHz Band," *Solid-State Circuits, IEEE Journal of*, vol. 44, no. 3, pp. 751 –762, march 2009.

- [3] W. Chan and J. Long, "A 60-GHz Band 2 × 2 Phased-Array Transmitter in 65-nm CMOS," *Solid-State Circuits, IEEE Journal of*, vol. 45, no. 12, pp. 2682 –2695, dec. 2010.

- [4] C. Marcu, D. Chowdhury, C. Thakkar, J.-D. Park, L.-K. Kong, M. Tabesh, Y. Wang, B. Afshar, A. Gupta, A. Arbabian, S. Gambini, R. Zamani, E. Alon, and A. Niknejad, "A 90 nm CMOS Low-Power 60 GHz Transceiver With Integrated Baseband Circuitry," *Solid-State Circuits, IEEE Journal of*, vol. 44, no. 12, pp. 3434 –3447, dec. 2009.

- [5] D. Zhao, S. Kulkarni, and P. Reynaert, "A 60-GHz Outphasing Transmitter in 40-nm CMOS," *Solid-State Circuits, IEEE Journal of*, vol. 47, no. 12, dec. 2012.

- [6] A. Valero-Lopez, S. T. Moon, and E. Sanchez-Sinencio, "Self-calibrated quadrature generator for WLAN multistandard frequency synthesizer," *Solid-State Circuits, IEEE Journal of*, vol. 41, no. 5, pp. 1031 – 1041, may 2006.

- [7] W. Volkaerts, M. Steyaert, and P. Reynaert, "118GHz fundamental VCO with 7.8% tuning range in 65nm CMOS," in *Radio Frequency Integrated Circuits Symposium (RFIC), 2011 IEEE*, june 2011, pp. 1–4.

- [8] K. Scheir, S. Bronckers, J. Borremans, P. Wambacq, and Y. Rolain, "A 52 GHz Phased-Array Receiver Front-End in 90 nm Digital CMOS," *Solid-State Circuits, IEEE Journal of*, vol. 43, no. 12, pp. 2651 –2659, dec. 2008.

- [9] Notten, M.G.M. and Veenstra, H., "60GHz quadrature signal generation with a single phase VCO and polyphase filter in a 0.25 μm SiGe BiCMOS technology," in *Bipolar/BiCMOS Circuits and Technology Meeting*, 2008. BCTM 2008. IEEE, 13-15 2008, pp. 178–181.

- [10] Behbahani, F. and Kishigami, Y. and Leete, J. and Abidi, A.A., "CMOS mixers and polyphase filters for large image rejection," *Solid-State Circuits, IEEE Journal of*, vol. 36, no. 6, pp. 873 –887, jun 2001.

- [11] J. Kaukovuori, K. Stadius, J. Ryynanen, and K. Halonen, "Analysis and Design of Passive Polyphase Filters," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 55, no. 10, pp. 3023 –3037, nov. 2008.

- [12] C. Meng, D. Sung, and G. Huang, "A 5.2-GHz GaInP/GaAs HBT double-quadrature downconverter with polyphase filters for 40-dB image rejection," *Microwave and Wireless Components Letters, IEEE*, vol. 15, no. 2, pp. 59 – 61, feb. 2005.

- [13] H. Kodama, H. Ishikawa, N. Oshima, and A. Tanaka, "A 1.3-degree I/Q phase error, 7.1 - 8.7-GHz LO generator with single-stage digital tuning polyphase filter," in VLSI Circuits (VLSIC), 2010 IEEE Symposium on, june 2010, pp. 145 –146.

- [14] H. Forstner, M. Ortner, and L. Verweyen, "A fully integrated homodyne upconverter MMIC in SiGe:C for 60 GHz wireless applications," in *Silicon Monolithic Integrated Circuits in RF Systems (SiRF), 2011 IEEE 11th Topical Meeting on*, jan. 2011, pp. 129–132.