# This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Design of high performance continuous time sigma delta ADC

Zhang, Fan

2011

Zhang, F. (2011). Design of high performance continuous time sigma delta ADC. Master's thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/43538

https://doi.org/10.32657/10356/43538

Downloaded on 24 Aug 2022 21:54:23 SGT

# Design of High Performance Continuous Time Sigma Delta ADC

# ZHANG FAN

# SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING

2011

# Acknowledgements

I wish to express my sincere gratitude to my professor, Associate Professor Siek Liter. I feel very honored and privileged to have worked under his supervision. I have greatly benefited from his deep intuition and extensive knowledge of system and circuit design, from his invaluable teaching and research skills, and from his guidance in writing papers/thesis and making presentations.

I would like to thank Panasonic Semiconductor Pte. Ltd and EDB for awarding me with this precious opportunity for two years of Master of Engineering training program in NTU and giving me consistent financial as well as technical support throughout my M.Eng candidature.

As this research largely relies on collaboration effort, help and collaboration from group members and partners are vital to the completion of the project. Hence, I would like to extend my sincere gratitude to my research team members as well as close friends Ms. Teh Li Lian and Mr. Leow Yoon Hwee for their generous help in the research progress. Together with my research teammates, we worked together very closely throughout the entire project. We used to discuss on the subjects that aroused our interests and share latest thoughts that came into our minds. I have to say, working with them has always been pleasant and fruitful. Their special insights into some problems and inspirable idea always give me great help. Without their help and encouragement, I would not have achieved so much.

Also, I am also grateful to all the technicians and friends working in the Centre of Integrated Circuits and Systems (CICS) in Nanyang Technological University for their technical support and friendship. Last but not least, I want to dedicate this thesis to my parents. Their unconditional love and mental support demonstrated in so many admirable ways are still the strongest support throughout my life in Singapore.

# Summary

$\Sigma\Delta$  technique has always been the popular choice for designing high resolution data converters due to the advantage of oversampling and noise shaping. In recent years, continuous time implementation of  $\Sigma\Delta$  modulator is attracting more and more research attention for its superior potential to realize low power low voltage and/or high speed design. CT  $\Sigma\Delta$  modulator relaxes amplifier's unity gain bandwidth requirements which greatly improves its achievable conversion speed. It also has the advantage of implicit anti-aliasing feature.

In this research, various design trade-offs and implementation issues have been introduced and discussed. Special focus has been put on the issue of clock jitter which is considered to be the major obstacle for CT  $\Sigma\Delta$  modulator to be widely implemented. In this research, a special pulse shaping technique which is called fixed length return-to-zero method was proposed. Simulation shows that it almost achieves the best performance any pulse shaping method can achieve. It not only greatly improves CT modulator's jitter performance, but also exerts very little adverse effects such as increased power consumption, circuit overhead, and increased loop delay.

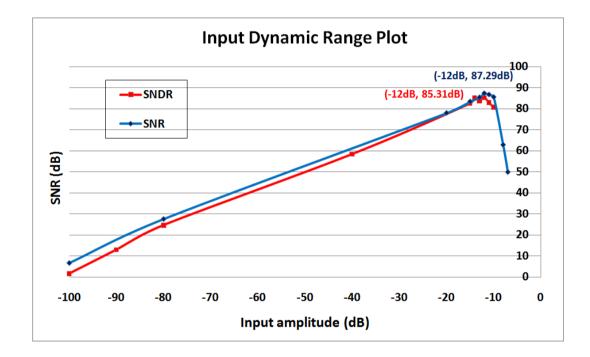

For the purposed of verifying various design concepts developed in this research, a 4<sup>th</sup> order 1-bit prototype modulator integrated in 0.18  $\mu$ m CMOS technology has been developed. Simulation shows it is able to achieve 85 dB SNDR for 25 kHz input signal range. And the FOM it achieves is 0.22pJ/conversion. The total chip occupies an area of 1.725mm<sup>2</sup>.

# TABLE OF CONTENTS

| ACKNOW | VLEDGEMENTS                                              | I    |

|--------|----------------------------------------------------------|------|

| SUMMAR | XY                                                       | IV   |

| CHAPTE | R 1 INTRODUCTION                                         | 1    |

| 1.1 M  | otivation                                                | 1    |

| 1.2 Ob | jective                                                  | 5    |

| 1.3 Th | esis Organization                                        | 5    |

| CHAPTE | R 2 OVERVIEW OF ΣΔ CONVERTERS                            | 7    |

| 2.1 Sa | mpling and Quantization                                  | 7    |

| 2.1.1  | Sampling                                                 | 7    |

| 2.1.2  | Quantization                                             | 8    |

| 2.2 ΣΔ | ADC Performance Metrics                                  | . 10 |

| 2.3 ΣΔ | Modulator Operating Principles                           | . 12 |

| 2.3.1  | Oversampling                                             | . 12 |

| 2.3.2  | Oversampled Noise Shaping Converters: $\Sigma\Delta$ ADC | . 15 |

| 2.3.3  | High Order Noise Shaping                                 | . 18 |

| 2.3.4  | Stability                                                | . 22 |

| 2.4 Co | ntinuous Time $\Sigma\Delta$ Modulators                  | . 23 |

| 2.4.1  | Theory of CT Modulators                                  | . 24 |

| 2.4.2  | Features of Continuous Time $\Sigma\Delta$ Modulators    | . 26 |

| CHAPTE | <b>R 3</b> CONTINUOUS TIME ΣΔ MODULATOR DESIGN ISSUES    | .29  |

| 3.1 Ar | chitecture Design Trade-offs Analysis                    | . 29 |

| 3.1.1  | Feedforward vs. Feedback Loop Filter                     | . 29 |

| 3.1.2  | Single-bit vs. Multi-bit Quantization                    | . 32 |

| 3.1.3  | DAC Pulse Shape                                          | . 37 |

| 3.2 M  | odulator Coefficients Calculation & Scaling              | . 40 |

| 3.2.1  | DT-to-CT Transformation                                  | . 40 |

| 3.2.2  | Coefficient Calculation & Scaling: An Automated Approach | . 42 |

| 3.3 Ci | rcuit Based Differential Behavioral Model                | . 44 |

| 3.4 Cr | itical Circuit Non-idealities and Their Effects          | . 46 |

| 3.4.1  | Finite Gain Bandwidth Effect                             | . 47 |

| 3.4.2                                                                                                                                                                                                       | Coefficients Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

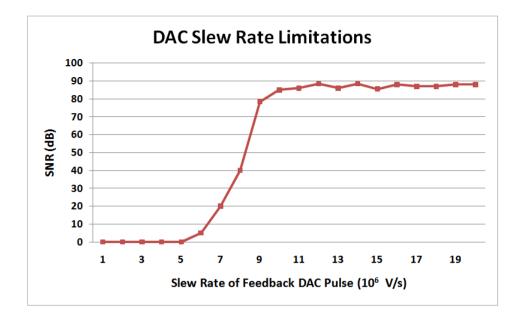

| 3.4.3                                                                                                                                                                                                       | Slew Rate Limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

| 3.4.4                                                                                                                                                                                                       | Offset and Tones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| 3.4.5                                                                                                                                                                                                       | Inter-symbol Interference (ISI) in NRZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

| 3.4.6                                                                                                                                                                                                       | Thermal Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| CHAPTI                                                                                                                                                                                                      | ER 4 THEORETICAL STUDIES ON TIMING NON-IDEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ALITIES IN    |

| <b>CT ΣΔ Ν</b>                                                                                                                                                                                              | IODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63            |

| 4.1 E                                                                                                                                                                                                       | Excess Loop Delay (ELD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| 4.1.1                                                                                                                                                                                                       | Effects of Excess Loop Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64            |

| 4.1.2                                                                                                                                                                                                       | Solutions to Tackle ELD Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

| 4.2 0                                                                                                                                                                                                       | Clock Jitter Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

| 4.2.1                                                                                                                                                                                                       | Synchronous Jitter vs. Accumulated Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

| 4.2.2                                                                                                                                                                                                       | Pulse Width Jitter vs. Pulse Position Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71            |

| 4.2.3                                                                                                                                                                                                       | Jitter Effects in CT Modulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72            |

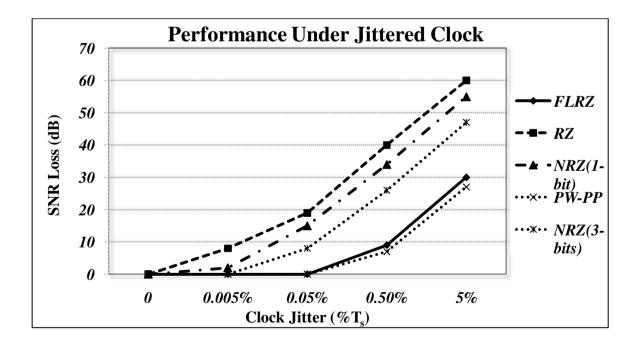

| 4.2.4                                                                                                                                                                                                       | Clock Jitter Effect Minimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75            |

| 4.2.5                                                                                                                                                                                                       | Novel Fixed-Length Return-to-Zero Feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78            |

| 4.2.6                                                                                                                                                                                                       | Performance Simulation & Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

|                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

| CHAPTI                                                                                                                                                                                                      | ER 5 IMPLEMENTATION OF A 4 <sup>TH</sup> ORDER SINGLE-B                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IT            |

| -                                                                                                                                                                                                           | ER 5 IMPLEMENTATION OF A 4 <sup>TH</sup> ORDER SINGLE-B<br>UOUS TIME ΣΔ MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| CONTIN                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

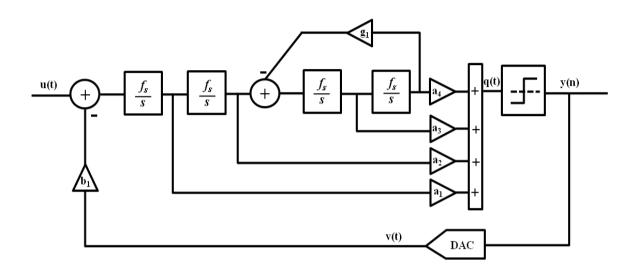

| <b>CONTIN</b><br>5.1 M                                                                                                                                                                                      | UOUS TIME ΣΔ MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88            |

| 5.1 N<br>5.2 C                                                                                                                                                                                              | UOUS TIME ΣΔ MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88<br>        |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F                                                                                                                                                                           | UOUS TIME ΣΔ MODULATOR<br>Iodulator Architecture Design<br>Coefficient Calculations & Mapping                                                                                                                                                                                                                                                                                                                                                                                                                               | 88<br>        |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F                                                                                                                                                                           | UOUS TIME ΣΔ MODULATOR<br>Iodulator Architecture Design<br>Coefficient Calculations & Mapping<br>from Single-End Model to Differential Model                                                                                                                                                                                                                                                                                                                                                                                |               |

| CONTIN           5.1         M           5.2         O           5.3         F           5.4         O                                                                                                      | UOUS TIME ΣΔ MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F<br>5.4 C<br>5.4.1                                                                                                                                                         | UOUS TIME ΣΔ MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>88</b><br> |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F<br>5.4 C<br>5.4.1<br>5.4.2                                                                                                                                                | UOUS TIME ΣΔ MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F<br>5.4 C<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4                                                                                                                              | <b>UOUS TIME ΣΔ MODULATOR</b> Iodulator Architecture Design         Coefficient Calculations & Mapping         Trom Single-End Model to Differential Model         Circuit Implementations         Class AB Op-amp in First Stage Active-RC Integrator         Multiple-output Transconductor         Quantizer                                                                                                                                                                                                             | <b>88</b><br> |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F<br>5.4 C<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.5 L                                                                                                                     | <b>UOUS TIME ΣΔ MODULATOR</b> Iodulator Architecture Design         Coefficient Calculations & Mapping         Crom Single-End Model to Differential Model         Circuit Implementations         Class AB Op-amp in First Stage Active-RC Integrator         Multiple-output Transconductor         Quantizer         The Fixed Length Return-to-Zero DAC Cell                                                                                                                                                            |               |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F<br>5.4 C<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.5 L                                                                                                                     | <b>UOUS TIME ΣΔ MODULATOR</b> Addulator Architecture Design         Coefficient Calculations & Mapping         Crom Single-End Model to Differential Model         Circuit Implementations         Class AB Op-amp in First Stage Active-RC Integrator         Multiple-output Transconductor         Quantizer         The Fixed Length Return-to-Zero DAC Cell         ayout Considerations                                                                                                                               | <b>88</b><br> |

| CONTIN<br>5.1 M<br>5.2 C<br>5.3 F<br>5.4 C<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.5 L<br>5.6 S<br>CHAPTI                                                                                                  | <b>UOUS TIME ΣΔ MODULATOR</b> Addulator Architecture Design         Coefficient Calculations & Mapping         Crom Single-End Model to Differential Model         Circuit Implementations         Class AB Op-amp in First Stage Active-RC Integrator         Multiple-output Transconductor         Quantizer         The Fixed Length Return-to-Zero DAC Cell         ayout Considerations                                                                                                                               |               |

| CONTIN         5.1       M         5.2       O         5.3       F         5.4       O         5.4.1       5.4.2         5.4.3       5.4.4         5.5       L         5.6       S         CHAPTI       6.1 | IOOUS TIME ΣΔ MODULATOR         Modulator Architecture Design         Coefficient Calculations & Mapping         Crom Single-End Model to Differential Model         Crown Single-End Model to Differential Model         Cricuit Implementations         Class AB Op-amp in First Stage Active-RC Integrator         Multiple-output Transconductor         Quantizer         The Fixed Length Return-to-Zero DAC Cell         ayout Considerations         imulation Results         ER 6       CONCLUSIONS & FUTURE WORK |               |

| BIBLIOGRAPHY              |     |

|---------------------------|-----|

| APPENDIX CIRCUIT DIMENSIO | DNS |

# LIST OF FIGURES

| Figure 1-1 Conventional Audio Signal Processing Chain                           | 3        |

|---------------------------------------------------------------------------------|----------|

| Figure 1-2 Audio Signal Processing Chain for DSD Technology                     | 4        |

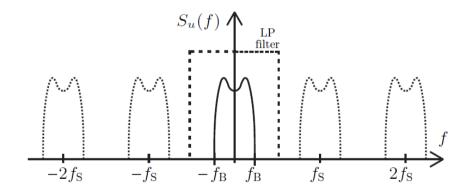

| Figure 2-1 Spectral Sampling Operation                                          | 7        |

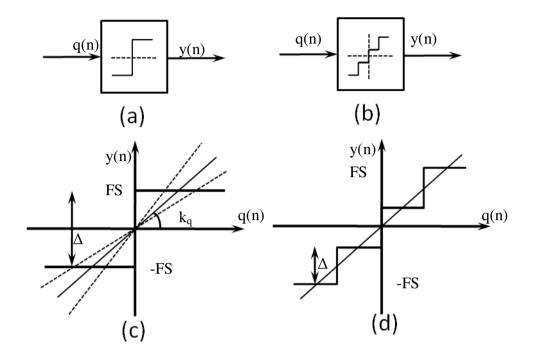

| Figure 2-2 (a) Single-bit Quantizer (b) Multi-bit Quantizer (c)Single-bit Q     | uantizer |

| Transfer Curve (d) Multi-bit Quantizer Transfer Curve                           | 9        |

| Figure 2-3 Conventional ADC Structure                                           |          |

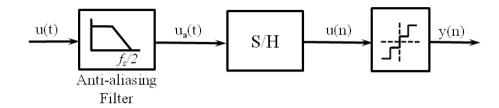

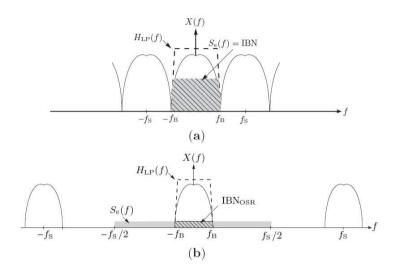

| Figure 2-4 PSD of an Oversampled Signal                                         |          |

| Figure 2-5 Spectral Effect of Oversampling                                      | 14       |

| Figure 2-6 Noise-Shaped Oversampling Modulator                                  |          |

| Figure 2-7 Linearized Model of $\Sigma\Delta$ Modulator                         | 16       |

| Figure 2-8 NTF and STF of a Second Order $\Sigma\Delta$ Modulator               | 17       |

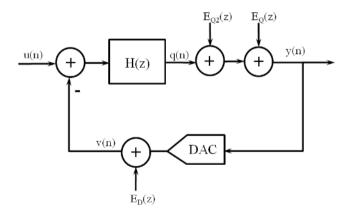

| Figure 2-9 $\Sigma\Delta$ Modulator Model Including Non-idealities              | 17       |

| Figure 2-10 First Order $\Sigma\Delta$ Modulator                                |          |

| Figure 2-11 Second Order $\Sigma\Delta$ Modulator                               | 19       |

| Figure 2-12 NTF of First Order and Second Order $\Sigma\Delta$ Modulator        | 20       |

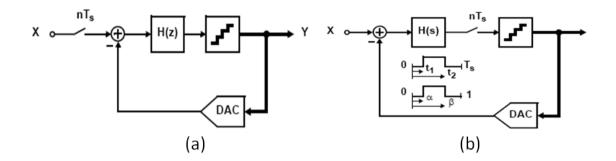

| Figure 2-13 (a) DT $\Sigma\Delta$ Modulator (b) CT $\Sigma\Delta$ Modulator     |          |

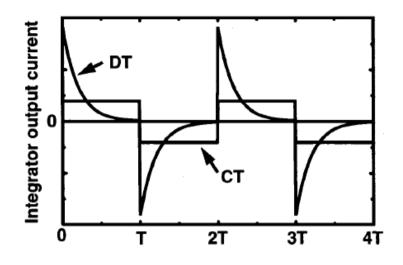

| Figure 2-14 Integrator Output Current with CT Feedback vs. DT Feedback          |          |

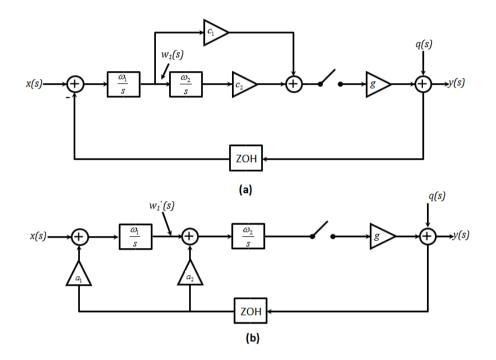

| Figure 3-1 Linearized 2 <sup>nd</sup> order (a) CIFF (b) CIFB Modulator         | 30       |

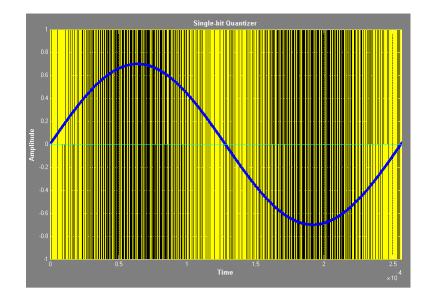

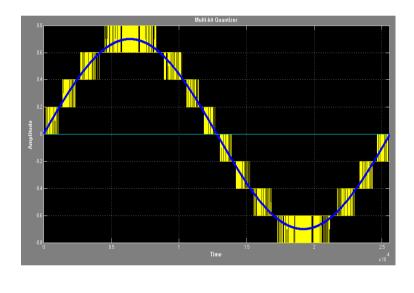

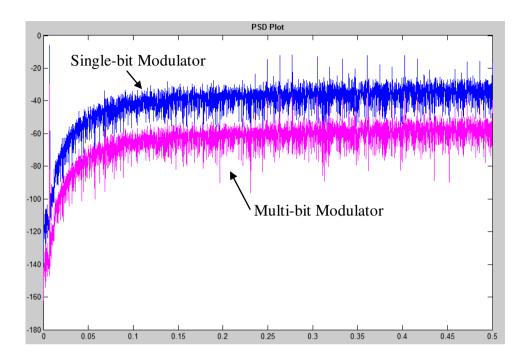

| Figure 3-2 Output waveforms of (a) Single-bit Modulator (b) Multi-bit Modulator |          |

| Figure 3-3 PSD plot of Single-bit Modulator vs. Multi-bit Modulator             | 34       |

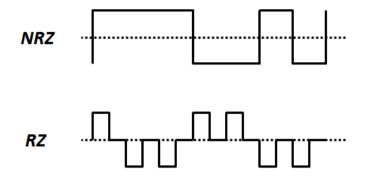

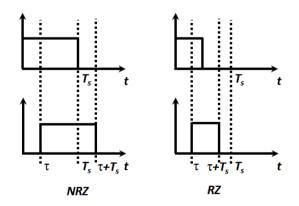

| Figure 3-4 NRZ and RZ Feedback Pulses                                           |          |

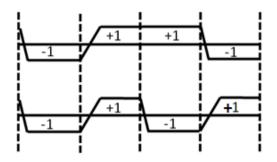

| Figure 3-5 ISI Effect Demonstrated by Two DAC Feedback Sequences                | 39       |

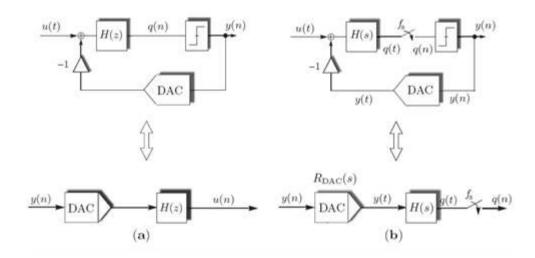

| Figure 3-6 (a) DT Modulator and its Feedback Equivalence (b) CT Modulator       | and its  |

| Feedback Equivalence                                                            | 41       |

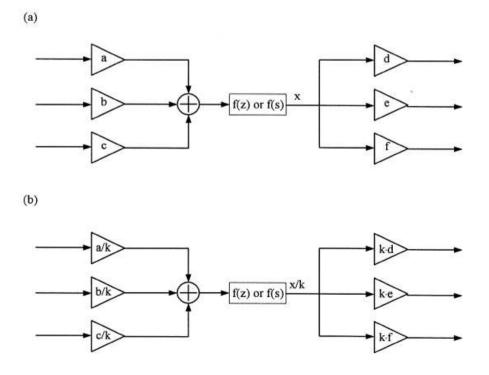

| Figure 3-7 Signal Scaling in Integrator                                         |          |

| Figure 3-8 Behavior Model of First Stage Op-amp                                 | 45       |

| Figure 3-9 Behavior Model of Multiple-outputs Transconductor                    |          |

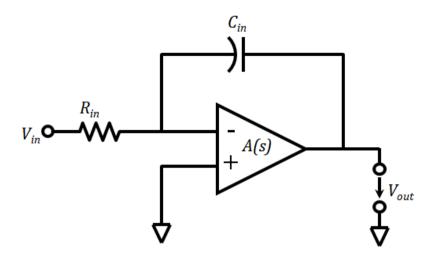

| Figure 3-10 A Simplified Active-RC integrator Model                             |          |

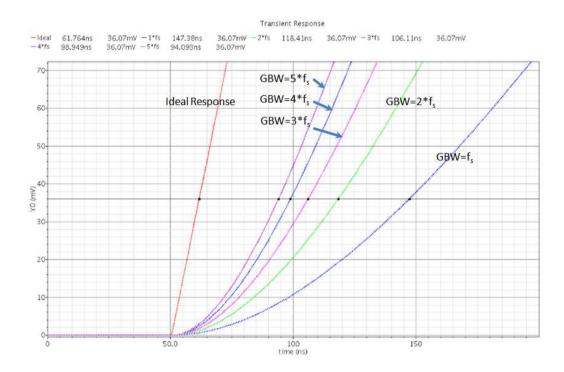

| Figure 3-11 Step Response of Integrators with Different GBW Values              | 50       |

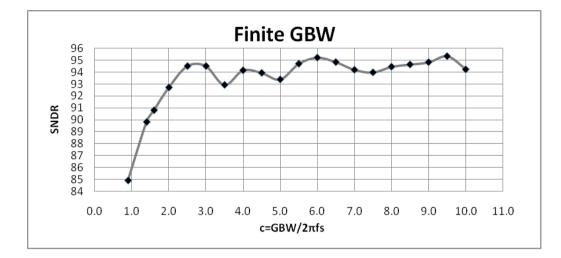

| Figure 3-12 Finite GBW vs. SNDR for CT Modulator                                | 51       |

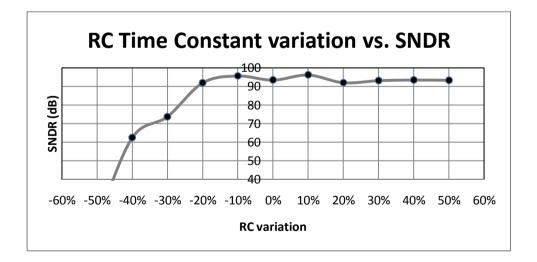

| Figure 3-13 RC Product Variation vs. SNDR                                       | 52       |

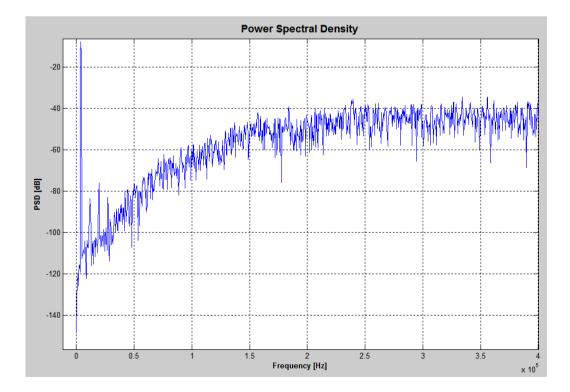

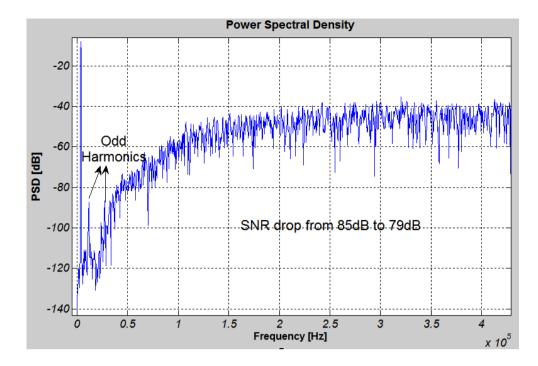

| Figure 3-14 PSD of a CT Modulator under Slew Rate Limitation                    | 54       |

|                                                                                 | viii     |

| Figure 3-15 ISI Effect of CT $\Sigma\Delta$ Modulator                                       |

|---------------------------------------------------------------------------------------------|

| Figure 3-16 Feedback Pulse Shape under Strong Slew Rate Limitation57                        |

| Figure 3-17 Model of Feedback Pulse Spike in Simulink58                                     |

| Figure 3-18 PSD of CT $\Sigma\Delta$ Modulator with Strong Feedback Spike                   |

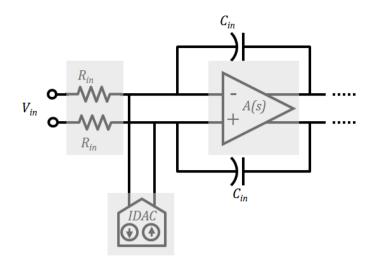

| Figure 3-19 Input Stage of CT $\Sigma\Delta$ Modulator                                      |

| Figure 3-20 Noise Model of 1-bit DAC Cell                                                   |

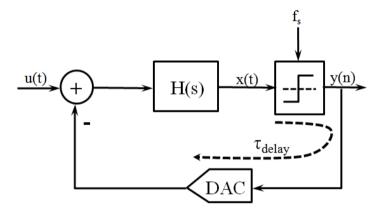

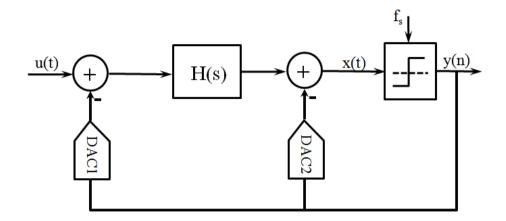

| Figure 4-1 Excess Loop Delay Effect in Block Model                                          |

| Figure 4-2 RZ & NRZ Feedback Pulse with Excess Loop Delay64                                 |

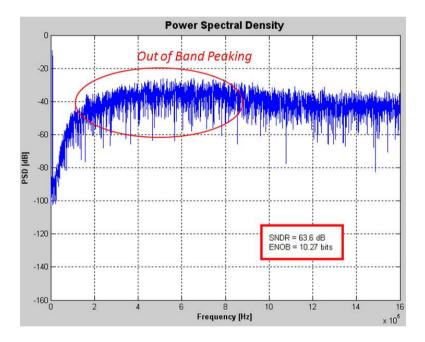

| Figure 4-3 PSD Plot Showing Out-of-band Peaking due to ELD                                  |

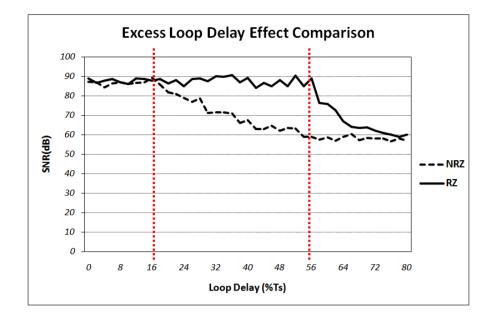

| Figure 4-4 ELD vs. SNR for RZ & NRZ Feedback Pulse                                          |

| Figure 4-5 Compensation of ELD Effect with Direct Feedback Method                           |

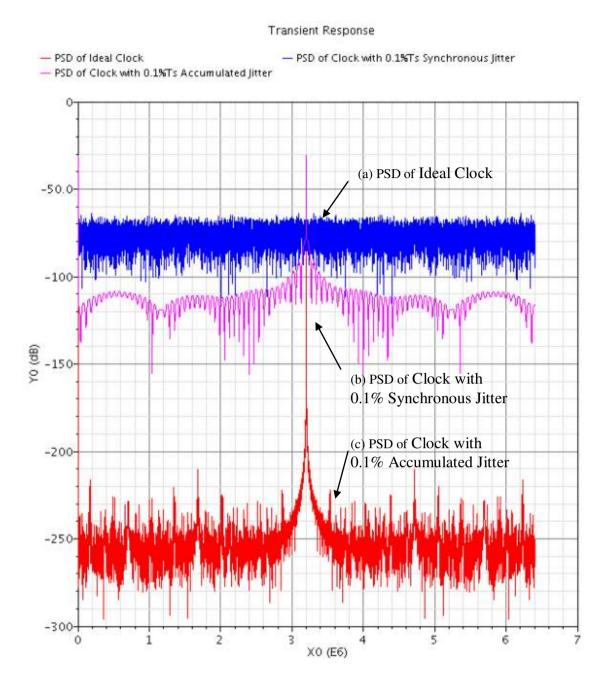

| Figure 4-6 PSD Plot of Clock with (a) no jitter (b)synchronous jitter (c)accumulated jitter |

|                                                                                             |

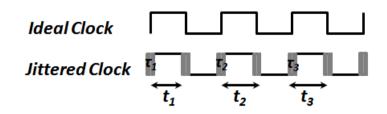

| Figure 4-7 Time Domain Visualization of Jittered Clock                                      |

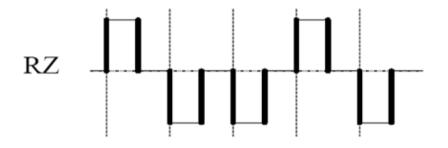

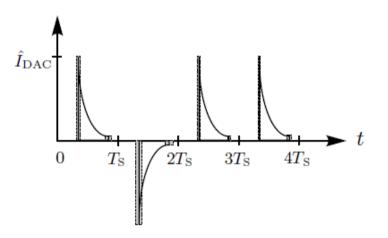

| Figure 4-8 RZ Feedback Pulse with Jitter                                                    |

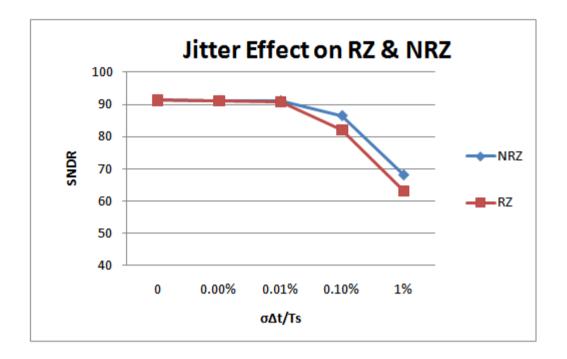

| Figure 4-9 Simulated SNDR with Jitter Noise for RZ and NRZ Feedback Pulse74                 |

| Figure 4-10 Pulse Jitter Effect for SCR Shaped feedback                                     |

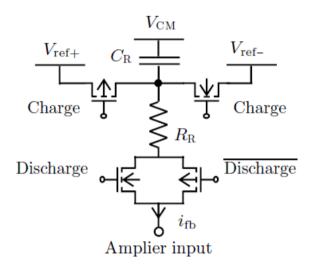

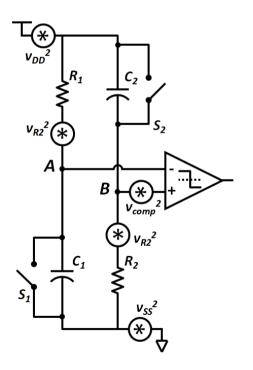

| Figure 4-11 Implementation of SCR Pulse Shaping DAC in [36]77                               |

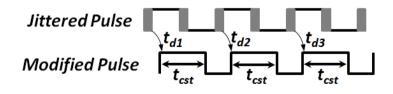

| Figure 4-12 Concept of Transforming Pulse Width Jitter to Pulse Position Jitter78           |

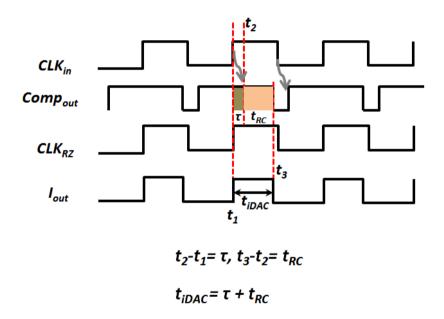

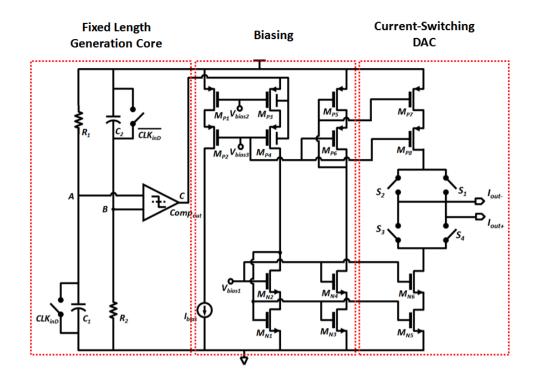

| Figure 4-13 Implementation of Proposed FLRZ DAC79                                           |

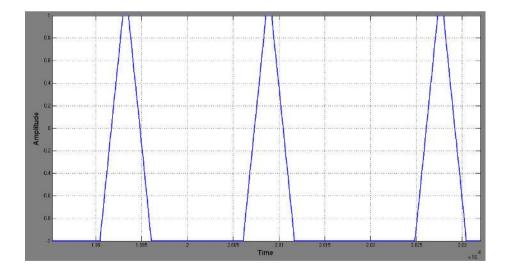

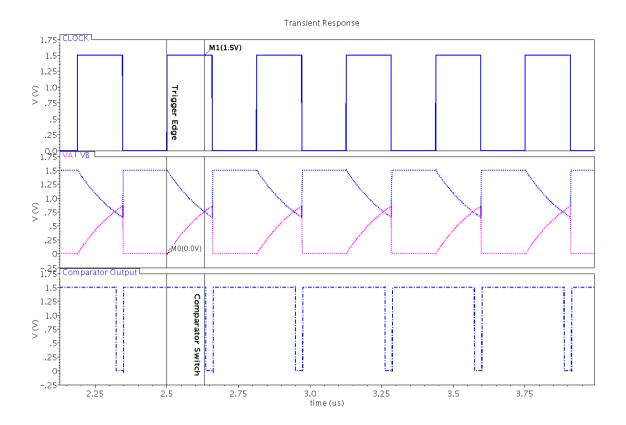

| Figure 4-14 Output Waveform for Fixed Length Pulse Core Generation Circuit                  |

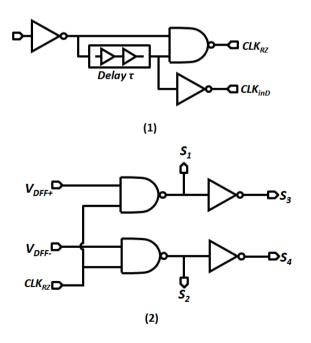

| Figure 4-15 Proposal of Clocking Scheme for FLRZ DAC Implementation                         |

| Figure 4-16 Noise Model for the Fixed Length Pulse Generation Core Circuit                  |

| Figure 4-17 Behavioral Simulation for Different Feedback Pulse Scheme                       |

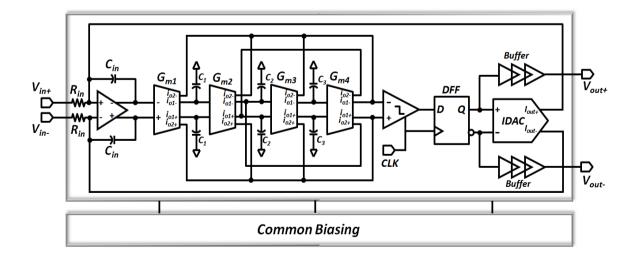

| Figure 5-1 Block Level Model of Proposed Modulator Architecture                             |

| Figure 5-2 Differential Model of the Proposed Modulator                                     |

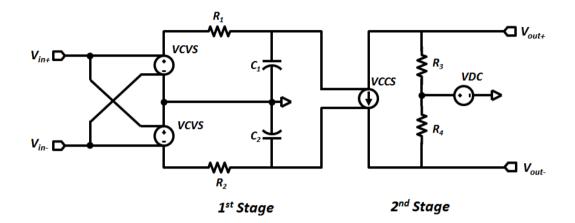

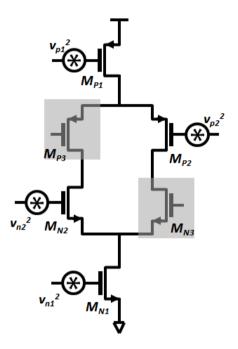

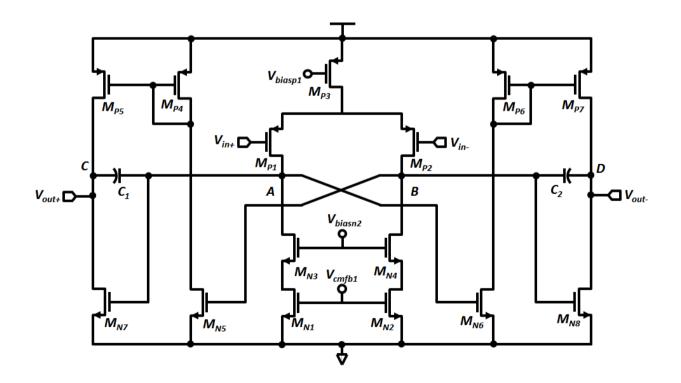

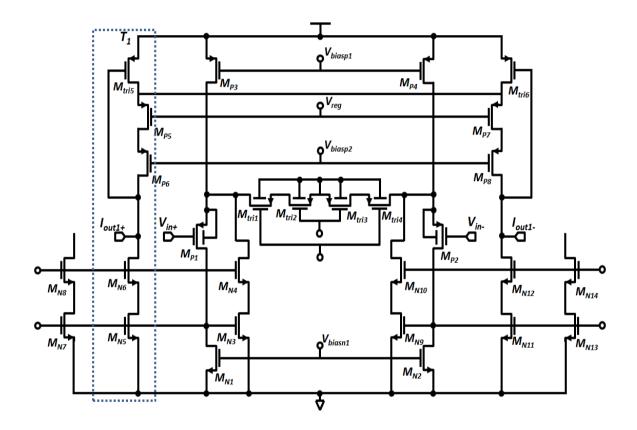

| Figure 5-3 ClassAB Op-amp Implemented in 1 <sup>st</sup> Stage Integrator                   |

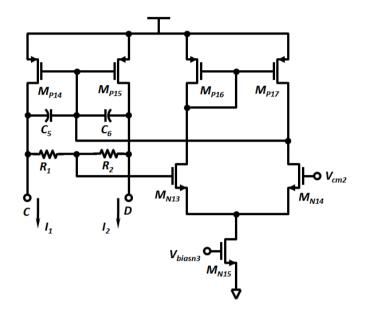

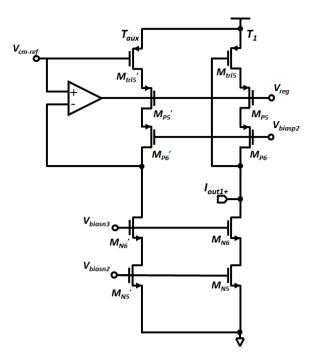

| Figure 5-4 CMFB for 1 <sup>st</sup> Stage Output of the ClassAB Op-amp96                    |

| Figure 5-5 CMFB for 2 <sup>nd</sup> Stage Output of the ClassAB Op-amp                      |

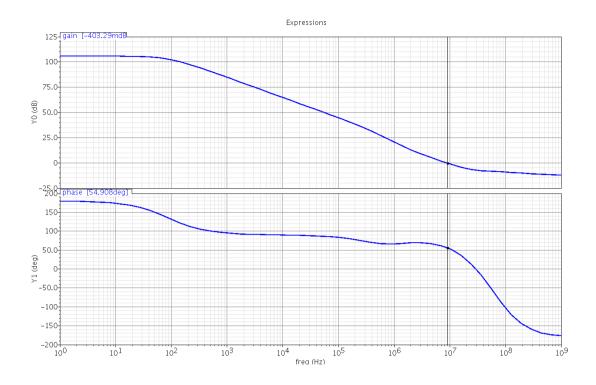

| Figure 5-6 Bode Plot of the ClassAB Op-amp                                                  |

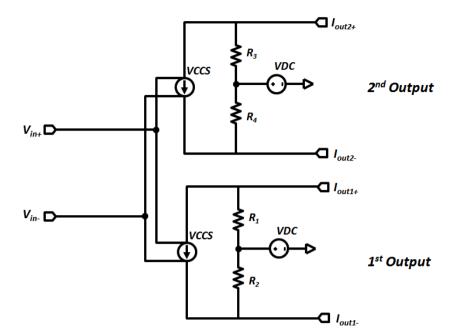

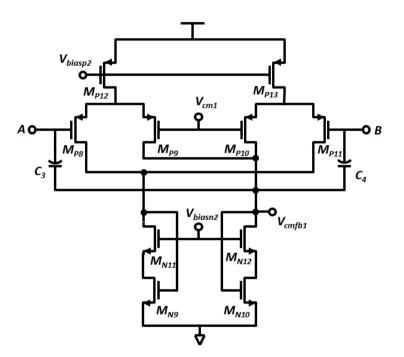

| Figure 5-7 Schematic of Triode Based Multiple-output Transconductor                         |

| Figure 5-8 Accurate Definition of Common Mode Level Using Auxiliary Amplifier 101           |

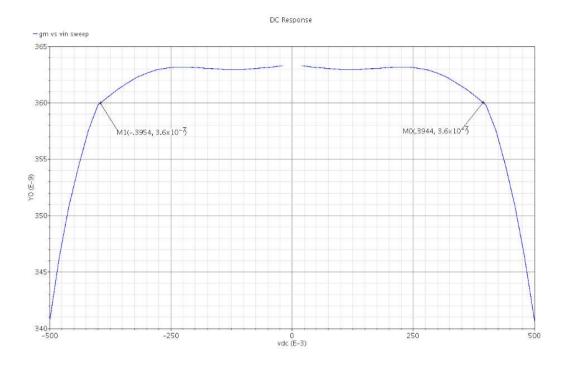

| Figure 5-9 Linear Range Plot of the Multiple Output Transconductor                          |

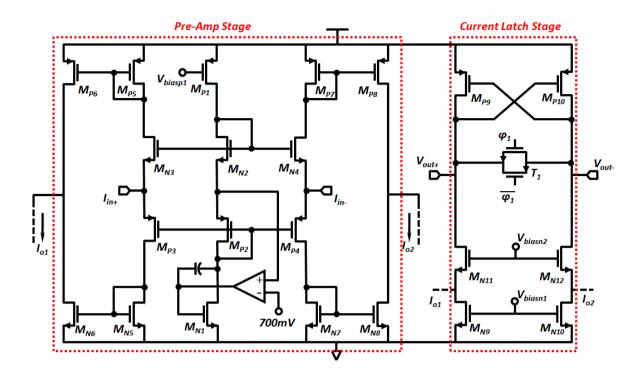

| Figure 5-10 Schematic of the 1-bit Current Latch Quantizer                                  |

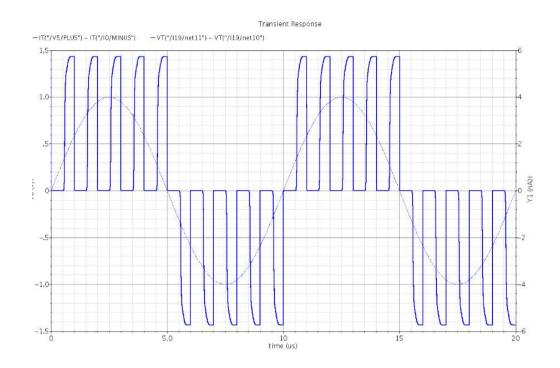

| Figure 5-11 Output Waveform of the Quantizer with 1nA Amplitude Current Input 104           |

| Figure 5-12 Schematic of the Proposed FLRZ DAC Cell                     | 105 |

|-------------------------------------------------------------------------|-----|

| Figure 5-13 Internal Control Signal Generation Circuit                  | 105 |

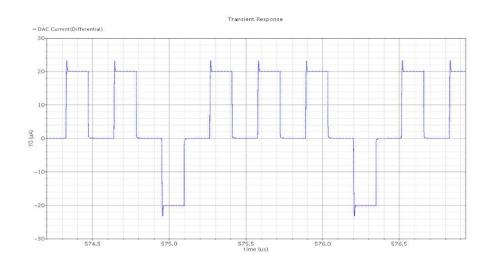

| Figure 5-14 Output Current Waveform of the FLRZ DAC Cell                | 106 |

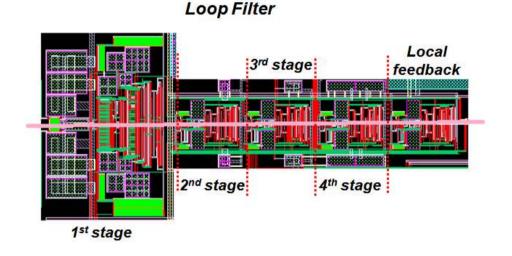

| Figure 5-15 Layout View of Loop Filter                                  | 107 |

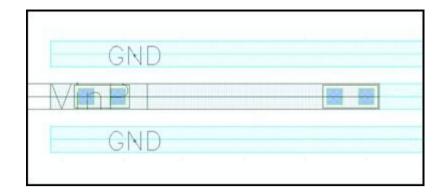

| Figure 5-16 Shielding of Signal Line                                    | 108 |

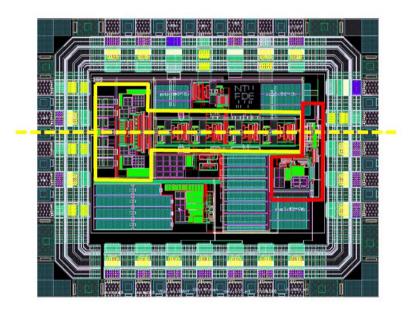

| Figure 5-17 Layout View of Entire Modulator with Pads                   | 108 |

| Figure 5-18 Dynamic Range Plot of the Designed Modulator                | 109 |

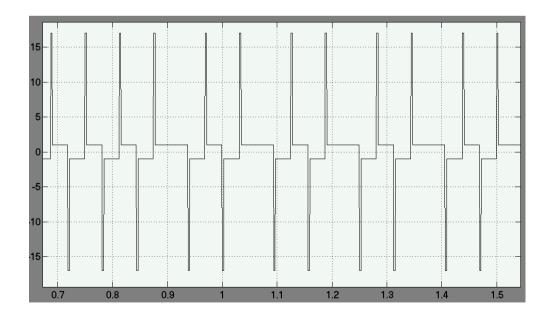

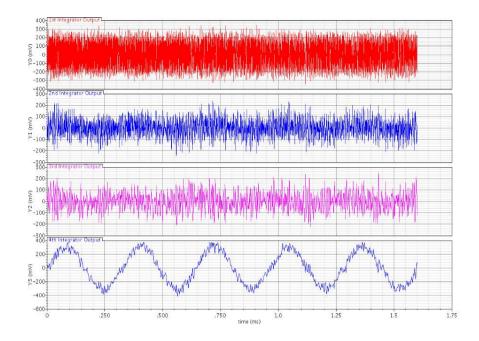

| Figure 5-19 Signal Swing for Internal Nodes (Output of Each Integrator) | 110 |

# LIST OF TABLES

| Table 3-1 Comparison of Single-bit Quantizer and Multi-bit Quantizer        | . 36 |

|-----------------------------------------------------------------------------|------|

| Table 4-1 Comparison of Various Jitter Reduction Techniques                 | . 87 |

| Table 5-1 Comparison of Integrator Implementation Methods                   | . 91 |

| Table 5-2 Circuit Components Values                                         | . 94 |

| Table 5-3 Key Specifications for Op-amp in 1 <sup>st</sup> Stage Integrator | . 95 |

| Table 5-4 Performance Summary of the ClassAB Op-amp                         | . 98 |

| Table 5-5 Performance Summary of the Modulator         1                    | 110  |

| Table 5-6 Comparison of Several Reported Works       1                      | 111  |

# Chapter 1 Introduction

### 1.1 Motivation

Until mid 70's, almost all signal processing was performed in the analog domain. With the advance of very large scale integration (VLSI) technology, implementing sophisticated digital signal processing functions on an integrated chip has become not only possible but also advantageous compared to the traditional analog signal processing. Digital signal processing offers enhanced functionality, increased resolution and higher noise immunity which are key to produce a high performance system. Nowadays, digital signal processing systems have penetrated almost every area of our world, from general consumer markets to military use. Its ubiquitous existence in our life makes this new millennium what we called a 'digital age'. State-of-the-art electronic gadgets like Digital Media Player, Handphone, Laptop, and HDTV etc. are all practical applications of digital processing.

Although the signal processing is done in digital domain, the signals in this world are still analog in nature and this will never change. Thus, interfacing between analog and digital signal is inevitable. This interfacing is what we referred to as Analog-to-Digital (A/D) and Digital-to-Analog (D/A) converters. In fact, it is the bottleneck of the overall system because it determines the accuracy that the entire system can achieve.

Generally, there are two broad categories of data converters, namely, Nyquist rate converter and oversampling converter. Nyquist rate converters generally achieve high speed conversion but with limited resolution. On the other hand, oversampling converters are meant for high resolution applications.  $\Sigma\Delta$  Converter is the most commonly seen oversampling converter.

$\Sigma\Delta$  technique has always been the popular choice for designing high resolution data converters due to the advantage of oversampling and noise shaping. Combined with the invention of switched capacitor technique, in the past decades,  $\Sigma\Delta$  converters are mostly implemented in switched capacitor form, which are also referred to as Discrete Time  $\Sigma\Delta$ Modulator because signal processing is done in discrete time domain. This kind of modulator possesses the advantages of relaxed circuit constraints and complexity, full compatibility with CMOS technology and scalability with sampling rate. However, due to stringent settling requirement on switched capacitor amplifier, it is difficult to extend its input bandwidth to a few megahertz without compromising its achievable resolution. A 5MHz bandwidth DT design has been reported but only with 7 bits of resolution [1].

In recent years, more and more attention has been paid upon implementing  $\Sigma\Delta$  Modulator in continuous time domain (referred as CT  $\Sigma\Delta$  Modulator). In fact this concept is not newfound as the starting concept and first few prototypes of  $\Sigma\Delta$  converter are based on continuous time implementation. By implementing  $\Sigma\Delta$  Modulator in continuous time domain, the speed requirement that was originally imposed on first stage integrator of  $\Sigma\Delta$ modulator in DT implementation has been greatly relaxed. This offers a good prospect for a very power efficient design. Additionally, the inherent implicit anti-aliasing from CT implementation eliminates the need for anti-aliasing filter in the front end, further reducing the circuit complexity and power consumption. In [46], a CT  $\Sigma\Delta$  modulator with an FOM of 0.054pJ/con was reported. This figure is far beyond the capability of DT modulators which normally achieve FOMs in several-pJ/conv range. On the other hand, speed performance of  $\Sigma\Delta$  modulator can be significantly improved due to relaxed speed requirements for integrators. Modulator with 20MHz input bandwidth in 0.13 µm technology with 12 bits of resolution has been designed [2]. This is not practical if DT implementation were to be used.

However, CT  $\Sigma\Delta$  Modulator has its own limitations. First, unlike DT implementations, whose coefficients are determined by capacitor ratios in SC technique, in CT implementations, coefficients are determined by RC product or Gm/C which are subject to significant process variations and mismatches. Hence, stability and performance may suffer. Secondly, due to continuous nature of feedback pulses, excess loop delay becomes an important consideration because it can cause potential instability and performance degradations. Thirdly, due to integration operation of feedback pulse over time, CT modulators are sensitive to feedback related non-idealities. The most severe problem is created by clock jitters. Clock jitter always exists and it can only be minimized by careful clock generation circuit design. It causes non-uniform feedback pulses which are effectively considered as noise directly added to the input. This will add white noise floor to the original signal and subsequently degrade the resolution. It has been shown that jitter noise effect may exceed all other noise sources like quantization noise and circuit noise and become the limiting factor of the modulator design. Thus reduction of clock jitter effect and at the same time creating minimum impact on other aspects of the system's performance becomes an attractive and important research direction.

#### Audio Signal Processing

Figure 1-1 Conventional Audio Signal Processing Chain

Figure 1-1 shows the typical sequence of audio signal processing. The audio signal is first converted to a 1-bit Pulse Density Modulated (PDM) digital signal at an oversampled rate (64f<sub>s</sub>) through an oversampling ADC. Then this 1-bit signal is down-sampled and filtered, generating an output of 44.1kHz/16bits (Pulse Code Modulation or PCM) which is to be stored on disc. When the stored information is to be read out, it is again up-sampled and converted to 1-bit format through multi-bit DAC. This 1-bit code is then low passed, generating analog sound.

The 1-bit coding in front end ADC is the most critical step which directly interfaces between analog sound and digital representation. This step is lossy in nature. It is usually performed by high resolution  $\Sigma\Delta$  Modulator which may be implemented using either single-bit or multi-bit structure. If multi-bit  $\Sigma\Delta$  modulators are used, extra digital signal processing step needs to be performed in order to obtain the 1-bit audio representation. Hence, though multi-bit  $\Sigma\Delta$  modulator achieves better performance, it complicates the system and is less direct than their single-bit counterpart.

In recent years, a new coding format which is called direct stream digital (DSD) is proposed to replace traditional compact disc (CD) [3]. The signal chain architecture is shown in Figure 1-2.

Figure 1-2 Audio Signal Processing Chain for DSD Technology

Instead of storing 44.1 kHz/16bits PCM code, the 1-bit 64 times oversampled PDM code is directly stored and processed. During read out, the 1-bit signal is directly fed to analog low pass filter, generating audio output. By using this structure, several digital processing steps can be removed, and it is believed that higher quality audio signal processing can be

achieved. Also, storing 64f<sub>s</sub>/1bit signal is much more efficient than traditional CD format. In this architecture, 1-bit front end ADC is still the most critical part.

### 1.2 **Objective**

This research aims to investigate the various design trade-offs of Continuous Time  $\Sigma\Delta$ Modulator primarily targeting at audio sensor applications. The primary focus is on the aspects of achieving high performance design (i.e. high speed, high resolution). In the context of this research, achieving high resolution data conversion under strong non-ideal effects is the primary research focus. The most serious issue specifically related to Continuous Time  $\Sigma\Delta$  Modulator-clock jitter noise is to be studied and analyzed in great depth. Various techniques to counteract the effect are to be explored and compared while optimum design methodology and possibly new techniques are to be proposed.

### 1.3 **Thesis Organization**

This thesis presents the theoretical analysis of CT  $\Sigma\Delta$  A/D converters, differential behavioral modeling technique and non-idealities investigation. Timing non-idealities such as excess loop delay, jitter noise are discussed and proposed techniques are introduced. Circuit implementation is carried out as well. The remaining chapters are organized as following.

Chapter 2 introduces the fundamental theories of  $\Sigma\Delta$  converter. Discrete Time approach is first presented. Then Continuous Time design is introduced. Advantages and disadvantages of each type are compared.

Chapter 3 presents the system design approach where major design trade-offs are introduced. Following that, differential behavioral modeling technique is presented, its advantages are demonstrated. With this modeling technique, non-idealities are investigated and their effects are visualized from simulation.

Chapter 4 analyses timing non-idealities in CT  $\Sigma\Delta$  modulators which are key disadvantages of CT implementation over DT counterpart. Clock jitter is examined in great depth. A novel method for clock jitter noise reduction technique named Fixed-Length Return-to-Zero pulse shaping technique is introduced.

Chapter 5 gives an implementation example which is a 4<sup>th</sup> order single-bit Continuous time sigma delta modulator. The entire design flow from topology selection to behavioral modeling, then to circuit implementation and chip layout is elaborated to show the design concept developed in this research.

Chapter 6 concludes the thesis and proposes possible future research directions.

# Chapter 2 Overview of ΣΔ Converters

### 2.1 Sampling and Quantization

#### 2.1.1 Sampling

The most basic operation in a digital system is sampling. An important characteristic of ideal sampling is that sampling in time is a completely reversible process given the condition that the sampled signal is band-limited and the sampling rate is high enough. Figure 2-1 shows a perfectly sampled signal (without aliasing). It is obvious that by low pass filtering the signal, the original signal can be recovered. This means proper sampling would not introduce any distortion to the original signal.

Figure 2-1 Spectral Sampling Operation

For a sampled signal to be re-constructible as in Figure 2-1, aliasing should not happen. This condition is ensured by the famous Nyquist Theorem [4] which states that the sampling rate  $f_s$  has to be at least twice the highest spectral component,  $f_b$ , of the signal, i.e.  $f_s \ge 2^* f_b$ . The sampling rate which satisfies the Nyquist Theorem is called Nyquist Rate. If the sampling rate is much higher than Nyquist Rate, the sampling is called oversampling. The benefit of oversampling will be discussed shortly.

#### 2.1.2 Quantization

Another basic operation in digital systems is called quantization. Different from sampling, quantization operation is a lossy process and hence irreversible. However quantization is inevitable in a digital system as a discretized signal can only be represented by a finite number of discrete levels. The difference between the actual value and the quantized value is called quantization error. The primary objective of ADC design is to minimize this error indeed.

The device that encodes analog signal and produce digital signal output is called a quantizer. The main distinguishing parameter of a quantizer is the number of bit which correlates with the number of output levels. If  $2^{B}$  output levels output is available, the quantizer is called a B-bit quantizer. Quantizer bit is the most important performance indication of a quantizer as it determines the quantization error. As the input signal is quantized to the nearest quantization level, the interval between two quantization levels which is called quantization step width bounds the maximum quantization error. For uniform quantization, quantizer step width is defined as

$$\Delta = \frac{FS}{2^{B-1}} \tag{2.1}$$

where FS denotes the full scale output range. Thus, the quantization error is always bounded within  $\left[-\frac{\Delta}{2}, \frac{\Delta}{2}\right]$ . Obviously, the larger the quantizer bit, the smaller the average quantization error. Mathematically, total quantization noise is proved to be

$$\sigma_e^2 = \frac{\Delta^2}{12} \tag{2.2}$$

In general, quantizer can be divided into two categories according to their number of bits: single-bit quantizer and multi-bit quantizer (Figure 2-2).

Figure 2-2 (a) Single-bit Quantizer (b) Multi-bit Quantizer (c)Single-bit Quantizer Transfer Curve (d) Multi-bit Quantizer Transfer Curve

Obviously, multi-bit quantizer will have much smaller quantization error than single-bit quantizer. However, this is not the only difference between the two quantizers.

As can be seen from the transfer curve (Figure 2-2) of the two quantizers, a noticeable difference between the two is for multi-bit quantizer, its quantizer gain is well defined (usually assumed to be 1) while for single-bit quantizer, its gain varies according to the input signal. This difference is non-trivial and may cause stability and performance difference in  $\Sigma\Delta$  modulator which will be discussed in later section.

# 2.2 ΣΔ ADC Performance Metrics

The performance of an ADC governs how closely the digital signal matches its original analog input and also sets a limit on the fastest input signal the converter can digitize. The former represents the quantization operation of a converter. The latter simply represents the bandwidth of the input signal.

Fundamental differences in operating principle exist between Nyquist rate converter and  $\Sigma\Delta$  converter, thus it is useful to clarify performance parameters that are usually used in characterizing  $\Sigma\Delta$  converter.

Oversampling A/D converters minimize quantization errors through a sequence of samples while Nyquist rate converters do so on a sample to sample basis. Thus, static performance metrics like INL (Integral Nonlinearity) and DNL (Differential Nonlinearity) which measures the sample difference are not appropriate for  $\Sigma\Delta$  converters. Instead, dynamic metrics such as mean square error, signal-to-noise ratio, and dynamic range are used to evaluate the performance of  $\Sigma\Delta$  A/D converters. Some of the important metrics are introduced below.

#### Signal to Noise Ratio (SNR)

SNR defines the ratio between the power of the desired output signal and the power of the output noise. It is to be made clear that this output power defined here is the total power within converter bandwidth excluding the input signal and any harmonics of the input signal. This output noise is also called in-band-noise (IBN).

$$SNR_{dB} = 10 \log_{10} \frac{P_{SIG}}{P_{NOISE}}$$

2.3

10

#### Signal to Noise and Distortion Ratio (SNDR)

SNDR is similar to SNR, but all the undesired contents including all noise sources and non-linear harmonic distortions are incorporated into total noise.

$$SNDR_{dB} = 10 \log_{10} \left( \frac{P_{SIG}}{P_{HARMONICS} + P_{NOISE}} \right)$$

2.4

#### Dynamic Range (DR)

The ratio between the maximum signal amplitude that can be resolved without saturating the converter, and the minimum signal amplitude that can be resolved without being mistaken for noise.

$$DR_{dB} = 10 \log_{10} \left( \frac{P_{SIG,MAX}}{P_{SIG,MIN}} \right)$$

2.5

#### Effective Number of Bits (ENOB)

The effective resolution of the converter, with all non-ideal effects included. This parameter is the equivalent in bits to the SNDR.

$$ENOB = \frac{SNDR - 1.76}{6.02}$$

2.6

#### Spurious Free Dynamic Range (SFDR)

SFDR defines as the ratio of the signal power to the power of the strongest spectral tone. Its importance strongly depends on the application, since it dominates the resulting ADC linearity.

#### Figure of Merit (FOM)

This performance gauge serves as a useful tool for comparison among different implementations. It does not reflect a scientific relation between performance and power. Instead, it sets a straightforward comparison standard by combining a few important specifications in a single number. As a matter of fact, there are several different definitions of FOM. [5] summarizes and makes inspirational comments among them. The three most important FOMs are FOM related to thermal noise, FOM related to signal resolution and FOM including distortion. The primary difference is how the performance is quantified. These three FOMs use dynamic range, ENOB and SNDR respectively. For  $\Sigma\Delta$  A/D converters, FOM including distortions provides the best way for fair comparison. In this research, we also adopt this definition. It can be expressed as following:

$$FOM = \frac{P}{SNDR \cdot BW}$$

2.7

### 2.3 ΣΔ Modulator Operating Principles

#### 2.3.1 Oversampling

As introduced in previous section, for a sampling process to be performed without loss of information, Nyquist Theorem must be satisfied which means  $f_s \ge 2^* f_b$ . Thus normal Nyquist rate ADC must be band limited, which is ensured by the use of anti-aliasing filter (Figure 2-3). Usually the requirements on the anti-aliasing filter are very stringent, such as very narrow transition band, high attenuation in stop band and very small pass band ripple etc. All of these result in circuitry that is complex, area consuming and power hungry.

Figure 2-3 Conventional ADC Structure

One way of improving the situation is to increase the sampling rate to many times of its Nyquist rate. This is called oversampling. A measure of degree of oversampling is called oversampling ratio which is the ratio of actual sampling rate to its Nyquist rate, i.e.

$$OSR = \frac{f_s}{f_N}$$

2.8

where  $f_N$  denotes the Nyquist rate. To understand why oversampling helps to relax the requirements for anti-aliasing filter, spectrum of an oversampled signal is shown in Figure 2-4.

Figure 2-4 PSD of an Oversampled Signal

It is evident that the images of the signal band are not so close to one another, and hence the specifications of the anti-aliasing filter can be much relaxed.

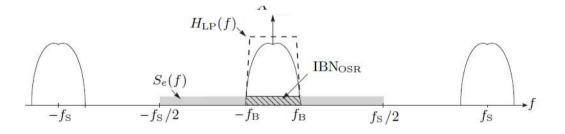

However, this is not the only benefit that can be obtained from oversampling. A more important advantage of oversampling is that oversampling helps to reduce in band noise.

This is due to the fact that the total quantization noise power is independent from the sampling frequency which can be seen from Eqn. 2-2. With the increase of sampling frequency, quantization noise is more and more flatten out across the entire band. Figure 2-5 shows the effect graphically.

Figure 2-5 Spectral Effect of Oversampling

Thus the integrated in-band quantization noise can be calculated by

$$IBN_{OSR} = \int_{0}^{f_B} S_e(f)df = \frac{\Delta^2 * f_B}{12 * f_S} = \frac{\Delta^2}{6} \frac{1}{OSR}$$

2.9

This effect greatly helps to increase the achievable maximum SNR, which can be calculated as

$$SNR_{OSR} = 10 \log_{10} \left( \frac{P_{SIG|FS/2}}{IBN_{OSR}} \right) = 6.02B_{INT} + 10\log_{10}OSR + 1.76 (dB)$$

2.10

here  $P_{SIG|FS/2}$  represents the power of largest sinusoidal input signal which has a magnitude of FS/2.

From Eqn.2.9, it can be inferred theoretically, every doubling of oversampling ratio will increase the maximum SNR by approximately 3dB or 0.5-bit.

Although oversampling is useful for reduction of in band noise, itself alone cannot make a highly efficient system. The benefit that can be obtained from enhancement of resolution may be offset by the increase in sampling rate, which corresponds to loss in conversion speed and an increase in power consumption. Fortunately, when combined with noise shaping technique, its advantage can be significant enough to make a great impact.

#### **2.3.2** Oversampled Noise Shaping Converters: $\Sigma \Delta$ ADC

A further improvement in SNR can be achieved by further suppressing in band noise and at the same time preserving the desired signal, i.e. high pass on quantization noise, low pass on desired signal. Conventional Nyquist rate converters or oversampling converters are pure open loop systems, thus they cannot implement different filter function on signal and noise at the same time. However, this can be easily done in a closed loop systems. With additional controller in feedback or feed-forward path, different shaping characteristics can be obtained for quantization noise and the desired signal, which are defined respectively as noise transfer function (NTF) and signal transfer function (STF). This is the basic concept of noise shaping. Moreover, when oversampling concept and noise-shaping concept are combined, very significant noise suppression can be achieved, forming the well-know  $\Sigma\Delta$  converter.

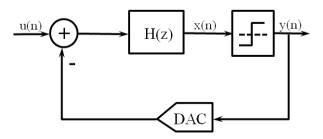

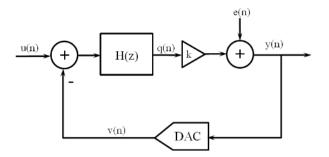

Figure 2-6 Noise-Shaped Oversampling Modulator

Figure 2-7 Linearized Model of  $\Sigma\Delta$  Modulator

$\Sigma\Delta$  modulator is a highly non-linear system due to the presence of quantizer (Figure 2-6) which is a strong non-linear element inside the loop. For such non-linear system, rigorous analytical analysis has proven difficult or even impossible. Thus some linearization technique is required. The linearized model shown in Figure 2-7 is simple enough to provide some insights into the operation of the  $\Sigma\Delta$  modulator, and also gives a rough estimation of the dynamic range performance of the modulator. [6]

Based on the linear model, the transfer function of the modulator can be written as

$$Y(z) = \frac{H(z)}{1 + H(z)}U(z) + \frac{1}{1 + H(z)}E_Q(z)$$

2.11

Here the gain factor,  $\frac{H(z)}{1+H(z)}$ , of the input signal U(z) is the signal transfer function (STF). And the gain factor,  $\frac{1}{1+H(z)}$ , of the quantization noise  $E_Q(z)$  is the noise transfer function (NTF).

Note: derivation of eqn. 2-11 bears the assumption that input signal and feedback signal are processed by the same loop filter function H(z). If it is not the case, STF would become  $\frac{H_1(z)}{1+H_0(z)}$  and NTF would become  $\frac{1}{1+H_0(z)}$ . However, the in-band characteristic doesn't change much for the two cases.

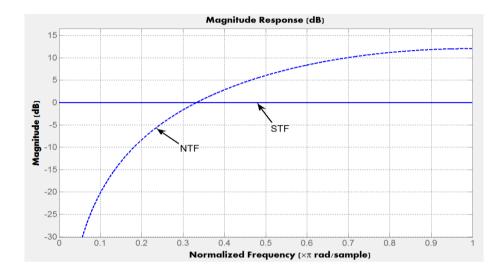

We may note that if H(z) represents a low pass transfer characteristic, and has a very large gain within the band of interest, |NTF| would be nearly zero while |STF| would be nearly 1 within signal band. Figure 2-8 shows the stated NTF and STF characteristic. The noise shaping is clearly visible.

Figure 2-8 NTF and STF of a Second Order  $\Sigma\Delta$  Modulator

If the non-idealities of forward path ADC and feedback DAC are included, the following model results as shown in Figure 2-9. [7]

Figure 2-9  $\Sigma\Delta$  Modulator Model Including Non-idealities

And this model gives rise to the following transfer function

$$Y(z) = \frac{H(z)}{1 + H(z)} \left( U(z) - E_D(z) \right) + \frac{1}{1 + H(z)} \left( E_Q(z) + E_{Q2}(z) \right)$$

2.12

where the  $E_D(z)$  denotes the feedback DAC error and  $E_{Q2}(z)$  denotes the forward path ADC error.

From this model, we can draw an important conclusion. The non-idealities of the forward path ADC is noise shaped, just like the quantization noise. However, the non-idealities of the feedback path DAC are not noise shaped and directly corrupt the input signal. This insight is important in the sense that it tells the designer where the design emphasis should be put. We can conclude feedback DAC determines the performance of the whole modulator and must be designed with special care. The requirement for the ADC (quantizer) on the other hand is quite relaxed. Hence, heavy research attention into reducing DAC non-idealities is justified.

#### 2.3.3 High Order Noise Shaping

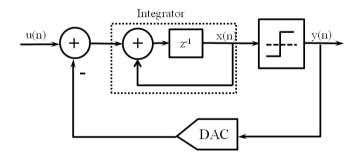

The simplest  $\Sigma\Delta$  modulator is a first order  $\Sigma\Delta$  modulator, as shown in Figure 2-10.

Figure 2-10 First Order  $\Sigma\Delta$  Modulator

The first order  $\Sigma\Delta$  modulator makes use of a first order loop filter with filter transfer function  $H(z) = \frac{1}{z-1}$ . As shown in the above figure, this low pass loop filter is realized using a single stage integrator. With the simple ideal linearized model, we may derive the transfer function of this first order modulator:

$$Y(z) = z^{-1} \cdot U(z) + (1 - z^{-1})E_Q(z)$$

2.13

Where STF= $z^{-1}$  and NTF= $1 - z^{-1}$ .

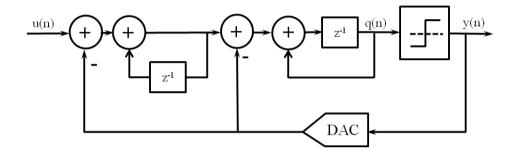

The first order  $\Sigma\Delta$  modulator can be extended to second order by cascading another integrator stage onto the original integrator as shown in Figure 2-11.

Figure 2-11 Second Order  $\Sigma\Delta$  Modulator

And similarly, its transfer function is derived as

$$Y(z) = z^{-1} \cdot X(z) + (1 - z^{-1})^2 E_Q(z)$$

2.14

where STF is 1, and NTF is  $(1 - z^{-1})^2$ .

A simple comparison of first and second order transfer function reveals how the modulator order affects the noise shaping effectiveness.

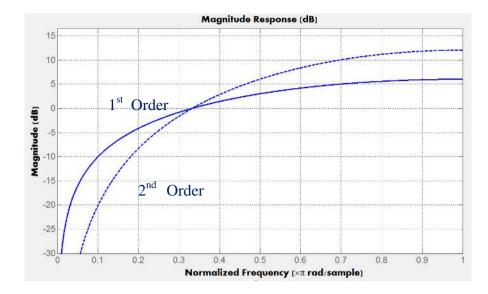

In both first order and second order modulators, within frequency band of interest, |STF| has the same value 1. But the |NTF| for  $1^{st}$  order and  $2^{nd}$  order are different. The difference is demonstrated by the frequency domain plot of the |NTF| for the two modulators as shown in Figure 2-12.

Figure 2-12 NTF of First Order and Second Order  $\Sigma\Delta$  Modulator

It is obvious from the above plot that at low frequencies, 2<sup>nd</sup> order modulator achieves better in band noise suppression. However at higher frequencies, the 2<sup>nd</sup> order modulators tend to amplify noise much more significantly than 1<sup>st</sup> order counterpart. This out of band amplification of noise is called out of band gain (OBG) of NTF. OBG is non-trivial although its effect is outside the signal bandwidth. A large OBG may cause high frequency noise to flood the modulator and create potential stability problem. This problem will be discussed in latter sections.

Quantitative analysis of an L<sup>th</sup> order modulator (L=1, 2, 3...) is given next to quantify the effect of modulator order on noise shaping performance. For an L<sup>th</sup> order  $\Sigma\Delta$  modulator, we assume the signal transfer function is expressed STF=1(non-delaying modulator), and the noise transfer functions as  $NTF = (1 - z^{-1})^L$ .

From the NTF given, total in band noise of an  $L^{th}$  order  $\Sigma\Delta$  modulator can be estimated.

Since the quantization noise power spectrum density is calculated as  $S_e(f) = \frac{\Delta^2}{6 \cdot f_s}$

Quantization noise with noise shaping is then

$$S_{eL}(f) = S_e(f) |NTF|^2 = \frac{\Delta^2}{6 \cdot f_s} 2^L sin^L(\pi f/f_s)$$

2.15

where NTF is expressed in frequency domain as

$$NTF = (1 - z^{-1})^{L}|_{z=e^{j2\pi f/f_{s}}} = (1 - e^{-j2\pi f/f_{s}})^{L} = (-2je^{\frac{j\pi f}{f_{s}}}sin(\frac{\pi f}{f_{s}}))^{L}$$

2.16

Thus the total in band noise of the modulator can be estimated as

$$P_{Q} = \int_{0}^{f_{B}} S_{eL}(f) df = \int_{0}^{f_{B}} \frac{\Delta^{2}}{6 \cdot f_{s}} 2^{L} sin^{L} \left(\frac{\pi f}{f_{s}}\right) df \approx \int_{0}^{f_{B}} \frac{\Delta^{2}}{6 \cdot f_{s}} 2^{L} \left(\frac{\pi f}{f_{s}}\right)^{L} df$$

$$= \frac{\Delta^{2} \pi^{2L}}{12 \cdot (2L+1)} \left(\frac{2f_{B}}{f_{s}}\right)^{2L+1}$$

2.17

assuming  $\frac{f_B}{f_s} \ll 1$ , i.e. large oversampling ratio. Suppose the modulator has a n-bit quantizer, the full scale range signal can be approximated as

$$P_{SIG|\frac{FS}{2}} = \frac{A^2}{2} = \frac{(2^n - 1)^2 \Delta^2}{8}$$

2.18

Thus, the maximum dynamic range for this L<sup>th</sup> order modulator is

$$DR = \frac{P_{SIG|\frac{FS}{2}}}{P_Q} = \frac{3}{2} \frac{2L+1}{\pi^{2L}} OSR^{2L+1} (2^n - 1)^2$$

2.19

This important expression shows  $\Sigma\Delta$  technique has much more aggressive noise shaping compare to simply oversampling technique. For example, with a first order noise shaping, every doubling of OSR will improve DR and SNR by 9 dB or 1.5 bits. In comparison, as mentioned in the above section, for pure OSR technique, every doubling of OSR only creates 0.5 bit of resolution gain. By increasing the modulator order, more noise shaped effects can be obtained. However, this does not mean modulator order can be increased without limit. As modulator order becomes higher, overloading effects (due to high NTF out-of-band gain) become more pronounced, consuming usable dynamic range, creating potential instability problem. Thus modulator's input range must be limited to ensure stability. This effect offsets the benefit brought from high order noise shaping and more so when the order goes higher and higher. Thus the achievable SNR will not increase without bound. Generally speaking, modulators order higher than 5 are not efficient and difficult to design due to stability concern.

#### 2.3.4 Stability

Stability is defined as a modulator condition, where all internal state variables, which are the integrator outputs, remain bounded over time [8]. Research studies have shown that modulator order higher than two is only conditionally stable. In reality, to ensure stability, the integrator gain has to be scaled down with less aggressive noise shaping.

The reason for instability to occur can be twofold: the modulator input signal is too strong or the power of the out-of-band quantization noise is too high. For this reason, stability is always ensured in two ways. First is to limit the input signal amplitude. Unfortunately, there are no strict criteria as for how to ensure a clear bound on input signal. It is common belief that extensive experiments that constitute of input signal of different amplitude and different frequency must be carried out. Furthermore, long simulation sequence need to be taken since some of the instability can only be observed after long simulation. Another simulation method is presented in [20], where the author proposes that a ramp input to the quantizer and observe the quantizer input. The moment the quantizer input amplitude exceed 10, the input amplitude is found out and assumed to be the maximum stable amplitude. The author claimed this method gives approximately same results as previous exhaustive simulation method while requiring much less simulation effort.

The second approach is to limit NTF out-of-band gain. This restricts the potential harmful effects of out-of-band quantization noise but at the expense of in-band noise shaping. Hence, theoretical signal-to-noise ratio as predicted in linearized model (Eqn. 2.19) cannot be achieved in practice. As a rule of thumb, in [16], it has been proposed to limit the out-of-band gain of single-loop single-bit modulators to be within 1.5. For multi-bit modulators, their out-of-band gain can be much relaxed to higher value. Values around 3.5 are achievable with proper design.

Besides simulation method, some other methods also exist for stability check. In [39], the method of root-locus plots has been adopted. This method is useful because it provide a closer insight into the behavior of the chosen modulator. This method is based on the linear approach of a strongly nonlinear modulator, especially single bit modulators. In this model, quantizer block is regarded as a variable gain block which is not defined in the case of a single-bit quantizer, and root-locus plot of the loop can be determined. To ensure stability, the root-locus must not exit the unit circle. The boundary condition can thus be found and hence the minimum quantizer gain. However, it should be noted that root-locus is only approximate approach and it still needs to be confirmed by behavioral simulation.

### 2.4 Continuous Time ΣΔ Modulators

The explanations and examples discussed in previous sections are all in z-domain. This is with the assumption that the  $\Sigma\Delta$  modulator is implemented using switched-capacitor (SC) technology. And this type of modulator is operated in discrete time domain. This is because  $\Sigma\Delta$  modulators implemented using SC technology is most popular during the last few decades, thus most theories and analysis are developed for discrete time implementations. Continuous time  $\Sigma\Delta$  modulators, although not entirely new, is not as well studied as their DT counterpart. However, as its name reveals, it still belongs to the  $\Sigma\Delta$  modulator family, hence most concepts and understandings introduced thus far also applies to continuous time (CT)  $\Sigma\Delta$  modulators, especially the noise shaping characteristics.

#### 2.4.1 Theory of CT Modulators

Due to the presence of a sampler inside the loop, continuous time sigma modulator is inherently discrete [9]. This means both types of modulator may be analyzed in discrete time domain. Despite of this, the fact that continuous time filter exists in the system makes the intuitive analysis of these two types of modulators quite different from each other. For DT modulators, analysis is usually done in z-domain as the entire modulator is sampled system. For CT modulators, the loop filter is implemented in continuous time domain, thus s-domain analysis like Laplace transform is mostly implemented. Although as proposed in [10], a complete mapping between CT  $\Sigma\Delta$  modulator and DT  $\Sigma\Delta$ modulator is possible, the calculation is time consuming and what is more important, not all non-idealities can be migrated to discrete time domain. Thus, most analysis for CT  $\Sigma\Delta$ modulators is still done in continuous time domain.

The primary difference between a DT modulator and CT modulator is where the sampling takes place. As can be seen in\_Figure 2-13, for DT modulator, sampling takes place at the input, thus any sampling non-idealities directly affect the modulator performance. Clearly, the upfront sampler in a DT modulator is the bottleneck of the entire system. On the contrary, sampling action takes place inside the loop for CT modulator, more

specifically, just before the quantizer. This is where noise suppression has the most significant effect. Thus, sampling errors introduced here are mostly noise suppressed and hence its performance is of no particular concern from system design point of view.

Figure 2-13 (a) DT  $\Sigma\Delta$  Modulator (b) CT  $\Sigma\Delta$  Modulator

However, as shown in section 2.3.2, non-idealities introduced by feedback DAC are not noise-shaped. And this problem gets aggravated for CT modulators because the modulator operation depends on continuous integration of DAC output over entire clock period. From signal processing point of view, the DAC feedback pulse is convoluted with loop filter impulse response in time domain to generate quantizer input signal. Thus the exact shape of feedback DAC is quite important. While for DT modulators, the settling requirement is more important. As long as the feedback charge is transferred within half of a clock period and output value settles well, the loop filter output is correct. Hence, exact feedback DAC pulse shape is not important. It is this difference that makes CT modulator more vulnerable to feedback pulse related problem such as finite rise/fall time, clock jitter etc.

Due to above discussed difference between DT and CT modulators, the implementation consideration for CT  $\Sigma\Delta$  modulators is somewhat different from DT modulators. In

discussion of structure selection and tradeoff which comes in later section, special considerations for CT implementations are explicitly stated.

### **2.4.2** Features of Continuous Time $\Sigma\Delta$ Modulators

In recent years, as the need for low power low voltage, high bandwidth design becomes higher, discrete time design of  $\Sigma\Delta$  modulator reveals severe limitations. On the other hand, their continuous time counterpart shows features which seem promising to resolve those issues. This explains why in recent years, more and more researchers turn their attention to this particular area.

#### Potential for Wideband Low Power Design

In a typical DT  $\Sigma\Delta$  modulator design, due to stringent settling requirement of a SC integrator (input and output voltage needs to settle to a specific tolerance level within half a clock period), the op-amp used in a typical integrator is required to have a gain bandwidth product of over 8 times of sampling frequency. This severely restricts the highest bandwidth the modulator can achieve. Also, the high GBW requirement means high power dissipation in the op-amp.

On the other hand, in CT  $\Sigma\Delta$  modulator design, the GBW requirement is very much relaxed. This is due to the fact that the feedback pulse is continuously fed into loop filter during the entire clock period and its output does not attempt to switch instantaneously as in the case of a switch-capacitor integrator. Figure 2-14 shows a representative output waveform employing CT waveform with DT feedback as reference. The voltage level in the integrator is not important, instead, the total charge being transferred is more of our concern. As a rule of thumb, GBW of two to three times of the sampling frequency is shown to satisfy the settling requirements for most feedback waveforms. Even lower values of GBW are possible with acceptable performance impact [11]. A work by [12] is even able to push the GBW requirement in CT  $\Sigma\Delta$  modulators to be below sampling frequency.

Figure 2-14 Integrator Output Current with CT Feedback vs. DT Feedback