Linköping Studies in Science and Technology Dissertations, No. 1688

### Design of High-Speed Time-Interleaved Delta-Sigma D/A Converters

Ameya Bhide

Division of Integrated Circuits and Systems Department of Electrical Engineering (ISY) Linköping University SE-581 83 Linköping, Sweden

Linköping 2015

Design of High-Speed Time-Interleaved Delta-Sigma D/A Converters Copyright © 2015 Ameya Bhide ISBN 978-91-7519-017-4 ISSN 0345-7524 Printed by LiU-Tryck, Linköping, Sweden, 2015

### Abstract

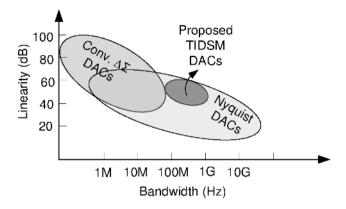

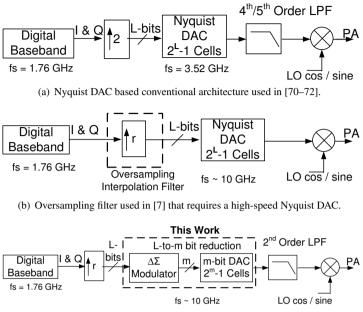

Digital-to-analog (D/A) converters (or DACs) are one the fundamental building blocks of wireless transmitters. In order to support the increasing demand for high-data-rate communication, a large bandwidth is required from the DAC. With the advances in CMOS scaling, there is an increasing trend of moving a large part of the transceiver functionality to the digital domain in order to reduce the analog complexity and allow easy reconfiguration for multiple radio standards.  $\Delta\Sigma$  DACs can fit very well into this trend of digital architectures as they contain a large digital signal processing component and offer two advantages over the traditionally used Nyquist DACs. Firstly, the number of DAC unit current cells is reduced which relaxes their matching and output impedance requirements and secondly, the reconstruction filter order is reduced.

Achieving a large bandwidth from  $\Delta\Sigma$  DACs requires a very high operating frequency of many-GHz from the digital blocks due to the oversampling involved. This can be very challenging to achieve using conventional  $\Delta\Sigma$  DAC architectures, even in nanometer CMOS processes. Time-interleaved  $\Delta\Sigma$  (TIDSM) DACs have the potential of improving the bandwidth and sampling rate by relaxing the speed of the individual channels. However, they have received only some attention over the past decade and very few previous works been reported on this topic. Hence, the aim of this dissertation is to investigate architectural and circuit techniques that can further enhance the bandwidth and sampling rate of TIDSM DACs.

The first work is an 8-GS/s interleaved  $\Delta\Sigma$  DAC prototype IC with 200-MHz bandwidth implemented in 65-nm CMOS. The high sampling rate is achieved by a two-channel interleaved MASH 1-1 digital  $\Delta\Sigma$  modulator with 3-bit output, resulting in a highly digital DAC with only seven current cells. Two-channel interleaving allows the use of a single clock for both the logic and the final multiplexing. This requires each channel to operate at half the sampling rate i.e. 4 GHz. This is enabled by a high-speed pipelined MASH structure with robust static logic. Measurement results from the prototype show that the DAC achieves 200-MHz bandwidth, -57-dBc IM3 and 26-dB SNDR, with a power consumption of 68-mW at 1-V digital and 1.2-V analog supplies. This architecture shows good potential for use in the transmitter baseband. While a good linearity is obtained from this DAC, the SNDR is found to be limited by the testing setup for sending high-speed digital data into the prototype.

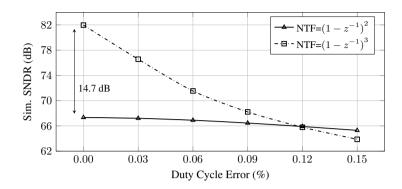

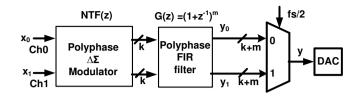

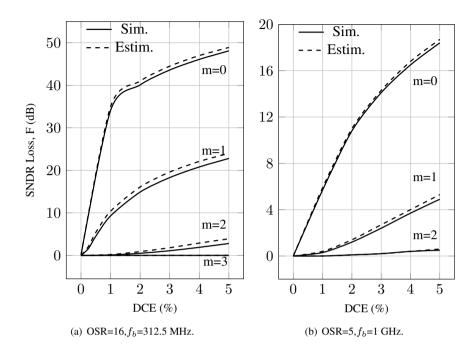

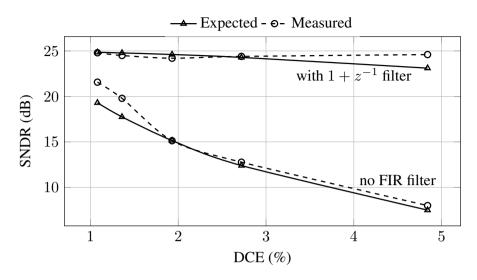

The performance of a two-channel interleaved  $\Delta\Sigma$  DAC is found to be very sensitive to the duty-cycle of the half-rate clock. The second work analyzes this effect mathematically and presents a new closed-form expression for the SNDR loss of two-channel DACs due to the duty cycle error (DCE) for a noise transfer function (NTF) of  $(1 - z^{-1})^n$ . It is shown that a low-order FIR filter after the modulator helps to mitigate this problem. A closed-form expression for the SNDR loss in the presence of this filter is also developed. These expressions are useful for choosing a suitable modulator and filter order for an interleaved  $\Delta\Sigma$  DAC in the early stage of the design process. A comparison between the FIR filter and compensation techniques for DCE mitigation is also presented.

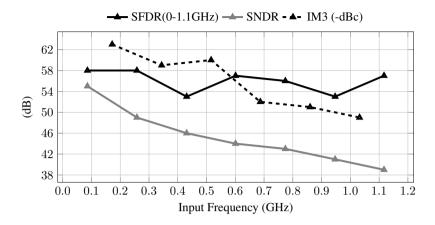

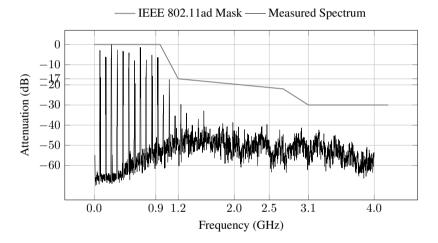

The final work is a 11 GS/s 1.1 GHz bandwidth time-interleaved  $\Delta\Sigma$  DAC prototype IC in 65-nm CMOS for the 60-GHz radio baseband. The high sampling rate is again achieved by using a two-channel interleaved MASH 1-1 architecture with a 4-bit output i.e only fifteen analog current cells. The single clock architecture for the logic and the multiplexing requires each channel to operate at 5.5 GHz. To enable this, a new look-ahead technique is proposed that decouples the two channels within the modulator feedback path thereby improving the speed as compared to conventional loop-unrolling. Full speed DAC testing is enabled by an on-chip 1 Kb memory whose read path also operates at 5.5 GHz. Measurement results from the prototype show that the  $\Delta\Sigma$  DAC achieves >53 dB SFDR, < -49 dBc IM3 and 39 dB SNDR within a 1.1 GHz bandwidth while consuming 117 mW from 1 V digital/1.2 V analog supplies. The proposed  $\Delta\Sigma$  DAC can satisfy the spectral mask of the 60-GHz radio IEEE 802.11ad WiGig standard with a second order reconstruction filter.

# Populärvetenskaplig sammanfattning

Digital-till-analog omvandlare (eller DA-omvandlare) är ett grundläggande block för trådlösa sändare. För att stödja de ständigt ökande kraven på höghastighetskommunikation så måste DA-omvandlaren ha en hög bandbredd. I och med att CMOS fortsätter skalas ned så blir det mer attraktivt att flytta en större del av sändtagaren till den digitala domänen för att reducera den analoga komplexiteten och tillåta enkel omkonfigurering för att stöda flera radiostandarder.  $\Delta\Sigma$  DA-omvandlare kan passa väl in i denna trend av digitala arkitekturer eftersom de innehåller en stor digital signalbehandlingsdel samt erbjuder två fördelar över de traditionellt sett använda Nyquist DA-omvandlarna. För det första, antalet enhetsströmceller reduceras vilket lättar på deras matchnings och utimpedans krav och för det andra så reduceras filter komplexiteten på rekonstruktionsfiltret.

För att få en hög bandbredd på  $\Delta\Sigma$  DA-omvandlare krävs en väldigt hög operationsfrekvens på flera GHz för det digitala blocket på grund av översamplingen. Detta kan vara väldigt utmanande i konventionella  $\Delta\Sigma$  DA-omvandlararkitekturer, även i nanometer CMOS processer. Sammanflätade  $\Delta\Sigma$  DA-omvandlare har potential att förbättra bandbredden och samplingshastigheten genom att lätta på hastighetskraven på enskilda kanaler. Dock har de inte fått stor uppmärksamhet det senaste decenniet och väldigt få arbeten har rapporterats inom området. Därför är målet med denna avhandling att undersöka arkitekturer och kretstekniker som kan förbättra både bandbredden och samplingshastigheten av sammanflätade  $\Delta\Sigma$  DA-omvandlare.

Det första bidraget i avhandlingen är en integrerad 8 GS/s sammanflätad  $\Delta\Sigma$ DA-omvandlare med 200 MHz bandbredd implementerad i 65-nm CMOS. Den höga samplingshastigheten uppnås genom att sammanfläta två kanaler med varsin MASH 1-1 digital 3-bitars  $\Delta\Sigma$  modulator, vilket resulterar i en till hög grad digital DA-omvandlare med enbart sju enhetsströmceller. Prestandan av den tvåkanals sammanflätade  $\Delta\Sigma$  DA-omvandlaren finnes väldigt känslig för driftcykelfel. Detta fel är matematiskt analyserat och presenteras tillsammans med tekniker för att minska driftcykelfelets påverkan i det andra bidraget. Det sista bidraget är en integrerad 11 GS/s 1.1 GHz bandbredd tvåkanals sammanflätad  $\Delta\Sigma$  DA-omvandlare i 65-nm CMOS. Den höga samplingshastigheten uppnås återigen genom att sammanfläta två MASH 1-1 arkitekturer med enbart femton enhetsströmceller. Den höga hastigheten uppnås genom en ny look-ahead teknik som reducerar den kritiska linjen av integratorn till enbart en adderare. Den föreslagna  $\Delta\Sigma$  DA-omvandlaren kan uppfylla spektrummasken av 60-GHz radiostandarden IEEE 802.11ad WiGig med ett andra ordningens rekonstruktionsfilter.

## Preface

This dissertation presents the research work performed during the period March 2010 – June 2015 at the Division of Integrated Circuits & Systems, Department of Electrical Engineering, Linköping University, Sweden. The main contributions of this dissertation are as follows:

- Design and implementation of an 200-MHz bandwidth 8-GS/s time-interleaved MASH 1-1 ΔΣ DAC in 65-nm CMOS. A comparative analysis of different logic styles for achieving a high sampling rate is also performed.

- A mathematical analysis of the effect of duty cycle error on the performance of two-channel time-interleaved  $\Delta\Sigma$  DACs. The effectiveness of different error mitigation techniques is also studied.

- Design and implementation of an 1.1-GHz bandwidth 11-GS/s Time-interleaved MASH 1-1  $\Delta\Sigma$  DAC in 65-nm CMOS for 60-GHz radio applications. A fast look-ahead technique is proposed for the interleaved MASH modulator.

- Design and implementation of a 1-Kb memory in 65-nm CMOS with a 5.5 GHz read path to enable the testing of high-speed DACs.

The contents of this dissertation are based on the following publications:

- Paper I A. Bhide, O. E. Najari, B. Mesgarzadeh and A. Alvandpour, "An 8-GS/s 200-MHz Bandwidth 68-mW ΔΣ DAC in 65-nm CMOS", *IEEE Transactions on Circuits and Systems-II: Express Briefs*, vol. 60, no. 7, pp. 387-391, July 2013.

- Paper II A. Bhide, A. Ojani and A. Alvandpour, "Effect of Clock Duty Cycle Error on Two-channel Interleaved ΔΣ DACs", *IEEE Transactions on Circuits and Systems-II: Express Briefs*, vol. 62, no. 7, pp. 646-650, July 2015.

- Paper III A. Bhide and A. Alvandpour, "A 11-GS/s 1.1-GHz Bandwidth Interleaved ΔΣ DAC for 60-GHz Radio in 65-nm CMOS", *IEEE Journal of Solid State Circuits (Accepted for publication)*, DOI: 10.1109/JSSC.2015.2460375.

- Paper IV A. Bhide and A. Alvandpour, "Critical Path Analysis of Twochannel Interleaved Digital MASH ΔΣ Modulators", 31<sup>st</sup> IEEE NORCHIP Conference, Vilnius, Lithuania, pp. 1-4, Nov. 2013.

- Paper V A. Bhide and A. Alvandpour, "Timing Challenges in High-speed Interleaved ΔΣ DACs", 14<sup>th</sup> International Symposium on Integrated Circuits, Singapore, pp. 1-4, Dec. 2014.

The following paper was also published during this period which is outside the scope of this dissertation:

• D. Zhang, **A. Bhide** and A. Alvandpour, "A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-µm CMOS for Medical Implant Devices", *IEEE Journal of Solid State Circuits*, vol. 47, no. 7, pp. 1585-1593, July 2012.

# Acknowledgments

This dissertation would have not been possible without the support, encouragement and the guidance of many people. I would like to express my deepest gratitude and thanks to them.

- I would like to thank my supervisor, Professor Atila Alvandpour for giving me this opportunity to pursue PhD studies and his guidance and support. He really knows how to inspire and motivate his students.

- The senior members at ICS and EK for sharing their technical knowledge : Prof. Emer. Christer Svensson, Asst. Prof. Behzad Mesgarzadeh, Adj. Prof. Ted Johansson, Universitetslektor Dr. J. Jacob Wikner, Assoc. Prof. Jerzy Dabrowski and Dr. Christer Jansson.

- Arta Alvandpour, Research Engineer at ICS for all his help with the equipment and hardware issues.

- All the former and current administrators at ICS for their help: Anna Folkesson, Jenny Stendahl, Maria Hamnér and Gunnel Hässler.

- The former and current PhD students at ICS for providing a very friendly and collaborative environment: Daniel Svärd (LISP/SKILL expert), Dr. Dai Zhang (always cool), Dr. Amin Ojani (always in office), Dr. Jonas Fritzin (impedance matching expert), Dr. Ali Fazli Yeknami, Dr. Fahad Qazi, Martin Nielsen-Lönn (makes PCBs at home and translator in the group), Omid E. Najari (always smiling), Tai Quoc Duong (always looking worried), Keirang Chen, Dr. Timmy Sundström, Vishnu Unnikrishnan, Tekn. Lic. Prakash Harikumar, Dr. Nadeem Afzal and Dr. Anu K.M. Pillai.

- TUS Team for all the support with the computing environment.

- Bo Ygfors for lending the Tektronix pattern generator without which measurements of the first chip would not have been possible.

- My wife Priyanka, for all the encouragement, patience and understanding, without which this dissertation would not have been possible. My daughter, Tanaya for always bringing a smile with her antics.

- Aai and Baba for their unconditional love and support due to which I have been able to reach this far. Also, my sister Ashlesha for all the affection.

- My in-laws for always wishing me the best in my endeavours.

- My friends for their support. A deepest thanks to the gang for always being there. A big thanks to the "CDTG-SoC" lunch table friends for the good times.

Ameya Bhide Linköping, July 2015

# Contents

| Intr | oduction                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Characteristics of Nyquist DACs                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.2  | Characteristics of $\Delta \Sigma$ DACs                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.3  | $\Delta\Sigma$ DAC Based Transmitters                                                                                                                                                                                                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.4  | Organization and Scope of Dissertation                                                                                                                                                                                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TID  | SM DAC Design Considerations                                                                                                                                                                                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1  | Conventional DSMs                                                                                                                                                                                                                                      | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 2.1.1 High-speed Conventional DSMs: Previous Works                                                                                                                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 2.1.2 Speed Limitation of a First Order EFB DSM                                                                                                                                                                                                        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.2  | Time-Interleaved DSM and Previous Works                                                                                                                                                                                                                | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3  | Choice of Multiplexing Strategy                                                                                                                                                                                                                        | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4  | DAC Current Cell Design                                                                                                                                                                                                                                | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                                                                                                                                                                                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.5  |                                                                                                                                                                                                                                                        | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.6  |                                                                                                                                                                                                                                                        | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.7  | Summary                                                                                                                                                                                                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| An 8 | 3-GS/s 200-MHz BW Interleaved $\Delta\Sigma$ DAC in 65-nm CMOS                                                                                                                                                                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1  | Introduction                                                                                                                                                                                                                                           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2  |                                                                                                                                                                                                                                                        | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | •                                                                                                                                                                                                                                                      | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | •                                                                                                                                                                                                                                                      | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                                                                                                                                                                                        | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                                                                                                                                                                                        | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3  |                                                                                                                                                                                                                                                        | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.4  | Summary                                                                                                                                                                                                                                                | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Effe | ct of Clock Duty Cycle Error on Two-channel Interleaved $\Delta\Sigma$ DACs                                                                                                                                                                            | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                                                                                                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1  |                                                                                                                                                                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | <ol> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> <li>TID</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>An 8</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Effe</li> </ol> | 1.2       Characteristics of $\Delta \Sigma$ DACs         1.3 $\Delta \Sigma$ DAC Based Transmitters         1.4       Organization and Scope of Dissertation <b>TIDSM DAC Design Considerations</b> 2.1       Conventional DSMs         2.1.1       High-speed Conventional DSMs: Previous Works         2.1.2       Speed Limitation of a First Order EFB DSM         2.3       Choice of Multiplexing Strategy         2.4       DAC Current Cell Design         2.5       Aspects of Clock Distribution         2.6       DAC Testing Challenges         2.7       Summary <b>An 8-GS/s 200-MHz BW Interleaved</b> $\Delta \Sigma$ <b>DAC in 65-nm CMOS</b> 3.1       Introduction         3.2.1       Analysis of Critical Path         3.2.2       Comparison With Alternative Logic Styles         3.2.3       Clock Distribution         3.2.4       Final Multiplexer and Current Cell Design         3.3       Measurement Results |

|            | 4.3    | Expression for SNDR Loss Due to DCE                                    | 59  |

|------------|--------|------------------------------------------------------------------------|-----|

|            | 4.4    | Validation of Expression for SNDR Loss                                 | 60  |

|            |        | 4.4.1 Extension to Larger Number of Channels                           | 63  |

|            | 4.5    | Mitigating DCE Effect with Digital Filtering                           | 64  |

|            | 4.6    | Expression for SNDR Loss with FIR Filter                               | 65  |

|            |        | 4.6.1 Validation of SNDR Loss with FIR Filter                          | 66  |

|            | 4.7    | Other Timing Error Mitigation Techniques                               | 68  |

|            |        | 4.7.1 Parallel-Path DACs or Hold Interleaving                          | 68  |

|            |        | 4.7.2 Compensation Through Analog Post-correction                      | 69  |

|            |        | 4.7.3 Compensation Through Digital Pre-correction                      | 69  |

|            | 4.8    | Comparison of Different Mitigation Techniques                          | 70  |

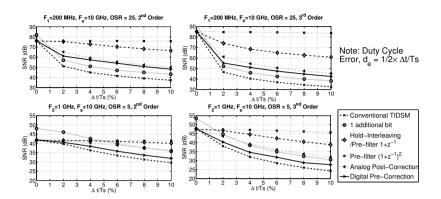

|            |        | 4.8.1 Performance of Correction Techniques                             | 70  |

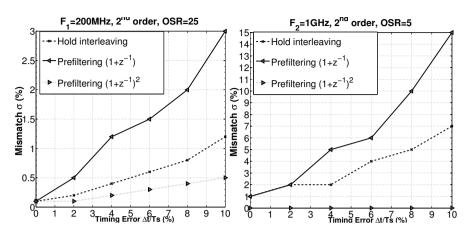

|            |        | 4.8.2 Performance of FIR Filtering Techniques                          | 72  |

|            | 4.9    | Summary                                                                | 73  |

|            |        |                                                                        |     |

| 5          |        | -GS/s 1.1-GHz BW TI- $\Delta\Sigma$ DAC for 60-GHz Radio in 65-nm CMOS |     |

|            | 5.1    | Introduction                                                           | 75  |

|            | 5.2    | Modulator Architecture                                                 | 78  |

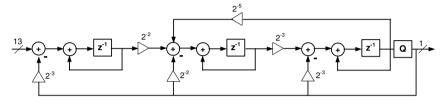

|            | 5.3    | Proposed Look-Ahead Time-interleaved Modulator                         | 80  |

|            |        | 5.3.1 Numerical Example of LA-TIDSM                                    | 84  |

|            |        | 5.3.2 Proof of Equivalency between TIDSM and LA-TIDSM                  | 84  |

|            |        | 5.3.3 LA-TIDSM for Larger Number of Channels                           | 86  |

|            |        | 5.3.4 Alternative Implementations                                      | 88  |

|            | 5.4    | High-Speed LA-TIDSM DAC Design                                         | 90  |

|            |        | 5.4.1 Modulator Design                                                 | 90  |

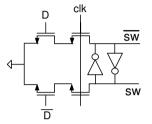

|            |        | 5.4.2 Final Multiplexer and DAC Current Cell Design                    | 92  |

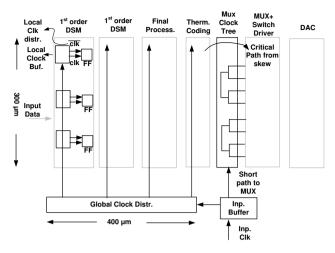

|            | 5.5    | Chip Implementation and Testing Methodology                            | 94  |

|            |        | 5.5.1 Layout Considerations                                            | 95  |

|            | 5.6    | Measurement Results                                                    | 96  |

|            |        | 5.6.1 Additional Duty Cycle Measurements                               | 102 |

| 6          | Con    | clusions and Future Work                                               | 105 |

|            | 6.1    | Future Work                                                            | 106 |

| Re         | eferen | ces                                                                    | 109 |

| Δ          | թոհ    | lished Papers                                                          | 117 |

| 1 <b>N</b> | I UD   | upitor i uporo                                                         |     |

# **List of Figures**

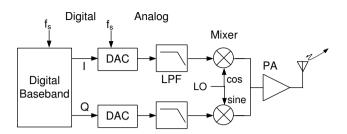

| 1-1                    | DAC in a conventional transmitter.                                             | 2        |

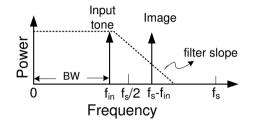

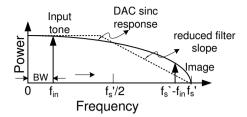

|------------------------|--------------------------------------------------------------------------------|----------|

| 1-2                    | Filtering of the nearest DAC image.                                            | 2        |

| 1-3                    | An oversampled DAC reduces the filter order                                    | 3        |

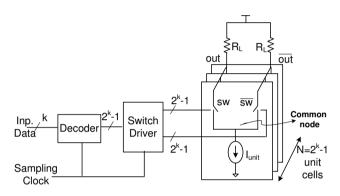

| 1-4                    | An k-bit current steering DAC.                                                 | 3        |

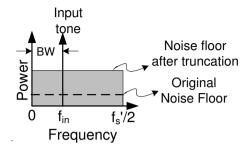

| 1-5                    | Effect of truncating the DAC input word length                                 | 5        |

| 1-6                    | Noise shaping of the quantization noise by a DSM                               | 6        |

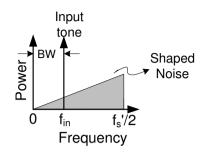

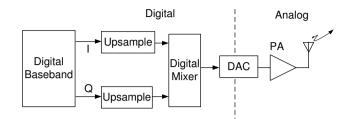

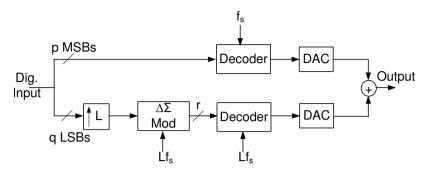

| 1-7                    | The $\Delta\Sigma$ DAC architecture.                                           | 6        |

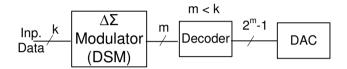

| 1-8                    | DAC in a "digital" transmitter.                                                | 7        |

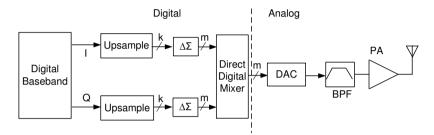

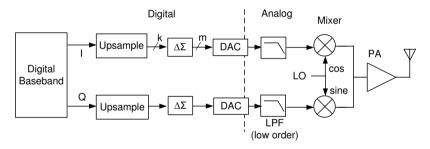

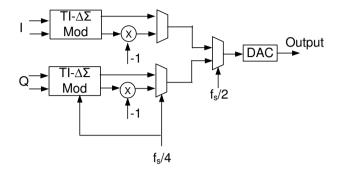

| 1-9                    | All digital transmitter used in [25] (4 GS/s DAC and 1 GHz carrier).           | 7        |

| 1-10                   | Config. used in [8] for a 3.6 GS/s $\Delta\Sigma$ DAC for 2.4/5 GHz carriers   | 7        |

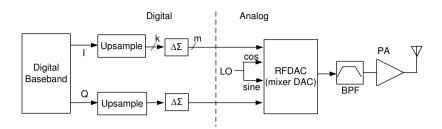

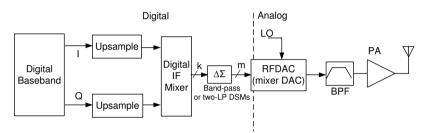

| 1-11                   | Config. used in [27] (5.4 GS/s DAC/2.7 GHz carrier) and [26]                   |          |

|                        | (2.6 GS/s DAC/5.4 GHz carrier)                                                 | 8        |

| 1-12                   | Config. used in [26] (2.6 GS/s DAC/650 MHz IF) and [32] (250 MS/s              |          |

|                        | DAC/62 MHz IF)                                                                 | 8        |

| 1-13                   | Aim of dissertation is to extend the BW of $\Delta\Sigma$ DACs. The source     |          |

|                        | data in this plot is derived from [40]                                         | 9        |

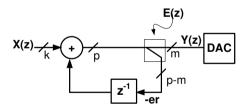

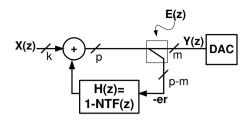

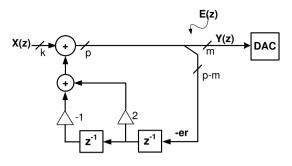

| 2-1                    | A first-order EFB DSM.                                                         | 11       |

| 2-1                    | An n <sup>th</sup> -order EFB DSM.                                             | 12       |

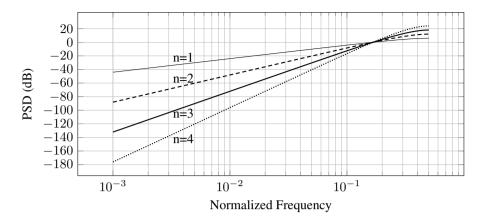

| 2-2                    | A 20 <i>n</i> dB/decade noise shaping for a DSM with $NTF(z) = (1-z^{-1})^n$ . | 12       |

| 2-3<br>2-4             | A second-order EFB DSM                                                         | 13       |

| 2-4                    | A third-order EFB DSM with four adder critical path.                           | 14       |

| 2-5                    | A second-order CIFB DSM topology used in [8].                                  | 14       |

| 2-7                    | A third-order 2 GS/s DSM proposed in [25].                                     | 15       |

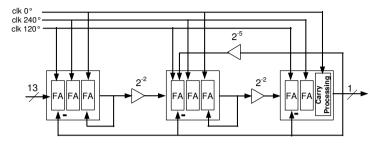

| 2-8                    | Three phase clocking with dynamic full adders used in [25].                    | 16       |

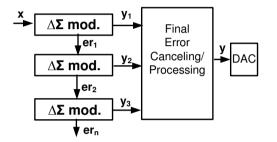

| 2-0                    | A MASH architecture with a cascade of individual modulators                    | 16       |

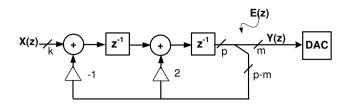

|                        | A MASH 1-1 DSM.                                                                | 17       |

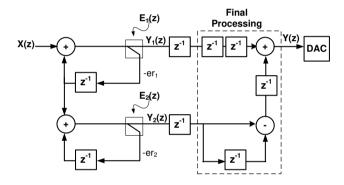

|                        | A pipelined MASH 1-1 DSM with only a one adder critical path                   | 17       |

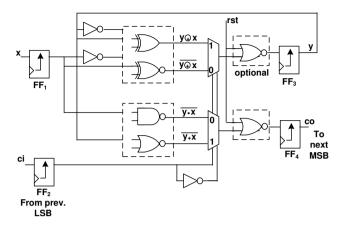

|                        | A 1-bit pipeline of the first-order EFB using a 1-bit carry select adder.      | 18       |

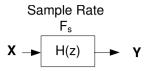

|                        | Transfer function $H(z)$ at a sample rate $f_s$ .                              | 20       |

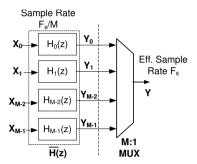

| $2^{-13}$<br>$2_{-14}$ | M-channel time-interleaved implementation of $H(z)$ .                          | 20<br>20 |

| 2-14                   | M-channel time-interceaved implementation of $M(z)$                            | 20       |

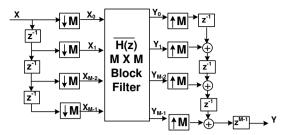

| 2-15 | TI using a $M \times M$ block filtering approach.                              | 21 |

|------|--------------------------------------------------------------------------------|----|

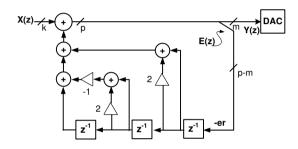

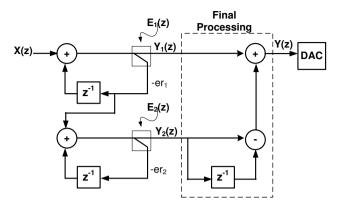

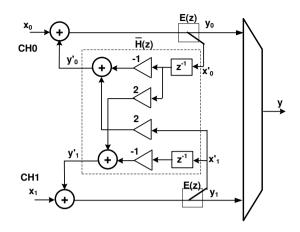

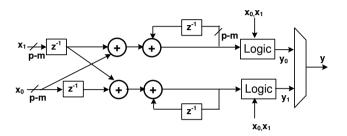

| 2-16 | A 2-channel TI-EFB implementation for a transfer function $NTF(z) =$           |    |

|      | $(1-z^{-1})^2$                                                                 | 22 |

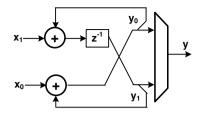

| 2-17 | Two-channel TI implementation of a delay element/FF                            | 23 |

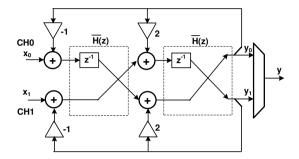

| 2-18 | Two-channel TI implementation of a second-order CIFB DSM                       | 23 |

| 2-19 | A first-order EFB with a delayed integrator.                                   | 24 |

| 2-20 | TI implementation of a first-order EFB by decomposing the integrator           |    |

|      | transfer function.                                                             | 24 |

| 2-21 | TI decomposition of a first-order EFB by decomposing the FF only.              | 25 |

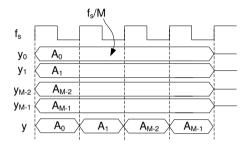

| 2-22 | Timing diagram for the multiplexer/serializer.                                 | 25 |

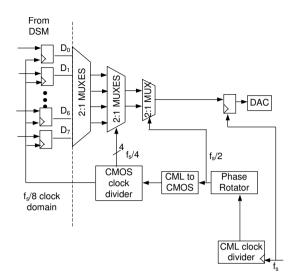

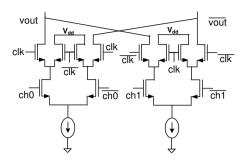

|      | The classical MUX scheme used in [34]                                          | 26 |

| 2-24 | CML Phase Rotator based calibration scheme for MUX used in [40].               | 27 |

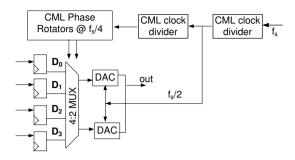

|      | Phase/Delay Calibration based DAC used in [48].                                | 28 |

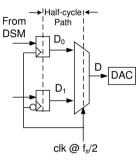

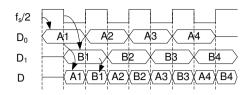

|      | Two-channel MUX with a single $f_s/2$ clock.                                   | 28 |

|      | Timing Diagram for a two channel MUX with a $f_s/2$ clock                      | 29 |

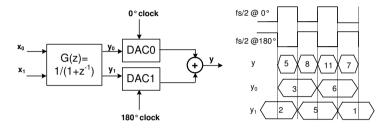

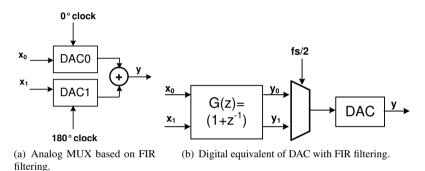

|      | Two-channel Analog MUX based on IIR pre-filtering used in [51].                | 29 |

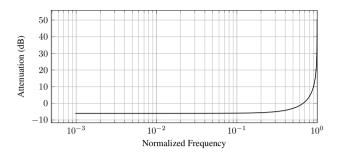

|      | Frequency response of the IIR filter with the transfer function $G(z) =$       |    |

|      | $1/(1+z^{-1})$ .                                                               | 30 |

| 2-30 | DACs with FIR response                                                         | 30 |

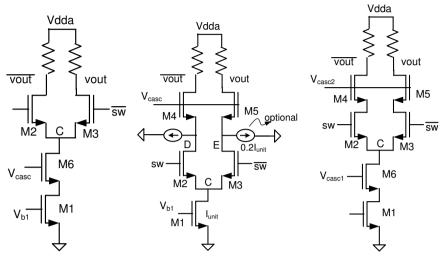

|      | Commonly used DAC current cell types.                                          | 32 |

|      | Dual current cells with embedded multiplexing [48].                            | 33 |

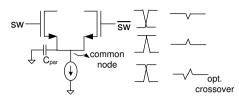

|      | Effect of switch crossover point on the common node potential [50].            | 34 |

|      | A fast high-crossing switch driver [16] [21].                                  | 34 |

|      | Floorplan of a TIDSM MASH 1-1 with clock distribution.                         | 36 |

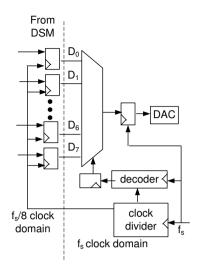

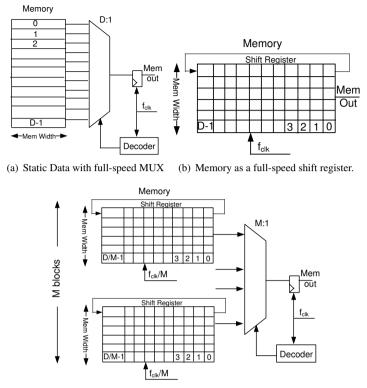

|      | Commonly used DAC testing memory types.                                        | 37 |

|      |                                                                                |    |

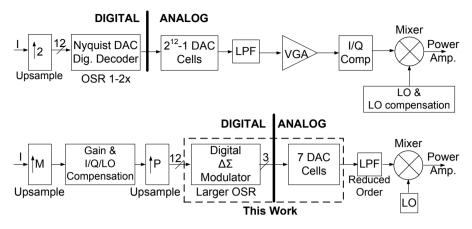

| 3-1  | Example of a Nyquist DAC in a traditional transmitter (top) and a              |    |

|      | $\Delta\Sigma$ DAC in a digital baseband transmitter (bottom). Only the I path |    |

|      | is shown.                                                                      | 40 |

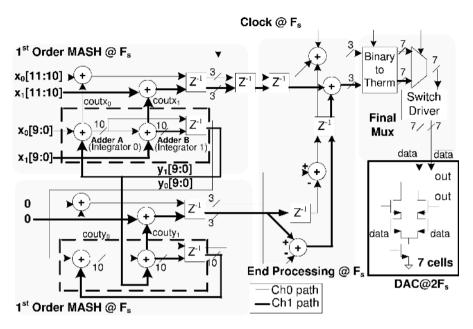

| 3-2  | Proposed two-channel interleaved second order MASH $\Delta\Sigma$ DAC          |    |

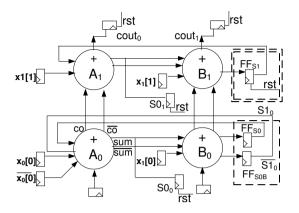

|      | with a $2F_s$ sampling rate. Critical path is enclosed by a dashed rectangle.  | 41 |

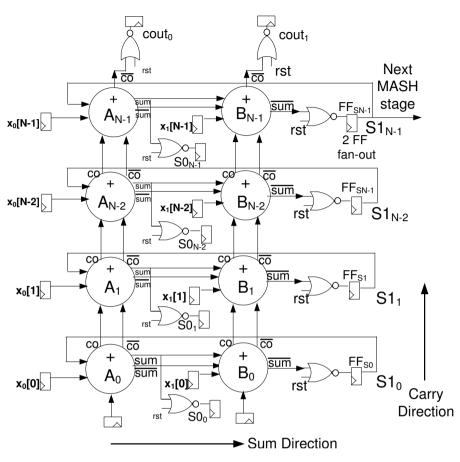

| 3-3  | N-bit deep Integrator Pipeline. Critical path is from at flop $FF_{S0}$ to     |    |

|      | flop $FF_{SN-1}$                                                               | 42 |

| 3-4  | A 2-bit pipeline with optimization. Single dashed box shows comple-            |    |

|      | mentary inputs. Double box shows reset moved to the flop                       | 45 |

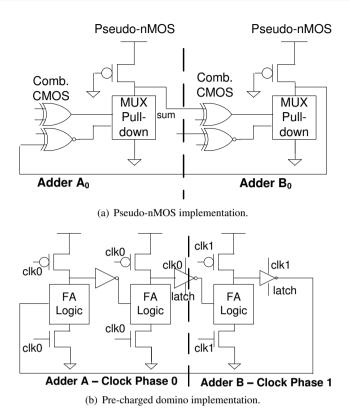

| 3-5  | Ratioed and Dynamic Logic Implementation of the integrator                     | 46 |

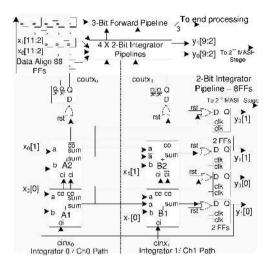

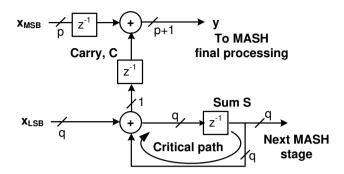

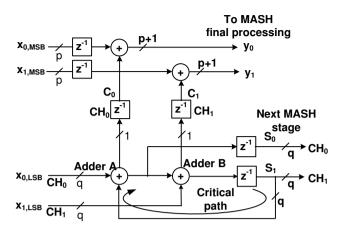

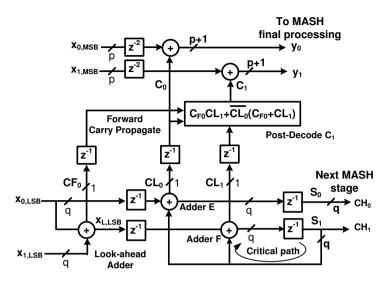

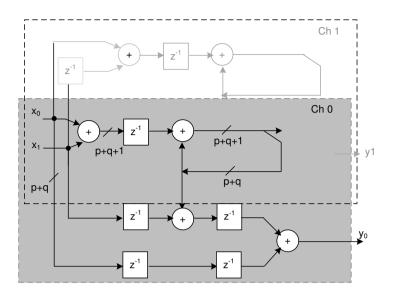

| 3-6  | The first order EFB TIDSM instantiated twice to obtain the MASH 1-1.           | 48 |

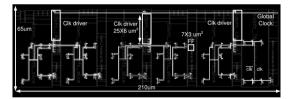

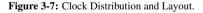

| 3-7  | Clock Distribution and Layout.                                                 | 48 |

| 3-8  | Final MUX and DAC current cell with the timing diagram. Switch                 |    |

|      | driver circuit is the same as the local clock driver of Fig. 3.7(a)            | 49 |

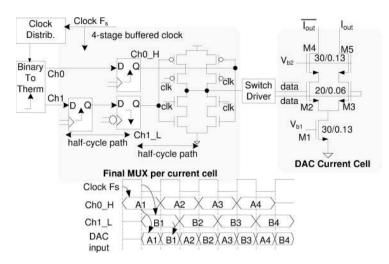

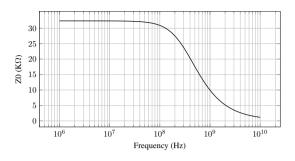

| 3-9  | Simulated output impedance $(Z_0)$ profile of the current cell                 | 50 |

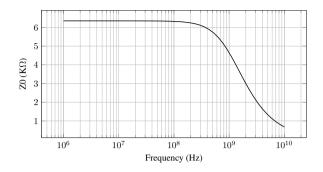

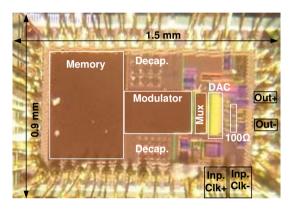

| 3-10 | Chip photograph of the implemented $\Delta \Sigma$ DAC                         | 51 |

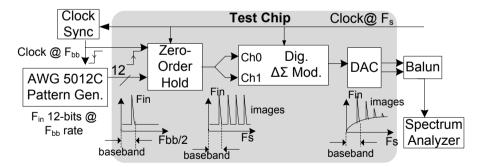

| 3-11        | Measurement setup for the $\Delta\Sigma$ DAC with the expected spectrum at output of every block. An up-sampling filter is not used to simplify |          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

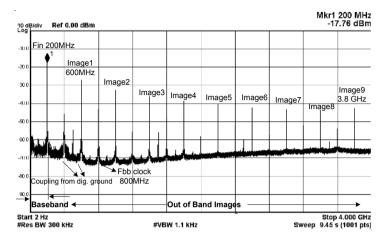

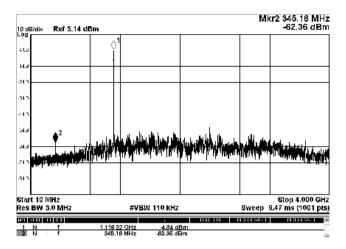

| 3-12        | testing. Up-sampling images in the output are out of the band of interest.<br>Measured single-ended spectrum showing 8 GS/s operation with      | 51       |

|             | $F_s=4$ GHz, $F_{bb}=800$ MHz and input frequency, $F_{in}=200$ MHz. The                                                                        | 50       |

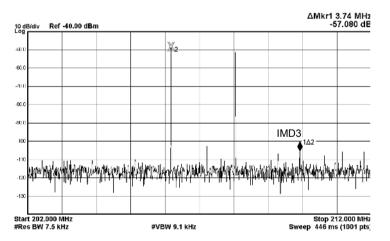

| 3 13        | noise shaping and the 9 out of band images can be seen Measured -57-dBc IMD3 with two -6 dBFS tones near 200 MHz                                | 52       |

| 5-15        | spaced 2 MHz apart.                                                                                                                             | 52       |

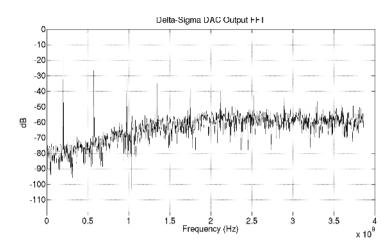

| 3-14        | Output spectrum with 42 dB SNDR obtained from post-layout simu-                                                                                 | 02       |

|             | lation for an 8 GS/s operation.                                                                                                                 | 53       |

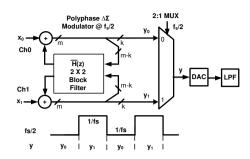

| 4-1         | Block diagram of a generic two-channel interleaved $\Delta\Sigma$ DAC imple-                                                                    |          |

| 4.0         | menting a noise transfer function $1 - H(z)$                                                                                                    | 56       |

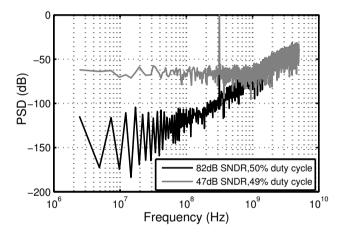

| 4-2         | Effect of 1% DCE on SNDR for a 4-bit DAC with $f_s$ =10 GHz, OSR=16 (BW=312.5 MHz) and NTF of $(1 - z^{-1})^3$ .                                | 56       |

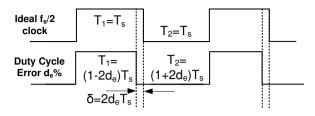

| 4-3         | USR=10 (BW=312.5 MHz) and N1F of $(1 - z^{-1})$<br>Half-rate sampling clock of frequency $f_s/2$ and DCE = $d_e\%$                              | 50<br>57 |

| 4-3<br>4-4  | Folding effect of DCE on time-interleaved Nyquist and DSM DACs.                                                                                 | 58       |

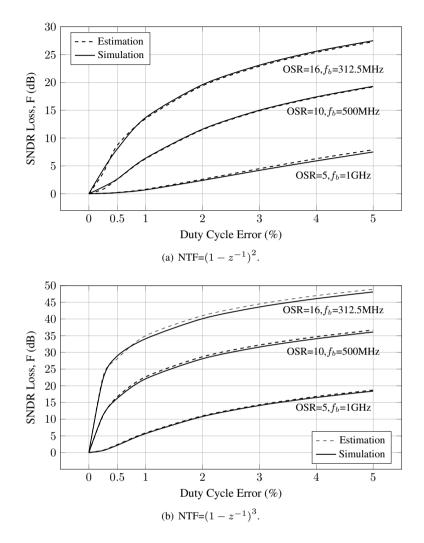

| 4-5         | Simulation versus Estimation of SNDR loss for a 10 GS/s TIDSM                                                                                   | 50       |

| ч 5         | DAC for (a) second-order $(n=2)$ and (b) third-order $(n=3)$ modulators.                                                                        | 61       |

| 4-6         | Second-order modulator shows a better SNDR than third-order for                                                                                 | 01       |

|             | OSR=16 and $d_e > 0.12\%$ as predicted by Eq. (4.15)                                                                                            | 63       |

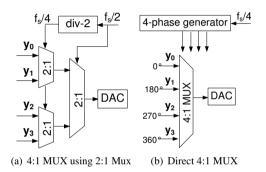

| 4-7         | Two multi-channel MUX styles.                                                                                                                   | 63       |

| 4-8         | Interleaved $\Delta\Sigma$ DAC with a FIR filter to reduce the effect of the DCE.                                                               | 65       |

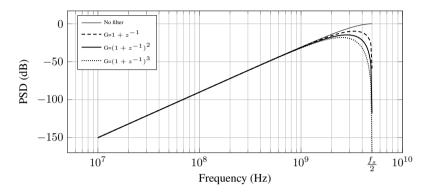

| 4-9         | Frequency response of a 10 GS/s TIDSM DAC noise-shaping with                                                                                    |          |

|             | NTF(z)= $(1 - z^{-1})^3$ in presence of the FIR filter.                                                                                         | 65       |

| 4-10        | Simulation versus estimation of SNDR loss of a 10 GS/s TIDSM                                                                                    |          |

|             | DAC for $n=3$ as a function of filter order, $m$ and OSR from Eq. (4.21).                                                                       | 67       |

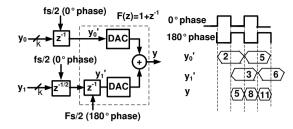

| 4-11        | Hold interleaving to introduce a zero at $f = f_s/2$ . i.e. implementing                                                                        |          |

|             | a filter $1 + z^{-1}$                                                                                                                           | 68       |

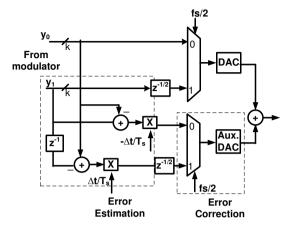

|             | Analog post-correction of timing skew with an auxiliary DAC                                                                                     | 69       |

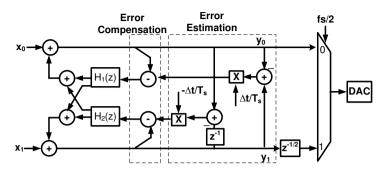

|             | Digital pre-correction of timing skew in the modulator.                                                                                         | 70       |

| 4-14        | Simulated variation of SNDR as a function of timing skew error for different OSR and modulator orders. Note that duty cycle error,              |          |

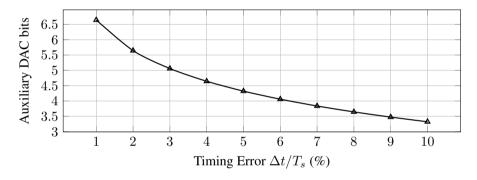

|             | $d_e = 1/2 \times \Delta t/T_s$ .                                                                                                               | 71       |

| 4-15        | $u_e = 1/2 \times \Delta t/T_s$ . Number of Aux. DAC required for analog post-correction with a                                                 | /1       |

| <b>-</b> 15 | timing error of $\Delta t/T_s$ .                                                                                                                | 71       |

| 4-16        | Simulated DAC mismatch ( $\sigma$ ) % as a function of the timing error for                                                                     | /1       |

| . 10        | achieving SNDR of Fig. 4-14.                                                                                                                    | 72       |

| 5-1         | Comparison of different DAC based architectures for 60-GHz radio                                                                                |          |

|             | baseband                                                                                                                                        | 76       |

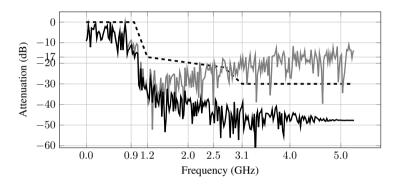

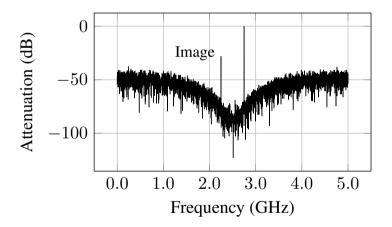

| 5-2  | Filtering with a second order LPF for a second order $\Delta\Sigma$ 4-bit DAC |     |

|------|-------------------------------------------------------------------------------|-----|

|      | at 10.56 GS/s 16-QAM encoded random data.                                     | 79  |

| 5-3  | A conventional first-order EFB DSM.                                           | 80  |

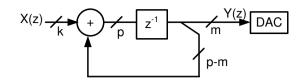

| 5-4  | A 2-channel TI EFB DSM.                                                       | 81  |

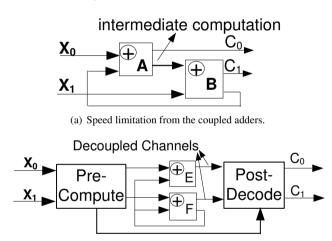

| 5-5  | TIDSM versus the LA-TIDSM approach to improve the speed                       | 81  |

| 5-6  | Proposed two-channel LA-TIDSM EFB DSM with only one adder                     |     |

|      | critical path.                                                                | 83  |

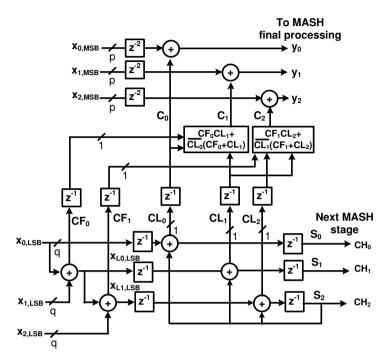

| 5-7  | A three channel LA-TIDSM implementation.                                      | 86  |

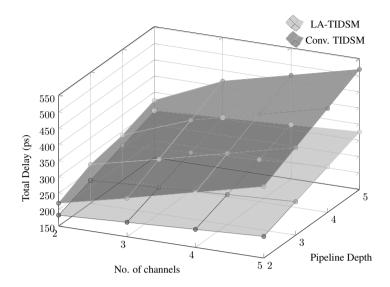

| 5-8  | Design space comparison of a conventional and LA TIDSM                        | 89  |

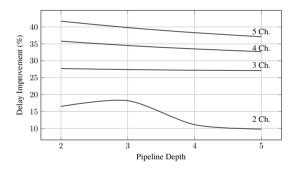

| 5-9  | Delay improvement over conventional TIDSM as a function of pipeline           |     |

|      | depth and number of channels.                                                 | 89  |

| 5-10 | An alternative two-channel TIDSM architecture of [40] also having 1           |     |

|      | adder critical path but requires 8 adders in total.                           | 90  |

| 5-11 | A 2-bit pipeline slice of a first-order EFB LA-TIDSM. Grey colour             |     |

|      | represents the LA part. Thin lines are used for CH0 path and thick            |     |

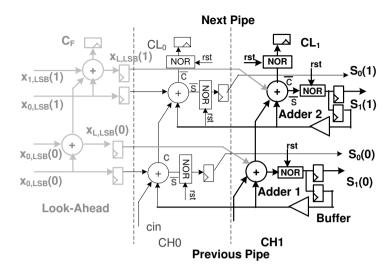

|      | ones for CH1 path.                                                            | 91  |

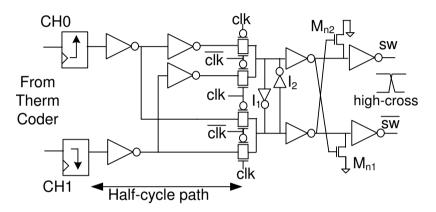

| 5-12 | Final 2:1 Multiplexer with high-crossing switch driver.                       | 92  |

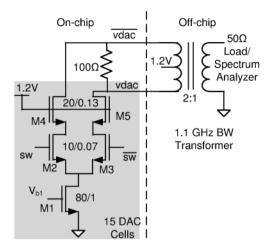

| 5-13 | DAC current cell interfaced with a centre-tapped 2:1 transformer              | 93  |

| 5-14 | Simulated output impedance $(Z_0)$ profile of the current cell                | 94  |

| 5-15 | Chip Photograph.                                                              | 94  |

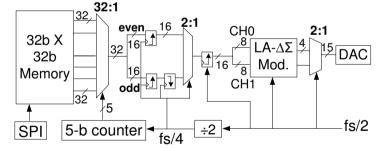

| 5-16 | Memory Architecture for full speed LA-TIDSM DAC testing                       | 94  |

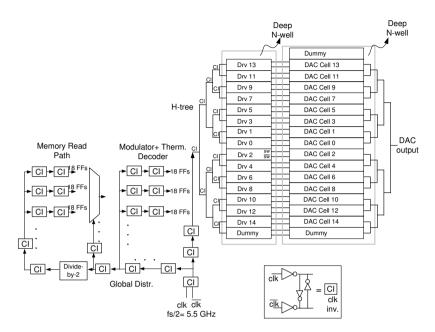

|      | DAC and switch driver floorplan.                                              | 96  |

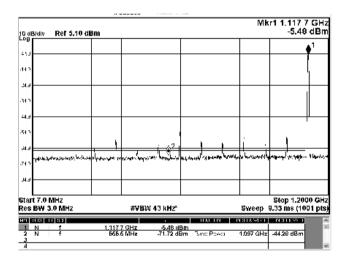

| 5-18 | Measured wideband spectrum with a 1.1 GHz input tone at 11 GS/s.              | 97  |

| 5-19 | Measured 39 dB SNDR with a 1.1 GHz at 11 GS/s tone with no                    |     |

|      | dithering                                                                     | 97  |

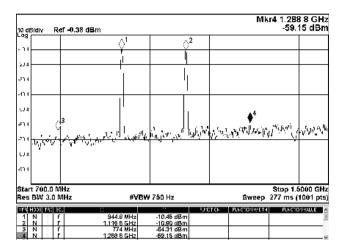

| 5-20 | Measured IM3 of -49 dBc with two tones at 945 MHz and 1.1 GHz                 |     |

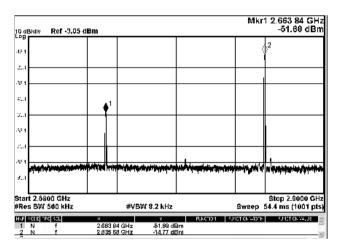

|      | respectively.                                                                 | 98  |

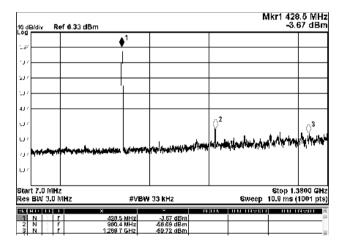

|      | Measured 53 dB HD2 and 56 dB HD3 with a 428 MHz input sine tone.              | 98  |

| 5-22 | Measured interleaving spur of $-36.9$ dBc at 2.67 GHz with a 2.83 GHz         |     |

|      | tone to estimate the DCE                                                      | 99  |

| 5-23 | Measured SFDR (in 0-1.1 GHz band), SNDR (0-inp. freq.) and IM3                |     |

|      |                                                                               | 00  |

| 5-24 | Measured Spectral Mask with 16-QAM encoded random data at                     |     |

|      |                                                                               | 00  |

| 5-25 | Effect of DCE on a 2-b modulator at 11 GS/s and input frequency of            |     |

|      | 601 MHz (OSR=9.15)                                                            | 03  |

| 6-1  | A hybrid DAC.                                                                 | 107 |

| 6-2  |                                                                               | 08  |

| 6-3  | Digital IF of 2.5 GHz using a 10 GS/s TI-DASM DAC. DCE causes                 | .00 |

| 55   |                                                                               | 08  |

|      | a erose mange spuri i i i i i i i i i i i i i i i i i i                       |     |

# **List of Tables**

| 2-1 | Post-layout simulated delay of a 1-bit pipeline at 1 V, 75°C, typical corner using TGFFs and static CMOS logic. | 19   |

|-----|-----------------------------------------------------------------------------------------------------------------|------|

| 3-1 | Maximum effective achieved speed as a function of the pipeline depth                                            |      |

|     | in a 2-channel interleaved modulator                                                                            | 44   |

| 3-2 | Delay Comparison with alternative logic style for 2-bit pipelines                                               | 47   |

| 3-3 | Comparison with $\Delta\Sigma$ DACs having >2.5-GS/s sampling rate                                              | 54   |

| 5-1 | Different modulator options for the 880 MHz bandwidth                                                           | 79   |

| 5-2 | Truth Table to compute the correct value of carry, $C_1$ from $CF_0, CL_0$                                      |      |

|     | and $CL_1$                                                                                                      | 84   |

| 5-3 | Carry computation truth table for $C_2$ in a three channel LA-TIDSM.                                            | 87   |

| 5-4 | Post-layout simulated delay of the integrator (Fig. 5-11) at 1 V, 75°C,                                         |      |

|     | typical corner.                                                                                                 | 92   |

| 5-5 | Power and Area Breakdown of the DAC by function.                                                                | 99   |

| 5-6 | Comparison with complete $\Delta\Sigma$ DACs having >2.5-GS/s sampling rate                                     | .101 |

| 5-7 | Comparison with other Digital $\Delta\Sigma$ Modulators with > 5 GHz speed.                                     | 102  |

| 5-8 | Comparison of this work with wideband Nyquist DACs                                                              | 102  |

|     |                                                                                                                 |      |

# **List of Abbreviations**

| ADC      | Analog-to-Digital Converter                         |

|----------|-----------------------------------------------------|

| BPF      | Band-Pass Filter                                    |

| BPSK     | Binary Phase Shift Keying                           |

| BW       | Bandwidth                                           |

| CIFB     | Cascaded Integrator with distributed error Feedback |

| CML      | Current Mode Logic                                  |

| CMOS     | Complementary Metal Oxide Semiconductor             |

| CS-DAC   | Current Steering DAC                                |

| DAC      | Digital-to-Analog Converter                         |

| DCE      | Duty Cycle Error                                    |

| DFF      | D-Flip flop                                         |

| DFT      | Design for Testability                              |

| DLL      | Delay Locked Loop                                   |

| DNL      | Differential Non-linearity                          |

| DSM/DDSM | Digital $\Delta\Sigma$ Modulator                    |

| EFB      | Error Feedback                                      |

| ENOB     | Effective Number of Bits                            |

| FA       | Full Adder                                          |

| FFT      | Fast Fourier Transform                              |

| FF              | Flip-flop                                            |

|-----------------|------------------------------------------------------|

| FIR             | Finite Impulse Response                              |

| FOM             | Figure of Merit                                      |

| HD <sub>n</sub> | Harmonic Distortion of n <sup>th</sup> -order        |

| IF              | Intermediate Frequency                               |

| IIR             | Infinite Impulse Response                            |

| IM3/IMD3        | Third-order Intermodulation Distortion               |

| INL             | Integral Non-linearity                               |

| JLCC            | J-Leaded Chip Carrier                                |

| LA-TIDSM        | Look-ahead Time-interleaved $\Delta\Sigma$ Modulator |

| LPF             | Low-Pass Filter                                      |

| LSB             | Least Significant Bit                                |

| MASH            | Multi stAge noise SHaping                            |

| MSB             | Most Significant Bit                                 |

| MUX             | Multiplexer                                          |

| NTF             | Noise Transfer Function                              |

| OFDM            | Orthogonal Frequency Division Multiplexing           |

| OSR             | Oversampling Ratio                                   |

| PA              | Power Amplifier                                      |

| PRBS            | Pseudo Random Bit Sequence                           |

| QAM             | Quadrature Amplitude Modulation                      |

| QPSK            | Quadrature Phase Shift Keying                        |

| SC              | Single Carrier                                       |

| SFDR            | Spurious-Free Dynamic Range                          |

| SNDR            | Signal-to-Noise-and-Distortion Ratio                 |

| SNR             | Signal-to-Noise Ratio                                |

| SoC   | System-on-Chip                            |

|-------|-------------------------------------------|

| SQNR  | Signal-to-Quantization-Noise Ratio        |

| STF   | Signal Transfer Function                  |

| TG    | Transmission Gate                         |

| TIDSM | Time-Interleaved $\Delta\Sigma$ Modulator |

| TSPCR | True Single Phase Clocked Register        |

| Тх    | Transmitter                               |

### **Chapter 1**

### Introduction

Digital-to-Analog Converters (DACs) are one of the fundamental building blocks of all wireless transmitters (Tx) and form the interface between the analog and the digital world. The increasing demand for high bandwidth and high-data rates has led to the development of a multitude of radio standards, which have channel bandwidths ranging from a few megahertz to many gigahertz. While standards like WiMAX (IEEE 802.16) [1] and Wi-Fi (IEEE 802.11x standards) [2] have channel bandwidths of up to about 40 MHz, recent standards for short-length communication e.g. Ultra Wide Band (UWB) [3] and 60-GHz radio [4–6] have channel bandwidths of 528 MHz and 1.76 GHz respectively. Consequently, there is also a requirement on the DAC to support these increasing bandwidths. If the total channel bandwidth of the radio standard is C, then the DAC is required to support a bandwidth, BW that is greater than C/2.

#### 1.1 Characteristics of Nyquist DACs

Traditionally, Nyquist DACs have been used in transmitters. Figure 1-1 shows the location of the DAC in a conventional Tx chain and operating at a sample rate of  $f_s$ . The DAC can support an input BW of up to  $f_s/2$  and the analog reconstruction/antialiasing low-pass filter (LPF) filters out the DAC images. As the input BW becomes closer to  $f_s/2$ , the first DAC image also moves nearer to the input signal. This results in an increase in the anti-aliasing filter order and a sharp cut-off to attenuate this nearest DAC image. Figure 1-2 shows that as the input tone  $f_{in}$  moves closer to  $f_s/2$ , the nearest DAC image located at  $f_s - f_{in}$  also moves nearer to  $f_s/2$ , thus increasing the difficulty of image filtering. The main drawback of passive on-chip implementations of this LPF is the large area of the inductors or capacitors required and their low quality factor [7] [8]. Recently, a few wideband active filters that can occupy a lesser area also have been proposed for receivers [9] [10]. However, they are

Figure 1-1: DAC in a conventional transmitter.

Figure 1-2: Filtering of the nearest DAC image.

challenging to design and can limit the transmitter linearity as compared to passive filters.