# Design of Low-Loss Transmission Lines in Scaled CMOS by Accurate Electromagnetic Simulations

Federico Vecchi, Student Member, IEEE, Matteo Repossi, Wissam Eyssa, Paolo Arcioni, Senior Member, IEEE, and Francesco Svelto, Member, IEEE

Abstract-Transmission lines are becoming of common use at mm-wave to implement on-chip functions as impedance matching, filtering and interconnects. Lack of an accurate and fast simulation method is nonetheless evident for transmission lines in scaled CMOS where metal dummies inserted for IC planarization make their physical structure extremely complicate. Although lines are not uniform due to displacement of small dummies, they are still periodic. In this paper, we describe an analytical procedure, leveraging lines periodicity and based on Floquet's theorem, in order to derive electromagnetic parameters from simulations. Conventional, slow-wave and shielded CPWs have been realized in a 65 nm CMOS technology. Thanks to the developed method, an optimum line design has been made possible. The lossy CMOS substrate, responsible for a significant performance degradation, can be effectively shielded and achieved performances are comparable with other technologies considered better suited to implement low-loss, high frequency passive components. Shielded CPW lines show attenuation as low as 0.65 dB/mm at 60 GHz, a record in scaled CMOS.

*Index Terms*—CMOS, EM simulators, millimeter-wave integrated circuits, transmission lines, wireless transceivers.

#### I. INTRODUCTION

**M** ILLIMETER-WAVE CMOS RF circuits are drawing more and more attention, motivated by the new wave of consumer products exploiting the 60–100 GHz frequency range: short-distance, high data-rates and point-to-point inter-building communications, anti-collision automotive radars, passive and active imaging representing possible applications [1], [2].

Due to the very high operating frequency, the signal wavelength becomes comparable with typical IC dimensions, making transmission lines attractive to implement on-chip functions as impedance matching, filtering and interconnections between different blocks [3]–[7]. One of the key merits of transmission

F. Vecchi is with the Dipartimento di Elettronica, Università di Pavia, 27100 Pavia, Italy, and also with the Istituto Universitario di Studi Superiori di Pavia, Pavia, Italy (e-mail: federico.vecchi@unipv.it).

M. Repossi is with STMicroelectronics, 27100 Pavia, Italy (e-mail: matteo. repossi@st.com).

W. Eyssa is with the Dipartimento di Elettronica, Università di Pavia, 27100 Pavia, Italy, and also with the Istituto Universitario di Studi Superiori di Pavia, Pavia, Italy (e-mail: wissam.eyssa@unipv.it).

P. Arcioni and F. Svelto are with the Dipartimento di Elettronica, Università di Pavia, 27100 Pavia, Italy (e-mail: paolo.arcioni@unipv.it; francesco.svelto@unipv.it).

Digital Object Identifier 10.1109/JSSC.2009.2023277

lines is easy model scalability, in contrast with lumped-element components, e.g., integrated capacitors or spiral inductors, which require a dedicated characterization procedure [8]. A well-designed RF circuit based on transmission lines also minimizes (or even completely removes) the need for a parasitic extraction tool, since all interconnect parasitics are already taken into account in the line model. Moreover, precise measurements of capacitors or inductors are problematic because of the small value of components typically needed at these high frequencies. On the contrary, line characterization can be performed on prototypes of arbitrary length, from which unit-length parameters can always be obtained allowing design of scaled length lines.

Many papers have been published in recent years reporting various different line topologies on Silicon substrates, including standard geometries (like microstrip (MS) and coplanar waveguides (CPW) [9]–[12]) and more complicated ones (like slowwave lines [3], [4], [13], [14]), which exploit the dense stratification of modern processes to improve the line characteristics–in terms of attenuation, quality factor, substrate shielding, occupied area—and, consequently the RF circuit performance.

However, to the authors' knowledge, no rigorous methodology has been yet developed in order to provide a rapid and accurate simulation tool for transmission lines in scaled CMOS. Moreover, a significant performance gap between transmission lines realized in bulk CMOS versus SOI or SiGe is evident from published literature.

In this paper, a method dedicated to the simulation of transmission lines on CMOS substrates is presented, guiding the design and optimization of the line geometry with commercial full-wave electromagnetic (EM) software, while considering all the details of the stratification, the actual substrate effects and the design constraints set by modern CMOS processes (e.g., density rules). This method allows rapid simulation of both conventional lines, with uniform geometry along the propagation direction, and "slow-wave" lines, which feature a periodic variation of their geometry along the propagation direction.

A set of transmission lines on standard 65 nm bulk CMOS process has been designed and their measurement is presented, achieving 1 dB/mm attenuation for conventional CPW lines and a record 0.65 dB/mm attenuation for a shielded-CPW line, which compares favorably with alternatives implemented in other technologies.

The paper is organized as follows. Section II describes the simulation methodology, Section III reports the design and measurement of different types of lines, Section IV compares results with state of the art and Section V draws conclusions.

Manuscript received December 22, 2008; revised April 14, 2009. Current version published August 26, 2009. This work was carried out within the Studio di Microelettronica, a research Laboratory, joint between Università di Pavia and STMicroelectronics, in the framework of the Italian National program, Contract RBA06L4S5, and supported in part by COST Action IC0803-RF/Microwave Communication Subsystems for Emerging Wireless Technologies (RFCSET).

a)

#### II. ACCURATE AND FAST ANALYSIS OF PERIODIC LINES

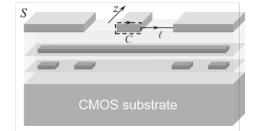

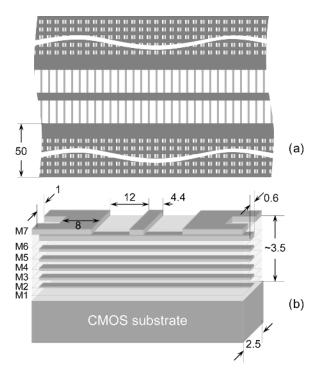

Standard transmission lines are usually uniform structures, i.e., their cross-section is constant along the propagation direction. In this case the propagation characteristics of the line can be derived considering its cross-section only, by using a 2-D EM analysis method [15]. On the other hand, lines realized in ultra-scaled CMOS technologies are usually periodic, rather than uniform, the periodicity being introduced intentionally, as in the slow-wave line shown in Fig. 1(a), or resulting from technological constraints, e.g., when a usually periodic pattern of dummy metals cells is introduced in order to guarantee IC planarity, as shown in Fig. 1(b). In these cases, 2-D EM analysis methods cannot be used, or may prove inaccurate whenever dummy metals cannot be placed far enough from line's conductors. Three-dimensional (3-D) EM analysis-leading to the representation of a line section in terms of scattering parameters from which its propagation characteristics are deduced-may require very long simulation times and memory resources, due to the huge number of unknowns resulting from the discretization of a large structure with fine geometrical details. Moreover, a multi-modal representation of the structure and/or sophisticated de-embedding techniques are often needed, since dummy cells and metal bars represent discontinuities very close to the reference sections of the ports, thus exciting higher-order modes [16]. Accuracy can be improved by considering longer line sections or a higher number of propagation modes on the port sections but this has an enormous impact on simulation time.

To speed up simulation without loss of accuracy, we propose a different approach based on the periodic nature of the lines. In fact, propagation characteristics of periodic structures can be studied by considering their "unit cell", enclosed by periodic boundaries defined on surfaces normal to the propagation direction [see Fig. 1(c)]. This approach has been followed to characterize periodically screened coplanar waveguides on semi-insulating GaAs substrate in [17], where the unit cell was analyzed according to circuit theory, by simply cascading short sections of CPW with and without metal bars, represented by their ABCD matrices. In this paper we extend this approach to the full-wave electromagnetic analysis of the unit cell, in order to consider all the discontinuity effects that cannot be accounted for by a circuit analysis.

According to Floquet's theorem [18], the problem can be formulated in order to find an EM field (Floquet's mode), solution of the Maxwell's equations inside the unit cell, which satisfies the following periodicity condition:

$$\vec{E}_2 = \vec{E}_1 e^{-\gamma d} \quad \vec{H}_2 = \vec{H}_1 e^{-\gamma d} \tag{1}$$

where  $\gamma$  is the complex propagation constant,  $\vec{E}_1, \vec{H}_1, \vec{E}_2, \vec{H}_2$ are the electric and magnetic fields on surfaces  $S_1$  and  $S_2$ , and d is the length of the unit cell [see Fig. 1(c)].

The standard procedure for determining Floquet's modes and their propagation constants consists in finding, at a given (angular) frequency  $\omega$ , a matrix relationship between the discretized fields on  $S_1$  and  $S_2$ , and determining the propagation constant as an eigenvalue of that matrix [19] (since we are interested in the quasi-TEM mode of the periodic structure,

Fig. 1. Transmission lines in scaled CMOS: (a) slow-wave CPW, and (b) standard CPW. Line characteristics can be obtained from unit cell analysis (c).

only the first eigenvalue must be evaluated). Repeating the procedure for different values of  $\omega$ , the dispersion curve  $\gamma = \gamma(\omega)$ of the quasi-TEM mode can be obtained. Unfortunately this procedure cannot be applied in conjunction with commercial EM solvers (e.g., Ansoft HFSS<sup>TM</sup>), since they usually do not provide the system matrices generated during the solution (FEM matrices, in the case of HFSS). Therefore, specialized solvers must be developed [20], [21].

In order to be able to exploit the flexibility of commercial electromagnetic solvers, HFSS in particular, we adopt a different procedure for finding the dispersion curve of the quasi-TEM Floquet's mode of the structure. The approach is similar to the one described in [21] in the context of a Finite-Difference Frequency-Domain algorithm, and consists in considering an equivalent resonant-cavity model of the periodic cell, obtained by imposing the following periodic boundary conditions on surfaces  $S_1$  and  $S_2$ :

$$\vec{E}_2 = \vec{E}_1 e^{-j\theta} \quad \vec{H}_2 = \vec{H}_1 e^{-j\theta}$$

(2)

where  $\theta$  is a given periodic phase shift. As discussed in [21], the complex propagation constant  $\gamma = \alpha + j\beta$  of the quasi-TEM mode of the periodic structure is deduced from the complex resonant frequency  $\Omega = \omega_r + j\omega_i$  of the first mode of the cavity obtained by solving a suitable eigenvalue problem. When the periodic structure can be considered lossless, the procedure is

straightforward, since in this case  $\gamma$  is imaginary ( $\gamma = j\beta$ ) and  $\Omega$  is real  $(\Omega = \omega_r), \omega_r$  representing the frequency at which the fields of the quasi-TEM mode satisfy the periodicity condition (2). Therefore the value of  $\beta$  at  $\omega_r$  is simply given by  $\beta = \theta/d$ . Actually, in the lossless case the two procedures are equivalent, the only difference being how the  $\omega - \beta$  diagram is obtained, i.e., finding  $\beta$  for a given  $\omega$  when using the standard procedure, or finding  $\omega$  for a given  $\beta = \theta/d$  when using the equivalent resonant-cavity model. When losses cannot be ignored, as in the case of CMOS transmission lines, the eigensolution inside the equivalent resonant-cavity model is in terms of damped quasi-sinusoidal fields, and therefore the eigenvalue  $\Omega$  is complex. Its real part has the same meaning as in the lossless case (and thus the  $\omega - \beta$  diagram is obtained in the same way as before), whereas the imaginary part accounts for the damping which, according to the theory of resonant cavities, can be expressed in terms of the well-known quality factor Q [22]

$$Q = \frac{\omega_r}{2\omega_i}.$$

(3)

Moreover, it is possible to translate the time-domain damping factor Q into a distance-related attenuation factor  $\alpha$ , i.e., into the real part of the propagation constant of the quasi-TEM Floquet's mode [21], [23]:

$$\alpha = \frac{v_p}{v_q} \frac{\beta}{2Q} \tag{4}$$

where  $v_p = \omega/\beta$  and  $v_g = \partial \omega/\partial\beta$  are the phase- and group-velocity of the mode, respectively. Equation (4) can be simplified in our case, since very low dispersion is expected for the quasi-TEM mode, and  $\beta$  has an almost linear dependence on  $\omega$  (this condition can be verified from the  $\omega - \beta$  diagram in Section III). If this condition holds,  $v_p \approx v_g$ , and from (3) and (4) we finally have

$$\alpha = \beta \frac{\omega_i}{\omega_r} = \frac{\theta}{d} \frac{\omega_i}{\omega_r}.$$

(5)

Note that (5) is consistent with the usual definition of the quality factor of a transmission line [23]:

$$Q_L = \frac{\beta}{2\alpha}.$$

(6)

The procedure described above can be easily implemented by using HFSS as EM solution engine. In fact, condition (2) can be imposed by using a master–slave boundary condition [24] on surfaces  $S_1$  and  $S_2$  of the unit cell, assigning a given value  $\bar{\theta}$  for the periodic phase shift. To calculate the propagation constant at a target frequency  $\omega$ , an initial value of  $\bar{\theta} = \omega \sqrt{\varepsilon_r} d/c$  is chosen, where c is the velocity of light and  $\varepsilon_r$  is the relative dielectric constant of the oxide. Then the structure is analyzed by using the so-called eigenvalue solution, in order to find the first (i.e., smallest magnitude) eigenvalue  $\bar{\Omega} = \bar{\omega}_r + j\bar{\omega}_i$ . Its real part gives the value of the frequency corresponding to  $\bar{\beta} = \bar{\theta}/d$  and (5) is used to calculate  $\alpha$  at  $\bar{\omega}_r$ . By iterating the procedure for different values of  $\bar{\theta}$ , the dispersion and the attenuation curves of the periodic line in a given frequency range is obtained.

Finally, the resonant electric and magnetic fields  $\vec{E}_r$  and  $\vec{H}_r$ , obtained as eigensolution associated with the eigenvalue

Fig. 2. Definition of integration paths for voltage  $(\ell)$  and current (C) determination on CPW section.

$\overline{\Omega}$  found for any value of  $\overline{\theta}$ , can be used to calculate the characteristic impedance of the quasi-TEM mode at  $\omega_r$ . The possible definitions of characteristic impedance are in terms of the voltage and current  $(Z_{VI})$ , power and voltage  $(Z_{PV})$ , or power and current  $(Z_{PI})$  [25]

$$Z_{VI} = \frac{V}{I} \quad Z_{PV} = \frac{|V|^2}{2P^*} \quad Z_{PI} = \frac{2P}{|I|^2} \tag{7}$$

where V, I have the usual meaning, P is the complex power and "\*" denotes the complex conjugate. These quantities can be easily evaluated by using the Field Calculator of HFSS [26]:

$$V = \int_{\ell} \vec{E}_r \cdot d\vec{l}$$

$$I = \oint_{C} \vec{H}_r \cdot d\vec{c}$$

$$P = \frac{1}{2} \int_{S} \vec{E}_r \times \vec{H}_r^* \cdot \hat{z} \, ds$$

(8)

where  $\ell$  and C, shown in Fig. 2, are suitable integration path defined on the surface S (which may coincide with either  $S_1$  or  $S_2$ ), and  $\hat{z}$  is the normal to S. For MSs or CPWs the most used impedance definition is  $Z_{PI}$ , but all the definitions in (7) provide similar results, in the range of a few percent.

Note that, in finding the impedance of the periodic line, we use the resonant fields of the equivalent resonant-cavity model, instead of those of the true Floquet's mode, as it would be required by the theory of periodic structures. Actually, the two fields are slightly different, the former having the same magnitude at both ends of the unit cell [see (2)], the latter accounting also for the attenuation across the unit cell. Therefore, only approximated values of the impedance can be obtained by the equivalent resonant-cavity model. However, from a practical point of view, the accuracy in estimating the impedance is better than a few percent, provided the attenuation-per-unit cell is reasonably small, e.g., less than 0.01 dB per cell, a condition that applies in any line of practical use.

In order to validate this procedure, we have simulated a uniform 50  $\Omega$  MS transmission line, assuming the process parameters of a 65 nm CMOS process from STMicroelectronics, featuring 7 metal Cu layers plus an Al metal cover layer. Signal line is in Metal 7 and a solid ground is obtained shunting Metal 1 and 2 together. This structure, though not compliant with metal density design rules, has been selected since it can be analyzed

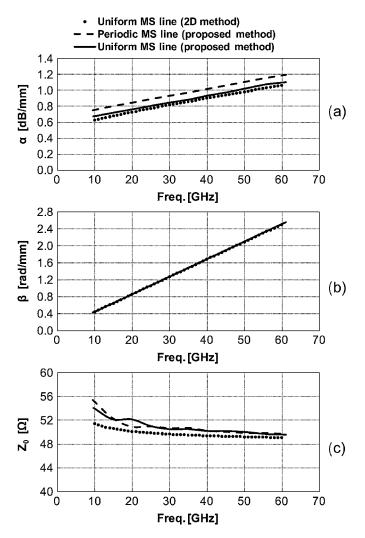

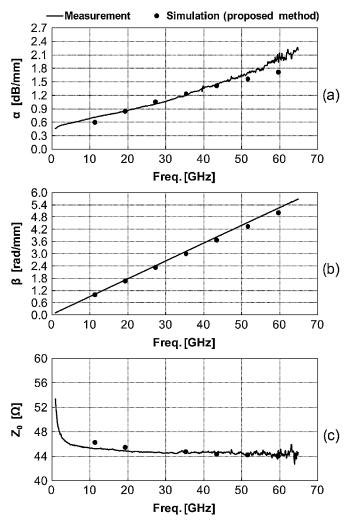

Fig. 3. (a) Attenuation, (b) phase constant, and (c) characteristic impedance versus frequency for a MS line. Simulations assuming a uniform line have been performed both by means of 2-D simulator ( $\bullet$ ) and proposed cavity-resonant model (—). Simulations of periodic structures (i.e., perforated ground plane) with proposed model are also reported (--).

either by conventional 2-D method or by the equivalent resonant-cavity model, defining a fictitious periodicity ( $d = 1 \ \mu m$  in this case). Fig. 3 shows the attenuation, the phase constant and the characteristic impedance as a function of frequency, comparing the results of our method versus the 2-D method of the commercial simulator HFSS. An excellent agreement emerges. To fulfill metal density rules for process planarity, we then introduced a periodically perforated ground plane, by using a configuration similar to the one introduced in [27] (metal strips of 0.55  $\mu$ m in the longitudinal and transverse direction; square holes 0.45  $\mu$ m × 0.45  $\mu$ m). The MS line is not uniform anymore, but still periodic, with the same period of 1  $\mu$ m as before. In this case, 2-D simulators cannot be adopted while our method can. Results for the periodic MS line are also reported in Fig. 3. At 60 GHz the design-rule compliant MS line features an attenuation constant of 1.2 dB/mm and a quality factor of 9.2. Note that the slots do not significantly influence the characteristic impedance, since they are much shorter than the wavelength, but they increase the attenuation constant of the MS. The simulation requires 212 s of CPU time and 84 MB of memory,

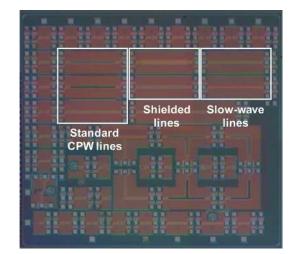

Fig. 4. Chip photomicrograph.

for each frequency point, on a PC using an Intel Core 2 Duo T7250 processor.

#### **III. DESIGN AND MEASUREMENTS**

Although MS lines offer an intrinsic good isolation from the substrate, its field being almost confined in the low-loss oxide region between ground and signal conductors, we used MS lines as validation test case only, and we did not realize any MS prototype. In fact, in order to reduce MS line attenuation and improve its quality factor, larger line-to-ground distance and line width would be required, but the former is set given the used process, the latter determines the characteristic impedance. For this reason we considered CPW lines only, where more parameters are available, allowing the designer to optimize the line geometry for better performances.

All the lines were fabricated in the same 65 nm CMOS process used in the microstrip simulations. Fig. 4 shows the chip photomicrograph. The lines were designed using the proposed method, employing the commercial simulator HFSS from Ansoft, and its "eigenmode" EM simulator engine in particular [28]. All simulations were performed on a personal computer with an Intel Core 2 Duo T7250 processor. All the measurements were performed using Cascade Infinity Probes and an Anritsu VNA. Probe tips calibration was performed on a standard alumina substrate, and measurements were de-embedded by the Open-Short method [29].

### A. Standard CPW Lines

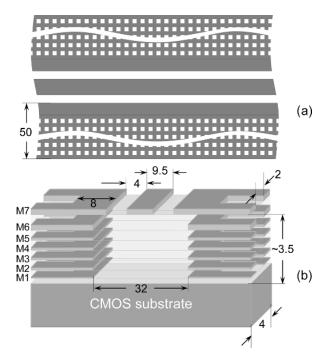

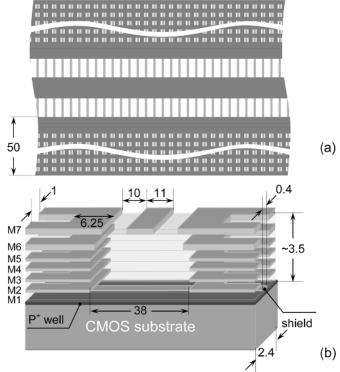

Fig. 5 shows the geometry used to obtain a standard CPW. The two ground conductors and the signal one are realized on the top metal layer, which offers the lowest sheet resistance and highest distance from the substrate. To achieve a desired characteristic impedance two parameters are available, i.e., the signal conductor width W and the gap distance G between signal and ground conductors. The design is made more complicate and achievable performances are limited by the need for a specified metal density at each metal level. Dummies in metal levels where signal and ground are drawn can limit realizable impedances, while those at other levels can impair performances.

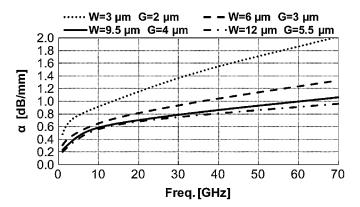

A set of lines, all with 50  $\Omega$  characteristic impedance, but with various signal conductor widths and gap distances has been

Fig. 5. Geometry of the proposed standard CPW transmission line: (a) top view; (b) detail of the cross section. Dimensions in  $\mu$  m (drawing not to scale).

Fig. 6. Attenuation constant of standard CPW lines (Z0  $\thickapprox$  50  $\Omega$  @ 60 GHz) for different values of signal width W and gap G.

simulated. In principle, an optimum performance is expected as a compromise between metal and substrate losses. In fact, increasing the width of the signal conductor decreases metal losses, but larger gaps are needed to keep the impedance value constant, causing a reduction of field confinement in the lowloss oxide gap region and an increase of substrate losses. Fig. 6 plots simulated results. Attenuation reduction is monotonic with increasing W and G. The benefit is marginal for  $W > 9.5 \ \mu m$ and  $G > 4 \ \mu m$ , though. Moreover, larger line width and gap complicate the layout in order to respect density rules. Thus we chose  $W = 9.5 \ \mu m$  and  $G = 4 \ \mu m$  as optima values. Characterization of the unit cell at one frequency point requires about 330 s and 150 MB of memory.

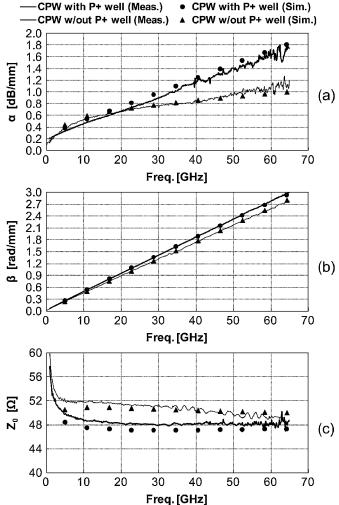

To verify the impact of  $P^+$  doped well on the surface of the CMOS substrate, introduced to prevent latch-up phenomena, two lines with the same geometry of Fig. 5 were realized, the

Fig. 7. (a) Attenuation, (b) phase constant, and (c) characteristic impedance versus frequency for the standard CPW shown in Fig. 5. Continuous lines show measurements of the CPW with  $P^+$  well layer (—) and without  $P^+$  well layer (—). Discrete points represent simulations.

only difference being a drawing layer which inhibits well diffusion. Fig. 7 shows measured and simulated results. Very good agreement can be observed in the whole frequency band. As expected, the P<sup>+</sup> well has a major impact on substrate losses, increasing attenuation from 1 dB/mm to 1.7 dB/mm at 60 GHz. Note that all dummy fills are connected to the ground planes through vias (not shown in Fig. 5), but no contacts are present between line ground-planes and substrate in proximity of the signal line: in fact, simulations show that in case of substrate contacts, the return currents would partially flow in the substrate due to the close spacing between top metals and substrate, producing a further increase in line attenuation.

# B. Slow-Wave CPW Lines

Slow-wave CPWs are a result of a smart use of the dense stratification available in modern CMOS processes, to artificially increase the effective dielectric constant of the line. This is achieved, as shown in Fig. 8, by adding equally spaced floating metal strips underneath the transmission line, to locally increase

Fig. 8. Geometry of the proposed slow-wave CPW transmission line: (a) top view; (b) detail of the cross section. Dimensions in  $\mu$  m (drawing not to scale).

the line capacitance: as a result, phase velocity of the line is decreased. In addition, these strips help fulfilling the metal density rules mitigating the problem of introducing metal dummies.

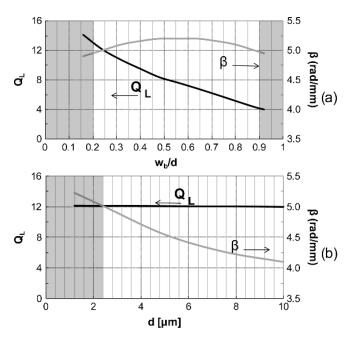

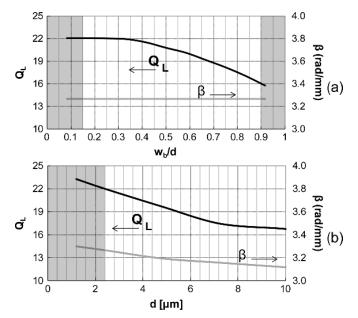

Besides W and G, a slow-wave CPW offers two additional degrees of freedom, i.e., the shield's metal strips width  $w_b$  and spacing s. These quantities define the period  $d = w_b + s$  of the unit cell. W and G control the characteristic impedance, like in a standard CPW. On the other hand, the values of  $w_b$ and s can be optimized in order to maximize shield efficiency and phase constant. These effects, however, are not simple to analyze with common methods. Relying on an accurate and fast simulation method, we were able to perform many simulations in order to gain more insight into slow-wave CPW design intended for matching networks, where the goal is maximum quality factor  $Q_L$ , maintaining a large value of the phase constant  $\beta$  for minimum area occupation. In these simulations, carried out at 60 GHz, we considered fixed values of  $W = 4.4 \ \mu m$ and  $G = 12 \ \mu m$ , allowing characteristic impedances close to 50  $\Omega$ . These values are at the edge of the allowed range for density rules fulfillment, and were not changed even if the obtained characteristic impedance was less than 50  $\Omega$ , since larger gaps violate design rules, and narrower line widths increase conductor losses too much. Fig. 9(a) shows  $Q_L$  and  $\beta$  as a function of the ratio  $w_b/d$  for a fixed period  $d = 2.5 \ \mu m$ . It is evident that reducing  $w_b$  yields larger values of  $Q_L$ , without affecting  $\beta$  too much. Characteristic impedance varies between 45.6  $\Omega$ for  $w_b/d = 0.16$  and 35.7  $\Omega$  for  $w_b/d = 0.92$ . Because the ratio  $w_b/d$  equals the metal density, not all values are possible (shaded regions in Fig. 9(a) correspond to metal densities forbidden by design rules), and the smallest feasible value should be used.

The effect of changing the unit cell period was also explored. Fig. 9(b) shows  $Q_L$  and  $\beta$  as a function of d, assuming a fixed

Fig. 9. Quality factor and phase constant of the slow-wave CPW transmission line at 60 GHz: (a) versus the ratio between strip width and unit cell period  $w_b/d$  for  $d = 2.5 \ \mu$ m; (b) versus cell period d for  $w_b/d = 0.24$ . Shadowed regions correspond to geometries forbidden by design rules.

ratio  $w_b/d = 0.24$ , i.e., a value close to the minimum allowed. In this case  $\beta$  increases for small values of d, while  $Q_L$  remains constant. Also in this case design rules set a limit to the minimum periodicity, due to the smallest feasible width of the strips  $(w_b \ge 0.5 \ \mu\text{m})$ . The shaded region in the plot corresponds to forbidden line widths. Characteristic impedance varies between 42.9  $\Omega$  for  $d = 1.2 \ \mu\text{m}$  and 51.9  $\Omega$  for  $d = 10 \ \mu\text{m}$ .

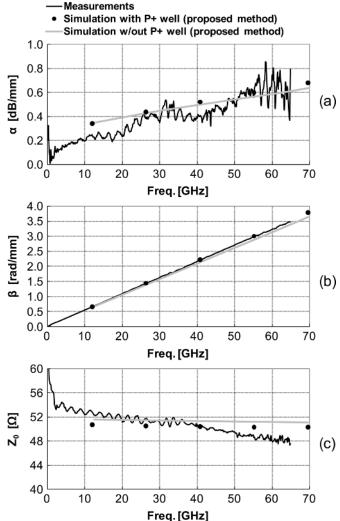

Based on these simulations, we designed the slow-wave CPW with the dimensions reported in Fig. 8. The resulting characteristic impedance is about 45  $\Omega$ . Measurements, performed on prototypes and reported in Fig. 10, show a very good agreement with simulations. Characterization of the unit cell at one frequency point requires about 320 s and 163 MB of memory. Note that  $\alpha$  and  $\beta$  are almost doubled with respect to the standard CPW line, i.e., slow-wave CPW provide the same quality factor  $(Q_L \cong 12 \text{ at } 60 \text{ GHz})$  as standard CPW, but they are suited to implement stubs and matching line sections using only half of the length, leading to a more compact circuit with unaltered performance. As a drawback, slow-wave lines usually require a larger cross-section for the same impedance as standard CPW line. Moreover, they allow increasing the capacitance per unit length, but the inductance is almost the same as for standard CPW lines: the range of feasible characteristic impedances is reduced with respect to standard CPW lines.

#### C. Shielded CPW Lines

As pointed out in Section III-A, in a standard CPW the EM field penetrates to some extent in the lossy CMOS substrate, contributing to the total attenuation factor. Using our method we could easily estimate this contribution, simulating a periodic cell with a fictitious loss-free CMOS substrate, and we found that in the CPW of Fig. 5 the substrate losses are about 40% of the total. The obvious remedy to reduce substrate losses would be to resort to an additional shielding metal layer, e.g., realized

Fig. 10. (a) Attenuation, (b) phase constant, and (c) characteristic impedance versus frequency for the slow-wave CPW shown in Fig. 8; measurement (—) and simulation with the proposed method  $(\bullet)$ .

in Metal 1, thus obtaining a grounded CPW (G-CPW) [30]. Unfortunately, this solution is not practical in our case, due to the small thickness of the oxide layers between Metal 1 and Metal 7 set by the CMOS process. In fact, a 50  $\Omega$  G-CPW designed in our process would have a maximum signal-line width W not much different from that of a MS, and a gap distance much larger than W (the structure would resemble more a MS-line than a G-CPW). In such a structure, a significant amount of longitudinal current would flow in the thinner bottom ground plane (Metal 1) rather than on the thicker top grounds (Metal 7), and the increase in metal losses would completely overwhelm the improvement in attenuation obtained by substrate shielding.

With these limitations in mind we considered a different shielding structure, inspired—to some extent—by the patterned ground used in shielded inductors, consisting of an array of thin metal strips realized in Metal 1, as shown in Fig. 11, and connected to the top ground planes. Actually, this screen can be seen as an equivalent bottom ground-plane with anisotropic resistivity (very high resistivity in the propagation direction, relatively low resistivity in the orthogonal direction), which

Fig. 11. Geometry of the proposed shielded CPW transmission line: (a) top view; (b) detail of the cross section. Dimensions in  $\mu$ m (drawing not to scale).

prevents the flow of longitudinal currents, still providing a good shielding of the substrate.

Metal strips geometry must be carefully optimized to obtain the maximum shielding efficiency, without introducing additional source of losses. As for the slow-wave CPW line, we carried out simulations at 60 GHz, to analyze the effects of metal strip width  $w_b$  and periodicity d for  $W = 11 \ \mu\text{m}$ ,  $G = 10 \ \mu\text{m}$ . The results are reported in Fig. 12, which show  $Q_L$  and  $\beta$  as a function of the ratio  $w_b/d$  for a fixed  $d = 2.4 \ \mu\text{m}$  and of d for a fixed value of  $w_b/d = 0.17$ , respectively. Again, shaded regions correspond to geometries forbidden by design rules. Plots show that the narrower the strips and the shorter the period, the higher  $Q_L$ ,  $\beta$  being less sensitive to the shield geometry. Characteristic impedance ranges from 49.3  $\Omega$  to 52.5  $\Omega$  for the geometries considered in the plots.

According to these considerations, we designed and realized a shielded-CPW (S-CPW) with the geometry shown in Fig. 11. After optimization, we chose  $W = 11 \ \mu m$ ,  $G = 10 \ \mu m$ ,  $w_b = 0.4 \ \mu m$  and  $d = 2.4 \ \mu m$ , in order to maximize  $Q_{L}$ ,  $\beta$ and to obtain a 50  $\Omega$  characteristic impedance. Note that in this case we were able to design the line for 50  $\Omega$ , without violating design rules. The strips were connected to the top ground planes and to the other dummy fills by vias displaced by 27  $\mu m$  from the structure centerline (for simplicity, vias are not shown in the figure). To better validate the effectiveness of the proposed S-CPW line, P<sup>+</sup> well was generated under the line in order to verify the shielding efficiency in the case where the substrate produces the worst impairment of attenuation.

Fig. 13 shows the good agreement between measured and simulated results. For comparison, also simulation results

Fig. 12. Quality factor and phase constant of the shielded CPW transmission line at 60 GHz: (a) versus the ratio between strip width and unit cell period  $w_b/d$  for  $d = 2.4 \ \mu$ m; (b) versus period d for  $w_b/d = 0.17$ . Shadowed regions correspond to geometries forbidden by design rules.

of the S-CPW on a substrate without P<sup>+</sup> well are reported, showing only a marginal improvement in attenuation (about 0.02 dB/mm), thus confirming the high shielding efficiency of the proposed structure). Simulation of the unit cell at one frequency point requires about 300 s and 148 MB of memory. The S-CPW shows an attenuation of 0.65 dB/mm at 60 GHz, i.e., a 30% improvement over standard CPW line. The shield affects also the phase constant of the S-CPW, which is increased by a 25% with respect to CPW. Consequently, the S-CPW features a quality factor  $Q_L = 22$  at 60 GHz, a figure almost doubled with respect to the CPW ( $Q_L = 12$  at 60 GHz). Note that, to the author's knowledge, the reported attenuation for S-CPW is the best performance ever obtained on a standard bulk 65 nm CMOS process. Additional simulations considering the same shielding structure with substrate contacts under the bottom metal bars show that also in this case line performance remains unaltered, confirming that no return currents flow in the lossy substrate.

#### IV. COMPARISON WITH STATE OF THE ART

The developed simulation method proves to be fast and accurate rate. As previously discussed, 2-D simulators are also accurate and fast, but they can be applied to uniform structures only. On the contrary, 3-D conventional methods not leveraging the periodicity of the line, require a huge amount of computational resources for an accurate result. As a final example, we have simulated the shielded CPW of Section III.C by means of a conventional 3-D simulator. In particular we considered line sections consisting of a variable number of unit cells. Increasing the number of cells, the results of the 3-D method tends to those of our method, of course at the expense of simulation time and required memory. Table I summarizes the results. Note that a conventional 3-D simulation of a line section consisting of 13

Fig. 13. (a) Attenuation, (b) phase constant, and (c) characteristic impedance versus frequency for the shielded CPW shown in Fig. 10; measurement (—) and simulation with the proposed method ( $\bullet$ ).

unit cells still provides results with an error of more than 6% in the characteristic impedance while requiring tens of minutes and some GB of memory. This suggests that an improved accuracy would require a prohibitive computational effort.

Finally, Table II compares performances of our realized CPW lines versus state of the art of integrated transmission lines of the same 50  $\Omega$  characteristic impedance. Noteworthy, although implemented in standard bulk CMOS, shielded CPW are comparable with lines realized in SiGe, SOI and high resistivity CMOS substrates [6], [7], [29]–[32].

#### V. CONCLUSION

We believe that the fast and accurate simulation method described in this paper can be very useful for the design of transmission lines for future industrial applications at mm-waves: not only to gain insight in the physical behaviour of complicated structures in order to optimize performances, but also to increase reliability of achieved results. Based on the proposed method, we have characterized several different CPW lines, either useful for a different function, e.g., slow-wave CPW for

TABLE I

Comparison Between 3-D Modal Analysis and Proposed Resonant Cavity Model

| Number of<br>Unit Cells | Memory<br>[MB] | CPU Time<br>[s] | α @ 60 GHz<br>[dB/mm] | β @ 60 GHz<br>[rad/mm] | Z <sub>0</sub> @ 60 GHz<br>[Ω] |  |

|-------------------------|----------------|-----------------|-----------------------|------------------------|--------------------------------|--|

| 3D Method               |                |                 |                       |                        |                                |  |

| 1                       | 85             | 36              | 4.00                  | 3.87                   | 40.60                          |  |

| 4                       | 830            | 257             | 2.83                  | 3.73                   | 42.69                          |  |

| 7                       | 1260           | 466             | 1.63                  | 3.69                   | 43.41                          |  |

| 10                      | 2410           | 1092            | 0.70                  | 3.70                   | 42.35                          |  |

| 13                      | 3040           | 1359            | 0.66                  | 3.54                   | 45.39                          |  |

| Proposed Method         |                |                 |                       |                        |                                |  |

| 1                       | 148            | 300             | 0.65                  | 3.33                   | 48.70                          |  |

| REF       | Technology                                          | Line type    | α @ 60 GHz<br>[dB/mm] |

|-----------|-----------------------------------------------------|--------------|-----------------------|

| [6]       | Intel CMOS 90nm High-<br>Resistivity (HR) Substrate | MS           | 1.2                   |

| [6]       | Intel CMOS 90nm HR                                  | CPW          | 0.6                   |

| [7]       | ST CMOS 90nm BULK                                   | G-CPW        | 1.1                   |

| [31]      | ST CMOS 130nm SOI                                   | CPW          | 0.65                  |

| [32]      | IBM SiGe 130nm                                      | MS           | 0.8                   |

| [33]      | ST CMOS 65nm SOI                                    | CPW          | 0.7                   |

| [34]      | ST SiGe 130nm - thick<br>copper metal option        | MS           | 0.5                   |

| This work | ST CMOS 65nm BULK                                   | CPW          | 1                     |

| This work | ST CMOS 65nm BULK                                   | Shielded-CPW | 0.65                  |

TABLE II State of the Art of 50  $\Omega$  Integrated Transmission Line

compact solutions, or shielded CPW when minimum attenuation, high Q is a key factor such as in resonators and low noise interconnects.

## ACKNOWLEDGMENT

The authors wish to thank Prof. Ali Niknejad and his group for fruitful discussions and for hosting chip characterization at Berkeley Wireless Research Center.

#### References

- P. Smulders, "Exploiting the 60 GHz band for the local wireless multimedia access: Prospects and future directions," *IEEE Commun. Mag.*, vol. 40, no. 1, pp. 140–147, Jan. 2002.

- [2] I. Gresham, A. Jenkins, R. Egri, C. Eswarappa, N. Kinayman, N. Jain, R. Anderson, F. Kolak, R. Wohlert, S. P. Bawell, J. Bennett, and J. P. Lanteri, "Ultra-wideband radar sensors for short-range vehicular applications," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 9, pp. 2105–2122, Sep. 2004.

- [3] B. Heydari, M. Bohsali, E. Adabi, and A. Niknejad, "Mm-wave devices and circuit blocks up to 104 GHz in 90 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2893–2903, Dec. 2007.

- [4] M. Varonen, M. Karkkainen, M. Kantanen, and K. Halonen, "Mmwave integrated circuits in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 9, pp. 1991–2002, Oct. 2008.

- [5] C.-L. Ko, C.-N. Kuo, and Y.-Z. Juang, "On-chip transmission line modeling and applications to millimeter-wave circuit design in 0.13 μm CMOS technology," in 2007 Int. Symp. VLSI Design, Automation and Test Dig. Tech. Papers, Apr. 2007, pp. 1–4.

- [6] S. Pellerano, Y. Palaskas, and K. Soumyanath, "A 64 GHz LNA with 15.5 dB gain and 6.5 dB NF," *IEEE J. Solid-State Circuits*, vol. 43, no. 7, pp. 1542–1552, Jul. 2008.

- [7] Y. Jin, M. A. T. Sanduleanu, and J. R. Long, "A wideband millimeterwave power amplifier with 20 dB linear power gain and +8 dBm maximum saturated output power," *IEEE J. Solid-State Circuits*, vol. 43, no. 7, pp. 1553–1562, Jul. 2008.

- [8] P. Leduc, A. Schellmanns, D. Magnon, and F. Guitton, "Frequency-dependant analytical modeling of integrated inductors based on design of experiments theory," in 2004 IEEE Radio Frequency Integrated Circuits Symp. Dig. Tech. Papers, Jun. 2004, pp. 631–634.

- [9] G. E. Ponchak, A. N. Downey, and L. P. B. Katehi, "High frequency interconnects on silicon substrates," in *1997 IEEE Radio Frequency Integrated Circuits Symp. Dig. Tech. Papers*, Jun. 1997, pp. 101–104.

- [10] M. A. T. Sanduleanu, G. Zhang, and J. R. Long, "31–34 GHz low noise amplifier with on-chip microstrip lines and inter-stage matching in 90-nm baseline CMOS," in 2006 IEEE Radio Frequency Integrated Circuits Symp. Dig. Tech. Papers, Jun. 2006, pp. 143–146.

- [11] W. Heinrich, J. Gerdes, F. J. Schmuckle, C. Rheinfelder, and K. Strohm, "Coplanar passive elements on SI substrate for frequencies up to 110 GHz," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 5, pp. 2264–2268, May 1998.

- [12] A. C. Reyes, S. M. El-Ghazaly, S. J. Dorn, M. Dydyk, D. K. Schroder, and H. Patterson, "Coplanar waveguides and microwave inductors on silicon substrates," *IEEE Trans. Microw. Theory Tech.*, vol. 43, no. 9, pp. 2016–2022, Sep. 1995.

- [13] T. D. Cheung and J. R. Long, "Shielded passive devices for siliconbased monolithic microwave and millimeter-wave integrated circuits," *IEEE J. Solid-State Circuits*, vol. 41, no. 5, pp. 1183–1200, May 2006.

- [14] I. C. H. Lai, Y. Kambayashi, and M. Fujishima, "60-GHz CMOS down-conversion mixer with slow-wave matching transmission lines," in 2006 IEEE Asian Solid State Circuits Conf. Dig. Tech. Papers, Nov. 2006, pp. 195–198.

- [15] R. E. Collin, Foundations for Microwave Engineering, 2nd ed. New York: McGraw-Hill, p. 96.

- [16] R. W. Jackson, "Mode conversion due to discontinuities in modified coplanar grounded waveguide," in *1988 IEEE MTT-S Int. Microwave Symp. Dig. Tech. Papers*, May 1988, pp. 203–206.

- [17] Y. R. Kwon, "Periodically screened coplanar waveguides on semiconductors," *Electron. Lett.*, vol. 27, no. 18, pp. 1665–1667, Aug. 1991.

- [18] R. E. Collin, Foundations for Microwave Engineering, 2nd ed. New York: McGraw-Hill, p. 569.

- [19] Y. Cassivi, L. Perregrini, P. Arcioni, M. Bressan, K. Wu, and G. Conciauro, "Dispersion characteristics of substrate integrated rectangular waveguide," *IEEE Microw. Wireless Compon. Lett.*, vol. 11, no. 2, pp. 333–335, Sep. 2002.

- [20] F. Xu, Y. Zhang, W. Hong, K. Wu, and T. J. Cui, "Finite-difference frequency-domain algorithm for modelling guided-wave properties of substrate integrated waveguide," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 11, pp. 2221–2227, Nov. 2003.

- [21] F. Xu, K. Wu, and W. Hong, "Equivalent resonant cavity model of arbitrary periodic guided-wave structures and its application to finitedifference frequency-domain algorithm," *IEEE Trans. Microw. Theory Tech.*, vol. 55, no. 4, pp. 697–702, Apr. 2007.

- [22] R. E. Collin, Foundations for Microwave Engineering, 2nd ed. New York: McGraw-Hill, p. 536.

- [23] H. P. Hsu, "On the general relation between α and Q (correspondence)," *IEEE Trans. Microw. Theory Tech.*, vol. 11, no. 4, p. 258, Jul. 1963.

- [24] HFSS Online Help, section 16, paragraph 79, Ansoft Corp., Dec. 2007.

- [25] J. R. Brews, "Characteristic impedance of microstrip lines," *IEEE Trans. Microw. Theory Tech.*, vol. 35, no. 1, pp. 30–34, Jan. 1987.

- [26] *HFSS Field Calculator Cookbook*, Ansoft Corp., 2000, pp. 10-12.

- [27] A. M. Mangan, S. P. Voinigescu, M.-T. Yang, and M. Tazlauanu, "Deembedding transmission line measurements for accurate modeling of IC designs," *IEEE Trans. Electron Devices*, vol. 53, no. 2, pp. 235–241, Feb. 2006.

- [28] HFSS Online Help, section 16, paragraph 25, Ansoft Corp., Dec. 2007.

- [29] T. E. Kolding, "On-wafer calibration techniques for giga-hertz CMOS measurements," in *Proc. 1999 IEEE Int. Conf. Microelectronic Test Structures*, Mar. 1999, pp. 105–110.

- [30] R. N. Simons, Coplanar Waveguide Circuits Components and Systems. New York: Wiley-IEEE Press, Apr. 2001.

- [31] F. Gianesello, D. Gloria, S. Montusclat, C. Raynaud, S. Boret, G. Dambrine, S. Lepilliet, B. Martineau, and R. Pilard, "1.8 dB insertion loss 200 GHz CPW band pass filter integrated in HR SOI CMOS technology," in 2007 IEEE/MTT-S Int. Microwave Symp. Dig. Tech. Papers, Jun. 2007, pp. 453–456.

- [32] T. Zwick, Y. Tretiakov, and D. Goren, "On-chip SiGe transmission line measurements and model verification up to 110 GHz," *IEEE Microw. Wireless Compon. Lett.*, vol. 15, no. 2, pp. 65–67, Feb. 2005.

- [33] B. Martineau, A. Cathelin, F. Danneville, A. Kaiser, G. Dambrine, S. Lepilliet, F. Gianesello, and D. Belot, "80 GHz low noise amplifiers in 65 nm CMOS SOI," in *Proc. 33rd European Solid State Circuits Conf. (ESSCIRC)*, Sep. 2007, pp. 348–351.

- [34] G. Avenier, P. Chevalier, G. Troillard, B. Vandelle, F. Brossard, L. Depoyan, M. Buczko, S. Boret, S. Montusclat, A. Margain, S. Pruvost, S. T. Nicolson, K. H. K. Yau, D. Gloria, D. Dutartre, S. P. Voinigescu, and A. Chantre, "0.13 μm SiGe BiCMOS technology for mm-wave applications," in *Proc. 2008 Bipolar/BiCMOS Circuits and Technology Meeting*, Oct. 2008, pp. 89–92.

Federico Vecchi (S'07) was born in Broni, Italy, in 1982. He received the B.S. and M.S. degrees in electronics engineering from the University of Pavia, Italy, in 2004 and 2006, respectively. In 2006 he joined the Department of Electronics, University of Pavia, as a Ph.D. student in microelectronics. He holds a research grant on RFIC design topics from IUSS–Institute for Advanced Studies–Pavia.

In 2007 he spent a period at the BWRC, Berkeley, CA, working on the characterization of integrated CMOS devices for millimeter-wave applications.

His current research interests include design and modeling techniques of analog components for millimeter-wave and RF applications on submicron CMOS technologies.

**Matteo Repossi** was born in Pavia, Italy, in 1977. He received the Laurea and the Ph.D. degrees in electronics engineering from the University of Pavia, Pavia, Italy, in 2002 and 2006, respectively.

In 2005, he was with DIEI, University of Perugia, Perugia, Italy, as a Guest Researcher in the framework of a national research project on wideband RF-MEMS circuits. In 2006, he joined STMicroelectronics within the Studio di Microelettronica, Pavia, where his research is focused on the design and characterization of RF/MW components and

circuits.

Dr. Repossi was the recipient of the Second Best Student Paper Award at the 2004 Applied Computational Electromagnetics Software Conference, Syracuse, NY.

Wissam Eyssa was born in Cairo, Egypt, in 1975. He received the Laurea degree and the Ph.D. degree in electronic engineering from the University of Pavia, Italy, in 2003 and 2007, respectively. The topic of his Ph.D. work was concerning theoretical study of electromagnetic numerical methods and implementation of a new efficient code for wide band modeling of microwave waveguide components loaded with dielectric insets. This code permitted accurate and rapid design of microwave waveguide filters based on the resonance of inserted dielectric insets.

Since 2007 his interests have included CMOS RF design and modeling of passive and active components for millimeter-wave applications. Currently, he has a grant from IUSS–Institute for Advanced Studies–Pavia.

**Paolo Arcioni** (M'90–SM'03) received the Laurea degree in electronic engineering from the University of Pavia, Pavia, Italy, in 1973.

In 1974 he joined the Department of Electronics, University of Pavia, where he currently teaches microwave theory as a Full Professor. His research activity initially concerned the design and the characterization of compensated structures for linear accelerators, the development of microwave equipment for EPR and the investigation of ferrite tuning of power magnetrons. Subsequently, his scientific interest con-

centrated on the study of a novel class of numerical methods, based on a hybrid representation of the electromagnetic field (boundary integral-resonant mode expansion, BI-RME). These methods have been applied successfully to the development of efficient codes for the design and the optimization of waveguide components and to the modeling of active and passive quasi-optical components for millimeter and sub-millimeter wavelengths. More recently, the same approach has been extended to the modeling of microstrip circuits on multi-layered substrates. His current research activities concern the modeling of planar components on semiconductor substrates and of integrated structures for millimeter-wave circuits. In 1991, he was a Visiting Scientist at the Stanford Linear Accelerator Center, Stanford, CA, where he worked in cooperation with the RF Group to design optimized cavities for the PEP II Project. From 1992 to 1993, he collaborated with the Istituto Nazionale di Fisica Nucleare (INFN), Frascati, Italy, on the design of the accelerating cavities for the DAΦNE storage ring. In 2004, he became Head of the Department of Electronics, University of Pavia.

Francesco Svelto (S'94–M'98) received the Laurea and Ph.D. degrees in electrical engineering from Università di Pavia, Italy, in 1991 and 1995, respectively.

During 1995–1997 he held an industry grant for research in RF CMOS. In 1997 he was appointed Assistant Professor at Università di Bergamo, and in 2000, he joined Università di Pavia, where he is now Professor. His current interests are in the field of RF and high speed integrated circuits. He has been technical advisor of RFDomus Inc., a start-up he co-founded in 2002 dedicated to highly integrated GPS receivers.

After merging with Glonav Inc. (Ireland), RFDomus was acquired by NXP Semiconductors in 2007. Currently, he is the Director of a Scientific Laboratory, joint between Università di Pavia and STMicrolectronics, dedicated to research in Microelectronics, with emphasis to mm-wave systems for wireless communications, high-speed serial links and read-write channels for hard disk-drives.

Dr. Svelto is a member of the technical program committee of the IEEE International Solid-State Circuits Conference and has been a member of the IEEE Custom Integrated Circuits Conference, Bipolar/BiCMOS Circuits Technology Meeting, and European Solid State Circuits Conference. He has served as Associate Editor of IEEE JOURNAL OF SOLID-STATE CIRCUITS (2003–2007), and as Guest Editor for a special issue on the same journal in March 2003. He was a co-recipient of the IEEE JOURNAL OF SOLID-STATE CIRCUITS 2003 Best Paper Award.