# Design of Power/Ground Noise Suppression Structures Based on a Dispersion Analysis for Packages and Interposers with Low-Loss Substrates

Youngwoo Kim D

Article

Abstract: In this study, power/ground noise suppression structures were designed based on a proposed dispersion analysis for packages and interposers with low-loss substrates. Low-loss substrates are suitable for maintaining signal integrity (SI) of high-speed channels operating at high data rates. However, when the power/ground noise is generated in the power delivery network (PDN), low-loss substrates cannot suppress the power/ground noise, thereby causing PDN-induced crosstalk and various power integrity (PI) issues. To solve these issues, noise suppression structures generating electromagnetic bandgap were proposed and designed. The mechanism of the proposed structures was examined based on a proposed dispersion analysis. The proposed structures were designed and fabricated in glass interposer test vehicles, and the effectiveness of the structures on power/ground noise suppression was experimentally validated by measuring the noise suppression band. The proposed dispersion analysis was also verified by comparing the derived noise stopband edges ( $f_L$  and  $f_U$ ) with electromagnetic (EM) simulation and experimental results, and they all showed good agreement. Compared to EM simulation, the proposed method required smaller computational resources but showed good accuracy. Using the proposed dispersion analysis, various power/ground noise suppression bands were designed considering the applications and design rules of packages and interposers. With measurements and EM/circuit simulations, the effectiveness of the designed structure in maintaining SI/PI was verified. By adopting the designed structures, the noise transfer properties in the PDN were suppressed in the target suppression frequency band, which is key for PI design. Finally, it was verified that the proposed structures were capable of suppressing power/ground noise propagation in the PDN by analyzing PDN-induced crosstalk in the high-speed channel.

**Keywords:** electromagnetic bandgap (EBG); interposers; low-loss substrates; noise suppression structures; packages; power delivery network (PDN); power/ground noise

## 1. Introduction

Transistor scaling based on Moore's law is facing a limit. At the same time, the realization of electrical systems with wide bandwidth, superior performances, small form factor, low power consumption, and reduced manufacturing cost has been a continuous challenge. System scaling based on through-silicon via and interposer technologies is a promising solution for current industrial challenges [1–5]. Recently, silicon interposers have been widely used to integrate graphic processing unit (GPU) and high bandwidth memory (HBM) to form 2.5-dimensional (2.5-D) systems to realize over terabyte per second (TB/s) system bandwidths for extremely high-performance computing [6,7]. However, reducing the manufacturing cost of silicon interposers is still difficult due to the throughput issues associated with limited wafer dimension. Even though silicon interposer-based integration and packaging provides promising solutions, reducing the manufacturing cost is difficult due to the following reasons: throughput issues associated with limited wafer dimension and additional fabrication steps to isolate metal layers from the conductive silicon substrate.

Citation: Kim, Y. Design of Power/Ground Noise Suppression Structures Based on a Dispersion Analysis for Packages and Interposers with Low-Loss Substrates. *Micromachines* **2022**, *13*, 1433. https://doi.org/10.3390/ mi13091433

Academic Editor: Wensheng Zhao

Received: 30 July 2022 Accepted: 26 August 2022 Published: 30 August 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). Moreover, the finite conductivity of the silicon substrate can generate signal integrity (SI) issues in the high-frequency range, which may limit high-speed digital signaling, radio frequency (RF) applications, and mixed-signal integrations [8]. Because of these limitations, packages and interposers with low-loss substrates have gained attention as a long-term alternative to silicon interposers.

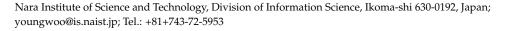

Packages and interposers with low-loss substrates have been continuously developed. Glass substrates have several advantages, such as dimensional stability, coefficient of thermal expansion (CTE) similar to silicon, smooth surface, submicron metallization, double-sided build-up lamination, and superior electrical resistivity enabling low insertion loss up to millimeter (mm)-wave range [9–11]. Recently, glass substrates have been widely adopted for various packaging applications, such as bandpass filters for 5G communication [12], MEMS [13], millimeter-wave radar for autonomous driving [14], and antennas [15,16]. Fan-out packages with low-loss materials have also been widely adopted [17]. Ultrathin, high-permittivity, and low-loss substrates have been released in the market for printed circuit boards (PCBs), which can also be embedded in packages to realize embedded decoupling capacitors [18,19]. These substrate materials are fabricated from panels that are much larger in dimension compared to silicon wafers. Therefore, these substrates also have the potential to reduce the fabrication cost due to increased yield. The advantages are depicted in Figure 1.

**Figure 1.** Advantages of low-loss substrate for packages and interposers. (a) Ultrathin (sub 100  $\mu$ m) and fine-pitch metallization; (b) high fabrication yield, which has great potential for cost reduction; (c) low signal loss, enabling high-speed signaling.

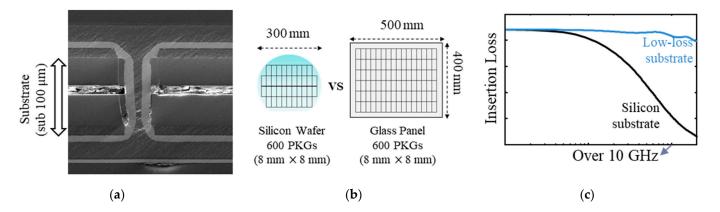

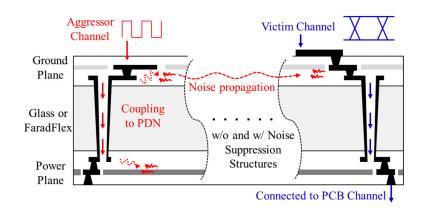

Despite these advantages and potentials, low-loss substrates are vulnerable to power/ground noise generated in the power delivery network (PDN) [20]. Low-loss substrates are excellent for high-frequency signaling, but at the same time, it is difficult to suppress power/ground noise induced in the PDN. The noise can be induced in the PDN due to various reasons, such as simultaneous switching noise (SSN), return current discontinuity of the signal via penetration of the PDN, and coupling from other signal/power/ground interconnections. When the power/ground noise is generated, it propagates along the PDN without suppression, causing various SI/PI (power integrity) and electromagnetic interference (EMI) issues. These issues are shown in Figure 2. When designing a PDN, the allowed power/ground noise margin is becoming tighter because the operating voltages of electrical systems are continuously decreasing to realize low power consumption [21]. Moreover, due to recent trends requiring system-in-package, heterogeneous integration, and mixed modes, various noises are generated in the broadband frequency range. To maximize the advantages of low-loss substrates, power/ground noise must be suppressed and effective suppression bands should be analyzed in advance.

**Figure 2.** Issues related to low-loss substrate. When the noise is induced in the PDN due to SSN, P/G noise, or return current loading, low substrate loss cannot suppress it. The noise propagates along the PDN and causes SI/PI problems.

Decoupling capacitor arrays and schemes may be insufficient for achieving broadband power/ground noise suppression. Moreover, assembling various decoupling capacitors to achieve broadband suppression can increase the lateral dimensions of packages and interposers, which directly affects the fabrication yield. For security applications, exposed decoupling capacitors attached to the cryptographic core PDN cause electromagnetic (EM) information leakages and security issues [22,23]. Various electromagnetic bandgap (EBG) structures that are mostly embedded inside the PDN have been proposed and validated to achieve wideband power/ground noise suppression [24–31]. Considering recent trends requiring broadband noise suppression without dramatically affecting lateral dimensions of the package/interposer and unexposed areas for some applications, adopting the EBG structure embedded in the PDN is one of the most promising solutions to solve the power/ground noise issues associated with low substrate loss. However, such structures have not been widely developed and applied for packages and interposers with low-loss substrates. Therefore, an efficient design method considering design parameters and material properties is desired. Using the method, noise suppression structures should be developed and verified.

In this study, power/ground noise suppression structures were designed based on a proposed dispersion analysis for packages and interposers with low-loss substrates. The mechanism of noise suppression was thoroughly examined based on the proposed dispersion analysis. The structures were designed and fabricated in glass interposer test vehicles, and the effectiveness of the structures was experimentally validated by measuring the noise suppression band. The proposed dispersion analysis was also verified by comparing derived noise stopband edges ( $f_L$  and  $f_U$ ) with electromagnetic (EM) simulation. It was confirmed that  $f_L$  and  $f_U$  estimations based on the proposed analysis method showed good agreement with those acquired from experiments and simulations. Compared to EM simulation, the proposed method required smaller computational resources but showed good accuracy, which is suitable for early design stages. Using the proposed dispersion analysis, various power/ground noise suppression bands were designed considering the applications and design rules of packages and interposers. With measurements and EM simulations, the effectiveness of the designed structure in maintaining SI/PI was ver-

ified. Finally, it was shown that the proposed structures were capable of suppressing power/ground noise propagation in the PDN by analyzing PDN-induced crosstalk in the high-speed channel.

# 2. Proposed Dispersion Analysis: Mechanism of Noise Suppression Band Formation and Stopband Edge Estimation

In this section, a dispersion analysis is proposed to explain the mechanism of noise suppression band formulation in the PDN. The proposed dispersion analysis is also capable of deriving noise suppression (stopband) edges. The proposed dispersion analysis is based on a transmission line (TL) theory and mathematics. Compared to full EM simulations, which require heavy computational resources, the proposed method can efficiently estimate the suppression band. In addition, the impacts of material properties and design rules on the suppression band can be easily understood.

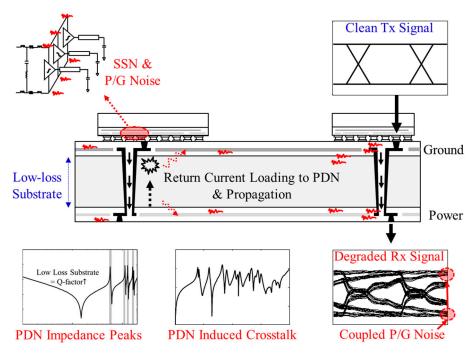

Compared to mesh or grid-type PDN structures in silicon interposers, plane-type PDN can be fabricated in packages and interposers with low-loss substrates, such as glass, ceramic, and organic materials [9,18]. In the plane-type PDN, the power/ground noise propagates in forms of transverse electromagnetic (TEM) and quasi-TEM modes. The PDN becomes a transmission line (TL) for the noise wave. To suppress noise propagation, a noise suppression band can be formed by designing certain repetitive structures generating lumped capacitance (*C*) and inductance (*L*). The band must be analyzed and engineered to cover the target noise band. In this study, power/ground noise propagation is analyzed in the +*x*-direction (**N**(*x*) =  $e^{-jk_x x} \mathbf{a}_x$ ).  $k_x$  is an effective phase constant defined as  $k_x = \alpha_x + j\beta_x$ , where  $\alpha_x$  becomes an attenuation constant and  $\beta_x$  is a propagation constant of the power/ground noise wave propagating in the +x-direction. Let the size of the repetitive structure formed in the PDN be  $W_{\rm u}$ . A two-dimensional periodic structure can be reduced into a one-dimensional array of unit cells (size of  $W_u$ ) by placing perfect magnetic conductor (PMC) walls at  $y = \pm W_u/2$ , as depicted in Figure 3. This assumption and dimension reduction can be applied as the PMC wall can be located anywhere where there is a zero tangential magnetic (H) field [31–33]. By adopting the PMC boundary condition, the noise suppression structure and the PDN can be modeled as TL with lumped C and L. In the following sections, detailed equations for *C* and *L* are provided considering the design, physical dimensions, and material properties.

In typical advanced packages and interposers, build-up layers exist in between the substrate and metal layers (ML), as shown in Figure 3. The power/ground noise propagating in the form of the quasi-TEM mode can be modeled into a TL. The TL has a thickness of  $t_{PDN}$ , which is summation of the substrate thickness ( $t_{sub}$ ) and the thickness of two build-up layers ( $t_{bu}$ ). The dielectric layers in between power and ground planes can be modeled as a single dielectric mixture layer represented with the effective complex dielectric constant ( $\varepsilon_{mix}(\omega)$ ) shown in the following equation:

$$\varepsilon_{\rm mix}(\omega) = \frac{\varepsilon_{\rm sub}(\omega)\varepsilon_{\rm bu}(\omega)}{q\varepsilon_{\rm sub}(\omega) + (1-q)\varepsilon_{\rm bu}(\omega)} \tag{1}$$

where *q* is the volume fraction of the dielectric layers;  $\varepsilon_{sub}(\omega)$  and  $\varepsilon_{bu}(\omega)$  are complex permittivity of the substrate and build-up layer, respectively [34]; and  $\omega$  is the angular frequency (2 $\pi f$ ). Real parts of the  $\varepsilon_{mix}(\omega)$ ,  $\varepsilon_{sub}(\omega)$ , and  $\varepsilon_{bu}(\omega)$  are defined as  $\varepsilon_{r,mix}$ ,  $\varepsilon_{r,sub}$ , and  $\varepsilon_{r,bu}$ , respectively.

**Figure 3.** One-dimensional equivalent circuit model of the PDN with structure generating *C* and *L*. Considering the *H*-field direction, PMC boundary condition is adopted to reduce the two-dimensional PDN into one-dimensional domain in the *x*-direction.  $\mathbf{a}_x$  is a unit vector.

Characteristic impedance ( $Z_{0, PDN}$ ) and phase constant ( $\beta_{PDN}$ ) of the TL without C and *L* can be expressed as follows:

$$Z_{0,\text{PDN}} = \frac{\eta_0}{\sqrt{\varepsilon_{\text{r,mix}}}} \frac{t_{\text{PDN}}}{W_{\text{u}}}, \ t_{\text{PDN}} = t_{\text{sub}} + 2t_{\text{ub}}$$

(2)

and

$$\beta_{\rm PDN} = \sqrt{\varepsilon_{\rm r,mix}} \omega / c \tag{3}$$

where  $\eta_0$  is the wave impedance of free space, and *c* is the speed of light in a vacuum.

1

To derive the dispersion equations to estimate the noise stopband, *ABCD* parameters of the TL shown in Figure 3 is analyzed. The unit cell of the TL has an effective phase constant  $k_x$ . Compared to the silicon, the substrate and build-up layer of the target study have much lower loss factors. Therefore, lossless condition is adopted for an efficient calculation during the dispersion analysis. The *ABCD* parameters of the TL's unit cell can be expressed as follows:

$$\begin{bmatrix} A_{u} & B_{u} \\ C_{u} & D_{u} \end{bmatrix} = \begin{bmatrix} \cos(k_{x}W_{u}) & jZ_{0,u}\sin(k_{x}W_{u}) \\ jZ_{0,u}^{-1}\sin(k_{x}W_{u}) & \cos(k_{x}W_{u}) \end{bmatrix}$$

$$= \begin{bmatrix} \cos\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) & jZ_{0,\text{PDN}}\sin\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) \\ jZ_{0,\text{PDN}}^{-1}\sin\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) & \cos\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) \end{bmatrix} \times \begin{bmatrix} 1 & 0 \\ Y & 1 \end{bmatrix} \times \begin{bmatrix} \cos\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) & jZ_{0,\text{PDN}}\sin\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) \\ jZ_{0,\text{PDN}}^{-1}\sin\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) & \cos\left(\beta_{\text{PDN}}\frac{W_{u}}{2}\right) \end{bmatrix}$$

$$(4)$$

where  $Y = j\omega C/(1 - \omega^2 LC)$ , and  $Z_{0,u}$  is the characteristic impedance of TL with the structure inducing *L* and *C*. Among the four parameters,  $A_u$  is the simplest. By analyzing  $A_u$ , a dispersion equation is derived as follows:

$$A_{\rm u} = \cos(k_x W_{\rm u}) = \cos(\beta_{\rm PDN} W_{\rm u}) + j \frac{Z_{0,\rm PDN} Y}{2} \sin(\beta_{\rm PDN} W_{\rm u})$$

(5)

From (5), the effective phase constant  $k_x$  is derived as follows:

$$k_x = \frac{1}{W_u} \cos^{-1} \left[ \cos(\beta_{\text{PDN}} W_u) - \frac{\omega Z_{0,\text{PDN}} C}{2(1 - \omega^2 L C)} \sin(\beta_{\text{PDN}} W_u) \right]$$

(6)

In this study, the lossless condition has been assumed. However, the effective phase constant  $k_x$  becomes a complex number. The effective phase constant has an imaginary part when the argument of the inverse cosine function in (6) is outside the interval [-1, 1]. The noise stopband is formed at the frequency range where the imaginary part of (6) is nonzero and changes dramatically. The wave becomes evanescent at this frequency range.

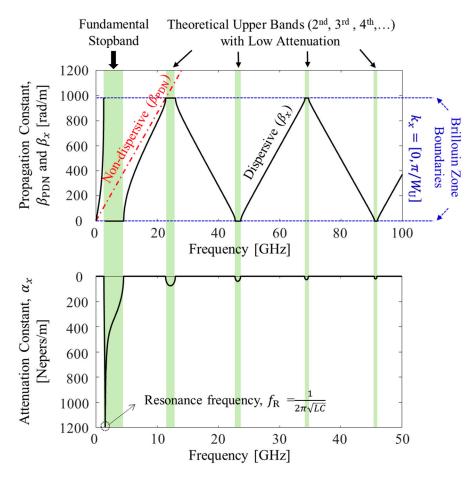

To graphically explain the noise propagation characteristics, dispersion diagrams are estimated from (6) and plotted in Figure 4 as an example. The design parameters and values to derive dispersion diagrams shown in Figure 4 are summarized in Table 1. Values are carefully chosen to derive diagrams that can graphically support the method and concept. Without noise suppression structures in the PDN, the propagation constant of the power/ground noise has a constant slope  $(2\pi\sqrt{\varepsilon_{r,mix}}/c)$  in the frequency domain, which is nondispersive. When the structure forming the *L* and *C* is inserted in the PDN, the power/ground noise propagating in the +*x*-direction  $(e^{-jk_xx})$  will experience sudden attenuation at certain frequency band. Let  $-jk_x = -\alpha_x - j\beta_x$ , and  $\alpha_x$  becomes an attenuation constant of the power/ground noise wave. In this case,  $\beta_x$  is periodic due to periodicity of the inverse cosine function.

**Table 1.** Summary of important design parameters and values used to derive dispersion diagrams shown in Figure 4.

| <i>e</i> <sub>r,mix</sub> | Z <sub>0,PDN</sub> | W <sub>u</sub> | L         | С         |

|---------------------------|--------------------|----------------|-----------|-----------|

| 4.25                      | 9.14 Ω             | 3.2 mm         | 125.49 pH | 22.831 pF |

As can be seen from Figure 4, there are frequency bands where the slope of  $\beta_x$  becomes closer to zero (or  $\beta_x$  is at the Brillouin zone boundaries) or the attenuation constant  $\alpha_x$  becomes nonzero. These frequency bands are theoretical noise bandgap or electromagnetic bandgap (EBG) where power/ground noise is suppressed and cannot propagate. However, except for the fundamental stopband, the attenuation constant for other bands are too small to suppress noise propagation.

In this study, the dispersion equations are calculated and plotted under the assumption of lossless substrate and build-up layer. In reality, there always exists attenuation of the wave associated with dielectric loss. Usually, noise suppression bands are valid if they can achieve -40 dB or lower isolation characteristics. Therefore, theoretical upper bands marked in Figure 4 cannot play a role as a suppression band. A band that can suppress power/ground noise will exist inside the fundamental stopband marked in Figure 4.

**Figure 4.** Dispersion diagrams. Without noise suppression structures in the PDN, the power/ground noise is nondispersive. With noise suppression structures, theoretical stopbands are generated.

The lower edge of the noise suppression band  $(f_L)$  can be derived by finding the condition satisfying " $A_u = \cos(k_x W_u) = -1$ ". Among various cases, " $k_x W_u = \pi$ " is selected in this study. Because  $\beta_{PDN}W_u$  is located far from the Brillouin zone boundary at the lower cut-off frequency, the small-angle approximation " $\sin(\beta_{PDN}W_u) \approx \beta_{PDN}W_u$ " and " $\cos(\beta_{PDN}W_u) \approx 1$ " can be used. Under these conditions, (6) can be rewritten as follows:

$$-1 = 1 - \frac{\omega Z_{0,\text{PDN}} C}{2(1 - \omega^2 L C)} \beta_{\text{PDN}} W_{\text{u}}.$$

(7)

Because the wave impedance of free space ( $\eta_0$ ) can be expressed as  $\mu_0 c$ , the lower edge of the noise suppression band ( $f_L$ ) can be derived from (7) and is shown in the following equation:

$$f_{\rm L} = \frac{1}{\pi \sqrt{C \left(\mu_0 t_{\rm PDN} + 4L\right)}} \tag{8}$$

By setting different boundary condition, it is possible to estimate the upper edge of the noise suppression band ( $f_U$ ). It can be obtained by adopting conditions that satisfy " $A_u = \cos(k_x W_u) = +1$ ". Under this condition, (6) becomes the following:

$$\tan\left(\frac{\beta_{\text{PDN}}W_{u}}{2}\right) = \frac{-\omega C Z_{0,\text{PDN}}}{2(1-\omega^{2}LC)}$$

(9)

If  $f_U$  and the resonant frequency  $(f_R = \frac{1}{2\pi\sqrt{LC}})$  are far away from each other, (9) can be approximated as follows:

$$\tan\left(\frac{\pi\sqrt{\varepsilon_{\rm r,mix}}W_{\rm u}}{c}f_{\rm U}\right) \approx \pi c f_{\rm R}^2 Z_{0,\rm PDN} \frac{1}{f_{\rm U}} = \frac{Z_{0,\rm PDN}}{4\pi L} \frac{1}{f_{\rm U}}$$

(10)

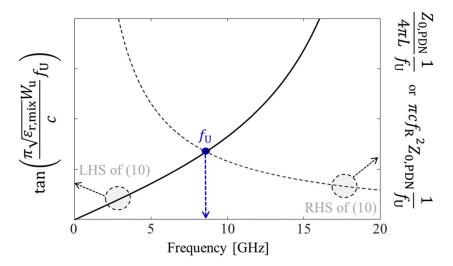

From (10), it is difficult to directly estimate  $f_U$ . A graphical (numerical) approach is applied to estimate  $f_U$ , and an example is shown in Figure 5. In Figure 5, the left-hand side (LHS) and right-hand side (RHS) of (10) are plotted in the frequency domain. The frequency where the two graphs intersect is the upper edge of the noise suppression band ( $f_U$ ).

**Figure 5.** Estimation of  $f_U$  based on a graphical approach shown as an example. The LHS and RHS of (10) are plotted in the frequency domain. The intersection frequency of LHS and RHS is  $f_U$ .

The following section outlines the design and fabrication of test vehicles with thin and low-loss glass substrate and low-loss polymer as a build-up material. The test vehicles were measured to validate the proposed dispersion analysis and effectiveness of the proposed structures on noise suppression.

# **3. Verification of the Proposed Dispersion Analysis and Noise Suppression Structures** *3.1. Design and Fabricated Test Vehicles*

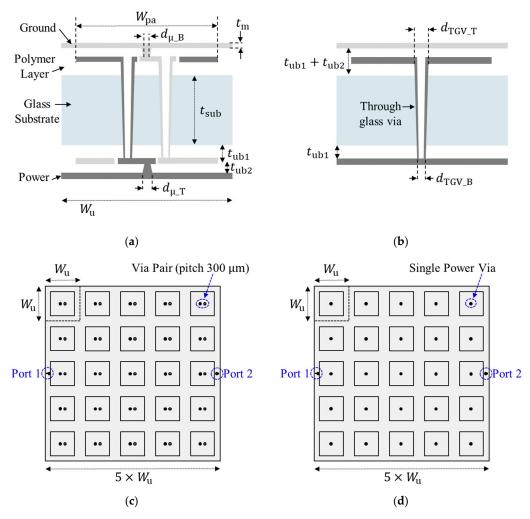

To validate the proposed dispersion analysis and noise suppression structures, two structures were designed and fabricated. In Figure 6, cross-sections/top views of the structures in the glass interposer test vehicles are shown. As shown in Figure 6a, this structure (Type A) had double patches to increase capacitance. Four metal layers (MLs) were needed to form this structure. In Figure 6b, a simpler structure (Type B) is shown, which only had one patch and three MLs were required. Because the copper used to form metal layers (MLs) does not adhere to the glass substrate directly, low-loss polymer was used between the substrate and MLs. In glass packages and interposers, using a low-loss polymer provides various advantages, such as additional mechanical strength, prevention of substrate cracking, prevention of moisture contact, and CTE control [35]. In each test vehicle, 25 (5 in x-direction and 5 in y-direction) unit structures, shown in Figure 6, were embedded in the PDN. The top view of the test vehicle with 25 Type A unit structures is shown in Figure 6c. Similarly, the top view of the test vehicle with 25 Type B unit structures is shown in Figure 6d. In Table 2, the physical dimensions and material properties of the test vehicles are summarized. More detailed process design rules and explanations of the structures have been described in previous works [36,37].

**Figure 6.** Designed noise suppression structures in the glass interposer test vehicles. (a) Type A: double-patch structure; (b) Type B: single-patch structure. Top view of the fabricated test vehicles composed with (c) Type A and (d) Type B. Each test vehicle has 25 unit structures.

|                     | Symbol                  | Type A           | Туре В             |  |

|---------------------|-------------------------|------------------|--------------------|--|

|                     | t <sub>sub</sub>        | 100              | μm                 |  |

|                     | t <sub>bu1</sub>        | 15 μm            | 17.5 μm            |  |

|                     | $t_{\rm bu2}$           | 15 µm            | 35 µm              |  |

|                     | $t_{\rm m}$             | 3~5 μm           | 4~10 μm            |  |

|                     | d <sub>TGV T</sub>      | 60 µm            | 100 µm             |  |

| Physical            | $d_{\rm TGV_B}$         | 40 µm            | 60 µm              |  |

| Dimensions          | $d\mu_{\rm T}$          | 35 µm            | 45 µm              |  |

|                     | $d\mu_{\rm B}$          | 30 µm            | 45 µm              |  |

|                     | $\overline{W_{u}}$      | 3.2 mm           |                    |  |

|                     | $W_{pa}$                | 2.2 mm           |                    |  |

|                     | <i>p</i> <sub>TGV</sub> | 300 µm           | NA                 |  |

|                     | € <sub>r,sub</sub>      | 5.3 @ 2.4 GHz    | 5.3 @ 2.4 GHz      |  |

|                     | <sup>ε</sup> r.bu       | 3.2 @ 5.8 GHz    | 3@10GHz            |  |

| Material Properties | $tan \delta_{sub}$      | 0.004 @ 2.4 GHz  | 0.004 @ 2.4 GHz    |  |

| 1                   | tan $\delta_{bu}$       | 0.0042 @ 5.8 GHz | 0.005 @ 10 GHz     |  |

|                     | $\sigma_{ m m}$         | 5.8 	imes 1      | 0 <sup>7</sup> σ/m |  |

Table 2. Physical dimensions and material properties of the glass interposer test vehicles.

Each structure has different lumped capacitance (*C*) and inductance (*L*). First, the structure of Type A was analyzed to derive lumped *C* and *L*. The lumped capacitance ( $C_A$ ) can be

derived by adding capacitance between patches and planes ( $C_{pa}$ ) and capacitance between the power/ground through-glass via (TGV) pair ( $C_{TGV}$ ) [38]. They can be summarized as follows:

$$C_{\rm A} = C_{\rm pa} + C_{\rm TGV} \tag{11}$$

$$C_{\rm pa} = \frac{\varepsilon_0 \varepsilon_{\rm r,bu} \left( 2 \left( W_{\rm pa} \right)^2 - \pi \left( d_{\rm TGV\_T} / 2 \right)^2 - \pi \left( d_{\rm TGV\_B} / 2 \right)^2 \right)}{t_{\rm bu2} - t_{\rm m}}$$

(12)

$C_{\text{TGV}} = \int_{z=0}^{t_{\text{bul}}} \frac{\pi \varepsilon_{\text{r,bu}}}{\cos h^{-1} (p_{\text{TGV}}/2r(z))} dz + \int_{z=t_{\text{bul}}}^{t_{\text{bul}}+t_{\text{sub}}} \frac{\pi \varepsilon_{\text{r,sub}}}{\cos h^{-1} (p_{\text{TGV}}/2r(z))} dz + \int_{z=t_{\text{bul}}+t_{\text{sub}}}^{2t_{\text{bul}}+t_{\text{sub}}} \frac{\pi \varepsilon_{\text{r,bu}}}{\cos h^{-1} (p_{\text{TGV}}/2r(z))} dz$ (13)

where

$$r(z) = \frac{d_{\text{TGV}\_B}}{2} + \frac{d_{\text{TGV}\_A} - d_{\text{TGV}\_B}}{2(2t_{\text{ub1}} + t_{\text{sub}})}z$$

(14)

The lumped inductance  $(L_A)$  can be modeled as follows:

$$L_{\rm A} = L_{\rm TGV} + 2L_{\mu \rm via} \tag{15}$$

$$L_{\text{TGV}} = \int_{z=0}^{2t_{\text{bul}}+t_{\text{sub}}} \frac{\mu_0}{\pi} \cos h^{-1} (p_{\text{TGV}}/2r(z)) \, dz \tag{16}$$

$$L_{\mu\nu ia} = \frac{\mu_0(t_{bu2} - t_m)}{4\pi} \left[ \ln\left(\frac{4 W_u^2}{\pi d_{\mu\nu ia}^2}\right) + \frac{\pi d_{\mu\nu ia}^2}{4 W_u^2} - 1 \right]$$

(17)

Equation (16) has a close relationship with (13), which dominates  $L_A$ . Derivation of (16) is shown in [38]. Because microvia is not paired, the derivation of (17) is a bit different from (16).  $L_{\mu\nu ia}$  can be derived from the magnetic energy in the unit structure, which is known as  $U_m = \frac{1}{2} \int \mathbf{B} \cdot \mathbf{H} \, dv$ . By adopting boundary condition  $U_m = \frac{1}{2} I^2 L$ , it is possible to derive (17) [24,39]. This relationship can be used to derive the inductance of the single TGV in the Type B structure. Because microvia is relatively shorter than the TGV pair,  $d\mu_T$  and  $d\mu_B$  was averaged to derive  $d_{\mu\nu ia}$  in (17).

The Type B structure shown in Figure 6b is simple compared to Figure 6a. The lumped capacitance ( $C_B$ ) can be expressed as follows:

$$C_{\rm B} = \frac{\varepsilon_0 \varepsilon_{\rm r,bu} \left( 2 \left( W_{\rm pa} \right)^2 - \pi \left( d_{\rm TGV_T} / 2 \right)^2 \right)}{t_{\rm bu2} - t_{\rm m}}$$

(18)

The inductance of the single TGV can be obtained by modifying (17). It can be summarized as follows:

$$L_{\rm B} = L_{\rm sin\,gle-TGV} = \int_{z=0}^{t_{\rm bu1}+t_{\rm sub}} \left[ \ln\left(\frac{W_{\rm u}^{\ 2}}{dS(z)}\right) + \frac{dS(z)}{W_{\rm u}^{\ 2}} - 1 \right] dz \tag{19}$$

where

$$dS(z) = \pi \left(\frac{d_{\text{TGV}\_B}}{2} + \frac{d_{\text{TGV}\_A} - d_{\text{TGV}\_B}}{2(2t_{\text{ub1}} + t_{\text{sub}})}z\right)^2.$$

(20)

Basically, the derivation process of (17) and (19) is identical because they are both single via confined in the unit cell. Therefore, the two equations are similar. In (19) and (20), the tapered structure of the TGV is reflected. If the length of the TGV is very short and it is not tapered, the integral calculation in (19) can be simplified as in (17). The derived parameters can be inserted into the proposed dispersion analysis explained in the previous section to analyze the noise suppression band.

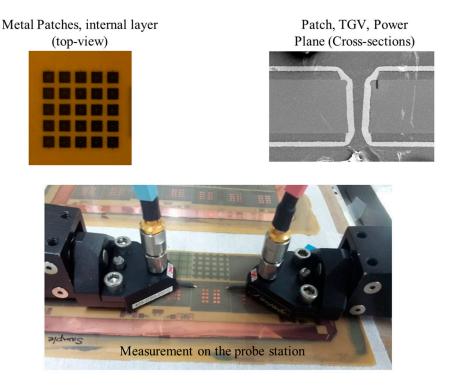

In Figure 7, fabricated glass interposer test vehicles are shown. Metal patches generating *C*, through-glass via (TGV), and planes are shown. Optical microscope and scanning electron microscope (SEM) were used to take images of various structures inside the glass interposer test vehicles. As can be seen from Figure 7, measurements were conducted on the probe station. Various measurements were conducted in both frequency and time domains. After verifying the effectiveness of the dispersion analysis, more structures were designed, as outlined in Section 4.

Figure 7. Measurement of fabricated glass interposer test vehicles.

#### 3.2. Verification by Measurement and EM Simulation

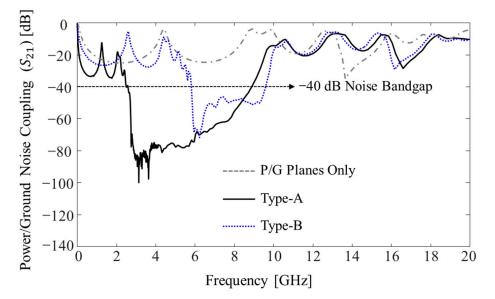

Measured power/ground noise couplings ( $S_{21}$ ) are plotted and compared in Figure 8. Two microprobes (Picoprobe GS type with 250 µm pitch, GGB industries Inc., Naples, FL, USA), two coaxial cables (W.L. Gore & Associates, Inc., Newark, DE, USA), and a calibration kit (CS-14, GGB industries Inc., Naples, FL, USA) were used to measure power/ground noise couplings. A vector network analyzer (VNA) (N5230A, Keysight, Santa Rosa, CA, USA) was used to measure the couplings in the PDN and validate the noise suppression band in the frequency domain up to 20 GHz. As a reference, a PDN without noise suppression structures was also measured. The distance between the two measurement ports (port 1 and port 2 shown in Figure 6c,d) was approximately 15.5 mm ( $\approx 5 \times W_u$ ). In such cases, it is difficult to suppress the generated noise in the PDN due to low-loss substrate and polymer build-up layer. By adopting the proposed structures (Types A and B), -40 dB noise suppression bands were generated. In these frequency bands, the power/ground noise will be significantly attenuated and isolated.

Due to the double patches and paired through vias, the Type A structure had much larger lumped capacitance (*C*) than the Type B structure. The total lumped inductance (*L*) of the Type A structure was 130.80 pH, whereas it was 89.65 pH for the Type B structure. As can be seen from (8), the Type A structure had a lower  $f_L$  compared to Type B due to larger capacitance. With larger *C*, the noise suppression band can be expanded by lowering  $f_L$ . However, the Type A structure had larger *L* compared to the Type B structure, which also lowered  $f_H$ . To achieve wider noise suppression band, higher  $f_H$  is desired. In the following section, the impacts of various design parameters and material properties on the noise suppression band is analyzed. A design direction to achieve wider noise suppression band is also given.

Figure 8. Comparison of the measured power/ground noise couplings (S<sub>21</sub>) in the PDN.

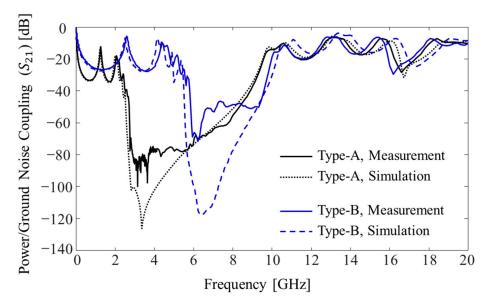

In Figure 9, the measurement results are compared with simulated results. Using the 3-D EM simulator Ansys high-frequency structure simulator (HFSS) (version 2020 R2), noise coupling ( $S_{21}$ ) of each structure was estimated and compared. The measurement and simulation results showed good agreement up to 20 GHz in the frequency domain for both structures. To verify the proposed dispersion analysis, estimated stopband edges ( $f_L$  and  $f_U$ ) were compared with the simulated and measured edges. In Table 3, edges obtained by different methods are summarized and compared. The estimated edges showed good correlation with the simulated and measured edges. The accuracy of the proposed dispersion analysis for stopband edge estimation was verified. When fabricating the glass interposer test vehicles, the diameter of the TGV showed process variations associated with substrate drilling and copper plating. If the process becomes more mature, more accurate results are expected.

Figure 9. Measured power/ground noise couplings are compared with simulated results.

| Structures | Edges       | Measurement | Simulation<br>(Error) | Estimation<br>(Error) |

|------------|-------------|-------------|-----------------------|-----------------------|

| Type A     | $f_{\rm L}$ | 2.51 GHz    | 2.49 GHz<br>(1.00%)   | 2.51 GHz<br>(0.04%)   |

|            | $f_{\rm U}$ | 8.91 GHz    | 8.75 GHz<br>(1.83%)   | 8.59 GHz<br>(3.61%)   |

| Туре В     | $f_{\rm L}$ | 5.82 GHz    | 5.50 GHz<br>(5.49%)   | 5.87 GHz<br>(0.86%)   |

|            | $f_{\rm U}$ | 9.66 GHz    | 9.75 GHz<br>(0.93%)   | 10.4 GHz<br>(7.66%)   |

Table 3. Summary and comparison of measured, simulated, and estimated stopband edges.

Compared to 3-D EM simulation, the proposed method required less time and computational resources to estimate the stopband edges. When designing the structure, the proposed dispersion analysis could effectively estimate the stopband considering the design rules and target noise band. After preliminary analysis, the structure could be designed in the 3-D EM simulator for further analysis and validation before tape-out.

#### 4. Design and Analysis of Noise Suppression Structures with Various Low-Loss Materials

In this section, design directions are discussed based on the proposed dispersion analysis. The impacts of various design parameters and material properties are considered. Some candidates are chosen, and noise stopbands are estimated. Additional measurements and 3-D EM simulations are conducted to verify the impacts of the proposed structures on power/ground noise suppression and decoupling.

#### 4.1. Noise Suppression Band Formulation with Various Materials

In general, broadband noise suppression is desired to cover various applications. To achieve broadband, the lower stopband edge ( $f_L$ ) should be designed toward lower frequency. At the same time, the upper stopband edge ( $f_U$ ) should be formed at higher frequency. Design parameters and material have significant impacts, but not all of them can be realized and adopted. It can be limited by process design rules or have a conflict with usages of advanced packages and interposers. In Table 4, the stopband expansion method by changing design parameters and impacts is summarized.

| Band Expansion         | <b>Design Parameters</b>                           | Impacts           | Note                   |

|------------------------|----------------------------------------------------|-------------------|------------------------|

|                        | High-K materials in BU                             | $C\uparrow$       |                        |

|                        | Thin BU materials                                  | $C\uparrow$       |                        |

| $f_{\rm L}\downarrow$  | Larger pactes $(W_{pa})$                           | $C\uparrow$       | Limited                |

|                        | Increase package/interposer a $(t_{PDN}\uparrow)$  | and PDN thickness | Not desired            |

|                        | Add defects in P/G planes $L\uparrow$              |                   | Limited                |

|                        | Through via diameter ↓                             | $L\uparrow$       | Limited & $1/\sqrt{L}$ |

|                        | Through via diameter ↑                             | $L\downarrow$     | 1/L                    |

| $f_{\rm U}$ $\uparrow$ | Via arrays or parallel vias                        | $L\downarrow$     | 1/L                    |

| -                      | $Z_{0,\text{PDN}}\uparrow(t_{\text{PDN}}\uparrow)$ | RSH of (10) ↑     | Not desired            |

Table 4. Stopband expansion method by changing design parameters and impacts.

By analyzing the proposed dispersion equations, the impacts of design parameters can be easily determined. As can be seen from (8), increasing lumped capacitance (*C*), inductance (*L*), and PDN thickness will lower  $f_L$ . Adopting build-up materials with high permittivity can increase *C*. At the same time, selecting thinner build-up materials will have the same impact. However, using larger structures can increase the overall *x*–*y* dimensions of the packages/interposers. The *x*–*y* dimensions directly affect the overall fabrication yield, so this design direction is not desired. Moreover, a design direction that increases

the PDN thickness should be avoided. Adding defects in power/ground planes increases L [31]. In terms of power integrity, this can be a good solution. However, adding defects can cause return current discontinuity issues. If such a design is adopted, routings, fan-out, and signal integrity analysis should be carefully conducted as well.

The diameter of the through-substrate via affects both stopband edges, so it is highlighted in Table 4. When the diameter is altered, RHS of (10) is affected more dramatically, which is inversely proportional to L, whereas (8) is inversely proportional to  $\sqrt{L}$ . Moreover, the diameter of the through substrate is heavily determined by the process design rule. It is difficult to freely modify the diameter when designing packages/interposers. It is more realistic to adopt parallel through via scheme than changing the diameter to achieve lower L. A design that can achieve higher characteristic impedance ( $Z_{0,PDN}$ ) shifts RSH of (10) and can formulate  $f_U$  at higher frequency. However, compared to other parameters, changing  $Z_{0,PDN}$  is not easy as it will have multiple impacts. The easiest method is increasing the PDN thickness, but this direction is not desired in advanced packages/interposers.

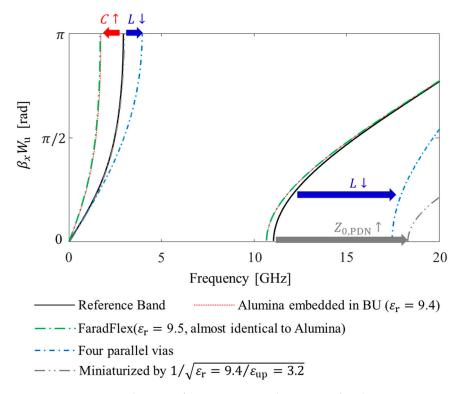

In Figure 10, dispersion diagrams with design parameters and material properties are plotted for comparison. For fare comparison, the normalized value in radian ( $\beta_x W_u$ ) is plotted instead of the propagation constant ( $\beta_x$ ). Fundamental bandgaps are formed in the bands where  $\beta_x W_u$  does not exist. High-*K* material alumina can be embedded in polymer build-up layers of glass packages and interposers to increase *C* [40]. Moreover, ultrathin and high-*K* materials, such as FaradFlex substrate, can be embedded in the build-up layers of packages [18]. These materials can also be used for miniaturization of structures instead of increasing *C*. By adopting parallel trough via arrays, the suppression band is expanded toward higher frequency.

**Figure 10.** Dispersion diagrams for comparison. The impact of each parameter on stopband edge is also marked.

In the following subsection, additional results obtained by measurement and 3-D EM/circuit simulations are provided. The impacts of noise suppression/isolation are graphically delivered in the time domain.

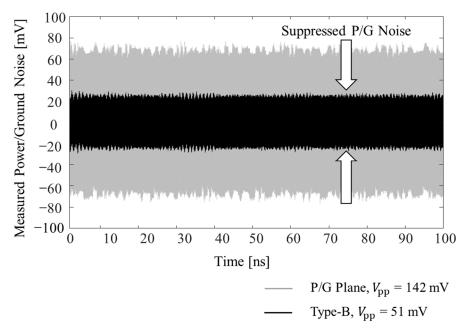

#### 4.2. Impacts of Power/Ground Noise Decoupling Using the Proposed Structures

In Figure 11, measured power/ground noise coupling results are plotted and compared in the time domain. A pulse-pattern generator (PPG) (Anritsu MP-1763C, Atsugi, Japan) and a digital sampling oscilloscope (Tektronix TDS800B, Beaverton, OR, USA) were used to conduct measurements in the time domain. The Type B structure explained in Section 3 was used for the experiment. Twelve gigabits per second (GB/s) clock signal (0 to 1 V, 30 ps rise-and-fall time and all ports terminated with 50 ohm) was injected to the interposer PDN (port 1 in Figure 6d) as a noise source. Frequency band of the injected noise existed in the suppression band of the Type B structure. From the noise source to the measurement location in the PDN (port 2 in Figure 6d), five unit structures existed, and the distance was approximately 15.5 mm. Without the noise suppression structure, 142 mV peak-to-peak voltage ( $V_{pp}$ ) was measured, which corresponded to 14.2% of the input voltage. When the proposed noise suppression structure was fabricated in the PDN, 51 mV  $V_{pp}$  was observed. Significant noise suppression/isolation was achieved by adopting the proposed structure.

**Figure 11.** Comparison of the measured power/ground noise coupling results in the time domain without and with the noise suppression structure (Type B). By adopting the proposed structure, power/ground noise was significantly suppressed in the interposer with low-loss substrate.

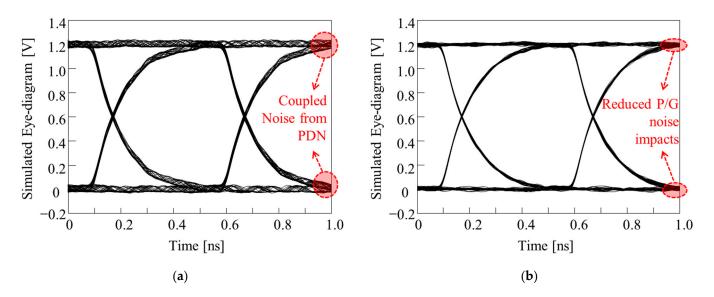

Additional 3-D EM/circuit simulations were conducted to verify the effectiveness of the proposed structure. In this study, eye diagrams of the through-substrate (glass or FaradFlex) via channel under the influence of power/ground noise coupling were simulated and compared. The through-substrate via channel (victim) was designed to penetrate the PDN, and the noise source was located far away from the victim. In this scenario, the noise induced in the PDN propagates without attenuation, couples to the victim channel, and degrades SI of the victim channel (PDN-induced crosstalk). This scenario is likely to happen as there are thousands of signal through-substrate vias escaping packages or interposers, such as SerDes. Pseudo-random binary sequence (PRBS) of  $2^8 - 1$ , 0 V to 1.2 V, with rise-and-fall time of 30 ps and data rate (DR) of 2 GB/s was injected to the victim channel. The total length of the victim channel was designed to be approximately 14 mm, including the through via, microvia, interposer channel, and PCB channel located under the package. At the receiving location of the victim channel where eye diagrams were monitored, a capacitive termination was applied. This simulation scenario was graphically depicted in Figure 12.

**Figure 12.** Graphical depiction of the simulation scenario. Aggressor channel escaping the package or interposer induces noise in the PDN. The noise propagates and couples to the victim channel. Eye diagrams of the victim channel are compared without and with noise suppression structures.

In Figure 13, eye diagrams of the victim channel are plotted and compared without and with the proposed structure. In Figure 13, the Type B structure is used as a representative. In Table 5, additional results are also summarized for other structures, and eye-opening voltage, jitter, and maximum  $V_{pp}$  noise at logics zero/one are compared. For all three cases, eye diagrams of the through-substrate via channel were improved by adopting the proposed structures. Low-loss substrates for packages and interposers provide various advantages. However, power/ground noise must be isolated and suppressed. In this study, noise suppression was conducted by designing various structures in the PDN. The structures were analyzed and determined by the proposed dispersion analysis. Compared to full 3-D EM simulations, the proposed dispersion analysis is fast and requires smaller computational resources. Therefore, the proposed dispersion analysis is useful at the preliminary PDN design stage.

**Figure 13.** Verifications of the impacts of the proposed structure by eye diagram simulations. By adopting the proposed structure, power/ground noise coupling from the PDN to through-substrate via channel was suppressed. (**a**) P/G planes only. (**b**) embedded Type B structure.

| Structures                  | Eye-Opening<br>Voltage                        | Jitter (% of UI)                                        | P/G Noise at 0 or 1                       |

|-----------------------------|-----------------------------------------------|---------------------------------------------------------|-------------------------------------------|

| Type A                      | $784 \text{ mV} \rightarrow 838 \text{ mV}$   | $36.5 \text{ ps}(7.1) \rightarrow 22.2 \text{ ps}(4.4)$ | $60 \text{ mV} \rightarrow 19 \text{ mV}$ |

| Type B (Figure 13)          | $1.08 \text{ V} \rightarrow 1.15 \text{ V}$   | $18 \text{ ps} (3.6) \rightarrow 7 \text{ ps} (1.4)$    | $62 \text{ mV} \rightarrow 36 \text{ mV}$ |

| FaradFlex based (Figure 10) | $1.05~\mathrm{V} \rightarrow 1.11~\mathrm{V}$ | 21 ps (4.2) $\rightarrow$ 13 ps (2.6)                   | $70 \text{ mV} \rightarrow 39 \text{ mV}$ |

Table 5. Summary of the eye diagram improvement by adopting the proposed structures.

### 5. Conclusions

In this study, dispersion analysis was proposed to efficiently design power/ground noise suppression structures for packages and interposers with low-loss substrates. The mechanism of noise suppression/isolation was thoroughly explained based on the proposed dispersion analysis. By conducting the proposed dispersion analysis, the impacts on physical design parameters and material properties on the suppression band could be easily explained. To validate the proposed dispersion analysis, noise suppression structures were designed and fabricated in the glass interposer PDN and measured. It was verified that  $f_L$  and  $f_U$  estimated based on the proposed analysis method showed good agreement with those acquired from experiments and simulations. Compared to EM simulation, the proposed method required smaller computational resources but showed good accuracy. Various structures were designed and analyzed based on the proposed dispersion analysis. The effectiveness of the proposed structures was further validated by additional experiments and simulations in the time domain. The proposed structures suppressed power/ground noise propagation and coupling.

Low-loss substrates for packages and interposers provide various advantages, especially for high-speed signaling. However, power/ground noise must be isolated and suppressed. To solve issues, this article proposed an efficient dispersion analysis method, fabricated the noise suppression structures, and applied the structures. The proposed structures have minimal impacts on the channel routing, fan-out, and return current path. However, the structures proposed in this article require additional metal layers. These designs increase the fabrication cost. Even though they provide promising solutions toward power/ground noise issues with minimal impacts on channel properties and designs, more cost-effective designs are desired in the near future. Because the proposed dispersion analysis can be expanded to various designs, such as defects in the plane, development of a new structure based on the proposed method without increasing the number of metal layer remains the subject of work for the near future.

**Funding:** This work was supported in part by JSPS KAKENHI Grant Number 20K14719 and in part by JSPS KAKENHI Grant Number 22K14241. In addition, this work was supported in part by the MKE through the International Collaborative Research and Development Program "Glass interposer based RF FEM for Next Generation Mobile Smart Phone" under Grant N0000899.

Conflicts of Interest: The author declares no conflict of interest.

### References

- Pak, J.; Ryu, C.; Kim, J. Electrical Characterization of Trough Silicon Via (TSV) depending on Structural and Material Parameters based on 3D Full Wave Simulation. In Proceedings of the 2007 IEEE International Conference on Electronic Material and Packaging, Daejeon, Korea, 19–22 November 2007; pp. 1–6.

- Tummala, R.; Sundaram, S.; Chatterjee, R.; Raj, P.M.; Kumbhat, N.; Sukumaran, V.; Sridharan, V.; Choudury, A.; Chen, Q.; Bandyopadhyay, T. Trend from ICs to 3D ICs to 3D systems. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 13–16 September 2009; pp. 439–444.

- Swaminathan, M.; Han, K. Design and Modeling for 3D ICs and Interposers; World Scientific Publishing Co. Pte. Ltd.: Singapore, 2014; ISBN 978-981-4508-59-9.

- Technology Roadmap of DRAM for Three Major Manufacturers: Samsung, SK-Hynix and Micron. Available online: https://docplayer.net/29965569-Technology-roadmap-of-dram-for-three-major-manufacturers-samsung-sk-hynix-andmicron-may-2013.html (accessed on 30 May 2013).

- 5. Lim, S. Design for High Performance, and Reliable 3D Integrated Circuits; Springer: Berlin/Heidelberg, Germany, 2013. [CrossRef]

- 6. Standard JESD235A; High Bandwidth Memory (HBM) DRAM. JEDEC: Arlington, VA, USA, 2015.

- Cho, K.; Kim, Y.; Lee, H.; Kim, H.; Choi, S.; Song, J.; Kim, S.; Park, J.; Lee, S.; Kim, J. Signal Integrity Design and Analysis of Silicon Interposer for GPU-Memory Channels in High-Bandwidth Memory Interface. *IEEE Trans. Compon. Packag. Manuf. Technol.* 2018, *8*, 1658–1671. [CrossRef]

- 8. Kim, H.; Lee, H.; Cho, J.; Kim, Y.; Kim, J. Electrical Design of silicon, glass and organic interposer channels. In Proceedings of the 2014 Pan Pacific Microelectronics Symposium, Kauai, HI, USA, 3 February 2014.

- 9. Sukumaran, V.; Bandyopadhyay, T.; Sundaram, V.; Tummala, R. Low-cost thin glass interposers as a superior alternative to silicon and organic interposers for packaging of 3-D ICs. *IEEE Trans. Compon. Packag. Manuf.* 2012, 2, 1426–1433. [CrossRef]

- Hu, D.C.; Hung, Y.; Chen, T.; Tain, R.; Lo, W. Embedded glass interposer for heterogeneous multi-chip integration. In Proceedings of the IEEE Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015; pp. 314–317.

- Lu, H.; Furuya, R.; Sawyer, B.M.; Nair, C.; Liu, F.; Sundaram, V.; Tummala, R.R. Design, modeling, fabrication and characterization of 2-5 μm redistribution layer traces by advanced semi-additive processes on low-cost panel based glass interposers. *IEEE Trans. Compon. Packag. Manuf.* 2016, 6, 959–967. [CrossRef]

- Park, G.; Cho, K.; Son, K.; Park, H.; Lho, D.; Kim, S.; Shin, T.; Kim, Y.; Kim, J.; Watanabe, A.; et al. Design and Measurement of a 28 GHz Glass Band Pass Filter based on Glass Interposers for 5G Applications. In Proceedings of the 2019 IEEE Electrical Design of Advanced Packaging and Systems Symposium, Kaohsiung, Taiwan, 16–18 December 2019.

- Laakso, M.J.; Bleiker, S.J.; Liljeholm, J.; Martensson, G.E.; Asiatici, M.; Fischer, A.C.; Stemme, G.; Ebefors, T.; Niklaus, F. Through-Glass Vias for Glass Interposers and MEMS Packaging Applications Fabricated Using Magnetic Assembly of Microscale Metal Wires. *IEEE Access.* 2018, *6*, 44306–44317. [CrossRef]

- Tschoban, C.; Rossi, M.; Reyes, J.; Ndip, I.; Lang, K. Development of a Glass Technology Based 79 GHz MIMO Radar Front-End Module for Autonomous Driving. In Proceedings of the 2019 IEEE 21st Electronics Packaging Technology Conference, Singapore, 4–6 December 2019; pp. 376–381.

- Chang, Y.-H.; Chen, J.-C.; Chung, W.; Li, W.-Y.; Shih, P.-T.B.; Ng'Oma, A.; Yang, C.; Huang, M.-C.; Lin, H.-Y.; Wang, C.-H.; et al. A Novel Fabrication Process and Measurement Results of a 28 GHz Glass Antenna with Single TGV for 5G Communication Applications. In Proceedings of the 2019 14th International Microsystems, Packaging, Assembly and Circuits Technology Conference, Taipei, Taiwan, 23–25 October 2019; pp. 112–115.

- Hwangbo, S.; Yoon, Y.; Shorey, A. Glass Interposer Integrated Dual-band Millimeter Wave TGV Antenna for Inter-/Intra Chip and Board Communications. In Proceedings of the 2016 IEEE International Symposium on Antennas and Propagation, Fajardo, Puerto Rico, 26 June–1 July2016; pp. 1639–1640.

- Kim., Y.; Kim, Y.; Cho, K.; Park, G.; Kim, S.; Kang, K.; So, K.; Jeon, J.; Kim, C.; Paik, W. Power and Signal Integrity Analysis of Fan-out Wafer Level Package for Mobile Application Processor. In Proceedings of the DesignCon 2017, Santa Clara, CA, USA, 30 January 2017.

- 18. FaradFlex for PCBs. Available online: https://www.faradflex.com/pcbs/ (accessed on 1 April 2022).

- Kitazawa, T.; Hayashi, Y.; Fukawa, Y.; Kim, Y. Analysis of the PDN Induced Crosstalk Impacts on the High-speed Signaling in Ultra-thin and High Permittivity Substrates. In Proceedings of the EMC Europe 2022, Gothenburg, Sweden, 5–8 September 2022.

- Kim, Y.; Kim, K.; Cho, J.; Kim, J.; Sundaram, V.; Tummala, R. Analysis of Power Distribution Network in Glass, Silicon Interposer and PCB. In Proceedings of the 2014 IEEE International Symposium on Electromagnetic Compatibility, Raleigh, NC, USA, 5 August 2014.

- 21. Hashimoto, M.; Nair, R. Power Integrity for Nanoscale Integrated Systems; McGraw-Hill Education: New York, NY, USA, 2014; ISBN 978-0-07-178776-5.

- Kim, Y.; Wada, S.; Fujimoto, D.; Hayashi, Y. Analysis of Electromagnetic Information Leakage from Overdesigned Power Delivery Network of Cryptographic Devices. In Proceedings of the 2021 Asia Pacific International Symposium on Electromagnetic Compatibility, Hybrid (Bali & On-line), 28 September 2021.

- Wada, S.; Hayashi, Y.; Fujimoto, D.; Homma, N.; Kim, Y. Measurement and Analysis of Electromagnetic Information Leakage from Printed Circuit Board Power Delivery Network of Cryptographic Devices. *IEEE Trans. Electromagn. Compat.* 2021, 63, 1322–1332. [CrossRef]

- Rogers, S.D. Electromagnetic-bandgap Layers for Broad-band Suppression of TEM modes in Power Planes. *IEEE Trans. Microw. Theory Tech.* 2005, 53, 2495–2505. [CrossRef]

- Toyota, Y.; Engin, A.; Kim, T.; Swaminathan, M. Stopband Analysis Using Dispersion Diagram for Two-Dimensional Electromagnetic Bandgap Structures in Printed Circuit Boards. *IEEE Microw. Wirel. Compon. Lett.* 2006, 16, 645–647. [CrossRef]

- 26. Kim, L.; Schutt-Aine, J. Analysis and Modeling of Hybrid Planar-Type Electromagnetic-Bandgap Structures and Feasibility Study on Power Distribution Network Applications. *IEEE Trans. Microw. Theory Tech.* **2008**, *56*, 178–186. [CrossRef]

- 27. Hwang, C.; Shim, Y.; Koo, K.; Kim, M.; Pak, J.; Kim, J. An On-Chip Electromagnetic Bandgap Structure using an On-Chip Inductor and a MOS Capacitor. *Microw. Wirel. Compon. Lett.* **2011**, *21*, 439–441. [CrossRef]

- 28. Wei, P.; Tsai, M.; Hsu, S.; Shen, C.; Wu, T. An Electromagnetic Bandgap Structure Integrated with RF LNA Using Integrated Fan-Out Wafer-Level Package for Gigahertz Noise Suppression. *IEEE Trans. Microw. Theory Tech.* **2018**, *66*, 5482–5490. [CrossRef]

- 29. Das, R.; Yoo, H. Application of a Compact Electromagnetic Bandgap Array in a Phone Case for Suppression of Mobile Phone Radiation Exposure. *IEEE Trans. Microw. Theory Tech.* **2018**, *66*, 2363–2372. [CrossRef]

- Zhu, H.; Wang, J.; Sun, Y.; Wu, X.; Mao, J. A Novel Automatically Designed EBG Structure by Improved GA for Ultrawideband SSN Mitigation of System in Package. *IEEE Trans. Compon. Packag. Manuf. Technol.* 2020, 10, 123–133. [CrossRef]

- Kim, M.; Koo, K.; Hwang, C.; Shim, Y.; Kim, J.; Kim, J. A Compact and Wideband Electromagnetic Bandgap Structure Using a Defected Ground Structure for Power/Ground Noise Suppression in Multilayer Packages and PCBs. *IEEE Trans. Electromagn. Compat.* 2012, 54, 689–695.

- Kim, K.; Hwang, C.; Koo, K.; Cho, J.; Kim, H.; Kim, J.; Lee, J.; Lee, H.; Park, K.; Pak, J. Modeling and Analysis of a Power Distribution Network in 3-D Memory IC Including P/G TSVs, On-chip Decoupling Capacitors, and Silicon Substrate Effects. *IEEE Trans. Compon. Packag. Manuf. Technol.* 2012, 2, 2057–2070. [CrossRef]

- Kim, K.; Yook, J.; Kim, J.; Kim, H.; Lee, J.; Park, K.; Kim, J. Interposer Power Distribution Network Modeling Using a Segmentation Method for 3-D ICs with TSVs. *IEEE Trans. Compon. Packag. Manuf. Technol.* 2013, *3*, 1891–1906. [CrossRef]

- 34. Tuncer, E.; Serdyuk, Y.V.; Gubanski, S.M. Dielectric mixtures: Electrical properties and modeling. *IEEE Trans. Dielectric. Electr. Insul.* **2002**, *9*, 809–828. [CrossRef]

- McCann, S.R.; Sato, Y.; Sundaram, V.; Tummala, R.; Sitaraman, K. Prevention of Cracking from RDL Stress and Dicing Defects in Glass Substrates. *IEEE Trans. Device Mater. Reliab.* 2016, 16, 43–49. [CrossRef]

- Kim, Y.; Cho, J.; Kim, J.J.; Kim, K.; Cho, K.; Kim, S.; Sitaraman, S.; Sundaram, V.; Raj, P.M.; Tummala, R.; et al. Measurement and Analysis of Glass Interposer Power Distribution Network Resonance Effects on a High-Speed Through Glass Via Channel. *IEEE Trans. Electromagn. Compat.* 2016, 58, 1747–1759. [CrossRef]

- Kim, Y.; Park, G.; Cho, K.; Raj, P.M.; Tummala, R.R.; Kim, J. Wideband Power/Ground Noise Suppression in Low-Loss Glass Interposers Using a Double-Sided Electromagnetic Bandgap Structure. *IEEE Trans. Microw. Theory Tech.* 2020, 68, 5055–5064. [CrossRef]

- 38. Pozar, D. Microwave Engineering, 3rd ed.; John Wiley and Sons: Hoboken, NJ, USA, 2005.

- Clavijo, S. Design Methodology for Sievenpiper High-impedance Surfaces. M.S. Thesis, Department of Electrical Engineering, Arizona State University, Tempe, AZ, USA, 2002.

- 2.5D Interposer for High Bandwidth: Design, Fabrication and Characterization. Available online: http://www.prc.gatech.edu/ sites/default/files/documents/iab\_spring2016/Presentations/Wednesday%20Presentations/09%20IAB\_May\_2016-DDTV\_2. 5DGIP%20Brett%20Sawyer.pdf (accessed on 1 December 2016).