### Błażej Nowacki

Mestre

### Design of Sigma-Delta Modulators for Analog-to-Digital Conversion Intensively Using Passive Circuits

Dissertação para obtenção do Grau de Doutor em Engenharia Electrotécnica e de Computadores

- Orientador: Nuno Filipe Silva Veríssimo Paulino, Prof. Auxiliar, Universidade Nova de Lisboa

- Co-orientador: João Carlos da Palma Goes, Prof. Associado com Agregação, Universidade Nova de Lisboa

Júri:

| Presidente: | Prof. Luís Camarinha-Matos                                                        |

|-------------|-----------------------------------------------------------------------------------|

| Arguentes:  | Prof. José M. de la Rosa<br>Prof. Jorge Manuel Correia Guilherme                  |

| Vogais:     | Prof. Luís Camarinha-Matos<br>Prof. João Pedro Oliveira<br>Dr. Michael Figueiredo |

Maio, 2016

# Design of sigma-delta modulators for analog-to-digital conversion intensively using passive circuits.

Copyright © Błażej Nowacki, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

### ACKNOWLEDGMENTS

First and foremost, I strongly acknowledge my supervisor Prof. Nuno Paulino and my cosupervisor Prof. João Goes.

I am sincerely and deeply grateful to Prof. Nuno Paulino for his support, availability, encouragement and motivation. More than a supervisor, he has also been a friend. Without his help, the work I present in this thesis would not have been developed.

I would like to state my appreciation and gratitude to Prof. João Goes for welcoming me first as a researcher and then as a Ph.D. student, for always having an open door for me, for all the help, support and useful remarks.

I also would like to acknowledge my gratitude to Prof. Rui Tavares, Prof. Luis Oliveira and Prof. João Oliveira for all the support and technical help.

I would like to thank to the members of my Thesis Accompanying Committee, Prof. João Pedro Oliveira, Prof Jorge Manuel Correia Guilherme, Prof. Nuno Paulino and Prof. João Goes for taking all their time and attention in the analysis of the working plan of my thesis.

I would like to thank to my fellow colleagues and friends, Edinei Santin, Michael Figueiredo, João Ferreira, José Custódio, Ivan Bastos, João de Melo, Hugo Serra, Somaye Abdollahvand, Nuno Pereira, Ana Correia, Richa Arya and Miguel Fernandes for all the support.

I would like to give special and meaningful thanks to Edinei, who helped me so much during the final prototype layout design and the evaluation board design. Moreover, I would like to thank João de Melo, with whom I shared the test chip die, for providing me designs of few auxiliary blocks, for helping with the final prototype layout design and for helping during the chip evaluation task. Also, special thanks to João Ferreira and José Custódio who helped me during the layout design of the first prototype circuit.

I would like to thank for the support of the following institutions:

Fundação para a Ciência e Tecnologia that supported this work through projects (DISRUPTIVE - EXCL/EEI-ELC/0261/2012, PEST - UID-EEA/EEI/00066/2013) and a Ph.D. scholarship: SFRH / BD / 71313 / 2010.

- Department of Electrical Engineering of the FCT-UNL that provided the necessary conditions to realize the work,

- CTS-UNINOVA that provided the necessary conditions to realize the work,

Finally I thank my parents and my girlfriend, Adalgiza Fonseca, for their unconditional and persistent help, encouragement, motivation, support, patience and above all love.

### ABSTRACT

This thesis presents the analysis, design implementation and experimental evaluation of passiveactive discrete-time and continuous-time Sigma-Delta ( $\Sigma\Delta$ ) modulators ( $\Sigma\Delta$ Ms) analog-todigital converters (ADCs).

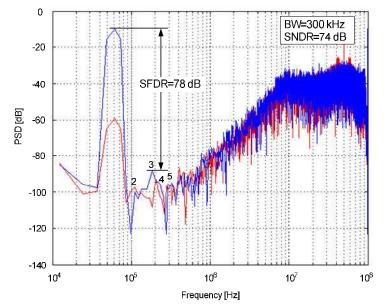

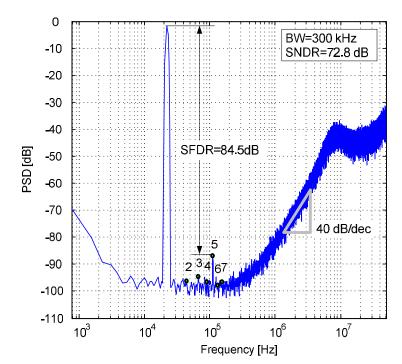

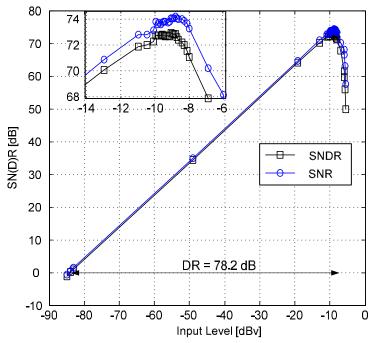

Two prototype circuits were manufactured. The first one, a discrete-time  $2^{nd}$ -order  $\Sigma\Delta M$ , was designed in a 130 nm CMOS technology. This prototype confirmed the validity of the ultra incomplete settling (UIS) concept used for implementing the passive integrators. This circuit, clocked at 100 MHz and consuming 298  $\mu$ W, achieves DR/SNR/SNDR of 78.2/73.9/72.8 dB, respectively, for a signal bandwidth of 300 kHz. This results in a Walden FoM<sub>W</sub> of 139.3 fJ/conv.-step and Schreier FoM<sub>S</sub> of 168 dB.

The final prototype circuit is a highly area and power efficient  $\Sigma\Delta M$  using a combination of a cascaded topology, a continuous-time *RC* loop filter and switched-capacitor feedback paths. The modulator requires only two low gain stages that are based on differential pairs. A systematic design methodology based on genetic algorithm, was used, which allowed decreasing the circuit's sensitivity to the circuit components' variations. This continuous-time, 2-1 MASH  $\Sigma\Delta M$  has been designed in a 65 nm CMOS technology and it occupies an area of just 0.027 mm<sup>2</sup>. Measurement results show that this modulator achieves a peak SNR/SNDR of 76/72.2 dB and DR of 77dB for an input signal bandwidth of 10 MHz, while dissipating 1.57 mW from a 1 V power supply voltage. The  $\Sigma\Delta M$  achieves a Walden FoM<sub>w</sub> of 23.6 fJ/level and a Schreier FoM<sub>s</sub> of 175 dB. The innovations proposed in this circuit result, both, in the reduction of the power consumption and of the chip size. To the best of the author's knowledge the circuit achieves the lowest Walden FOM<sub>w</sub> for  $\Sigma\Delta M$ s operating at signal bandwidth from 5 MHz to 50 MHz reported to date.

### RESUMO

Esta tese de investigação apresenta a análise, projecto e avaliação experimental de conversores analógico-digital (ADCs) usando moduladores Sigma-Delta ( $\Sigma\Delta M$ ) baseados em amplificadores de baixo ganho e utilizando tempo discreto e contínuo.

Dois circuitos protótipos foram fabricados. O primeiro, um  $\Sigma\Delta M$  em tempo discreto de segunda ordem, foi implementando numa tecnologia CMOS 130 nm. Este protótipo validou o conceito de circuitos de condensadores comutados com tempo de estabelecimento ultra incompleto (UIS) usado para realizar integradores passivos. Este circuito opera a uma frequência de 100 MHz, tem uma dissipação de potência de 298  $\mu$ W, apresenta uma DR/SNR/SNDR de 78.2/73.9/77.8 dB, respetivamente, e uma largura de banda de 300 kHz. Estes resultados apresentam uma figura de mérito medido experimentalmente de 139.3 fJ/conv.-step (Walden FoM<sub>W</sub>) e de 168 dB (Schreier FoM<sub>S</sub>).

O segundo protótipo, consiste num  $\Sigma\Delta M$  altamente eficiente em temos de área e de potência dissipada, utiliza uma combinação de topologias em cascata, através de filtros RC contínuos no tempo, necessitando apenas de dois andares de amplificação com baixo ganho implementados através de pares diferenciais. A malha de realimentação utiliza condensadores comutadores. Foi utilizada uma metodologia de projeto sistemática baseada em algoritmo genético que permite diminuir a sensibilidade do circuito face a variações nos seus components constituíntes. Este 2-1 MASH  $\Sigma \Delta M$  contínuo foi implementado numa tecnologia CMOS 65 nm e ocupa uma área de apenas 0.027 mm<sup>2</sup>. Os resultados medidos mostraram que este modulador atinge uma SNR/SNDR de 76/72.2 dB, e uma DR de 77 dB para um sinal de entrada com uma largura de banda de 10 MHz. Nesta configuração a dissipação de potência é de 1,57 mW para uma tensão de alimentação de 1 V. O ΣΔM apresenta, respectivamente, figuras de mérito de 23.6 fJ/level (Walden FoM<sub>w</sub>) e de 175 dB (Schreier FoM<sub>s</sub>). A inovação presente neste circuito resulta numa redução na potência dissipada e na área do chip. Este circuito, tanto quanto os autores têm conhecimento, apresenta a mais baixa figura de mérito de Walden para  $\Sigma\Delta Ms$  que operam com sinais cuja largura de banda esta entre os 5 MHz e os 50 MHz, reportada na literatura à date deste documento.

## TABLE OF CONTENTS

| Acknowledgm     | entsiii                                            |

|-----------------|----------------------------------------------------|

| Abstract        |                                                    |

| Resumo          | vii                                                |

| Table of Conte  | entsix                                             |

| List of Figures | xiii                                               |

| List of Tables  |                                                    |

| List of Symbol  | ls and Acronymsxix                                 |

| 1. Introducti   | on and Motivation                                  |

| 1.1. Cont       | ributions                                          |

| 1.2. Thes       | is Layout                                          |

| 2. Basics of    | Sigma-Delta Modulators                             |

| 2.1. Princ      | ciples of Sigma-Delta Modulation7                  |

| 2.2. Perfe      | ormance Metrics                                    |

| 2.3. Basi       | c Architectures of $\Sigma\Delta Ms$               |

| 2.3.1.          | Low-Pass Single-Loop ΣΔM13                         |

| 2.3.2.          | Discrete-Time and Continuous-Time $\Sigma\Delta M$ |

| 2.3.3.          | Single-bit and Multi-bit $\Sigma\Delta M$          |

| 2.3.4.          | Multi Feedback and Multi Feed-Forward ΣΔM          |

| 2.3.5.          | Multistage Noise Shaping (MASH) ΣΔM                |

| 2.3.6.          | Switched-Capacitor, Active-RC and Gm-C Integrators |

| 2.3.7. Band-pass Modulators                                                         | 22 |

|-------------------------------------------------------------------------------------|----|

| 2.4. Methods of Reducing Effect of DAC Nonlinearities in Multi-bit $\Sigma\Delta M$ | 23 |

| 2.5. Stability of $\Sigma\Delta Ms$                                                 | 25 |

| 2.6. Strategies to Improve Figure of Merit                                          | 26 |

| 3. Literature Review                                                                | 29 |

| 3.1. MASH Architectures and Unity-STF                                               | 30 |

| 3.2. Integrator Circuits                                                            | 33 |

| 3.3. Multi-bit Quantizers                                                           | 37 |

| 3.4. Jitter Reduction Techniques                                                    | 40 |

| 3.5. Summary                                                                        | 41 |

| 4. Passive Sigma-Delta Modulators                                                   | 47 |

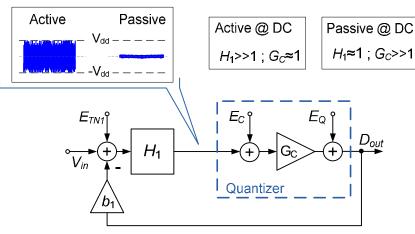

| 4.1. Active vs. Passive $\Sigma \Delta M$                                           | 47 |

| 4.1.1. Analysis of a $1^{st}$ -Order $\Sigma \Delta M$                              | 48 |

| 4.1.2. Dead Zones                                                                   | 49 |

| 4.1.3. Analysis of a $2^{nd}$ -Order $\Sigma \Delta M$                              | 49 |

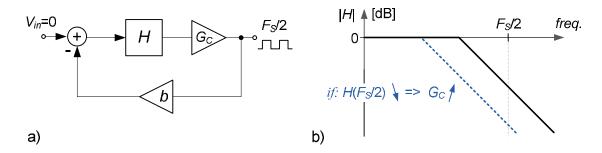

| 4.2. Approximation of the Gain of the Comparator                                    | 51 |

| 4.3. Concept of Ultra-Incomplete Settling (UIS) in a Switched-Capacitor Integrator  | 52 |

| 4.4. Discrete-Time Passive Integrator                                               | 53 |

| 4.4.1. Non-Ideal Effects in the Passive UIS Switched-Capacitor Integrator           | 57 |

| 4.5. Continuous-Time Passive Integrator with Switched-Capacitor Feedback            | 58 |

| 4.6. Thermal Noise Analysis                                                         | 62 |

| 4.6.1. Passive Discrete-Time Integrator                                             | 62 |

| 4.6.2. Passive Continuous-Time Integrator                                           | 63 |

| 4.7. Jitter Analysis                                                                | 65 |

| 4.7.1. Passive Continuous-Time Integrator                                           | 65 |

| 4.7.2.   | Passive Discrete-Time Integrator                                          | . 66 |

|----------|---------------------------------------------------------------------------|------|

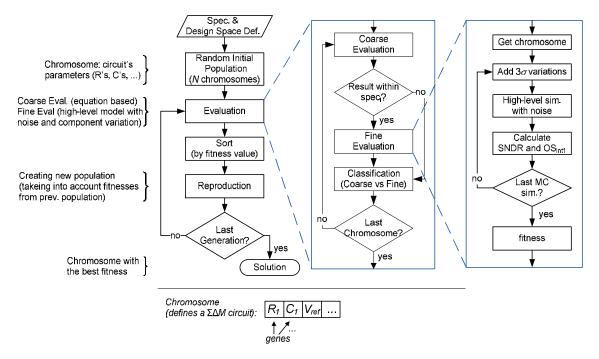

| 4.8. Sy  | stematic Design Methodology Using Optimization Based on Genetic Algorithm | . 67 |

| 4.9. Su  | immary                                                                    | . 69 |

| 5. Examp | les of Passive and Passive-Active $\Sigma\Delta Ms$                       | . 71 |

| 5.1. C   | ase Study: 1 <sup>st</sup> -Order Discrete-Time $\Sigma\Delta M$          | . 71 |

| 5.1.1.   | Block Diagram and Transfer Functions                                      | . 71 |

| 5.1.2.   | Circuit Implementation                                                    | . 72 |

| 5.1.3.   | Electrical Simulations                                                    | . 75 |

| 5.1.4.   | Case Study Summary                                                        | . 75 |

| 5.2. D   | esign Example #1: $2^{nd}$ -Order Discrete-Time $\Sigma \Delta M$         | . 75 |

| 5.2.1.   | Block Diagram and Transfer Functions                                      | . 76 |

| 5.2.2.   | Circuit Implementation                                                    | . 77 |

| 5.2.3.   | Electrical Simulations                                                    | . 78 |

| 5.2.4.   | Design Example Summary                                                    | . 79 |

| 5.3. C   | ase Studies of Higher Order Architectures of $\Sigma\Delta Ms$            | . 79 |

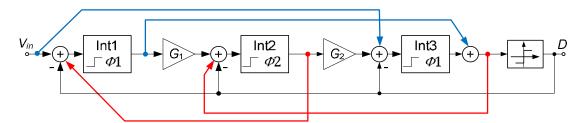

| 5.3.1.   | Third-Order $\Sigma\Delta M$                                              | . 80 |

| 5.3.2.   | SMASH $\Sigma\Delta M$                                                    | . 83 |

| 5.3.3.   | ΜΑՏΗ ΣΔΜ                                                                  | . 83 |

| 5.3.4.   | Case Studies Summary                                                      | . 84 |

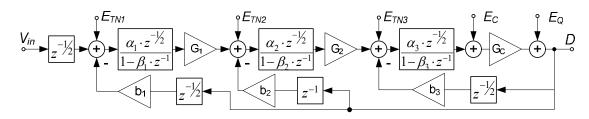

| 5.4. D   | esign Example #2: Continuous-Time 2-1 MASH $\Sigma\Delta M$               | . 85 |

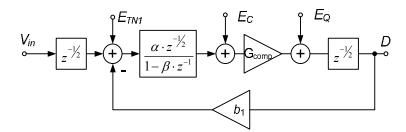

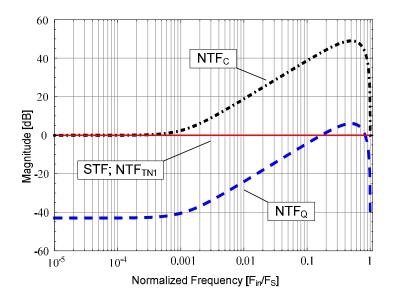

| 5.4.1.   | Block Diagram and Transfer Functions                                      | . 85 |

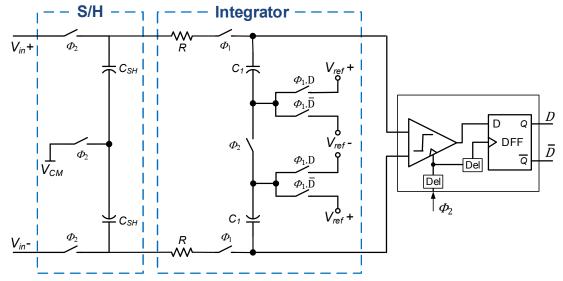

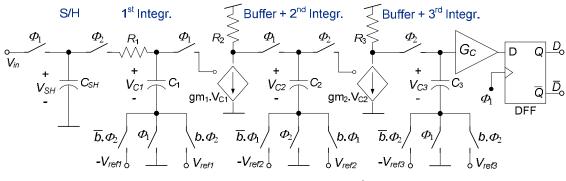

| 5.4.2.   | Circuit Implementation                                                    | . 89 |

| 5.4.3.   | Digital Cancellation Logic (DCL) Implementation                           | . 91 |

| 5.4.4.   | Optimization procedure                                                    | . 94 |

| 5.4.5.   | Electrical Simulations                                                    | . 96 |

| 5.4     | .6.    | Design Example Summary                      | 97  |

|---------|--------|---------------------------------------------|-----|

| 5.5.    | Sun    | nmary                                       | 97  |

| 6. Int  | egrate | d Prototypes and Measured Results           |     |

| 6.1.    | Disc   | crete-Time $2^{nd}$ -Order $\Sigma\Delta M$ |     |

| 6.1     | .1.    | Layout                                      |     |

| 6.1     | .2.    | Experimental Set-Up                         |     |

| 6.1     | .3.    | Measured Results                            |     |

| 6.2.    | Con    | ntinuous-Time 2-1 MASH ΣΔM                  |     |

| 6.2     | .1.    | Layout                                      |     |

| 6.2     | .2.    | Experimental Set-Up                         | 110 |

| 6.2     | .3.    | Measured Results                            |     |

| 7. Co   | nclusi | ons and Future Work                         |     |

| 7.1.    | Con    | nclusions                                   |     |

| 7.2.    | Futı   | ure Work                                    |     |

| Referen | ces    |                                             |     |

## **LIST OF FIGURES**

| Fig. 2.1 Conceptual scheme of an ADC system                                                                        | 7      |

|--------------------------------------------------------------------------------------------------------------------|--------|

| Fig. 2.2 Representation of anti-aliasing filter (a) for Nyquist-rate (b) for oversampling ADC                      | C 8    |

| Fig. 2.3 (a) Ideal characteristic of quantizer. (b) Quantization error                                             | 9      |

| Fig. 2.4 Spectral density of quantization noise power for: (a) Nyquist-rate and (b) oversam                        | npling |

| converter                                                                                                          | 9      |

| Fig. 2.5 (a) $\Sigma\Delta M$ ADC and (b) its linear z-domain model                                                | 10     |

| Fig. 2.6 Examples of noise shaping transfer functions                                                              | 11     |

| Fig. 2.7 Basic performance metrics: SNR, SNDR, DR                                                                  | 12     |

| Fig. 2.8 Example of a 1 <sup>st</sup> -order discrete-time $\Sigma\Delta M$                                        | 13     |

| Fig. 2.9 Example of spectral density of the 1 <sup>st</sup> -order $\Sigma\Delta M$ output signal power            | 13     |

| Fig. 2.10 Example of second-order $\Sigma \Delta M$                                                                | 14     |

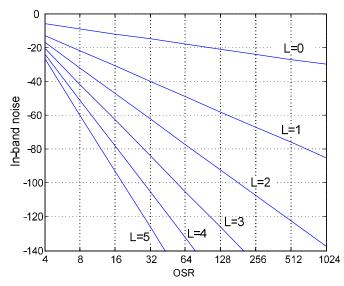

| Fig. 2.11 Theoretical SNR vs. OSR and modulator order [32]                                                         | 15     |

| Fig. 2.12 (a) Discrete-time and (b) continuous-time modulators                                                     | 15     |

| Fig. 2.13 Clock jitter effect in CT $\Sigma\Delta M$ (a) main error sources (b) DT vs. CT wavefor                  | ms of  |

| feedback DAC                                                                                                       | 16     |

| Fig. 2.14 Quantization characteristics of (a) single-bit and (b) multi-bit quantizers.                             | 17     |

| Fig. 2.15 General structure of a $2^{nd}$ -order $\Sigma \Delta M$                                                 | 18     |

| Fig. 2.16 General MASH ΣΔM structure                                                                               | 19     |

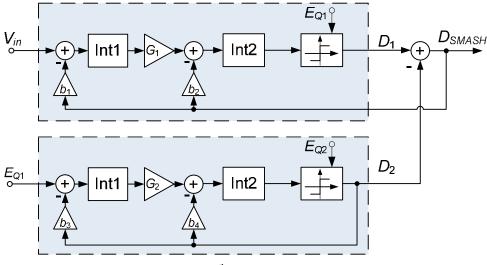

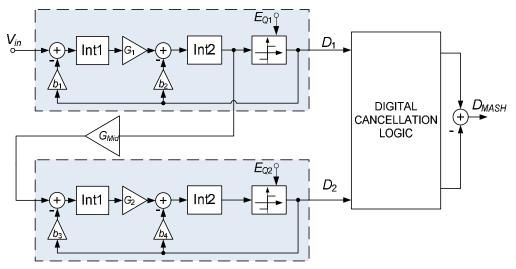

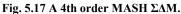

| Fig. 2.17 Example of $4^{\text{th}}$ order MASH $\Sigma\Delta M$ .                                                 | 20     |

| Fig. 2.18 A discrete-time switched-capacitor integrator                                                            | 21     |

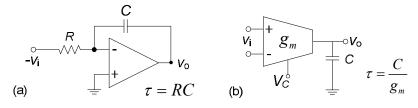

| Fig. 2.19 Continuous-time integrators: (a) Active-RC and (b) Gm-C                                                  | 21     |

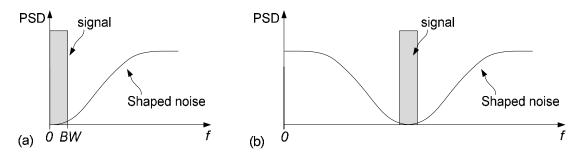

| Fig. 2.20 Conceptual output power spectral density of (a) low-pass and (b) band                                    | 1-pass |

| modulators                                                                                                         | 22     |

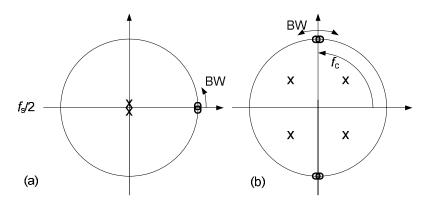

| Fig. 2.21 Example of pole-zero location of (a) low-pass and (b) band-pass NTFs                                     | 22     |

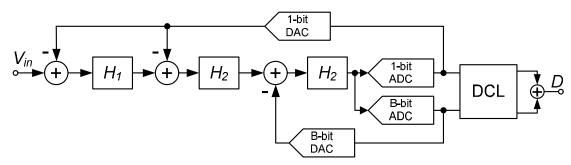

| Fig. 2.22 Dual quantization in single-loop $\Sigma\Delta M$ .                                                      | 23     |

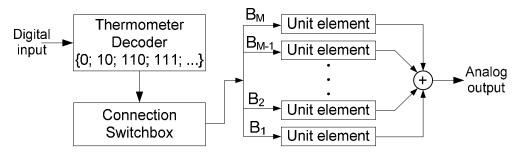

| Fig. 2.23 Parallel unit element DAC with thermometer coded digital input                                           | 24     |

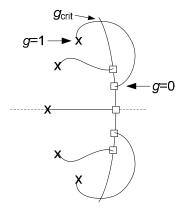

| Fig. 2.24 Root locus of the example 5 <sup>th</sup> -order $\Sigma \Delta M$ affected by varying quantizer gain, g | 26     |

| Fig. 2.25 Theoretical in-band noise power vs. OSR [4 ch. 1]                                                        | 27     |

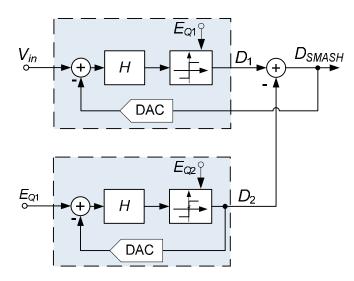

| Fig. 3.1 General SMASH structure.                                                                                  | 31     |

| Fig. 3.2 Block diagram of $\Sigma\Delta M$ with unity-STF                                                          | 32     |

| Fig. 3.3 Pseudo-differential SC integrator using class-C inverters [47, 48]                                        | 33     |

| Fig. 3.4 Basic switched-capacitor low-pass filter.                                                                 | 35     |

| Fig. 3.5 Simple low-pass filter (a) and gain-boost filter, N=2 for simplicity (b)                                  | 36     |

| Fig. 3.6 Passive filter circuit                                                                                         | 36      |

|-------------------------------------------------------------------------------------------------------------------------|---------|

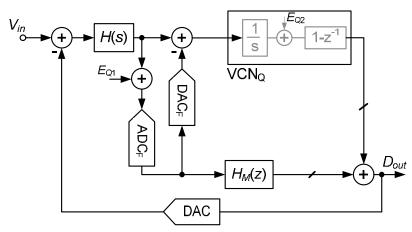

| Fig. 3.7 Block diagram of the VCO-based $\Sigma\Delta M$ from [56]                                                      | 39      |

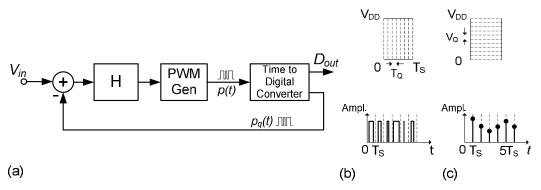

| Fig. 3.8 (a) PWM-based quantizer [59] (b) discrete levels of pulse width (c) discrete levels                            | vels of |

| amplitude                                                                                                               | 40      |

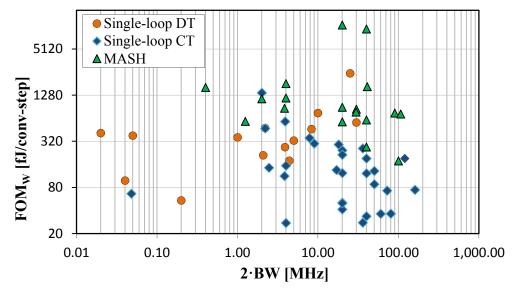

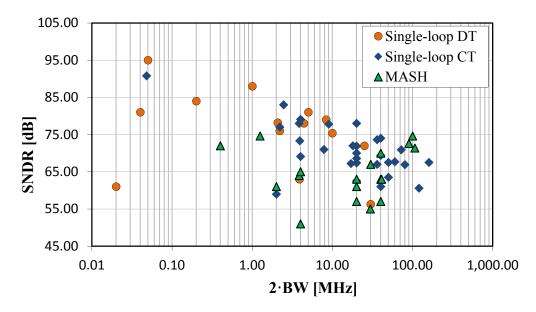

| Fig. 3.9 The graph FoM <sub>W</sub> vs. $2 \cdot BW$ of the state-of-the-art $\Sigma \Delta Ms$ .                       | 42      |

| Fig. 3.10 The graph SNDR vs. $2 \cdot BW$ of the state-of-the-art $\Sigma \Delta Ms$                                    | 42      |

| Fig. 4.1 Linear model of single-loop $1^{st}$ -order $\Sigma \Delta M$                                                  | 48      |

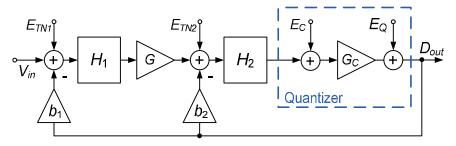

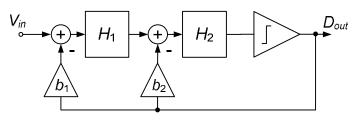

| Fig. 4.2 Linear model of single-loop $2^{nd}$ -order $\Sigma\Delta M$ .                                                 | 50      |

| Fig. 4.3 First order $\Sigma\Delta M$ with $V_{in} = 0$ (a) and frequency response of a first order passiv              | e loop  |

| filter (b).                                                                                                             | 51      |

| Fig. 4.4 Second-order $\Sigma\Delta M$                                                                                  | 52      |

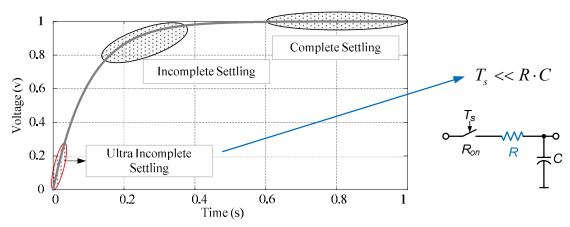

| Fig. 4.5 Capacitor voltage for a step input (normalized time)                                                           | 53      |

| Fig. 4.6 Schematic of a single-ended switched-capacitor integrator and corresponding                                    | timing  |

| diagram                                                                                                                 | 53      |

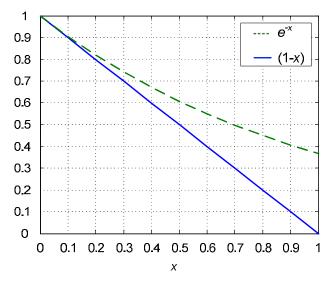

| Fig. 4.7 1 <sup>st</sup> -order $\Sigma\Delta M$ built using differential passive UIS switched-capacitor integrator.    | 54      |

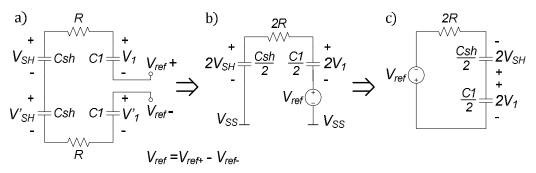

| Fig. 4.8 S/H and integrator circuits in phase $\Phi$ 1 (a) and they transformation (b, c)                               | 54      |

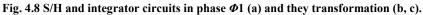

| Fig. 4.9 $e^{-x}$ versus (1 -x) approximation                                                                           | 56      |

| Fig. 4.10 Typical voltage waveforms in capacitors C1 and CSH                                                            | 56      |

| Fig. 4.11 Single-ended branch of the discrete-time integrator with parasitic capacitances (                             | (a) and |

| integrator with moved input switch (b).                                                                                 | 58      |

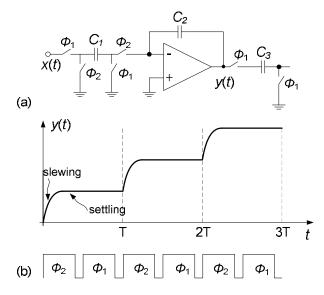

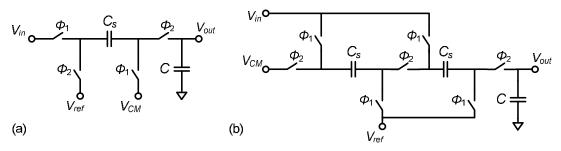

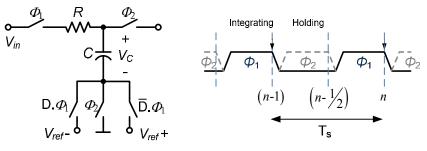

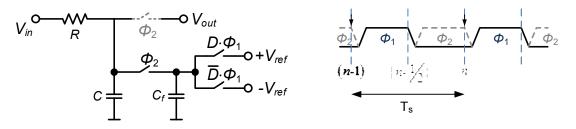

| Fig. 4.12 Schematic of a single-ended RC integrator and corresponding timing diagram                                    | 58      |

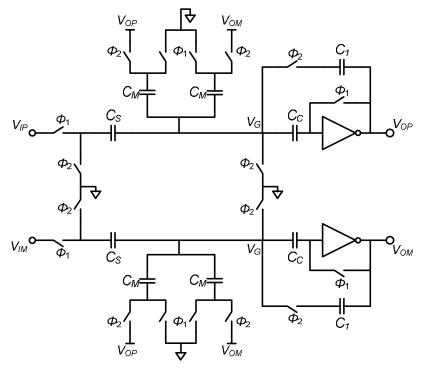

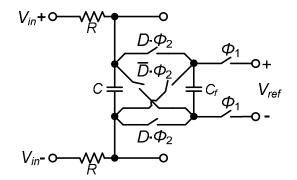

| Fig. 4.13 Schematic of a differential RC integrator                                                                     | 61      |

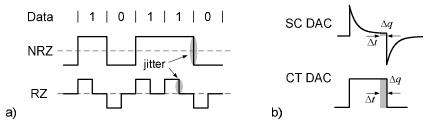

| Fig. 4.14 Clock jitter in the feedback of a CT $\Sigma\Delta M$ . (a) Simplified waveforms in NRZ a                     | nd RZ   |

| DAC, (b) SC vs. CT DAC waveforms.                                                                                       | 65      |

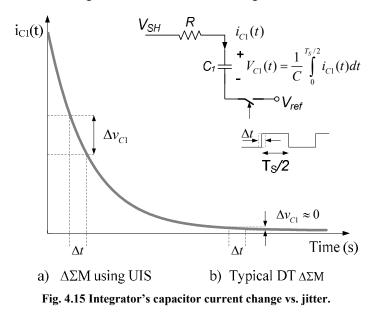

| Fig. 4.15 Integrator's capacitor current change vs. jitter                                                              | 66      |

| Fig. 4.16 Genetic algorithm optimization flow.                                                                          | 68      |

| Fig. 5.1 Block diagram of the passive $1^{st}$ -order $\Sigma \Delta M$                                                 |         |

| Fig. 5.2 Ideal graphs of STF and NTFs of the 1 <sup>st</sup> -order passive $\Sigma\Delta M$                            | 72      |

| Fig. 5.3 Complete schematic of the passive $1^{st}$ -order $\Sigma \Delta M$ modulator circuit                          | 73      |

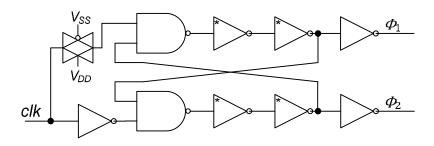

| Fig. 5.4 Generator of two non-overlapping phases.                                                                       | 73      |

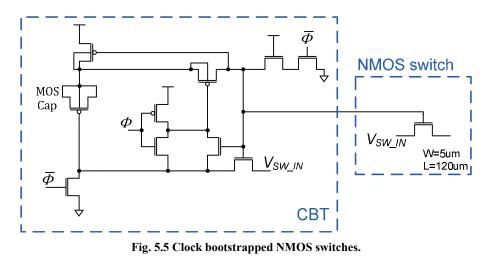

| Fig. 5.5 Clock bootstrapped NMOS switches.                                                                              | 74      |

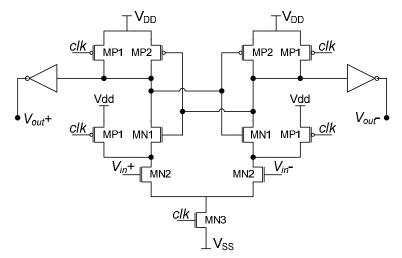

| Fig. 5.6 Electrical schematic of the comparator [98].                                                                   | 74      |

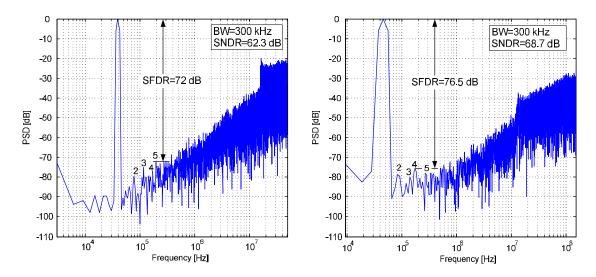

| Fig. 5.7 $2^{15}$ point PSD of the 1 <sup>st</sup> -order $\Sigma \Delta M$ for $F_s = 100$ MHz, $F_s = 300$ MHz.       | 75      |

| Fig. 5.8 Linear model of the proposed $\Sigma\Delta M$ based on UIS                                                     | 76      |

| Fig. 5.9 Ideal graphs of STF and NTFs of the $2^{nd}$ -order passive $\Sigma\Delta M$ .                                 | 76      |

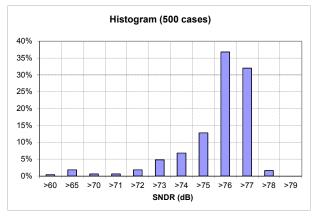

| Fig. 5.10 Histogram of the SNDR obtained through 500-case MC analysis of $2^{nd}$ -order $\Sigma\Delta$                 | M77     |

| Fig. 5.11 Complete schematic of the $\Sigma\Delta M$ including clocking circuitry                                       | 78      |

| Fig. 5.12 PSD with $2^{13}$ point of the output bit-stream of the $\Sigma\Delta M$ , obtained by ele                    | ctrical |

| transient noise simulation of the complete circuit, for 2 $mV_{\text{pp,diff}}$ and 600 $mV_{\text{pp,diff}}$ amplitude | ides of |

| the input signal.                                                                                                       | 79      |

| Fig. 5.13 A 3 <sup>rd</sup> -order multi feedback and feed-forward $\Sigma\Delta M$                                        | 81     |

|----------------------------------------------------------------------------------------------------------------------------|--------|

| Fig. 5.14 A block diagram of the $3^{rd}$ -order $\Sigma\Delta M$                                                          | 81     |

| Fig. 5.15 A simplified single-ended version of the $3^{rd}$ -order $\Sigma \Delta M$ circuit                               | 81     |

| Fig. 5.16 A 4 <sup>th</sup> order SMASH $\Sigma\Delta M$ .                                                                 | 83     |

| Fig. 5.17 A 4th order MASH $\Sigma\Delta M$ .                                                                              | 84     |

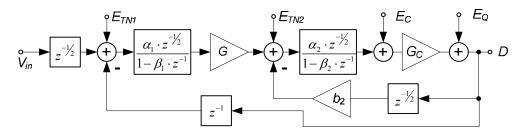

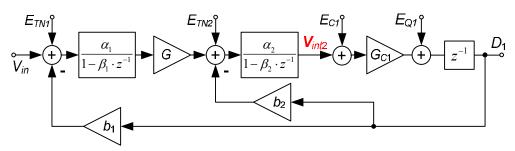

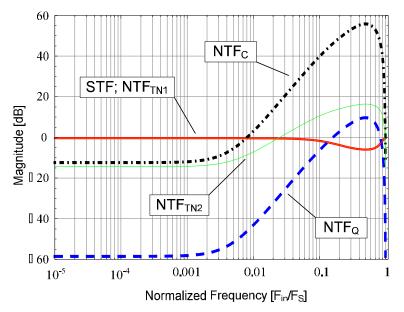

| Fig. 5.18 Block diagram of the proposed 2-1 MASH ΣΔM                                                                       | 86     |

| Fig. 5.19 Block diagram of the proposed first stage $\Sigma\Delta M$ .                                                     | 86     |

| Fig. 5.20 Middle gain block $G_{Mid}$ and the proposed second stage $\Sigma \Delta M$                                      | 86     |

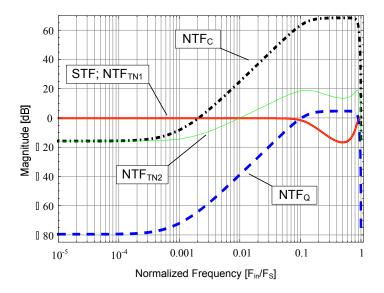

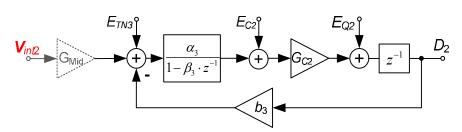

| Fig. 5.21 Ideal graphs of STF and NTFs of the first stage of the MASH modulator, the 2 <sup>nd</sup>                       | -order |

| ΣΔΜ                                                                                                                        | 88     |

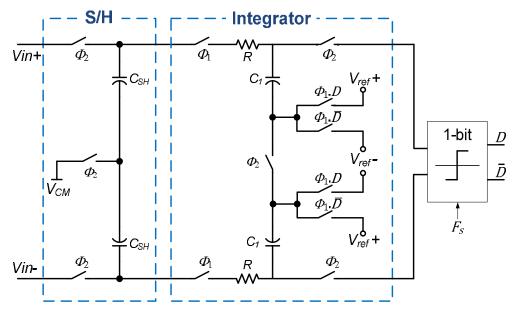

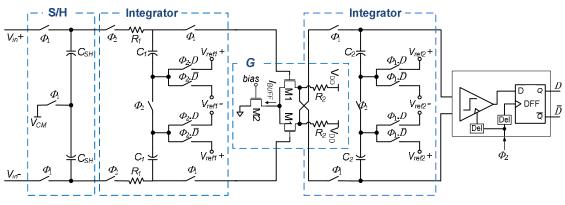

| Fig. 5.22 Schematic of the proposed MASH modulator.                                                                        | 90     |

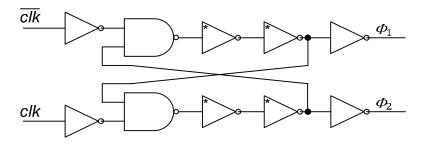

| Fig. 5.23 NAND based two-phase clock generator                                                                             | 90     |

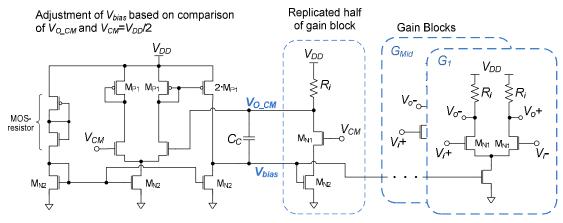

| Fig. 5.24 The Gain Blocks with the replica bias circuit.                                                                   | 91     |

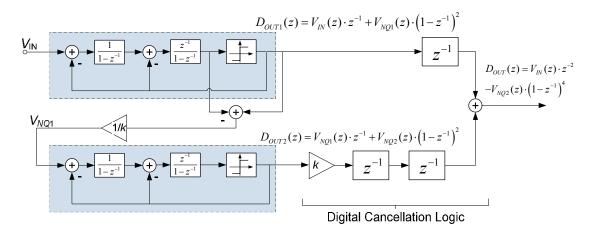

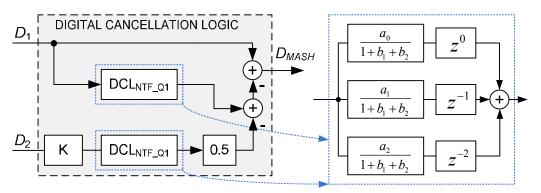

| Fig. 5.25 First modification of digital cancellation logic (DCL) block.                                                    | 92     |

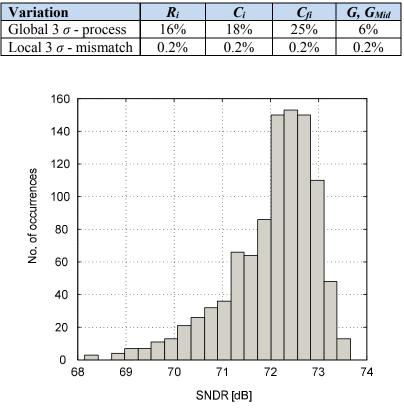

| Fig. 5.26 SNDR histogram of the MASH $\Sigma\Delta M$ of 1000-case MC analysis with process                                | s and  |

| mismatch variations added to the values of the modulator's components                                                      | 95     |

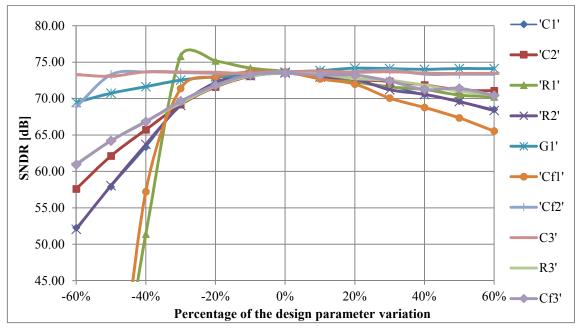

| Fig. 5.27 SNDR of the MASH modulator versus variation of the components around the op                                      | otimal |

| design point selected by the genetic algorithm based optimizer                                                             | 95     |

| Fig. 5.28 SNDR of the $2^{nd}$ -order $\Sigma\Delta M$ (first stage of the MASH modulator) vs variation                    | of the |

| components around the optimal design point selected by the genetic algorithm based optim                                   | mizer. |

|                                                                                                                            | 96     |

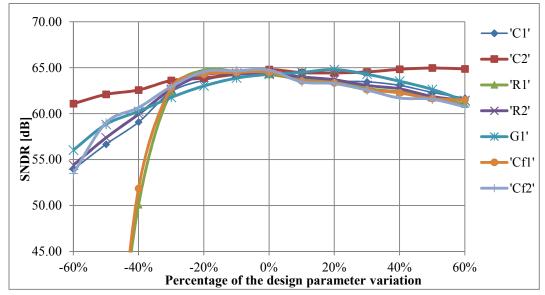

| Fig. 5.29 The $2^{13}$ point PSD of a) the 2-1 MASH $\Sigma\Delta M$ b) the $2^{st}$ -order $\Sigma\Delta M$ (first stage) | 96     |

| Fig. 6.1 Layout of the $2^{nd}$ -order $\Sigma \Delta M$                                                                   | 100    |

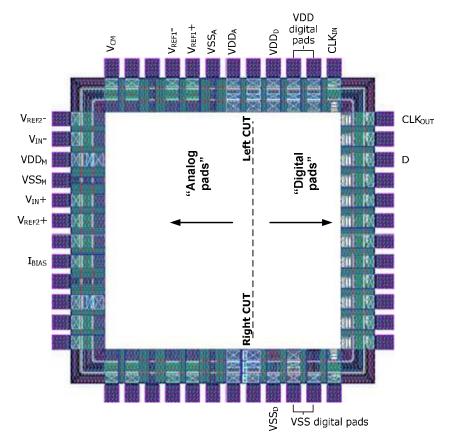

| Fig. 6.2 Layout of the pad ring with the names of the used pads (for interfacing the $2^{nd}$                              |        |

| ΣΔΜ)                                                                                                                       |        |

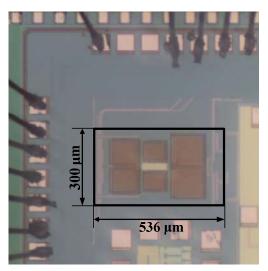

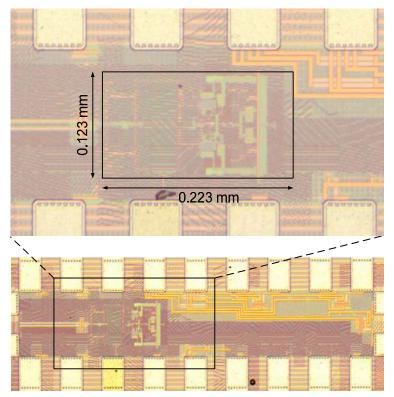

| Fig. 6.3 Chip die photograph of the $2^{nd}$ -order $\Sigma \Delta M$ circuit.                                             | 102    |

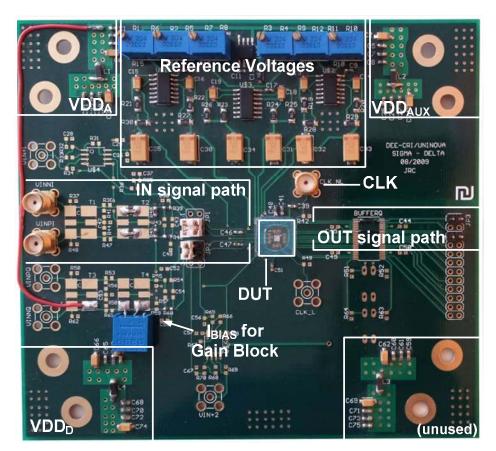

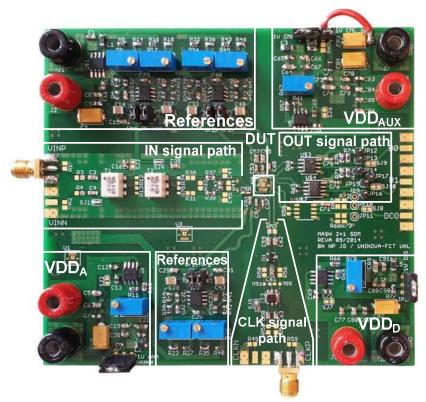

| Fig. 6.4 Photograph of the PCB evaluation board for the $2^{nd}$ -order $\Sigma\Delta M$ .                                 |        |

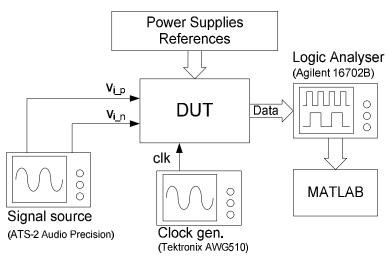

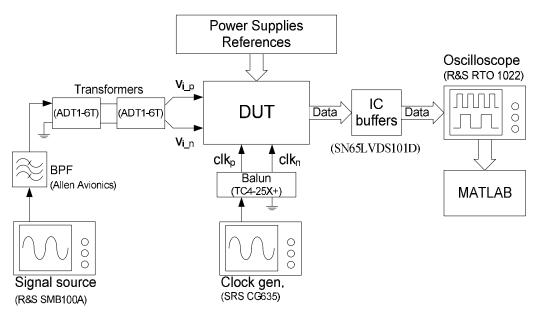

| Fig. 6.5 Simplified schematic of the test setup of the DT $2^{nd}$ -order $\Sigma\Delta M$ .                               | 104    |

| Fig. 6.6 Measured spectra of the 2 <sup>nd</sup> -order $\Sigma \Delta M$ for $F_{in}$ =22 kHz, THD=-80.7 dB (sample II    | I) 105 |

| Fig. 6.7 SNR/SNDR vs. amplitude graphs for a 22 kHz input signal (sample III)                                              | 106    |

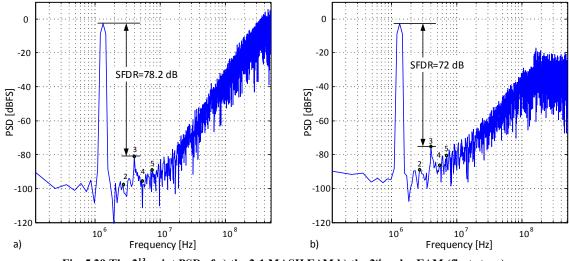

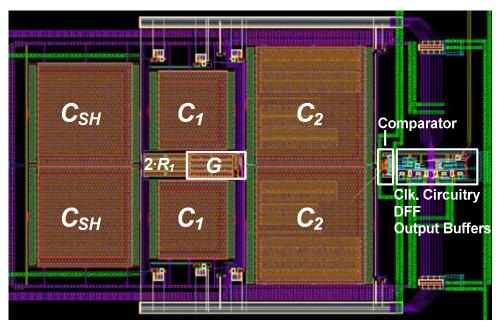

| Fig. 6.8 Layout of the 2-1 MASH $\Sigma\Delta M$                                                                           | 108    |

| Fig. 6.9 Layout of the pad ring used to interface the 2-1 MASH $\Sigma\Delta M$ .                                          |        |

| Fig. 6.10 Micrograph of the test chip die in 65 nm CMOS                                                                    | 109    |

| Fig. 6.11. Photograph of the test board for the MASH $\Sigma\Delta M$                                                      | 111    |

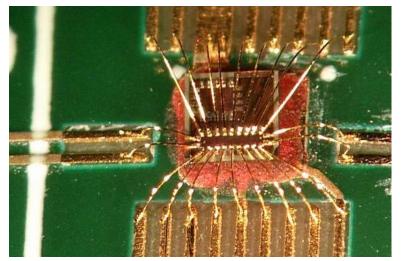

| Fig. 6.12 DUT direct bonded to the test board                                                                              | 112    |

| Fig. 6.13. Simplified schematic of the test setup.                                                                         | 113    |

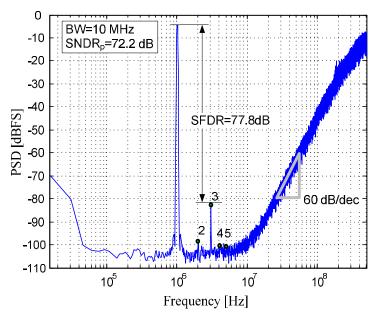

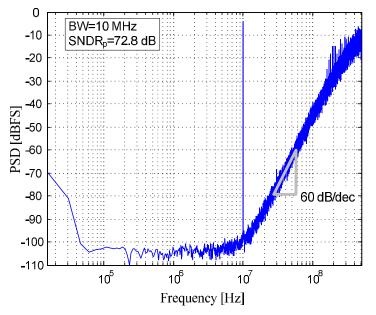

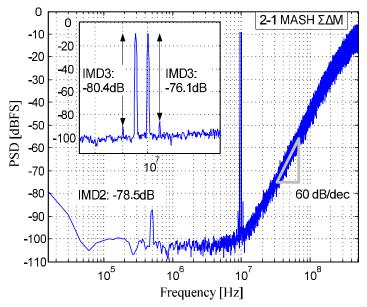

| Fig. 6.14. Measured spectra of the 2-1 MASH $\Sigma\Delta M$ (sample II) for $F_{in}=1$ MHz                                | 114    |

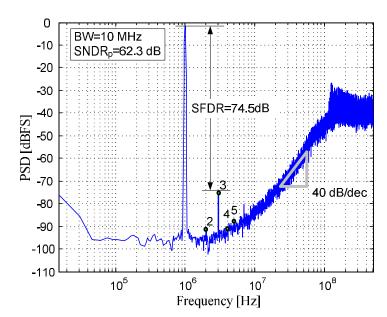

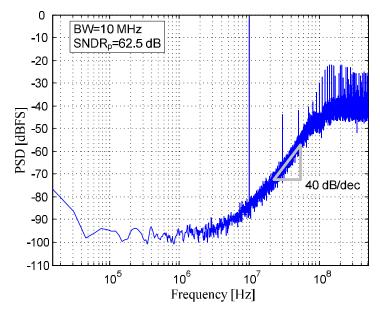

| Fig. 6.15 Measured spectra of the 2-1 MASH $\Sigma\Delta M$ (sample II) for $F_{in}=10$ MHz                                | 114    |

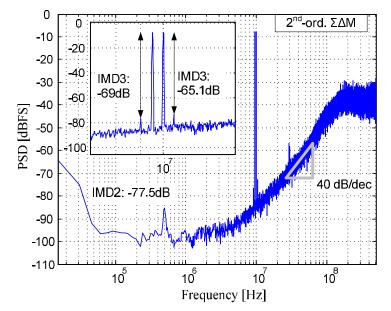

| Fig. 6.16. Measured spectra of the $2^{nd}$ -order $\Sigma \Delta M$ (sample II) for $F_{in}=1$ MHz.                       | 115    |

| Fig. 6.17 Measured spectra of the $2^{nd}$ -order $\Sigma \Delta M$ (sample II) for $F_{in}=10$ MHz.                       |        |

| Fig. 6.18 Measured spectra with two input tones near 10 MHz of the 2-1 MASH $\Sigma\Delta M$ (sample                 |

|----------------------------------------------------------------------------------------------------------------------|

| II)                                                                                                                  |

| Fig. 6.19 Measured spectra with two input tones near 10 MHz the $2^{nd}\text{-}order$ single-loop $\Sigma\Delta M$   |

| (sample II)                                                                                                          |

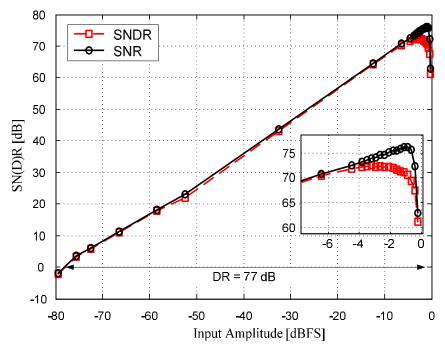

| Fig. 6.20 Measured SN(D)R as a function of input signal amplitude for 2-1 MASH $\Sigma\Delta M$                      |

| (sample II)                                                                                                          |

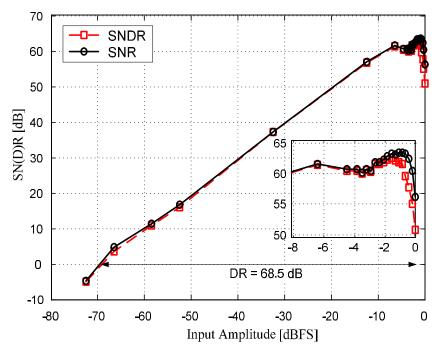

| Fig. 6.21 Measured SN(D)R as a function of input signal amplitude $2^{nd}\text{-}order$ single-loop $\Sigma\Delta M$ |

| (sample II)                                                                                                          |

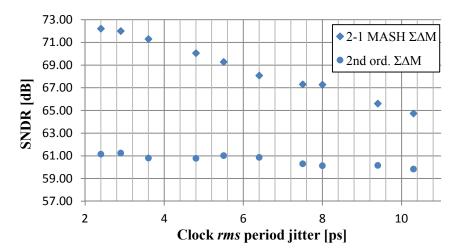

| Fig. 6.22 Measured SNDR vs. clock <i>rms</i> period jitter, <i>F<sub>in</sub></i> =1 MHz, (sample II)118             |

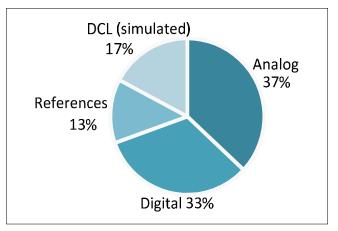

| Fig. 6.23 Percentage power break-down of the 2-1 MASH $\Sigma\Delta M$ (sample II)118                                |

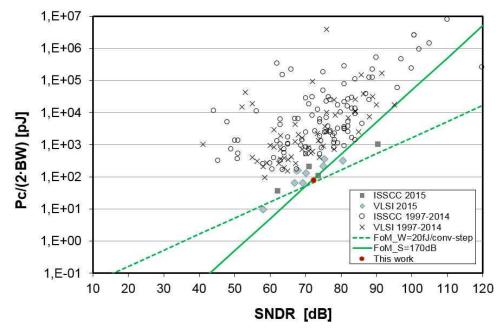

| Fig. 7.1 Power efficiency (P_c/(2·BW)) of oversampling ADCs as a function of SNDR [106]                              |

| (where FoM <sub>W</sub> =P/( $2 \cdot BW \cdot 2^{(SNDR-1.76)/6.02}$ ), FoMS=SNDR+10· $log_{10}(BW/P)$ )             |

## LIST OF TABLES

| Table 3.1 Course $\Sigma \Delta M$ categorization based on the achieved SNDR and BW.                                 | 29  |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2 Specification of standards [41].                                                                           | 29  |

| Table 3.3 State-of-the-art single-loop low-pass discrete-time $\Sigma\Delta Ms$ .                                    | 43  |

| Table 3.4 State-of-the-art single-loop low-pass continuous-time $\Sigma\Delta Ms$ .                                  | 43  |

| Table 3.5 State-of-the-art cascade low-pass $\Sigma\Delta Ms$                                                        | 44  |

| Table 5.1 The 1 <sup>st</sup> -order passive $\Sigma\Delta M$ design parameters                                      | 73  |

| Table 5.2 Simulated key performance parameters of the $1^{st}$ -order $\Sigma \Delta Ms$ .                           | 75  |

| Table 5.3 Passive component values and gain coefficients.                                                            | 78  |

| Table 5.4 Simulated key performance parameters of the $2^{nd}$ -order $\Sigma\Delta M$                               | 79  |

| Table 5.5 Simulated key performance parameters of the 3 <sup>rd</sup> -order $\Sigma\Delta M$ ( $F_S = 100$ MHz).    | 82  |

| Table 5.6 GA optimization results of the $3^{rd}$ -order $\Sigma \Delta M$ ( $F_S = 1$ GHz)                          | 83  |

| Table 5.7 GA optimization results of four $\Sigma \Delta M$ architectures clocked at $F_s = 1$ GHz                   | 84  |

| Table 5.8 The 2-1 MASH passive $\Sigma\Delta M$ design parameters.                                                   | 89  |

| Table 5.9 Modified digital cancellation logic (DCL) described as a look-up table                                     | 93  |

| Table 5.10 $3\sigma$ values of the circuit components' variations                                                    | 95  |

| Table 5.11 Simulation results of the 2–1 MASH $\Sigma\Delta M$ and the 2 <sup>nd</sup> -order $\Sigma\Delta M$       | 97  |

| Table 6.1 List of pads used to interface the $2^{nd}$ -order $\Sigma\Delta Ms$ prototype                             | 102 |

| Table 6.2 Measured key performance parameters of the DT 2 <sup>nd</sup> -order $\Sigma\Delta M$ ( $F_{in}$ =22 kHz). | 105 |

| Table 6.3 List of pads used to interface the MASH $\Sigma\Delta Ms$ prototype                                        | 110 |

| Table 6.4 Measured key performance parameters of the 2–1 MASH $\Sigma\Delta M$ ( $F_{in}$ =1 MHz)                    | 119 |

| Table 6.5 Measured key performance parameters of the 2 <sup>nd</sup> -order $\Sigma \Delta M$ ( $F_{in}$ =1 MHz)     | 119 |

| Table 7.1 Comparison of the 2-1 MASH $\Sigma\Delta M$ prototype (sample II) with the prior $\Sigma\Delta Ms$         | 121 |

## LIST OF SYMBOLS AND ACRONYMS

| Φ                     | Clock Phase                             |

|-----------------------|-----------------------------------------|

| dB <sub>FS</sub>      | dB Full Scale                           |

| $F_{in}$              | Input Signal Frequency                  |

| $F_S$                 | Sampling Frequency                      |

| gm                    | Transconductance                        |

| mV <sub>pp,diff</sub> | mV peak-to-peak, differential           |

| · pp,um               |                                         |

| AC                    | Alternating Current                     |

| A/D                   | Analog-to-Digital                       |

| ADC                   | Analog-to-Digital Converter             |

| BW                    | Bandwidth                               |

| CMOS                  | Complementary Metal-Oxide-Semiconductor |

| СТ                    | Continuous-Time                         |

| DAC                   | Digital-to-Analog Converter             |

| DC                    | Direct Current                          |

| DCL                   | Digital Cancellation Logic              |

| DFF                   | D-Type Flip-Flop                        |

| DR                    | Dynamic Range                           |

| DRC                   | Design Rule Check                       |

| DT                    | Discrete-Time                           |

| DUT                   | Device Under Test                       |

| ENOB                  | Effective-Number-Of-Bits                |

| FoM                   | Figure of Merit                         |

| FPGA                  | Field Programmable Gate Array           |

| GA                    | Genetic Algorithm                       |

| GBW                   | Gain-Bandwidth Product                  |

| IC                    | Integrated Circuit                      |

| LVS                   | Layout Versus Schematic                 |

| MASH                  | Multistage Noise-Shaping                |

| MiM                   | Metal-insulator-Metal                   |

| MOS                   | Metal-Oxide-Semiconductor               |

| NTF                   | Noise Transfer Function                 |

|                       |                                         |

| Op-amp         | Operational Amplifier                  |

|----------------|----------------------------------------|

| OSR            | Oversampling Ratio                     |

| ΟΤΑ            | Operational Transconductance Amplifier |

| PCB            | Printed Circuit Board                  |

| PECL           | Positive Emitter Coupled Logic         |

| PSD            | Power Spectral Density                 |

| PWM            | Pulse-Width Modulation                 |

| S/H            | Sample and Hold                        |

| SC             | Switched-Capacitor                     |

| $\Sigma\Delta$ | Sigma-Delta                            |

| ΣΔΜ            | Sigma-Delta Modulator                  |

| SMASH          | Sturdy MASH                            |

| SNDR           | Signal-to-Noise-plus-Distortion Ratio  |

| SNR            | Signal-to-Noise Ratio                  |

| STF            | Signal Transfer Function               |

| UIS            | Ultra Incomplete Settling              |

| VCO            | Voltage-Controlled Oscillator          |

|                |                                        |

### **1. INTRODUCTION AND MOTIVATION**

Analog-to-digital converters (ADCs) are important building blocks in all of today's electronic circuits. They are used in a wide range of devices in medical, consumer, instrumentation and communication applications, just to name a few. Many different ADC architectures are available for a vast selection of resolution and bandwidth requirements. ADCs' performance affects the efficiency and speed at which analog information can be converted into digital signals. Since an energy efficient operation is required by modern electronic systems, there has been a great push to reduce energy consumption in all relevant system building blocks, including ADCs [1]. The constant size reduction of CMOS technologies has resulted in an increase of the transition frequency of CMOS transistors, but it has also resulted in the reduction of the intrinsic gain of these devices [2]. As a consequence, it has become more difficult to design high gain and high bandwidth amplifiers with reduced power dissipation, making the design of ADCs that require such amplifiers, including  $\Sigma\Delta$ Ms, more challenging.

There are several possible implementation choices for  $\Sigma \Delta M$  architectures [3]. Continuous-time (CT) modulators are becoming more popular than discrete time (DT) modulators, since they can operate at higher clock rates [4, ch. 6]. Recent  $\Sigma \Delta M$  design trends include higher order loop filters (integrators) [5], digitally assisted digital-to-analog converter (DAC) correction [6, 7], and reduced number of operational amplifiers (op-amps) [5, 8]. These trends have contributed to an improvement of the figures of merit (FoMs) and to the decrease of the circuit active area. In the case of high order  $\Sigma\Delta Ms$ , MASH and SMASH structures reveal better stability and allow for more aggressive noise-shaping than their single-loop counterparts. Therefore, implementations of various MASH-like architectures can be found in recent publications [9-12]. In order to achieve reasonable cancellation of the quantization noise, a high gain in the integrators' amplifiers is desired. The amplifiers can improve the circuit linearity, parasitic insensitivity and robustness in exchange for the power they dissipate. Moreover, gain provided by the amplifiers in the active integrators, reduce the input-referred noise. On the other hand, even with the use of the techniques mentioned previously, the power consumption of the amplifiers is still a significant part of the total modulator's power consumption. In the case of increasing signal bandwidths, together with moderate-high resolutions and with diminishing supply voltage headroom, these amplifiers become difficult to design (since they must achieve a large enough gain-bandwidth product (GBW) to guaranty a small settling error during the limited clock period) and result in an increase of the power dissipation of  $\Sigma \Delta Ms$ .

One solution to deal with an issue of designing high gain amplifiers is to select passive or mixed active-passive  $\Sigma \Delta M$  architectures, where the processing gain of the comparator is used in the feedback loop of the modulator's filter [13]. This solution is very appealing for deep nanometer CMOS technologies, because a comparator can achieve large gain through positive feedback, which improves with faster transistors. This approach has been used in [13-20]. Passive integrators provide signal attenuation and therefore, are more sensitive to noise coupling than active integrators that use amplifiers. On the other hand, passive  $\Sigma \Delta M$ s are simpler (have less hardware complexity) compared to their active counterparts, do not require complex amplifiers and allow for significant power reduction.

The research question of this thesis is: how can one take advantage of the passive or hybrid active-passive structures in order to design  $\Sigma \Delta Ms$  achieving competitive power efficiency? Therefore, this thesis intends to investigate the passive and hybrid passive-active  $\Sigma \Delta M$  architectures and to define the most suitable area of application for these types of modulators.

This work focuses on the design of the integrated circuits (ICs). Therefore, a validation methodology ensuring proper operation of the IC is an important issue. Designing a circuit involves process of building and validating of: behavioral, high-level model of the system; transistor-based circuit schematic; layout and fabricated IC. High-level model, build in order to optimize circuit coefficients, is validated on the basis of its estimated performance. The schematic validation is based on electrical simulations (with process and temperature variations). At this point, one can verify if the system is working properly, according to the desired specifications. After the layout design the validation additionally includes post-layout simulations (including parasitics of the circuit) of the whole system, letting the designer to obtain the closest results to real behavior of the circuit. The most important and final is the validation of the IC prototype. The IC is soldered on the specially designed, fabricated testing board. Then meaningful data is collected and processed, following good measurement practices. If the obtained results meet the specification, the prototype can be considered as validated.

The first proposed implementation for a passive-active  $\Sigma \Delta M$  is based on ultra-incomplete settling (UIS). In this approach, a single switched-capacitor branch can implement a discrete-time (DT) lossy-integrator. As a proof of this concept, a 2<sup>nd</sup> order  $\Sigma \Delta M$ , has been built in a 130 nm CMOS technology and experimentally evaluated [21].

The second proposed implementation of a passive-active modulator is a continuous-time cascaded  $\Sigma\Delta M$  based on passive *RC* integrators (derived from the UIS structure [21]) and using low gain stages (~20 dB) instead of high gain amplifiers. Like in all circuit techniques, there are limits to the maximum achievable performance and the passive modulator structure requires a higher clock frequency (higher oversampling ratio) than other techniques used to design  $\Sigma\Delta Ms$ . This means that, that if the signal bandwidth is increased, the clock frequency would have to increase as well, in order to maintain the same signal-to-noise-plus-distortion ratio (SNDR).

Therefore, it would be very difficult to design the passive or passive-active modulator for high bandwidth applications. The analysis of various higher order  $\Sigma\Delta M$  topologies, supported by the optimization methodology, revealed that the passive-active modulator structures are suitable for moderate resolution (62 dB < SNDR  $\leq$  74 dB) and a medium signal bandwidth (5 MHz < BW  $\leq$  20 MHz) applications. Therefore, it was decided to design, fabricate and measure a moderate resolution  $\Sigma\Delta M$  achieving SNDR larger than 70 dB for a signal bandwidth of 10 MHz that occupies a small active area.

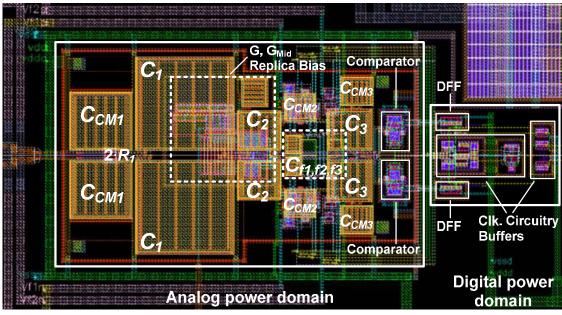

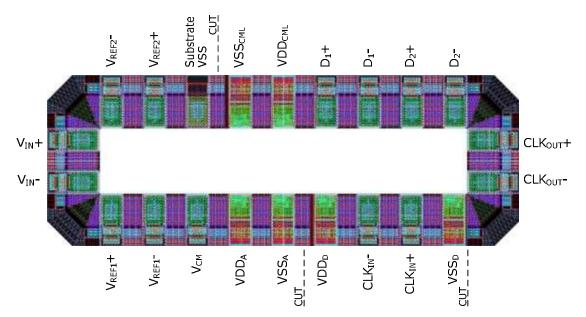

The final prototype developed in this thesis is a continuous-time 2-1 MASH  $\Sigma\Delta M$  based on passive *RC* integrators and low gain stages (~20 dB). The circuit has been designed in a 65 nm CMOS technology and occupies an active area of only 0.027 mm<sup>2</sup>. Measurement results show that the modulator achieves a peak SNR/SNDR/DR of 76/72.2 dB/77dB for an input signal bandwidth of 10 MHz, while dissipating 1.57 mW from a 1 V power supply voltage. The proposed  $\Sigma\Delta M$  achieves a Walden FOM of 23.6 fJ/level and a Schreier FOM of 175 dB. The innovations proposed in this circuit result, both, in the reduction of the power consumption and of the chip size. To the best of the author's knowledge the modulator achieves the lowest Walden FOM<sub>w</sub> for  $\Sigma\Delta M$  with signal bandwidth from 5 MHz to 50 MHz reported to date.

#### 1.1. Contributions

The main contributions of this research thesis are concentrated in the development and improvement of  $\Sigma\Delta M$  circuits using passive integrators. In this thesis we study and compare the behavior of passive and active  $\Sigma\Delta M$  architectures. This work also provides theoretical analysis of the proposed discrete-time and continuous-time passive integrators. These contributions have led to various publications. The main contributions of this work are summarized next:

- The derivation of the discrete-time transfer function and Z transfer function of the passive switched-capacitor integrator, using ultra incomplete settling (UIS), was shown in [22]. It also presented the thermal noise analysis of this passive integrator and studied the behavior of the 1<sup>st</sup>-order passive ΣΔM. Moreover, [23] analyzed the non-ideal effects present in the passive integrator, which become more significant for higher clock frequencies. It also presented two examples of 1<sup>st</sup>-order passive ΣΔMs operating with 100 MHz and 300 MHz sampling frequencies together with the results of the transient-noise electrical simulations of these two circuits.

- A  $2^{nd}$ -order  $\Sigma\Delta M$  circuit based on the discrete-time switched-capacitor integrators using ultra incomplete settling and implemented in 130 nm CMOS technology was proposed and described in [24]. The measured key performance parameters of three prototype circuit samples were presented in [21]. This approach allowed building a  $\Sigma\Delta M$  with mostly dynamic elements thus reducing the power dissipation. The  $\Sigma\Delta M$  architecture using this technique was presented and analyzed in detail. The validity of ultra

incomplete settling concept was confirmed by high-level simulations, transient noise electrical simulations and measurement results. The 2<sup>nd</sup>-order  $\Sigma\Delta M$  circuit, clocked at 100 MHz and consuming 298  $\mu$ W, achieved a peak DR/SNR/SNDR of 78.2/73.9/72.8 dB, respectively, for a signal bandwidth of 300 kHz. This resulted in a FoM<sub>W</sub> of 139.3 fJ/conv.-step and FoM<sub>s</sub> of 168 dB.

- A discrete-time, switched-capacitor, 2-2 MASH  $\Sigma\Delta M$ , clocked with frequency of 1 GHz, designed in a 65 nm CMOS technology was proposed in [25]. This modulator, similarly to the previous examples, was based on the passive integrators using the ultra-incomplete settling concept. Its high-level model and transistor-level implementation were discussed as well as modulator sensitivity to components variation. The work presented in [25] shown that it is possible to design MASH  $\Sigma\Delta M$ , using UIS integrators, operating in a 10 MHz bandwidth with a moderate resolution.

- A design methodology for ΣΔMs based on optimization using a genetic algorithm, was proposed in [26]. In order to obtain more accurate and faster performance predictions of a given ΣΔM architecture, the evaluation process is divided into a coarse (fast, equation based) and fine (slow, recursive simulation based) evaluations. It uses a high-level model of a given design, together with its theoretically estimated thermal noise, quantization noise, voltage swing variations and stability of the modulator. Furthermore, by taking into account mismatch errors between the circuit's components, it also selects the most insensitive design solution to components' variations. As a proof of validity of the methodology presented in [26], two case studies of continuous-time and a discrete-time ΣΔMs were carefully discussed.

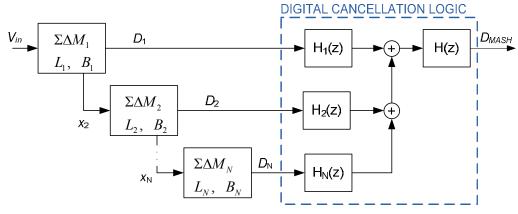

- A passive-active 2-1 MASH modulator, using *RC* integrators and simple low gain stages (~20 dB) was presented in [27]. In this work, a continuous-time implementation of the passive integrator with switched-capacitor feedback DAC has been proposed. A MASH modulator structure requires a digital cancellation logic that combines and filters its digital output signals (coming from the MASH stages). Therefore, simplified digital cancellation logic was proposed, which allowed for reduction in power and in number of components (avoiding multipliers, adders and multiplexers). The 2-1 MASH ΣΔM was implemented in a 65 nm CMOS technology and it occupied an active area of only 0.027 mm<sup>2</sup>. Measurement results showed that the circuit clocked at 1 GHz achieved a peak DR/SNR/SNDR of 77/76/72.2 dB for an input signal bandwidth of 10 MHz, while dissipating 1.57 mW from a 1 V power supply voltage. This modulator achieved a measured Walden FoM of 23.6 fJ/level and a Schreier FoM of 175 dB.

### 1.2. Thesis Layout

The thesis is composed of seven chapters (including the present introduction). It is structured as follows:

- Chapter 2 presents principles of ΣΔ modulation and basic definitions about ΣΔMs. It also describes performance metrics used for evaluating ADCs, techniques of reducing the feedback DAC nonlinearities and methods to further improve modulator's figure of merit.

- Chapter 3 gives a brief literature review regarding architectures and techniques used in designing recent single-loop and cascaded ΣΔMs. It also presents a comparison between selected state-of-the-art ΣΔMs.

- Chapter 4 compares active and passive  $\Sigma \Delta Ms$  structures and gives insight into discretetime and continuous-time implementations of passive integrators. In the last section it presents a general  $\Sigma \Delta M$  design methodology based on a genetic algorithm.

- Chapter 5 provides the high level and transistor level analyzes of the passive and hybrid passive-active  $\Sigma\Delta Ms$ . It discusses several modulators' case studies that include 1<sup>st</sup>, 3<sup>rd</sup>-order single-loop  $\Sigma\Delta Ms$  and cascaded  $\Sigma\Delta Ms$ . It also presents implementation details of two integrated prototypes, namely a discrete-time 2<sup>nd</sup>-order  $\Sigma\Delta M$  and a continuous-time 2-1 MASH  $\Sigma\Delta M$ .

- Chapter 6 presents the chip floor-planning, layout design, evaluation printed-circuitboard (PCB) design, testing setup and measured data obtained from the experimental evaluation of the two  $\Sigma\Delta Ms$  prototypes: 1) a discrete-time 2<sup>nd</sup>-order  $\Sigma\Delta M$ ; 2) a continuous-time 2-1 MASH  $\Sigma\Delta M$ .

- Chapter 7 discusses the results obtained by the evaluated circuits, comparing them to other state-of-the-art  $\Sigma\Delta Ms$  and it presents conclusions concerning this work as well as suggests topics for future work.

# 2. BASICS OF SIGMA-DELTA MODULATORS

This chapter presents some basic definitions about  $\Sigma\Delta M$  including description of different architectures and their analytical stability issues as well as performance metrics, techniques of DAC linearization and methods to improve modulators' figure of merits.

### 2.1. Principles of Sigma-Delta Modulation

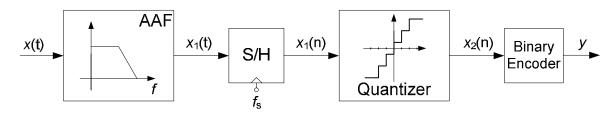

Sigma-delta ( $\Sigma\Delta$ ) modulation consists of two main operations, namely, oversampling and noise shaping, which are described in this chapter. Below we start by presenting basic principles of analog to digital (A/D) conversion, which apply directly to sigma-delta modulator ( $\Sigma\Delta$ M). A general analog to digital converter (ADC) (Fig. 2.1) is composed of:

- An anti-aliasing filter, which prevents folding or aliasing (interference between signal spectrum and its repeated versions) of high frequency components falling into the signal bandwidth;

- A sample and hold (S/H), that samples the continuous signal  $x_1(t)$  at sampling frequency  $F_s$  producing discrete signal  $x_1(n)$  (time discretization);

- A quantizer, which provides non-invertible process of mapping of continuous range of amplitudes of its input signal to finite number of discrete levels (amplitude discretization);

- A binary encoder, that transforms each level of the quantizer output signal into a unique binary code.

Fig. 2.1 Conceptual scheme of an ADC system

One of the main categories of data converters are the Nyquist-rate converters. In this type of

ADCs the sampling process is performed with a frequency of, at least, twice the signal bandwidth (BW)  $fs = 2 \cdot BW$  (usually somewhat higher because of practical reasons). This is the minimum  $F_s$ , which can be used according to the Nyquist theorem. This category of ADCs has one-to-one correspondence between their input and output signals. The converter has no memory and the samples are processed separately [4]. Each sequence (of given length) of the ADC input samples corresponds to its processed digital output word (of the same length).

The accuracy of a Nyquist-rate converter is mainly determined by the matching of its analog components. Therefore, it is difficult to achieve high resolutions for this type of ADCs [28]. Moreover the conversion resolution depends on the resolution of the quantizer. Concluding, one can claim that quantization and sampling operations limit the performance of Nyquist-rate converters.

The second category of A/D data converters are the oversampled converters. Their sampling rate is higher than the Nyquist rate,  $fs \gg 2 \cdot BW$ , (typically by factor 8 to 512 [4, p. 3]). The oversampling ratio (OSR) is defined as:

$$OSR = fs / (2 \cdot BW) \tag{2.1}$$

In a sigma delta modulator ( $\Sigma\Delta M$ ), which is an example of an oversampling converter, there is no one-to-one correspondence between input and output signals, because the converter uses all the preceding input samples to generate a valid output. This feature requires memory elements in the ADC structure.

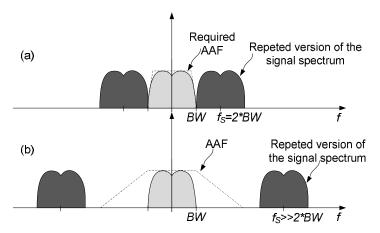

The oversampled converter, in contrary to the Nyquist-rate converter, does not require a sharp cut-off in the anti-aliasing filter, which could introduce phase distortion for signal components close to the cut-off frequency [29]. This means that, the requirements for anti-aliasing filter are relaxed as one can notice in Fig. 2.2.

Fig. 2.2 Representation of anti-aliasing filter (a) for Nyquist-rate (b) for oversampling ADC

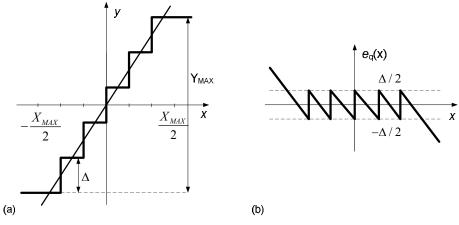

The ideal staircase characteristic of a quantizer is depicted in Fig. 2.3a. The digital output has  $2^{B}$  discrete levels. This number depends on resolution of the *B*-bit quantizer. The difference between two adjacent levels is called the quantization step,  $\Delta$ , and can be calculated as

$\Delta = Y_{MAX} / (2^B - 1)$ . For all input signals, in the range of  $X_{MAX}$ , the quantization error  $e_Q$  is limited to  $\pm \Delta/2$ , as depicted in Fig. 2.3b and its average value is zero. The quantization error, conceptually, can be defined as the difference between the analog version of its output and input signals. For inputs exceeding  $X_{MAX}$  the quantizer becomes overloaded and its  $e_Q$  grows beyond  $\pm \Delta/2$ .

Fig. 2.3 (a) Ideal characteristic of quantizer. (b) Quantization error

Assuming a rapidly varying input signal, the quantization error becomes uniformly distributed between  $\pm \Delta/2$  [30, p. 450]. This allows the quantizer, which is a nonlinear element, to be linearized and its  $e_Q$  modeled as, non-correlated with input signal, white quantization noise. The power spectral density (PSD) of the total quantization noise power equals:

$$S_{\mathcal{Q}}(f) = \frac{1}{F_{\mathcal{S}}} \left[ \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} e_q^2 de_q \right] = \frac{\Delta^2}{12F_{\mathcal{S}}}$$

(2.2)

and the in-band quantization noise power is given by:

$$P_{\mathcal{Q}} = \int_{-\mathrm{BW}}^{\mathrm{BW}} S_E(f) df = \frac{\Delta^2}{12 \cdot \mathrm{OSR}}$$

(2.3)

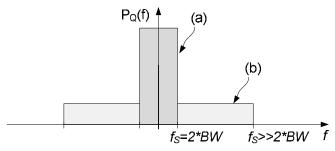

One can notice that, theoretically, doubling OSR decreases the  $P_Q$  by 3 dB. The fixed quantization noise power spreads over the sampling frequency range  $F_S$ , which is greater in case of an oversampled ADC than in case of a Nyquist-rate ADC. This means that, the  $P_Q$  of the former is much smaller comparing to the latter ADC (Fig. 2.4).

Fig. 2.4 Spectral density of quantization noise power for: (a) Nyquist-rate and (b) oversampling converter

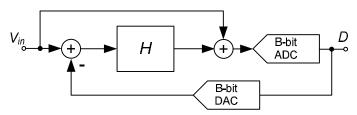

Two main types of oversampling converters are delta ( $\Delta$ ) and  $\Sigma\Delta$  modulators. A  $\Delta$  modulator has the disadvantage of amplifying the nonlinear DAC distortion in the signal band. The  $\Sigma\Delta M$ , which has a loop filter in a forward path (instead of feedback path, like in case of a  $\Delta$ modulator) avoids this shortcoming [4, ch. 1]. This modulator, shown in Fig. 2.5a, contains an internal ADC, a DAC and a loop filter (here, an integrator). Fig. 2.5b depicts a linear sampleddata system with a quantizer represented by a linear, additive white noise model.

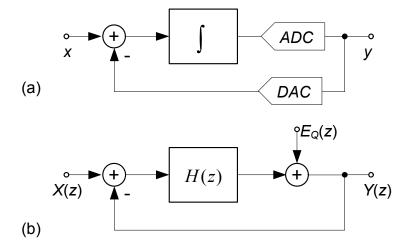

Fig. 2.5 (a)  $\Sigma \Delta M$  ADC and (b) its linear z-domain model.

The Z-domain output of the above system (having two independent inputs) can be represented by:

$$Y(z) = X(z) \cdot \text{STF}(z) + E_q(z) \cdot \text{NTF}(z)$$

(2.4)

where X(z) and  $E_Q(z)$  are the Z-transforms of x and  $e_Q$  respectively, and STF(z) and NTF(z) are the signal- and noise transfer functions, respectively given by:

$$STF(z) = \frac{H(z)}{1 + H(z)}; \quad NTF(z) = \frac{1}{1 + H(z)}$$

(2.5)

In general, if in signal band H(z) has a high gain, resulting in STF(z) being close to one and very small NTF(z) (the zeros of the NTF(z) are the equal to poles of H(z)). This means that, the input signal is largely unaffected, whereas the quantization noise is strongly attenuated. In the ideal situation, the quantization noise would be completely cancelled for a DC signal (if  $H(z=1) \rightarrow \infty$ ). The NTF(z), in the ideal case, can be defined as:

$$NTF(z) = (1 - z^{-1})^L$$

(2.6)

where *L* denotes the filter order,  $P_Q$  can be recalculated as (assuming that  $z=e^{j2\pi/F_s}$ , OSR>>1 and that the quantization error can be modeled as an additive white noise source):

$$P_{Q} \equiv \int_{-\text{BW}}^{\text{BW}} \frac{\Delta^{2}}{12 \cdot F_{S}} \left| \text{NTF}(f) \right|^{2} df \simeq \frac{\Delta^{2}}{12} \cdot \frac{\pi^{2L}}{(2 \cdot L + 1) \cdot \text{OSR}^{2 \cdot L + 1}}$$

(2.7)

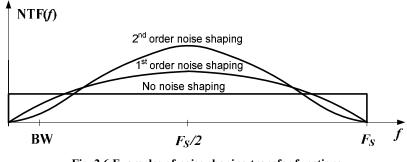

One can notice that, in the case of noise shaping, doubling the OSR decreases the  $P_Q$  by 6L dB more than in case of using just oversampling (which is 3 dB - (2.3)). Fig. 2.6, illustrates the general noise shaping curves for different NTFs, and it confirms this conclusion. Noise shaping causes less in-band ( $f_0$ ) noise than in case of a Nyquist-rate converter.

Fig. 2.6 Examples of noise shaping transfer functions

A  $\Sigma\Delta M$  converter incorporates, both, oversampling and quantization noise shaping, which allow improving performance of an ADC. These two operations allow relaxing the complexity of the analog circuitry. The anti-aliasing filter does not need sharp transition band and the quantizer resolution can be lower than in the case of Nyquist-rate converter. The price to pay for these improvements is mainly the required faster system operation for the same signal bandwidth and additional digital circuitry for the output filter. As mentioned before, the noise filtering "pushes" the quantization noise to higher than signal bandwidth frequencies. This noise power has to be strongly attenuated by employing a digital low-pass filter after the ADC. After digital filtering, the signal is usually downsampled to Nyquist rate without affecting the signal-to-noise ratio. The operation of filtering and downsampling is known as decimation.

#### 2.2. Performance Metrics

The accuracy of  $\Sigma\Delta M$  converters is degraded by their internal thermal noise (inherent to the circuit) and by their quantization noise (generated during the modulation process). The performance of a  $\Sigma\Delta M$  is evaluated by metrics, which are described below.

The signal-to-noise ratio (SNR) is the ratio of the output signal power at the frequency of an input sinusoid (with amplitude A) to the in-band noise power. For simplicity reasons, in the expression below, the quantization noise power  $P_Q$  is considered.

$$SNR = \frac{A^2}{2P_o}$$

(2.8)

The dynamic range (DR) is the ratio of the output signal power at the frequency of an input sinusoid (with maximum amplitude  $A_{MAX}$ ) to the output power for a small input for which one has SNR = 0 dB.

$$DR = \frac{A_{MAX}^{2}}{2P_{Q}}$$

(2.9)

Taking into consideration (2.7) the ideal DR is expressed as:

$$DR|_{dB} = 10 \cdot \log \left[ \frac{3 \cdot (2^{B} - 1)^{2} \cdot (2 \cdot L + 1) \cdot OSR^{2 \cdot L + 1}}{2 \cdot \pi^{2 \cdot L}} \right]$$

(2.10)

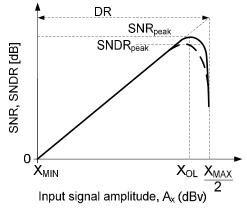

In order to take into consideration the aforementioned noises and distortions affecting the output signal, the signal-to-noise-plus-distortion ratio (SNDR) is used. A typical graph of the SNDR, of the SNR and of the DR is illustrated in Fig. 2.7. The values  $SNR_{peak}$  and  $SNDR_{peak}$  refer to the maximum values of SNR and SNDR. One can notice that, the SNR increases with  $A_X$  until  $A_X$  reaches the overload value  $X_{OL}$ . Beyond this level the quantizer often starts to be overloaded and, hence the SNR curve drops abruptly. The  $SNDR_{peak}$  value is lower than  $SNR_{peak}$  because the distortion is taken into consideration.

Fig. 2.7 Basic performance metrics: SNR, SNDR, DR

The effective-number-of-bits (ENOB) of  $\Sigma \Delta M$  is given by the equation:

$$\mathrm{ENOB}|_{bits} \approx \frac{\mathrm{SNDR}_{peak} - 1.76}{6.02}$$

(2.11)

In order to compare different modulator circuits and classify them, several figure of merits (FoM) can be defined. The Walden FoM (FoM<sub>w</sub>) takes into consideration the main specification metrics like: ENOB, signal bandwidth, and power consumption of a given  $\Sigma\Delta M$  [31]. The smaller the FoM<sub>w</sub>, a given ADC can achieve, the better is its energy efficiency.

$$\operatorname{FoM}_{W}|_{\mathfrak{G}J/conv-step} = \frac{P_{C}}{2^{\operatorname{ENOB}} \cdot 2 \cdot \operatorname{BW}} \cdot 10^{15}$$

(2.12)

Another well-known FoM used to rank circuits is the Schreier  $FoM_s$ . In this case, better circuits (i.e. more energy efficient) reach larger  $FoM_s$ .

$$\operatorname{FoM}_{S}|_{dB} = \mathrm{DR} + 10\log\left(\frac{\mathrm{BW}}{P_{C}}\right)$$

(2.13)

#### **2.3.** Basic Architectures of $\Sigma \Delta Ms$

$\Sigma\Delta M$  architectures can be mainly classified into few different categories:

- Discrete-time, continuous-time and hybrid continuous-time/discrete-time modulators (category classified according to type of loop filter);

- Single-bit/multi-bit modulators (category classified according to number of bits of the internal quantizer);

- Single-loop and cascade multistage noise-shaping (MASH) modulators (category classified according to the number of quantizers used in a complete modulator).

Moreover,  $\Sigma\Delta Ms$  can also be categorized according to input signal bandwidth being processed, resulting in low-pass and band-pass  $\Sigma\Delta Ms$ .

#### **2.3.1.** Low-Pass Single-Loop $\Sigma \Delta M$

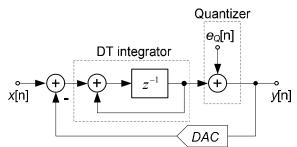

The first presented architecture of the considered modulators is first order discrete-time  $\Sigma\Delta M$ , illustrated in Fig. 2.8.

Fig. 2.8 Example of a  $1^{st}$ -order discrete-time  $\Sigma \Delta M$

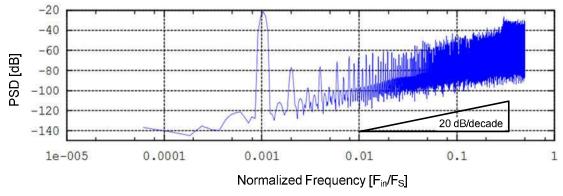

The loop filter is a discrete-time integrator, whose Z transfer function given by  $H(z) = z^{-1}/(1-z^{-1})$ , results in STF(z) =  $z^{-1}$  and NTF(z) =  $1-z^{-1}$ . The 1<sup>st</sup>-order  $\Sigma\Delta M$  shapes quantization noise with 20 dB/decade slope (Fig. 2.9).

Fig. 2.9 Example of spectral density of the 1<sup>st</sup>-order  $\Sigma \Delta M$  output signal power

An example of the output spectrum of the 1<sup>st</sup>-order  $\Sigma\Delta M$  is shown in Fig. 2.9. A disadvantage of the 1<sup>st</sup>-order  $\Sigma\Delta M$  is the quantization error power that is not uniformly distributed over the

entire spectrum and it contains strong tone distortion components. The reason is that the quantization error is strongly correlated with input signal, which leads to a colored quantization error instead of white noise and it raises and accumulates the in-band error power. The second disadvantage of this type of modulator is that doubling the OSR theoretically only improves SNR by 9 dB (1.5 bit) (in reality this assumption is often not accurate because of the above mentioned correlation between input signal and quantization error). This is because,  $1^{st}$ -order  $\Sigma\Delta M$  requires large OSR for accurate A/D data conversion. In practice  $1^{st}$ -order  $\Sigma\Delta M$  are not widely used [28].

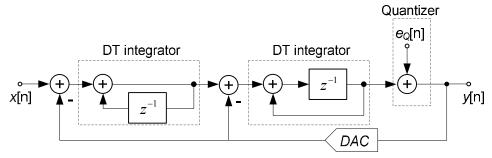

The problems described above can be mostly avoided by adding to the previous system one additional integrator and an extra feedback branch, which translates in using a second-order modulator (Fig. 2.10).

In this case  $\text{STF}(z) = z^{-1}$  and  $\text{NTF}(z) = (1 - z^{-1})^2$ . The 2<sup>nd</sup>-order  $\Sigma \Delta M$  shapes the quantization noise with 40 dB/decade slope. It provides additional in-band quantization noise suppression and it amplifies more efficiently the noise outside the signal bandwidth. Moreover the use of two integrators also helps to decorrelate the quantization error from input signal (less idle tones in output spectrum). The SNR of a 2<sup>nd</sup>-order  $\Sigma \Delta M$  improves by 15 dB (2.5 bits) each time the OSR is doubled.

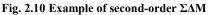

By adding more integrators and feedback branches, higher order modulators can be created. Their  $NTF(z) = (1-z^{-1})^L$  and the quantization noise is shaped with  $20 \cdot L$  dB/decade. Fig. 2.11 shows the theoretical relationship between the order of the  $\Sigma\Delta$  modulator versus the OSR value that allows achieving a particular SNR.

Doubling the OSR improves the SNR by 6L+3 dB (L+0.5 bit) and it results in less in-band noise and extra noise pushed into higher frequencies. However, in reality it is hard to achieve the theoretical performance because of some limitations of higher order structures. The main difficulty is that a high order  $\Sigma\Delta M$  is only conditionally stable when single-bit quantizer is utilized. The stability can depend either on precise circuit coefficient matching or limited range of input signal amplitudes. In particular, large input amplitudes can cause instability of the modulator, which may never return to stability, even when the input signal decreases [30, p. 556].

Fig. 2.11 Theoretical SNR vs. OSR and modulator order [32].

#### **2.3.2.** Discrete-Time and Continuous-Time $\Sigma \Delta M$

The previously presented low-pass structures are discrete-time  $\Sigma\Delta Ms$ . The conceptual diagram of a discrete-time modulator is illustrated in Fig. 2.12a. Usually, it is necessary that the modulator is preceded by an anti-aliasing filter. The filtered input is sampled and held by the S/H block and then made available to remaining part of the completely discrete-time modulator. It should be mentioned that in a switched-capacitor (SC) implementation the S/H block is not required because the switched-capacitor integrators already perform, inherently, the sampling operation.

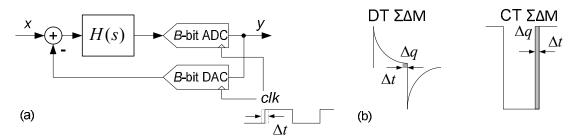

Fig. 2.12 (a) Discrete-time and (b) continuous-time modulators

The block diagram of a continuous-time modulator is depicted in Fig. 2.12b, using a continuous-time integrator while the rest of the circuit operates in the discrete-time domain. Therefore, the output signal of a continuous-time  $\Sigma\Delta M$  is discrete-time. One can notice that, the sampling operation occurs at the output of the loop filter. This node is less sensitive than input of the modulator and, moreover, it is already in a shaping loop of the  $\Sigma\Delta M$ . This is because the S/H imperfections and the wideband noise folding do not affect the circuit as much as in the

case of discrete-time  $\Sigma\Delta M$ . In this architecture the anti-aliasing filter usually is not required because both, sampling and quantization, occur at the same point in the loop [4, ch. 6.6.2]. Since quantization is usually modeled as addition of noise, the sampling can be regarded as addition of aliases. Therefore, the alias signals are usually attenuated by the same amount as the quantization noise.

Continuous-time  $\Sigma\Delta Ms$  allow designers using two to four times larger  $F_S$  and consequently achieve larger signal bandwidth than switched-capacitor discrete-time modulators. In the former ones,  $F_S$  is limited by the quantizer regeneration time and by the update rate of the feedback DAC, while in the latter ones,  $F_S$  is limited by settling requirements of operational amplifier (op-amp) to about 20% of its unity gain frequency [4, p. 206].

Despite of the previously mentioned advantages of the continuous-time  $\Sigma\Delta M$  architecture, it should be mentioned that the continuous-time signals have to be processed with high linearity and, on the other hand, that the system is sensitive to DAC memory effects [33, p. 297]. Moreover a continuous-time  $\Sigma\Delta M$  is more sensitive to the clock jitter noise than its discrete-time counterpart. This noise affects mainly the S/H and DAC, blocks working with discrete-time signals (Fig. 2.13a). The jitter noise is not critical for the S/H because, as mentioned before, in continuous-time architecture the errors added by the S/H are attenuated, in band, by the noise shaping. However, in the DAC, the jitter error is introduced at the input of the  $\Sigma\Delta M$  without any attenuation. Fig. 2.13b shows that in a switched-capacitor implementation, because of the complete settling of the charge in the capacitor, the charge loss caused by jitter is relatively small. In the case of the continuous-time circuit the rate of charge transferred during the whole period is constant. This means that, the charge loss due to jitter is, in this situation, more significant.

Fig. 2.13 Clock jitter effect in CT ΣΔM (a) main error sources (b) DT vs. CT waveforms of feedback DAC

Another important issue is related with the time delay in the response of the quantizer and DAC, which results in a delay in the  $\Sigma\Delta M$  loop filter response. This delay is called excess-loop-delay and usually it is a fraction of a sampling period, which can introduce additional poles, thus increasing the STF and NTF orders. This often leads to worse performance or even to an unstable behavior of continuous-time  $\Sigma\Delta Ms$ .

Because of these reasons, although continuous-time  $\Sigma\Delta Ms$  can achieve wide signal bandwidth, its linearity and accuracy is often reduced and compromised in comparison with discrete-time modulators.

#### **2.3.3.** Single-bit and Multi-bit $\Sigma \Delta M$

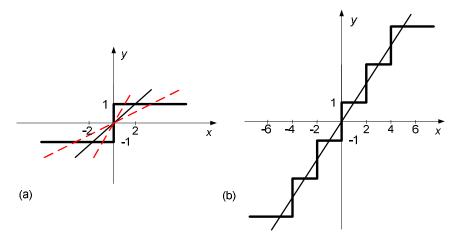

Depending on the number of bits of the quantizer used in the  $\Sigma\Delta M$ , one can distinguish between single-bit and multi-bit modulators. Usage of *B*-bit quantizer implies that the *B*-bit DAC is used in the feedback path of the converter. The examples of quantization characteristics of single-and multi-bit quantizers are illustrated in Fig. 2.14.

Fig. 2.14 Quantization characteristics of (a) single-bit and (b) multi-bit quantizers.

The output signal of the internal DAC is directly fed back into the  $\Sigma\Delta M$  input. Its non-linearity can be represented as an error source that adds directly to the input and which cannot be attenuated by the noise shaping loop of modulator. Therefore, the DAC linearity strongly influences the overall linearity of the  $\Sigma\Delta M$ , resulting in using single-bit quantizer (comparator) and a corresponding 1-bit DAC, which is inherently linear (there are only two output levels defining a straight line between two points  $\pm V_{ref}$ ) and it does not require neither trimming, calibration nor other precision component matching [30, p. 537]. On the other hand, the gain of the single-bit quantizer cannot be easily determined because it depends on its input signal amplitude as illustrated by the red dashed lines in Fig. 2.14a. When the input signal amplitude decreases, the gain increases and vice versa. This means that, a single-bit  $\Sigma\Delta M$  has to remain stable over a wide range of loop gains and that the maximum input signal amplitude is reduced as well as the achievable SNR [4, p. 15].

By using a single-bit  $\Sigma\Delta M$  with a large enough OSR, it is possible to achieve a high overall resolution. However, the multi-bit architecture has the advantage of improving the modulator's SNR by 6 dB per each bit added to the quantizer. This means that, by using a multi-bit  $\Sigma\Delta M$ , the target performance can be achieved with lower  $F_s$ , which helps to decrease the power consumption of the whole circuit. The gain of the multi-bit quantizer is well defined which can be noticed in Fig. 2.14b. The behavior of a multi-bit  $\Sigma\Delta M$  can be quite closely modeled by its linearized model. Consequently, the system stability can be more accurately predicted for the given range of input signals than the stability of a single-bit  $\Sigma\Delta M$ . Moreover this architecture reveals less tone problems in 1<sup>st</sup> and 2<sup>nd</sup>-order modulators than single-bit [28]. Although multi-bit architectures theoretically allow improving the performance of the modulator, the DAC nonlinearity problems can cause harmonic distortions and increase baseband noise because of inter-modulation of high frequency noise.

As mentioned before,  $\Sigma\Delta M$ 's linearity strongly depends on the linearity of the DAC. The components' mismatch in the multi-bit DAC causes, that its input-output characteristic becomes non-linear, which degrades the overall  $\Sigma\Delta M$  performance. In order to reduce the distortion added by the mismatch errors, dynamic element matching techniques are often used [4, ch. 6.4].

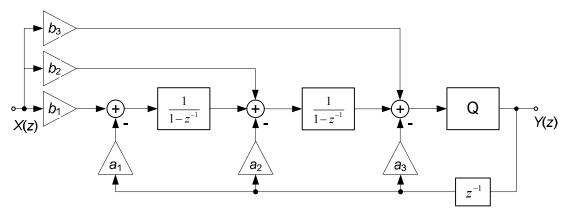

#### 2.3.4. Multi Feedback and Multi Feed-Forward $\Sigma \Delta M$