AMES/GRANT

# COMPUTER SYSTEMS LABORATORY

STANFORD UNIVERSITY · STANFORD, CA 94305-2192

**Design of Testbed and Emulation Tools**

S. F. Lundstrom and M. J. Flynn

**Technical Report: CSL-86-309**

## September 1986

(NASA-CR-180016) DESIGN OF TESTBED AND N87-14002 EMULATION TOOLS (Stanford Univ.) 86 p CSCL 09B

> Unclas G3/60 43951

1N-60 46595

This research was sponsored by the NASA-Ames Research Center under contract NAG2-248. The continuing participation of Dr. Lundstrom was supported by MCC (Microelectronics and Computer Technology Corporation).

# **Design of Testbed and Emulation Tools**

by

S. F. Lundstrom and M. J. Flynn Technical Report CSL-86-309 September 1986

Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford, California 94305-4055

### Abstract

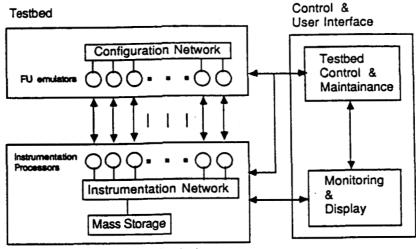

The research summarized in this report was concerned with the design of testbed and emulation tools suitable to assist in projecting, with reasonable accuracy, the expected performance of highly concurrent computing systems on large, complete applications. Such testbed and emulation tools are intended for the eventual use of those exploring new concurrent system architectures and organizations, either as users or as designers of such systems. While a range of alternatives was considered, a software-based set of hierarchical tools was chosen to provide maximum flexibility, to ease in moving to new computers as technology improves and to take advantage of the inherent reliabiliity and availability of commercially available computing systems.

### Key Words and Phrases:

Application Representation, Concurrent Systems, Emulation Tool, Graph Mapping, Interconnection Network, Intermediate Level Analysis, Performance Modeling, Performance Projection, Petri Net, Queueing Network Model, Simulation, Taxonomy, Testbed. Copyright © 1986 by S. F. Lundstrom and M. J. Flynn

### 1 Introduction

Highly concurrent systems are expected to make a key contribution to the future of highspeed computation, both for numeric and non-numeric applications. Unfortunately, only a few highly concurrent systems exist and very few actual applications have been developed to run on such systems. Operating systems, languages, compilers and associated run-time environments are not yet mature. Therefore, those who are developing future systems and those who expect to be major users of future highly concurrent systems, have no experience with which to make reasonable projections of the expected performance and efficiency of real applications on proposed new concurrent system organizations. The research reported here, the design of testbed and emulation tools, is part of a larger project whose longterm objective is to project, with reasonable accuracy, the expected performance of highly concurrent computing systems on large, complete applications.

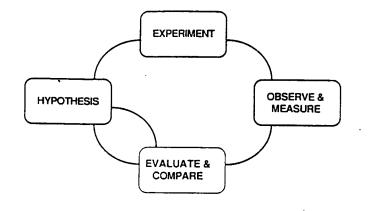

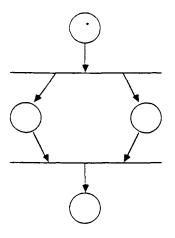

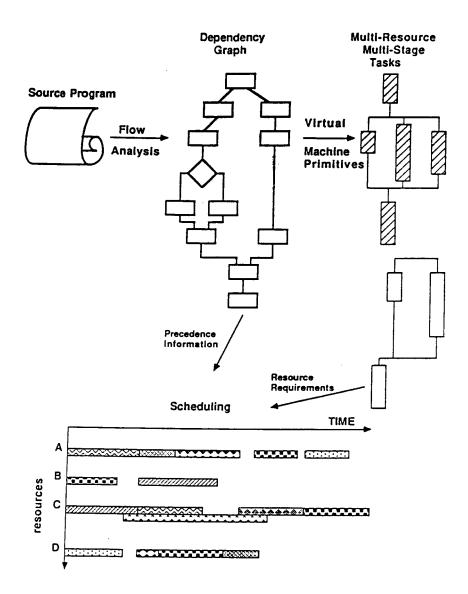

For those interested in the research and development of future, highly concurrent systems, the challenge is especially difficult. The discipline of the normal research cycle (see Figure 1), is to begin with a hypothesis, and then design and conduct an appropriate experiment. The researcher would then observe and measure the results of the experiment. Finally, the experimental results would be evaluated and compared to the hypothesis before starting the cycle over again. However, existing techniques to study the projected performance of large, complex applications on future, highly concurrent systems are tedious, extremely time consuming and inadequate. Consider two important factors, the time to prepare an experiment and the time to perform that experiment.

In computing systems, studies can be performed across a spectrum ranging from one extreme of detailed instruction-level simulation to another extreme of 'cut & try' where the whole system would actually be implemented. Simulation approaches are often chosen in order to reduce the time to evaluation of an experiment. However, as explained in Section 2, such simulations can be as much as six orders of magnitude slower than the actual system being studied. Therefore, some other approach is needed in order to understand the projected performance of concurrent systems.

The performance of an application on a concurrent system is dependent on many factors including

- the structure of the application,

- the language and compiler,

- the run-time environment,

- the operating system, and

- the concurrent computer system itself.

In order to develop a new approach to study of highly concurrent systems, this study first considered how each of these factors might impact the design of testbed and emulation tools. We then began the process which would lead to the design of a set of testbed and emulation tools. This report describes the research approach, the requirements for such a testbed, and the design approach chosen.

### 2 Research Approach

When considering how to approach the performance projection of complex applications on highly concurrent systems, a number of alternatives can be considered:

• Build System and Try It

This approach would have the highest fidelity in projecting performance since one would really know what would happen without any approximations. At the time of this study, this approach seemed most appropriate to the study of one particular system when considerable time and expense are already involved in the implementation of the system. This approach is of no help to those who are in the process of designing their system.

• Detailed Simulation

The detailed simulation of a system is often proposed for two reasons:

- speed of implementation

- flexibility in making changes

However, consider an example where the new system being studied must execute programs two orders of magnitude (100x) faster than the performance of existing machines. In addition, assume that the memory capacity of the projected new machines are larger than existing systems. In this case, three multiplicative factors contribute to the usage cost of detailed simulation:

- existing machine—100x slower than planned machine

- simulation overhead—# simulation instructions 100x more than the number of native instructions of the new machine during execution

- memory system—existing system must emulate new memory, using bulk memory techniques resulting in a 100x slow-down just from this factor.

The result is that simulation speed will be  $10^6$  times slower than the projected performance of the actual system. In other words, a job which would take one hour on the new system, would consume one million hours of simulation time (in excess of 117 years).

#### • Simulate Inner Loops

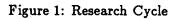

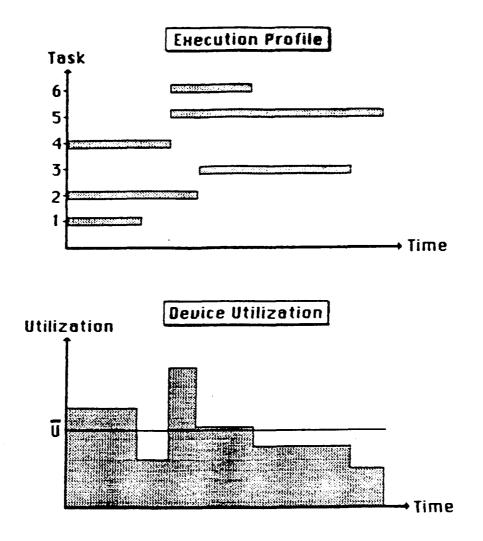

Because of the amount of time required to simulate an entire application, separate study of the computationally expensive inner loops would seem to be a reasonable approach. However, if 95% of an application executes at full speed, say at 1.00 GFLOP, and if the remaining 5% executes at 10 MFLOP, then the overall effective rate of execution is only 170 MFLOP (0.17 GFLOP), a significant reduction. Study of inner loops will help understand the effectiveness of the utilization of the concurrent system during the execution of the loops. Projection of the overall performance of an application based on study of inner loops alone can lead to optimistic performance estimates. For example, in Figure 2, the overall performance of a multiprocessor (with varying numbers of 10 MFLOP processors) is shown as a function of FS, the fraction of code executed in serial. Note that even when the 'non-kernel' code is less than 1%, the system is unable to utilize the potential cycles (FS=0).

• Develop a Mathematical Approximation

The time required for execution of an application is directly related to the slowest part of the system (the system bottleneck) for a particular application. In practice, the bottleneck may change from time to time during execution of an application (such as a channel, main memory access, and Arithmetic and Logic Unit). A mathematical expression could be written which is a function of the peak performance of these bottleneck units and of a set of parameters which are applications based. Unfortunately, the development of such a formula is not straight-forward and either would need to be verified with another method, or, more likely, might be developed on the basis of previous simulation tests.

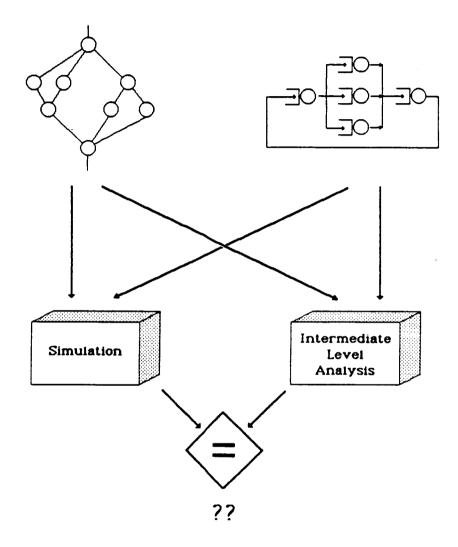

• Integrated Hierarchy of Models and Tools

The most cost effective approach to projecting the performance of highly concurrent systems seems to be a hierarchy of models and tools. In such a hierarchy, the majority of the work can be accomplished at more general levels of models. Parameters at the general levels can then be verified through use of more detailed models and tools, but without requiring execution of all of an application at the most detailed level.

Because the tools of interest in this study are intended to support the performance projection of complex applications on concurrent computer systems, this study first spent some time becoming familiar with the environment in which the tools might be used and with the process by which applications come to be executed on concurrent computer systems. These preliminary efforts led to an understanding of requirements which were then used in approaching the design of the testbed and emulation tools.

Figure 2: Available Computational Power as a Function of Serial Fraction in Code

4

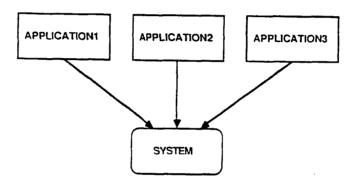

Figure 3: Best Target for Application

Figure 4: Application Challenges for a System

### **3** Requirements

### 3.1 Expected Usage

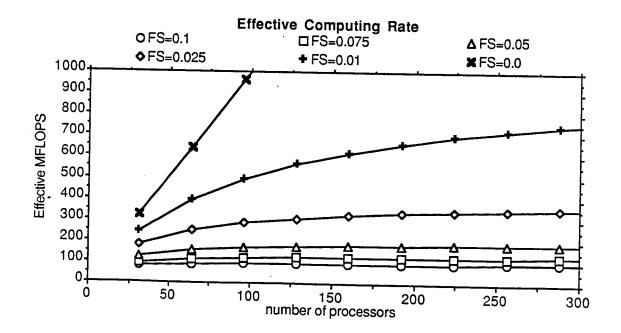

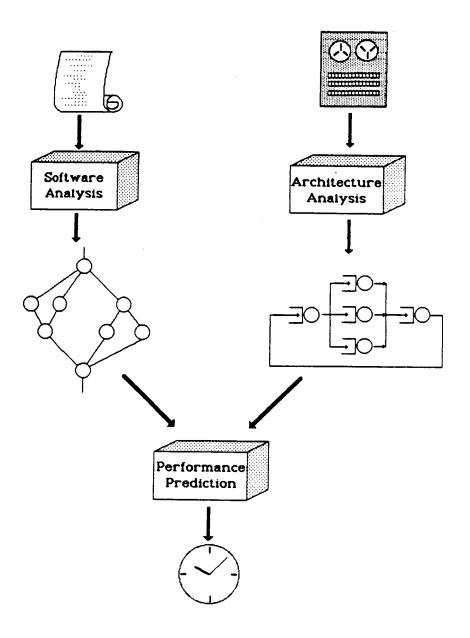

The testbed and emulation tools are expected to attract two basic types of users; those interested in determining which of a number of concurrent systems would be most effective in executing a particular application of interest (Figure 3), and those interested in determining how well various applications would execute on a particular concurrent system (Figure 4).

This research was concerned with applications as defined by a high-level language source code. Emphasis was placed on FORTRAN because of its common usage in applications already making significant use of parallel computational resources. A framework was established for understanding the application heritage of the source code representations.

The systems considered were those best described as concurrent processors. That is, those systems which might be classified as MIMD (Multiple-Instruction, Multiple-Data)

5

stream systems. SIMD systems, such as vector or pipelined computers, were not considered.

### **3.2 Accuracy of Results**

Since no capabilities to project performance of complex applications existed at the time of this work, the establishment of any bounds on a performance estimate would be a significant step forward. The accuracy of a performance estimate is a complex function of the ability to accurately estimate application needs (itself a function of input data in most cases), of the process of mapping the application onto the system through compilers, linkers, and loaders, of the management of the concurrent system by the operating system, and of the underlying concurrent system itself. Because of these complexities, our objective in making performance projections is to understand something about the accuracy of the projection. Definite bounds would be desirable, but estimates presented as probability distribution functions would also be useful.

### **3.3** Integrated Hierarchy of Tools

As mentioned in an earlier section, the time required to do a complete instruction-level simulation of a large, complex application can easily be more than six orders of magnitude slower than the time required by the real system, if it were available. While this level of detail would clearly give the most accurate results, if feasible, the testbed and emulation tools were considered at a number of levels of detail. High-level, general system functional models will be capable of full application/system models. By themselves, high-level models will necessarily have limited accuracy. More detailed model levels can be used judiciously in order to balance the benefit of the use of the detailed models with the time demands on the modeling resources. Selected questions raised at the system model level can be studied in more detail in lower level models in an integrated hierarchy of models.

### **3.4** Level of Detail Expected

As mentioned earlier, this testbed and emulation tool design project is part of a long-term research program to learn how to project the performance of complex applications on highly concurrent machines. The long-term project expects to either:

- make a performance projection within some known bounds, or

- estimate performance with a probability distribution function

Because of the emphasis on performance projection of a whole application, the focus of this design project is to provide tools to study those portions of a system which have the most significant effects on performance. Specific details of application execution are generally not needed in order to meet the overall objectives.

### 4 Background Studies

Before the design of the testbed and emulation tools could be considered, a review of available technology and of possible general approaches to the design was conducted. The technologies reviewed included existing tools, specialized hardware, and software. The process involved in application execution was reviewed in order to better understand the relationships between different levels of implementation.

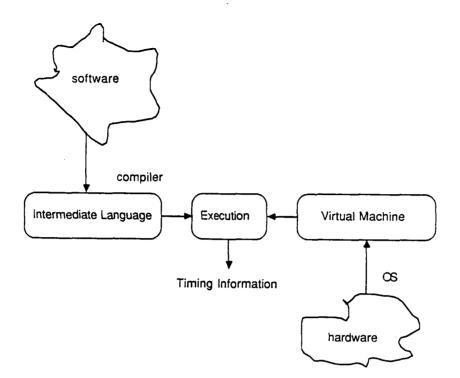

### 4.1 Application Execution Process

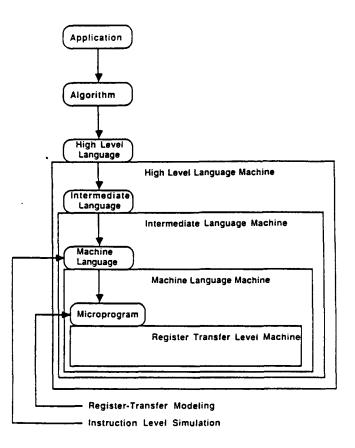

Before an application can be executed, it must progress successfully through a number of stages of development, some of which are automated, until a representation of the application exists in a form which can be executed on the system. As an application passes from one level to the next during development, more and more information needed for execution is bound to the application description. If this application mapping process is clearly understood, then the testbed and emulation tools may be able to work at more general, less constrained levels with known relationships to actual execution environments. Figure 5 shows the various level of detail, which are involved in the application development and execution process.

Consider the process of mapping the application onto an execution environment first. The initial approach to a problem is usually to describe it in English. A system analyst then studies the problem and designs an algorithm to solve the problem. A programmer codes the algorithm into some high level language. From this point on, most of the mapping process is automated, first through the use of a compiler which compiles the high level language into an intermediate language. Code optimization typically takes place at this level. The intermediate language code is then translated, by the code generators, to the machine code. The machine code is usually interpreted by a microprogram stored in the control store of the host machine.

Similarly, hardware can be represented by many levels of abstraction. At the most detailed level, the hardware can be defined in terms of register transfers and basic machine instructions. That hardware, together with the microcode stored in its control memory, is a virtual machine which executes assembly language code instructions. That assembly code virtual machine, together with the operating system which manages I/O operations, memory management, and process scheduling, is an intermediate language virtual machine. The intermediate language virtual machine hides a lot of specific details unique to the basic hardware machine. At the highest level, the algorithm designer assumes the existence of a

Figure 5: Levels of Application Implementation Detail

high-level language virtual machine which includes the capabilities of optimization of the original high-level language.

The execution of software on some hardware can be modeled at any of these various levels. At the lowest level, the behavior of the registers and basic functional components while executing the microprograms of the underlying machine could be simulated. This level would, obviously, provide the most detailed information. Simulation at the next more general level, known as instruction level simulation, is not concerned with all the details of data movements between registers. The execution model has been abstracted such that the underlying details are hidden and the results of the underlying details are represented in (sometimes an approximate way) the timing characteristics of the machine-language instruction set being simulated.

In a similar manner, intermediate language or high-level language interpretation can be considered. These execution models must also represent the effects of operating system functions, run-time environments, compiler optimization, and many more details. These more general forms of computational models do not require as much computational effort

8

to get results, but they hide a significant amount of information about the detailed execution process.

If modeling and emulation tools are available at each of the levels of this hierarchy, execution assumptions at one level can be validated at the next. For example, a floating point ADD instruction can be simulated in detail at the lowest level to determine the instruction execution time. This timing information can then be used by, higher levels in the hierarchy of tools.

Maintenance of the consistency of information (such as instruction timing) between various levels is very important. Unfortunately, while some simple one-to-one relationships hold between levels in the hierarchy of models, many practical system effects require consideration of more complicated (sometimes nondeterministic) functions describe the relationships between information in models at different levels of abstraction. Operating systems, optimizing compilers, and variable delays in memory systems and interconnection networks are some of the complicating factors. Some of these effects will need to be represented as probability distribution functions at the higher levels in the hierarchy.

### 4.2 Application Representation and Mapping

One part of the execution process clearly involves mapping an application through the various levels of instantiation to whatever level is being used for performance analysis. In the background studies, two problems were encountered:

- the semantics of the various levels of application instantiation were ambiguous, and

- each level of application instantiation is represented, typically, by a different language.

When trying to discuss these issues, the lack of a clear definition for the various levels of abstraction became a problem. Without a clear definition for each level, the identification of any added constraints on the inherent parallelism of a problem as the problem was mapped from the original problem domain to the domain of an executable computer program became very difficult.

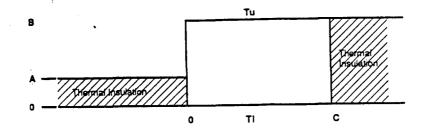

The following terminology was developed in order to describe the stages in the solution of a problem, from its original statement through creation of an executable algorithm. An example is used to demonstrate the use of this technology. The example is the determination of the temperature distribution of a conducting surface with various constant-temperature and insulation constraints.

• Problem Level 0 A problem level 0 specification is the highest-level specification of a problem. The PLO specification describes the problem, and contains the knowledge about the problem necessary for its solution.

#### Problem Level 0

What is the steady-state temperature distribution in the following conducting solid? The upper surfaces are maintained at temperature Tu, the lower surface at TI, and the sides are semi-insulated. (The physical differential equations are implicitly included at this level.

Figure 6: Problem Level 0

For the temperature distribution example (see Figure 6), a PLO specification would consist of a description of the conducting solid and its surfaces, and would pose the question as to what is the steady-state temperature distribution. The knowledge about the physical behavior of the system is included in the form of differential heat equations.

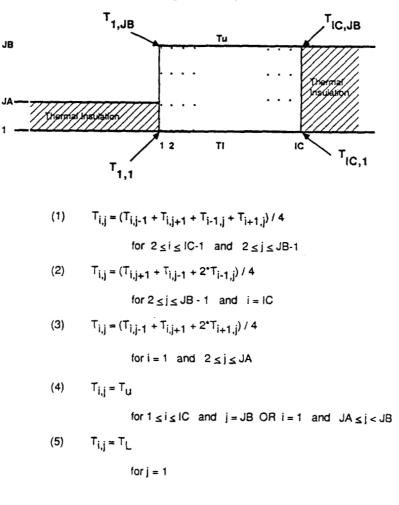

• Problem Level 1 A problem level 1 specification is complete enough that an algorithm could be generated from this specification without further knowledge of the problem. This PL1 specification introduces the model used in the solution, and thus is the first level where only an approximation to the actual problem may be found.

For the temperature distribution example, a problem level 1 specification describes the discrete form of the problem (see Figure 7). This discrete form includes the mesh, the boundary conditions, and the difference equations used at each point of the mesh.

• Problem Level 2 A problem level 2 specification of the problem includes the PL1 specification, but also includes algorithmic information. The algorithmic information specifies the execution of the model.

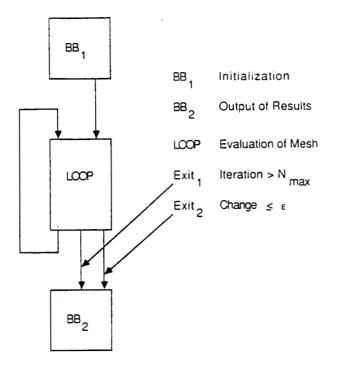

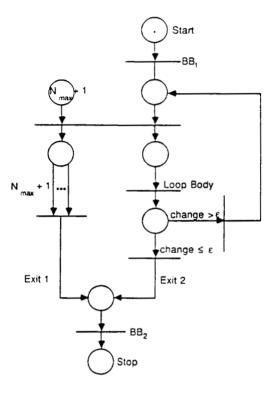

For the temperature distribution example (see Figure 8), this algorithmic information specifies the time-coincident, repetitive application of the difference equations over all points in the mesh, and the termination conditions.

• Algorithm Level 1 An algorithm level 1 specification is a representation of the algorithm to such detail that an execution of the representation would provide the algorithm's solution to the problem. The specification is unconstrained by factors not inherent in the PL2 specification, and represents the detailed algorithm at its most pure level. This AL1 specification is similar in content to the PL2 specification, but typically PL2 will be natural-language, and AL1 will be a more rigidly defined form

#### Problem Level 1

Divide the solid into an array of mesh points. The finite difference forms of the heat equation and boundary conditions relate the temperature at the mesh points for the given problem by the following relationships:

Figure 7: Problem Level 1

#### Problem Level 2

Over the mesh given in PL1, an initial temperature distribution is assigned and is then corrected by repetitive application of equations 1 through 5 from the PL1 description. The program is terminated when either the temperature at each point has been correct  $N_{max}$  times or when the absolute value of successive temperature changes is less than  $\varepsilon$  at every point.

For tests, use  $N_{max} = 60$ ,  $\varepsilon = 0.10$ , and 10 mesh points in each direction.

Figure 8: Problem Level 2

(e.g. Petri net, Holt diagram, etc.). The execution of any AL1 specification must be, by definition, equivalent to the execution of any other representation.

For the temperature distribution problem, an AL1 specification is a flow chart, or Holt diagram, or Petri net, etc., which specifies a precise execution of the algorithm, but does not constrain the algorithm (see Figure 9).

• Algorithm Level 2 An algorithm level 2 specification is a constrained AL1 specification. An AL2 specification has the same result potential as the AL1 specification, but may have artificially introduced constraints in either its representational method (e.g. FORTRAN), or its representational goals (e.g., coding for efficient execution on a specific machine).

For the temperature distribution example, the AL2 specification (see the example in Figure 10) is a FORTRAN, or Pascal, etc., program which has the same algorithmic features of the AL1 specification, but contains extra constraints such as the serialization of the calculations in a FORTRAN program.

The level descriptions above describe the transformation of a problem from its conception to its realization in an executable form. The definition of these levels was valuable in the analysis of where the application-related constraints occur. However, since the objective of the research was to proceed from high-level language source, further definition of these levels was not required at this time.

The relationships between the levels beginning with the high-level language level are important. Given an understanding of how an application maps through the various levels to the detailed register-transfer (RT) level, inverse mappings may be possible to relate performance parameters at higher levels to the RT level. Unfortunately, each of the levels, beginning with the high-level language level (Algorithm Level 2), are represented in different formal languages. These languages are so varied that important functional relationships between the levels are often obscured by differences in the notation used. As part of the Background Studies, alternative languages and other forms of representation were considered in order to determine whether a common form could be identified for use by all The following SASL program represents the algorithm.

temp 0 initial WHERE temp time T = time > Nmax -> T : [:(time=",time,%)] smallchange T T' -> T' : ["(time=",time+1,%)] temp (time + 1) T' WHERE T' = next Tsmallchange T1 T2 = all [(T1 i j - T2 i j) < epsilon; j <- 1..JB; i <- 1..IC] next T = [[f a b; b <- 1..JB]; a <- 1..IC] WHERE f i j = equation1 i j -> (T i (j-1) + T i (j+1) + T (i-1) j + T (i+1) j)/4 equation2 i j -> (T i (j+1) + T i (j-1) + 2 \* T (i-1) j)/4 equation3 i j -> (T i (j-1) + T i (j+1) + 2 \* T (l+1) j)/4 equation4 i j -> Tupper equation5 i j -> Tiower equation1 i j = 2 <= i and i <= (IC-1) and 2<= j and j <= (JB-1) equation2 i j = 2 <= j and j <= (JB-1) and i = IC equation3 | j = i = 1 and 2 <= j and j <= JB equation4 i j = 1 <= i and i <= IC and j = JB or i = 1 and JA <= j and j < JB equation 5 i j = j = 1Nmax = 60epsilon = 0.10IC = 10JB = 10Tupper = 100Tiower = 0initial = [[ 0,0,0,0,0,0,0,0,0],[ 0,0,0,0,0,0,0,0,0,0], 0,0,0,0,0,0,0,0,0,0], I 0,0,0,0,0,0,0,0,0,0], 0,0,0,0,0,0,0,0,0,0], 0,0,0,0,0,0,0,0,0,0,0], [ 0,0,0,0,0,0,0,0,0,0,0], [ 0,0,0,0,0,0,0,0,0,0,0], [ 0,0,0,0,0,0,0,0,0,0], [0,0,0,0,0,0,0,0,0,0]]

Figure 9: Algorithm Level 1 [in SASL]

13

| 5           | DIMENSION IT(10,10), R(10,10), T(10,10)<br>READ (5,10) TU,TL,IC,JB,EPS,N                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| 10          | FORMAT(1X,F5.2,1X,F5.2,1X,I2,1X,I2,1X,F4.3,1X,I2)<br>WRITE(6,11) TL, TU, IC, JB, EPS, N                                          |

| 11          | FORMAT(' TL=',F7.2,' TU=',F7.2,' IC=',I3,' JB=',I3,' EPS=',<br>1 F6.3,' N=',I3)<br>ICOL=JB/2<br>DO 100 I=1,IC<br>DO 100 J=1,ICOL |

| 10 <b>0</b> | T(I,J)=TL<br>CONTINUE<br>JA=ICOL+1<br>DO 101 1=1,IC<br>DO 101 J=JA,JB                                                            |

| 101         | T(I,J)=TU<br>CONTINE<br>DO 99 I=1,IC<br>DO 99 J=1,JB<br>R(I,J)=T(I,J)                                                            |

| 99<br>95    | CONTULE<br>FORMAT(',6F7.2)<br>DO 899 LOOP=1,N<br>ICE = IC-1<br>DO 140 I=1,ICE<br>J=1                                             |

|             | T(1,J)=TL<br>IF(1,EQ.1) GO TO 35<br>JBE=JB-1<br>DO 150 J=2,JBE                                                                   |

| 150         | T(I,J)=T(I,J-1)+T(I,J+1)+T(I-1,J)+T(I+1,J))/4<br>CONTINUE<br>T(I,JB)=TU<br>CO TO 40                                              |

| 35          | GO TO 140<br>DO 160 J=2, JA                                                                                                      |

| 160         | T(I,J)=(T(I,J-1)+T(I,JJ-1)+2*T(I+1,J))/4<br>CONTINUE<br>DO 165 J=JA,JB                                                           |

| 165         | T(I,J)=TU<br>CONTNUE                                                                                                             |

| 140         | CONTINUE                                                                                                                         |

|             | I=IC<br>J=1<br>T(I,J)=TL<br>DO 180 J=S,JA<br>T(I,J)=(T(I,J+1)+T(I,J-1)+2*T(I-1,J))/4                                             |

| 180         | CONTINUE<br>DO 199 I=1,IC<br>DO 199 J=1,JB                                                                                       |

| 199         | IF(ABS(T(I,J)-R(I,J)).GE.EPS) GO TO 77<br>CONTINE                                                                                |

| 77          | GO TO 900<br>DO 200 I=1,IC<br>DO 200 J=1,JB<br>R(1,J)=T(1,J)                                                                     |

| 200         | CONTINUE                                                                                                                         |

| 8 <b>99</b> | CONTINUE<br>WRITE(6,901)                                                                                                         |

| 901         | FORMAT( ***DID NOT EXIT ON THE EPSILON, ITERATION EXCEEDED****)                                                                  |

| 900         | CONTINUE<br>WRITE(6,902) LOOP                                                                                                    |

| 902         | FORMAT(' NÚMBER OF ITERATIONS TAKEN = ', 14)<br>DO 201 I=1,IC<br>DO 201 J=1,JB<br>IT(1,J)=T(I,J)*100+.5                          |

| 201         | T(I,J)=IT(I,J)/100.<br>CONTRUE                                                                                                   |

| 15          | WRITE(6,15)((T(1,J),I=1,IC),J=1,JB)<br>FORMAT(1X,6F7.2)<br>RETURN<br>BND                                                         |

Figure 10: Algorithm Level 2 [in FORTRAN]

14

ſ

Figure 11: A Simple Petri Net

levels in the hierarchy. Some of the alternatives considered as a common, level-independent representation form were:

- Petri Nets

- Role-Activity Diagrams

- SASL

3

Petri Nets are graphical representations of execution. A Petri Net has two types of nodes: *place* and *transition*. Edges in a Petri Net connect only nodes of opposite type. In Figure 11, the *places* are represented by circles and the *transitions* are represented by horizontal lines.

In addition, a notion of *activation* is used to understand the evaluation sequence in a Petri Net. When a *place* holds a value, a *token* is shown in the *place* (see top circle in the figure for example). When every input *place* of a *transition* has at least one token, the *transition* is *enabled to fire*. The process of *firing* a *transition*, removes a token from each input *place* and adds a token to each output *place* of the firing *transition*. Petri Nets are quite general and are a powerful notion in modeling parallel structures and asynchronous activities. However, they become quite complex when representing execution of a complicated application executing on a concurrent system.

Petri Nets can be analyzed with queueing models. In this case, a *transition* would represent a service station in the queueing model. A *place* would represent a queue. A token would represent a task. The number of tokens in a *place* would be the queue length. The *transition* firing time would be the service time in the queueing model.

Petri Nets could also be analyzed as a Markov process since the next state depends only on the previous state. Because of a property of conservation of tokens at a *place* within Petri

Figure 12: Pipelined Asynchronous Control Unit

Nets, notions such as bottleneck, peakload, max utilization, waiting time, queue length, etc. are straightforward to study.

Petri Nets show both control and data flow, and as such relate well to notions of simulation. The interpretation of token, transition, and place are flexible. In addition, Petri Nets themselves are hierarchical (as an example below demonstrates).

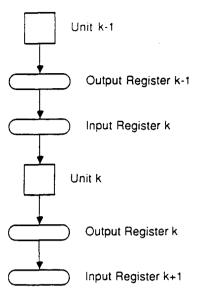

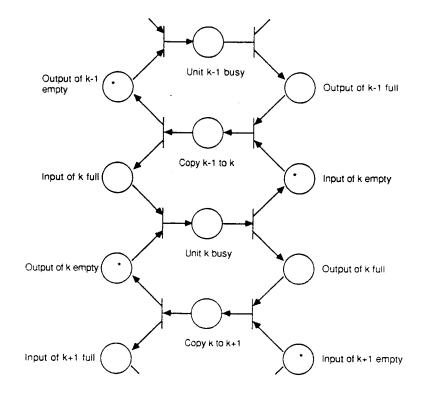

Hardware Modeling As an example, a simple asynchronous control unit for a pipelined computer could be represented by a Petri Net Model. Figure 12 shows the general organization of the hardware with various functional units, each of which has an input register and an output register. Figure 13 shows the corresponding Petri Net model of this asynchronous control unit. Notice the tokens residing simultaneously in various *places* in the net.

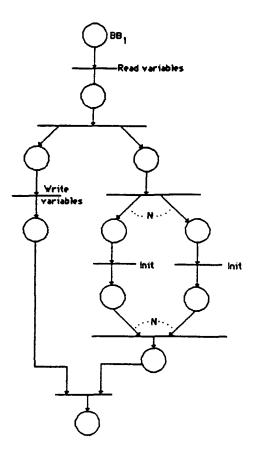

Software Modeling As a second example, consider the temperature distribution example given earlier. Recall that the overall problem was shown in Figure 6 and that a Fortran version of it was shown in Figure 10. Figure 14 shows the basic blocks in that Fortran program. Figure 15 shows the Petri Net representation of that program flow. In order to show more detail, a portion of the representation shown in Figure 15 is expanded in Figure 16, thus demonstrating the potential of hierarchy within this sort of a model.

Figure 13: Petri Net Model of Asynchronous Control Unit

Figure 14: Basic Blocks of Temperature Distribution Problem

### 4.2.1 Role-Activity Diagrams

Role-Activity diagrams are Petri nets which show the organization of systems. The method used was invented by Anatol Holt. Roles are sequences of activities in which actors participate when they are playing that role. An activity often requires a number of actors in their roles for its realization.

Any given role is played by, at most, one actor at a time, although different actors may play the role at different times. Also, an actor, playing a role, may participate in only one activity at a time. For an activity to occur, all roles associated with that activity must have actors taking part. Thus, each role associated with that activity is a resource necessary for the realization of that activity.

Role-Activity diagrams, represented as role-activity nets, are a method of specifying use of resources in a system. For computer algorithms, the resources compute the values in the solution of the problem. Thus, Role-Activity diagrams specify the interaction of values in the algorithm, as well as the interaction between resources.

A vertical strip in a Role-Activity diagram represents the succession of roles taken on by an actor (a resource) over time. Time is assumed to progress down the page. Activities requiring multiple actors are represented by horizontally-connected squares under each actor required. Figure 17 is an abbreviated directory which can be used to interpret the con-

Figure 15: Petri Net Model of Temperature Distribution Problem

Figure 16: Petri Net Expansion of BB<sub>1</sub>

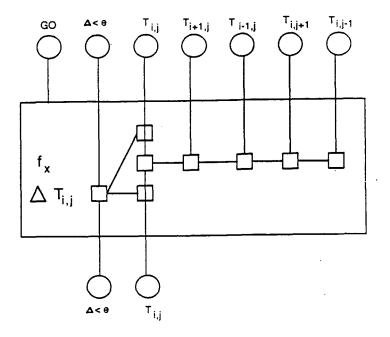

stituents of a Role-Activity diagram. Figure 18 shows a portion of a Role-Activity diagram. The figure shows the update of a cell within the temperature distribution problem.

Role-Activity diagrams are very general, although because of the explicit representation of time, they are more constrained than Petri Nets. The graph structure has few artificial restrictions. However, these diagrams are not a perfect representation for this project. Generalizations such as looping and recursion are not handled directly in Holt diagrams, and are often difficult to create and/or spot. Because the production of each value must be represented by one role, a program with a lot of values (such as large arrays) would take up a lot of diagram space. Not only is this kind of graph difficult to draw, it is also difficult to look at because of its large size. Large graphs are also tedious to change. Many problems, especially in simulation and modeling, have very regular characteristics. In these problems, the Role-Activity diagrams have similar regularity. We have identified the production of Role-Activity diagrams from a higher-level specification, the 'generative problem.' Some study of this has revealed some relatively simple extensions to Role-Activity

Vertical string as path of a role player. Circuits. Д Initialization and termination. Coincident activity of multiple role players. ☐ Invariance of value. Branching to alternative consumers. Steering. Merging from alternative producers. Ó · ↓ · ↓ Copying. ф - Saving an old value. Buffered communication.

Figure 17: Abbreviated Directory for Role-Activity Diagram Interpretation

Figure 18: Portion of Role-Activity Diagram—Temperature Distribution Problem

diagrams which provide the desired characteristics. A major advantage of Role-Activity diagrams for these applications is the ease and visibility with which artificial constraints, such as those imposed by certain compilers, or languages, may have been added to the AL1 representation. In addition, even constraints added by the machine (such as queueing at memory) can be easily represented with Role-Activity diagrams.

Role-Activity diagrams can easily represent the execution of a program on a concurrent system since the various system execution resources are the *actors* and the computations to be performed are *activities*. Communications between actors also are explicitly shown. However, these diagrams become quite complex when trying to represent dynamic resource allocation.

### 4.2.2 SASL Programs

SASL is a language developed by David Turner at the University of St. Andrews (hence SASL: St. Andrews Static Language). SASL is an applicative language, where the program is an expression consisting solely of the application of functions to arguments. Assignment is impossible; within a context, a variable's value never varies. Substitutions and reductions in the representation may occur, but the value stays the same. Parallelism in SASL is possible because there are no side effects (there is not assignment). So, 4+1 is always equal to 3+2 in SASL; the objects are different, but the value is the same. SASL's only data structures are lists, which may be arbitrarily complex. The elements of these lists need not be all of the same type. Lists may also be of infinite length, as long as all of the elements are not evaluated. For example,

ones = [1] ++ ones

is an infinite list of 1s.

A function is also a value in SASL, and all functions have only one argument. By a procedure known as Currying, a function of one argument returns a function which takes another argument, etc., so that many arguments can be used. For example,

PLUS 3 4 is really ((PLUS 3) 4),

where the function (PLUS 3) takes the argument 4.

Functions in SASL are non-strict. That is, they use lazy evaluation of their arguments so that a function can still have a defined value if not all of its arguments are defined.

SASL programs are expressively complete, but it is sometimes difficult to think of the proper way to express a concept such that no restriction of the AL1 parallelism occurs. Certain concepts cannot even be stated in SASL. For example, non-deterministic problems such as chaotic-relaxation algorithms cannot be represented. Some extension to SASL would have to be created in order to represent such a concept. Despite these drawbacks, SASL would probably be a good AL1 representation tool, especially if some form of state representation could be added. (The temperature distribution example given earlier used SASL in just this way—see Figure 9.) Problem representation in SASL is lucid and concise. However, there are no inherent means of inserting artificial constraints, so that un-adorned SASL cannot be used as a representation in the testbed at both AL1 and AL2 levels.

### 4.3 Survey of Concurrent Architectures

As part of the Background Study, the potential range of machines which might be studied with the planned Testbed and Emulation Tools was studied by surveying a wide range of existing machines. These machines can be characterized from different viewpoints:

- models of computation,

- interconnection network,

- processing element,

- memory system, and

- application

The purpose of this survey was to understand the breadth of each of these viewpoints, at least with current architectures.

### 4.3.1 Taxonomy of Concurrent Architectures

There are literally hundreds of concurrent architectures proposed and designed in the last decade. These architectures are so different that the usual classifications as SIMD and MIMD [Fly 72] machines are not sufficient.

New taxonomy schemes are developed by many researchers in order to catagorize these different architectures into different classes. One particular taxonomy as reported by Haynes and others in [HLS 82] divided the wide spectrum of concurrent architectures into six classes:

- 1. Multiple special-purpose functional units

- 2. Associative processors

- 3. Array processors

- 4. Data flow processors

- 5. Functional programming language processors

- 6. Multiple CPUs

Machines with multiple special-purpose functional units are usually designed to perform some specific tasks efficiently. One example is the systolic arrays which will be described in more detail in the next section. Computation intensive problems, in which the kernels are based on a number of basic mathematical operations, have found great success in these structures. Matrix multiplication, solution of linear systems, and FFT are some examples.

Associative processors are those machines which utilize an associative memory. In associative memory, one bit of any memory word is available on one access, thus it is possible to search the whole memory simultaneously for specified contents by iteration on bit slices. This organization also allows memory words to be addressed by their contents instead of their addresses. One example of associative processors that we will describe in the next section is STARAN designed and built by Goodyear Aerospace Corporation.

Array processors are machines with multiple arithmetic units operating in lockstep and performing the same operation on different data. This is the most common and popular type of concurrent architecture available on the market. They are particularly suitable to problems that involve a large proportion of array data types. Five examples will be studied in the next section: Illiac IV, BSP, MPP, CHiP, and NON-VON. Data flow computers are very different from the conventional von Neumann architectures in which a program counter is used to schedule the next instruction to be executed. An instruction in a data flow computer is ready for execution when its operands arrive. As a consequence of this data-activated property, a very high level of concurrency can be exploited. The Data Driven Signal Processor (DDSP) will be given as an example of this type of concurrent architecture.

Functional programming (FP) language machine or reduction machine has gained considerable interest recently. The main advantage of FP is that when algorithms are described in such applicative languages, much parallelism can occur automatically—with no analysis of program structure and without explicit programmer involvement with parallelism. SERFRE will be studied as an example in the next section.

Multiple processors belong to the class normally called MIMD. They are more flexible than the classes described above; however, their control is much more complex. The interconnection network, which connects the processors, usually forms a crucial part both in the design and operation of each machine.

Since the architectures in this class are so diverse that we are going to look at nine different machines in the next section: Cedar, FMP, S-1, Cm<sup>\*</sup>, HEP, Empress, MP/C, Ultra, and TRAC.

#### 4.3.2 Architectures Studied

In this section, we will describe 18 different machines, this is by no means a complete survey of all concurrent architectures, we are just trying to cover as wide a spectrum as possible. Using the taxonomy described in the previous section as a guideline, we have chosen machines that belong to these six different classes. Since array processors (SIMD) and multiple processors (MIMD) have received most attention, most machines that have been chosen belong to these two classes. In each subsection that follows, we will try to describe the most significant parts of each machine's architecture.

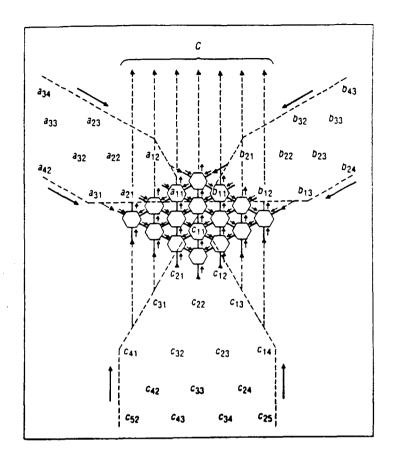

Systolic Array The systolic architectural concept [Kun 82] was developed by Kung and associates at Carnegie-Melon University, and is a general methodology for mapping highlevel computations into hardware structure. A systolic system consists of a set of interconnected cells, each capable of performing some simple operation. Information in a systolic system flows between cells in a pipelined fashion, and communication with the outside world occurs only at the boundary cells.

In Figure 19, the hex-connected systolic array can be used to multiply two N  $\times$  N band matrices of bandwidths W<sub>1</sub> and W<sub>2</sub>, each of which performs the inner product operation C  $\leftarrow$  C + A \* B. The entire multiplication requires only 3N + Min(W<sub>1</sub>, W<sub>2</sub>) time units. As the matrices shift into the array, they always move in exactly the same direction and

Figure 19: Hex-connected systolic array

require no control. Each cell performs one computation at each step, and input and output are overlapped with computation. For each I/O access, there are multiple computations performed on the data item, thus execution of compute-bound problems can be speeded up without increasing the I/O requirements. This is a very significant improvement over the classical von Neumann architecture in which the memory access time is associated with each operation of the data item.

For specialized algorithms that can be implemented by the systolic array, they are fast, hardware efficient, and require no software control in communication and synchronization. The major problem with a systolic array is still in its I/O barrier. Implementation of the systolic array on a VLSI chip is limited by the number of pins, or I/O terminal, available on a single chip.

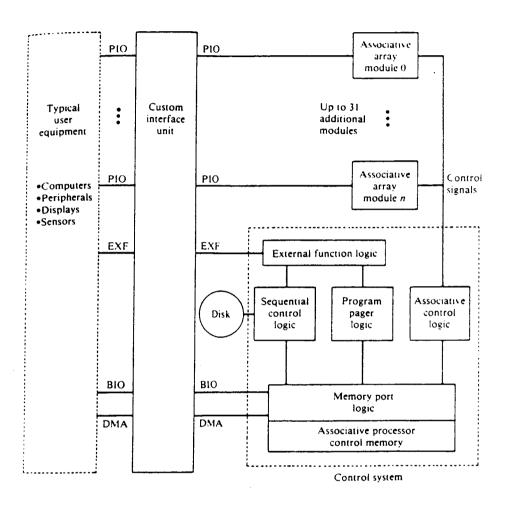

**STARAN** STARAN [Bat 74], depicted in Figure 20, is the first bit-serial parallel processing system. It was developed by Goodyear Aerospace Corporation in 1972. It consists of up

Figure 20: The STARAN System Architecture

to 32 associative array modules, each contains 256 processing elements, a 256-word 256-bit multidimensional access (MDA) memory, a flip network, and a selector. Each processing element operates serially bit by bit on the data in all MDA memory words. The MDA memory can be addressed in either bit-slice (one bit of all 256 words) or word-slice (all bits of one word).

Thus, data can be input and output in the usual word by word fashion while processing can be done in bit-serial fashion. The flip network is used for data shifting or manipulation to enable parallel search, arithmetic or logical operations among words of the MDA memory.

STARAN has high-speed input-output capabilities and the ability to interface easily with conventional computers which handle the tasks that must be processed in a single sequential data stream. The main application areas of STARAN are in signal processing and database.

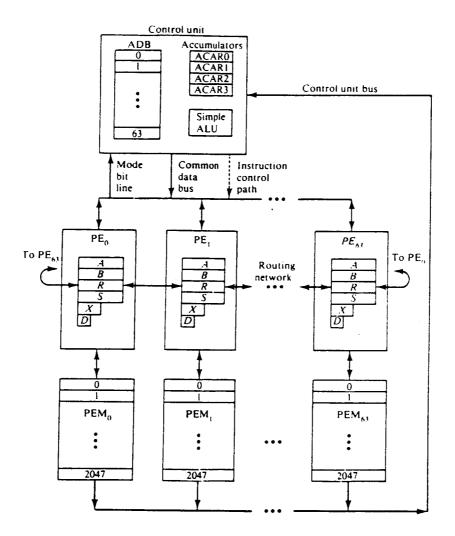

Illiac IV Illiac IV [BDM 72] was developed at the University of Illinois in the 1960s and fabricated by the Burroughs Corporation in 1972. The original design had 4 quadrants of 64 mesh-connected processing elements under the supervision of 4 control units. Due to cost escalation and schedule delays, only 1 quadrant (see Figure 21) was ever built. The speed of the 64-PE quadrant is approximately 200 million operations per second. The control unit controls and decodes the instruction stream and broadcasts instructions and common data to all PEs. It is also a scalar processor by itself besides having the ability to control the PE-array.

Each PE is a powerful computing unit, and has a 64-bit wide routing path to its four neighbors. The main application area is in scientific applications like numerical weather forecasting and nuclear engineering research.

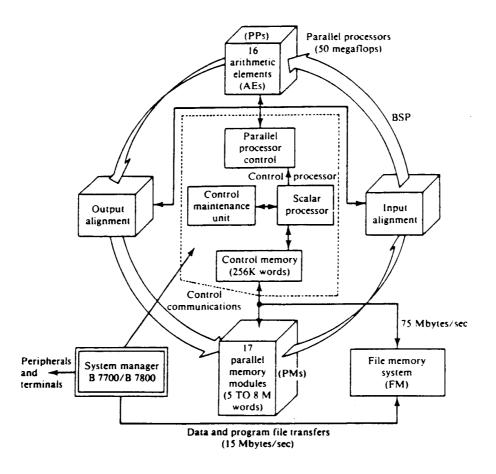

**BSP** The Burroughs Scientific Processor (BSP) [KS 82] (see Figure 22) was an attempt by Burroughs Corporation to improve on the Illiac IV design. It has 16 arithmetic elements and 17 (prime number) memory modules interconnected by two alignment networks: full crossbar switch with broadcasting and conflict resolving ability. This permits general-purpose interconnectivity between the arithmetic array and the memory-storage modules. It is the combined function of the memory-storage scheme and the alignment networks that supports the conflict-free capabilities of the parallel memory. The parallel processors perform vector computation with a clock period of 160 ns. The control processor provides the supervisory interface to the system manager in addition to controlling the parallel processor. The scalar processor processes all operating system and user-program instructions which are stored in the control memory. It executes some serial or scalar portions of user programs with a clock rate of 12 MHz and is able to perform up to 1.5 megaflops. The BSP is capable of executing up to 50 megaflops and is used mainly for scientific applications.

Figure 21: A 64-PE Illiac IV Array

Figure 22: Functional Structure of BSP

Figure 23: Block Diagram of the MPP

30

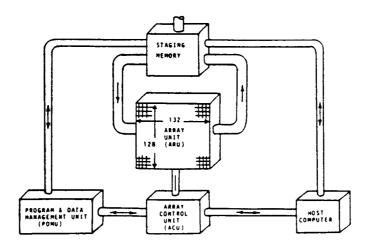

MPP Like STARAN, Massively Parallel Processor (MPP) [Bat 82] was also designed and built by Goodyear Aerospace Corporation starting from 1979 to be a high speed satellite image processing system. The processor, shown in Figure 23, has 16,896 bit-serial processing elements (PE's) arranged in a 128-row by 132-row (4 redundant rows for fault tolerance) rectangular array with strictly nearest-neighbor connections. The edge connection is programmable so that the array may look like a plane, a cylinder, a torus, a spiral, or a linear string. On 32-bit floating-point data, addition occurs at 430 MOPS and multiplication at 216 MOPS. The staging memory in the input-output path of the array unit acts both as a buffer between the array unit and the outside world, and also to reformat data so both the array unit (bit-serial) and the outside world (word-serial) can transfer data in the optimum format. MPP is a SIMD machine and all PE's perform the same instruction on every machine clock cycle. Although built for satellite imagery processing, preliminary application studies indicate that MPP can also support general image processing, weather simulation, aerodynamic studies, radar processing, reactor diffusion analysis, and computer image generation.

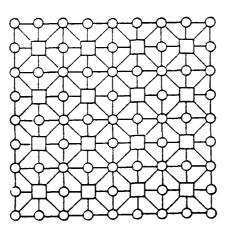

CHiP The CHiP computer, shown in Figure 24, [Sny 82] is a family of architectures each constructed from three components: a collection of homogeneous microprocessors (28 to 216), a switch lattice, and a controller. The microprocessors are not directly connected to each other, but rather are connected at regular intervals to the switch lattice. Each switch in the lattice contains local memory capable of storing several configuration settings and thus be changed dynamically during program execution: mesh for dynamic programming; hexagonally connected mesh for LU decomposition; torus for transitive closure; tree for sorting; double tree for searching; etc.. The perimeter switches are connected to external storage devices. The controller is responsible for loading the switch memory. CHiP processing begins with the controller broadcasting a command to all switches to invoke a particular configuration setting. Individual microprocessors then synchronously execute the instructions stored in their local memory.

By integrating programmable switches with the processing elements, the CHiP computer achieves a polymorphism of interconnection structure that also preserves locality, thus allowing algorithms that exploit different interconnection patterns to be used in the same program. CHiP can be viewed as a configurable systolic array: it has all the advantages of the systolic array while it is still general enough to embed different interconnection patterns in its lattice.

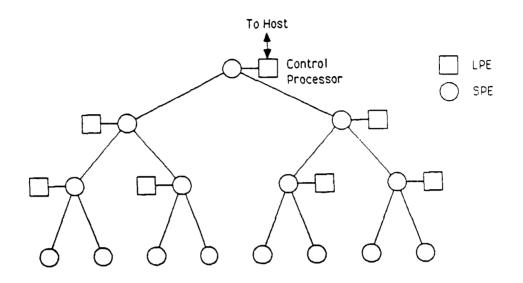

**NON-VON** The NON-VON architecture, shown in Figure 25, consists of two parts: primary processing subsystem and secondary processing subsystem. The primary processing subsystem is organized as a binary tree of small processing elements (SPEs) which have no stored program and can only execute instructions sent by its ancestor nodes. The SPEs in the first few levels of the tree are each connected to a large processing element (LPE) which

Figure 24: CHiP lattice. PEs shown as squares, switches as circles.

has locally stored program and may operate independently. Thus, NON-VON can act as a single SIMD machine with the node at the root being the ancestor of all the nodes below it, or as a multiple SIMD machine with each subtree controlled by a node connected to an LPE. The LPE connected to the root is called the control processor and is also connected to the host processor.

The secondary processing subsystem consists of 64 to 256 disk-drives each connected via an intelligent head unit to an LPE. These intelligent head units perform certain computationally simple operations (e.g. selection) on the fly, thus added to the processing power of the whole system.

NON-VON is designed to be used mainly in the areas of relational database, sorting and vision.

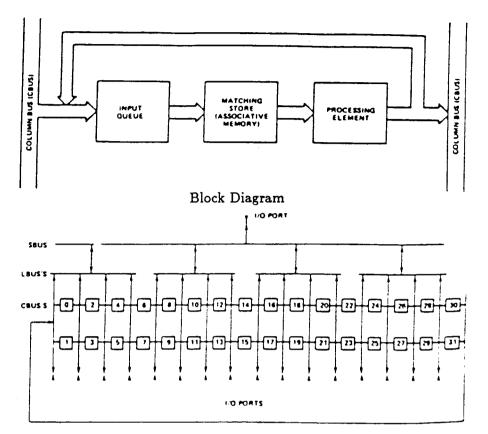

**DDSP** The Data Driven Signal Processor (DDSP) [HNI 82] is being developed by ESL Incorporated to be a programmable, modular, high-speed data flow computer primarily for signal processing applications. A block diagram is shown in Figure 26. Its configuration ranges from one to 32 processors with a maximum performance of 71 MFLOPS. DDSP is designed with a high order language (Data Driven Programming Language, or DDPL) capable of generating efficient machine code, and follows the single assignment rule. It implements a dynamic tagged data flow model where tokens are tagged with a label field determined at run-time. The processors in a DDSP system are closely coupled through an interconnection network. A processor consists of an input queue for temporarily saving tokens, a matching store (associative memory) for associating pairs of tokens, and a processing element for performing high speed integer and floating point computations (2.2 MFLOPS). Because of the nature of signal processors with wrap-around from the last pair of processors to the first pair, and augmented by a three level tree used for long distance communication. Besides

Figure 25: NON-VON Primary Processing Subsystem

signal processing, DDSP can also be used in fields of sonar and image processing.

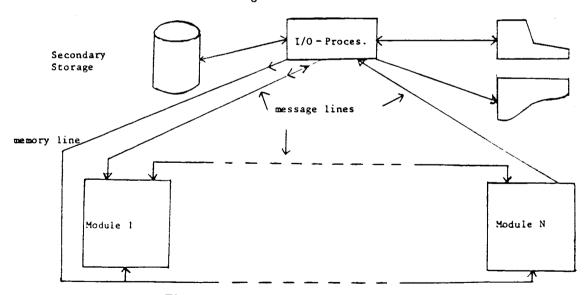

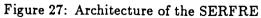

SERFRE SERFRE [Vil 82] is a multi-processor command-driven (string reduction) machine and can directly executes a FP (Functional Programming) language, trying to have subprograms executed on different processors. It is a dynamic loosely-coupled system using direct communication with storage of messages. Figure 27 shows the architecture of a possible, single-user implementation of SERFRE. Figure 28 shows the structure of a module. The I/O processor controls the memory system as well as the initiation of a program evaluation and returning of the result to the user. The C-processors have their own local memory to store data and function definitions. A C-processor consists of a register for the return address, a stack for the program, registers for the data, and a reduction engine. When asked to evaluate a function involving concurrency, it will try to call for other nonbusy C-processors to execute the subprograms, if none is available, it will evaluate them sequentially.

Cedar The objective of the Cedar project [GKL 83] at University of Illinois is to investigate ways to accommodate several thousands of high performance processors to deliver

# Interconnection Network

Figure 26: DDSP

34

Figure 28: Structure of a Module

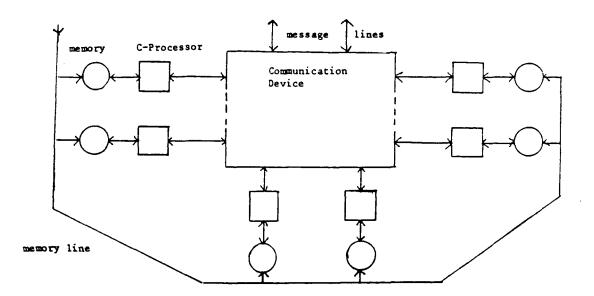

several gigaflops. It will make use of the VLSI technology to build powerful VLSI processors, for instance, 32-bit, 2.5 MFLOPS. The uniqueness of this architecture is the concept of Macro Dataflow which combines the control mechanisms of data flow architecture and storage management of the von Neumann machine. A program is viewed as a flow graph of nodes. Each node is either computational (CPF) or control (CTF). The Global Control Unit executes CTF while the processor clusters execute CPF. A processor cluster consists of a number of processors and local memory modules working cooperatively to execute a CPF. When a CPF is finished, the cluster control unit will signal the Global Control Unit so that other nodes depending on this CPF can be scheduled to be executed. Besides local memory, processor clusters can also access the global memory through the global network, an Omega network. Figure 29 shows a block diagram of the structure of Cedar.

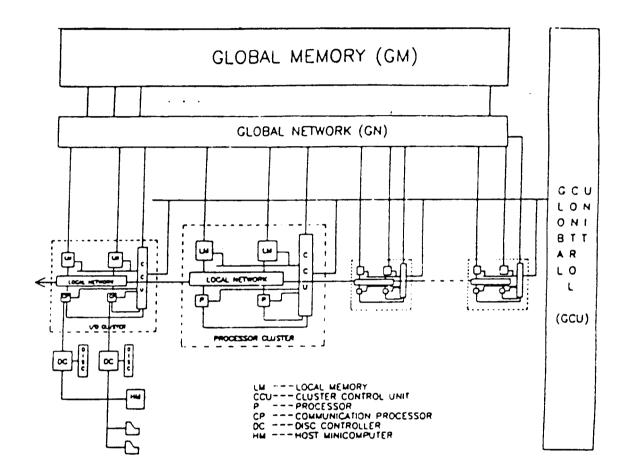

FMP The Flow Model Processor (FMP) [Lun 85] was the result of a series of design studies conducted from 1975 through 1982, sponsored both by Burroughs Corporation and by the NASA Ames Research Center. Its objective was to sustain throughput in excess of 1 GFLOP, and was intended to support large scientific problems especially modeling problems in computational aerodynamics. It was designed to support standard FORTRAN, with extended feature like **DOALL**, in which codes within the body of this construct is executed once for each value specified in the definition of the **DOALL** domain.

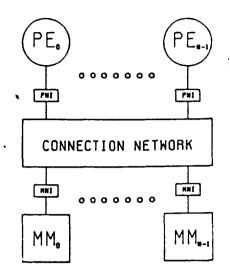

The conceptual design consists of 128 processor connected through a Connection Network (CN) to the Extended Memory. The Global Code Memory and the Data Base Memory can also be accessed through the CN. The CN, a form of Omega Network, is a circuitswitching network with decentralized control. The Processor Control and Maintenance

Figure 29: Structure of Cedar

Figure 30: Flow Model Processor Conceptual Design

Network acts as a tree of AND gates to be used to assist in the high speed synchronization at the end of the **DOALL**. Each processor in the FMP is a powerful computing unit. A scheme similar to that of the IBM 360/91 [Tom 67] was used to allow multiple functional units to be used efficiently. A block diagram is shown in Figure 30.

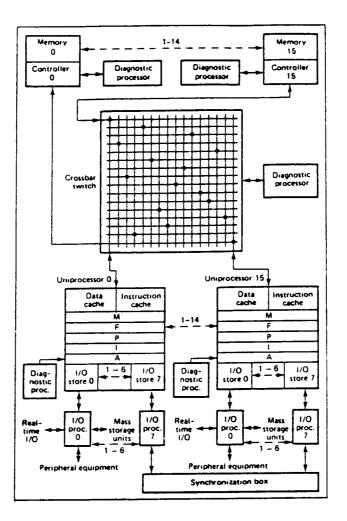

S-1 The S-1 project [WC 79] has as its general goal the development of advanced digital processing technology for potential application throughout the U.S. Navy. The S-1 multiprocessor is designed to be at least 10 times the computing power of the Cray-1. Its architecture (see Figure 31) consists of 16 independent, identical uniprocessors sharing a main memory of 16 modules, each of 1 billion bytes of semiconductor memory. Each uniprocessor is a powerful computing unit with performance comparable to the Cray-1, and can execute instructions independent of others. A full Crossbar Switch is used as the interconnection network between the processors and the main memory. A maximum peak bandwidth of more than 10 billion bits per second can be achieved when all 16 channels of the Crossbar Switch are transferring data simultaneously. To further reduce the main memory access time, each member uniprocessor contains private cache memories (data and instructions). As many as eight peripheral processors can be attached to each uniprocessor to handle I/O. The synchronization box is a shared bus connected to each member uniprocessor; one of its major functions is to transmit interrupts and small data packets from one uniprocessor to

Figure 31: The S-1 Multiprocessor

any subset of other uniprocessors in order to coordinate processing streams.

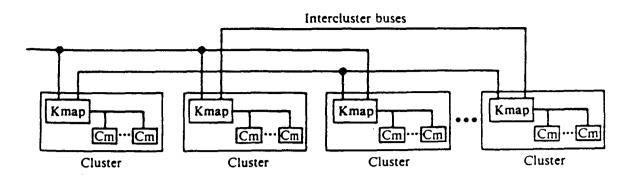

$Cm^*$   $Cm^*$  [SFS 77] is an experimental computer system designed and built at Carnegie-Mellon University. It is intended to be a testbed for exploring a number of research questions concerning multiprocessor systems.  $Cm^*$  is a hierarchical and modular system, the basic building block is a processor memory pair called a computer module or Cm. Up to 14 Cm's are connected into a cluster. Each cluster has a shared address mapping and routing processor, Kmap, which allows communication with other clusters through the intercluster buses. A simple 3-cluster system is depicted in Figure 32. Communication along the intercluster buses is done in packet switching mode to avoid deadlock over bus allocation. The processor is a DEC LSI-11. All processors share a single segmented virtual memory address space of  $2^{28}$  byte. Each processor has a local memory of 64 Kbyte and is also

Figure 32: A simple 3-cluster Cm\* system

part of the shared memory in the system. Efficient use of the system depends on ensuring that most of the code and the data references made by a processor are held locally to that processor. Inter-process communication is by message-passing and can be easily built on top of the Cm<sup>\*</sup> architecture.

HEP The HEP computer system [Smi 78] is an MIMD machine of the shared resource type. A typical system is shown in Figure 33. In this type of organization, skeleton processors compete for execution resources in either space or time. Two queues are used to time-multiplex the process states. One of these provides input to a pipelined instruction execution unit, which will decode and execute the instruction. For data memory access, the process state enters a second queue. This queue provides input to a pipelined switch which interconnects several data memory modules with several processors. Each processor of HEP can support up to 128 processes. Maximum throughput of  $10^7$  instructions per second per processor occurs when there are at least eight totally independent processes in each processor.

HEP instructions and data words are 64 bits wide. A domain of protection in HEP is called a task, and consists of a set of processes which are allowed to communicate with each other. Processes in different tasks or processors may only communicate via data memory if they have an overlapping allocation there. Any register or data memory location can be used to synchronize two processes in a producer-consumer fashion. Three states are provided: reserved, full, and empty. The execution of an instruction tests the states of locations and modifies them in an indivisible manner.

The interconnection switch consists of a number of nodes connected via ports. Messages are sent in packets and routed by the nodes according to their priorities.

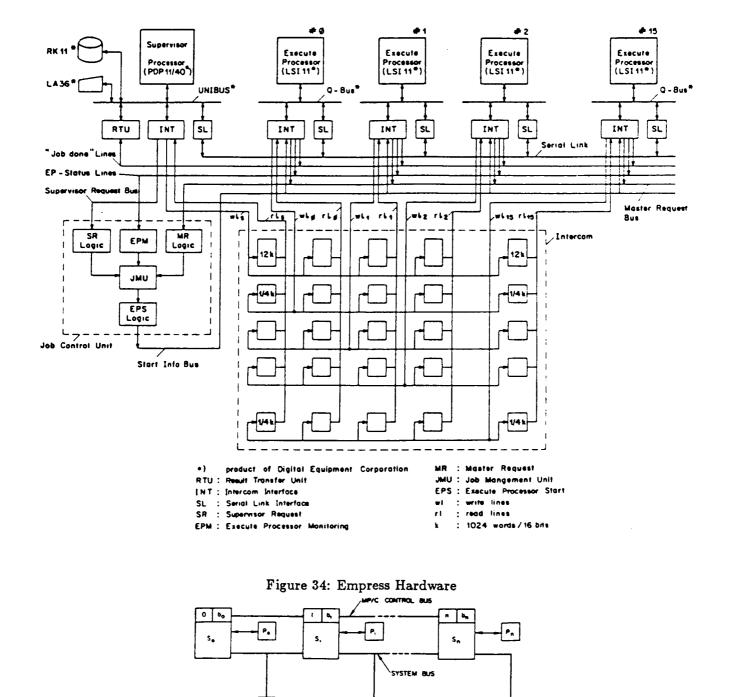

Empress The ETH-Multiprocessor Empress [BBB 82] was built in order to study the performance of MIMD architectures in general, and particularly in the field of simulation

Figure 33: A Typical HEP System

problems. Its architecture consists of a supervisor processor and a number of execute processors, all communicating through an Intercommunication System, Intercom (see Figure 34). The supervisor computer is used to partition a problem into executable jobs which will be dispatched by the job control unit to the execute processors. If an execute processor (master) finds its job exhibit inherent parallelism, it can dynamically request more (slave) processors from the job control unit to form a cooperative group. All I/O, precompilation, optimization and code generation as well as the integration step control are done in the supervisor processor.

The Intercom consists of a quadratic organized memory-matrix in which each processor writes to all blocks in its row and can read blocks from its column. Data duplication within the intercom is only executed into the matrix elements of processors working on the same job. In this way, a result provided by any of the processor is made immediately available to all other cooperating processors. Different logical addressing methods are allowed in the Intercom so that cooperating processors may appear to be neighbors although they may be physically apart.

MP/C The Multiprocessor/computer (MP/C) [AG 82], a dynamically partitioned system, has the shared memory aspect of tightly coupled multiprocessor systems and also the connection simplicity associated with message-connected, loosely-coupled multicomputer systems. It is proposed as a candidate for the effective execution of process-structured algorithms.

Its architecture consists of a number of processor and memory modules, all connected to a system bus. Process fork and join operations are implemented by bus switching as a means of partitioning and recombination of the address space. The bus can be opened between any two adjacent processor-memory pairs. Only the leftmost processor in each connected bus segment or partition is active, and can access all memory modules in that partition. All other processors in that partition are inactive. An active processor can activate an inactive processor by splitting the bus segment. Conversely, an active processor may deactivate itself by reconnecting its partition to the one on the left. This ability to partition and reconnect dynamically is best suited to execute tree algorithms, divideand-conquer algorithms, and database functions. A linear MP/C is shown in Figure 35. Multi-dimensional MP/C machines in which each row or column is a switchable bus, are also proposed.

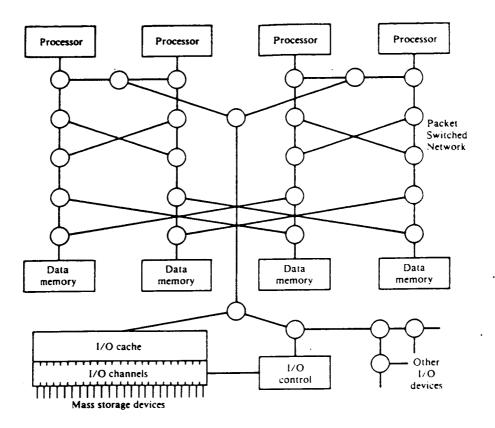

Ultra The NYU Ultracomputer [GGK 83] is a shared-memory MIMD parallel machine composed of thousands of autonomous processing elements (PE's). By the use of an enhanced message switching network with the geometry of an Omega-network, it can approximate the ideal behavior of Schwartz's paracomputer model of computation which permits every PE to read or write a shared memory cell in one cycle. The Omega-network also implements the fetch-and-add operation used as the synchronization primitive. ORIGINAL PAGE IS OF POOR QUALITY

OF POUR Williams

Figure 35: The Linear MP/C

м,

Mn

M.

42

Figure 36: Block Diagram of the NYU Ultracomputer

Its architecture consists of thousands of PE's connected through a connection network to thousands of memory modules (see Figure 36). Each PE is a high-speed VLSI floating point processor. It can also support the fetch-and-add operation: a PE will continue execution of the instruction stream immediately after issuing a request to fetch a value from central memory, the target register would be marked *locked* until the requested value is returned from memory; an attempt to use a locked register would suspend execution. The connection network is an enhanced message switching Omega-network. Each switch in the network has a queue and an internal adder to support the fetch-and-add operation. Simultaneous accesses to a common memory cell can be detected in the switch and be combined to a single fetch-and-add instruction. The memory unit also has an adder to implement the fetch-and-add instruction.

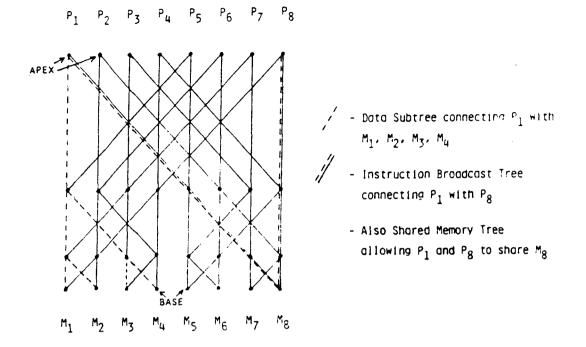

**TRAC** The Texas Reconfigurable Array Computer (TRAC) [SUK 80] is an experimental computer system built at the University of Texas at Austin. The uniqueness and the potential capabilities of TRAC arise from its interconnection network; a dynamically reconfigurable banyan network (see Figure 37). The banyan network serves to partition and to configure the processor, memory and I/O resources of the system into different architectural organizations under software control. Within a partition, TRAC is varistructured in that regardless of the data structure requirements for the task, any data width or architecture may be used. Independent or interacting tasks can all be running simultaneously on the same computer. The machine is also virtual in that user programs can be oblivious of the specific set of memory and processor modules used.

Inside the SW-banyan network, the nodes can be configured to form three types of subtree: data trees, instruction trees, and shared memory trees. Besides shared memory,

Figure 37: TRAC's Banyan Network

another means of processor-processor communication is packet switching. The packet transmission occur as a background activity so that they do not interfere with other activity.

TRAC subsystems can be architectured to implement multiple models of computation: process forking and joining, task pipelining, data-flow, vector parallelism, and synchronous parallelism.

## 4.3.3 Different Dimensions of Concurrent Architectures

In the last section, we have described 18 different concurrent architectures. They are so different in structure that it is hard to classify them in any single way. We have already described the different models of computation used by Haynes et. al. in section 4.3.1, there are four other dimensions that we can identify to describe these machines. They are interconnection network, processing element, memory system, and application. In this section, we will use these five dimensions to classify the 18 architectures described in the previous section.

Models of Computation The six different models of computation described by Haynes et. al. are multiple special-purpose functional units (or pipeline), associative processors,

|                                                                                                                                                     | Pipeline | Assoc.<br>Memory | SIMD                  | Dataflow | FP<br>Language | Multiple<br>CPU                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-----------------------|----------|----------------|-----------------------------------------|

| Systolic<br>STARAN<br>IIIiac IV<br>BSP<br>MPP<br>CHIP<br>NON-VON<br>DDSP<br>SERFRE<br>Cedar<br>FMP<br>S-1<br>Cm*<br>HEP<br>Empress<br>MP/C<br>Ultra | X        | X                | X<br>X<br>X<br>X<br>X | X        | X              | * * * * * * * * * * * * * * * * * * * * |

| TRAC                                                                                                                                                | X        |                  | X                     | X        | L              | X                                       |

Figure 38: Models of Computation

array processors, data flow computers, functional programming language machines, and multiple processors.

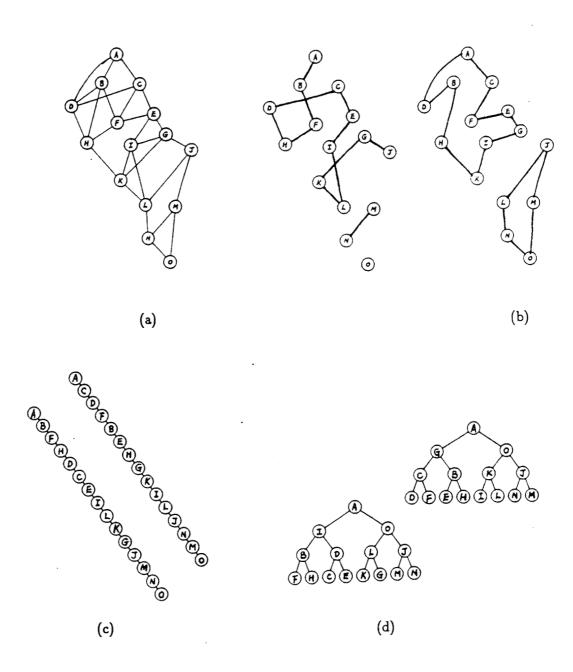

Interconnection Network In the machines that we have discussed, there are many types of interconnection network. Systolic arrays are connected in a pipelined fashion. STARAN has its own FLIP network. MPP and Illiac IV and MPP are mesh-connected. BSP and S-1 use full crossbar. CHiP uses the switch lattice. NON-VON is tree structured. Cm<sup>\*</sup> and MP/C are bus oriented. Cedar, FMP, and Ultra use the Omega network. HEP uses a pipelined switch. Empress has a quadratic memory matrix. TRAC has a 2-3 SW Banyan Network. Some of these interconnection networks can again be divided into either central or distributed control. Reconfigurability is a feature of some of the networks, which allow them to reconfigure the system resources dynamically to match the need of the problem. For multi-stage networks, three types of switching modes are possible: circuit, message, and packet. The purpose of the interconnection network is for the communication among processors (P-P), or processor to memory (P-M), or both.

**Processing Element** The number of processing elements used in each architecture varies from 1 for the DDSP to 64K for the CHiP. Most architectures allow variable number of processing elements. Requirements on the processing elements also vary.

STARAN, MPP, and NON-VON use very simple processors. CHiP, Cm<sup>\*</sup>, Empress, and TRAC use off-the-shelf microprocessors or LSI-11. Others use powerful custom made

|           | Туре         | Control     | Reconfig. | Switching  | Commun. |

|-----------|--------------|-------------|-----------|------------|---------|

| Systolic  | Pipeline     | •           | N         |            | P-P     |

| STARAN    | FLIP         | -           | N         |            | P-P     |

| Illiac IV | Mesh         |             | N         |            | P-P     |

| BSP       | Crossbar     | Central     | N         | Circuit    | P-M     |

| MPP       | Mesh         |             | N         |            | P-P     |

| СНІР      | Sw. lattice  | Central     | Y         |            | . р-р   |

| NON-VON   | Tree         |             | Y         | }          | P-P     |

| DDSP      | Bus          | Dist        | N         |            | р-р     |

| SERFRE    | Bus          |             | N         |            | P-P     |

| Cedar     | Omega        | Dist        | N         | Circuit    | P-M     |

| FMP       | Omega        | Dist        | N         | Circuit    | P-M     |

| S-1       | Crossbar     | Central     | N         | Circuit    | P-M     |

| Cm•       | Bus          | Dist        | N         | Packet     | P-M     |

| HEP       | Pipe, Switch | Dist        | N         | Packet     | P-M     |

| Empress   | Quad. Matrix | Central     | Y         |            | P-P     |

| MP/C      | Bus          | Dist        | Y         |            | P-M     |

| Ultra     | Omega        | Dist        | N         | Message    | P-M     |

| TRAC      | 2-3 Banyan   | Cent & Dist | Y         | Pack & Cir | P-P,M   |

Figure 39: Interconnection Network

|           | Number   | Power         | Size (bits) |

|-----------|----------|---------------|-------------|

| Systolic  | variable | •             |             |

| STARAN    | 32x256   | simple        | T           |

| Illiac IV | 64       | 3-5 MFLOPS    | 64          |

| BSP       | 16       | I-4 MFLOPS    | 48          |

| MPP       | 16,384   | simple        | 1           |

| CHIP      | 256-64K  | μP            |             |

| NON-VON   | >16K     | simple        | 8           |

| DDSP      | 1-32     | 2.2 MFLOPS    |             |

| SERFRE    | variable |               |             |

| Cedar     | 128x16   | 2.5 MFLOPS    | 32          |

| FMP       | 128      | 10 MFLOPS     | 64          |

| S-1       | 16       | 3 MFLOPS      | 64          |

| Cm*       | variable | LSI-11        | 16          |

| HEP       | variable | 10 MIPS       | 64          |

| Empress   | variable | LSI-11        | 16          |

| MP/C      | variable |               |             |

| Ultra     | 4096     | VLSI, fast FP |             |

| TRAC      | 16       | μΡ            | 8           |

Figure 40: Processing Element

|           | Shared     | Local | ASSOC.                                | Ext. Func |

|-----------|------------|-------|---------------------------------------|-----------|

| Systolic  | X          |       |                                       |           |

| STARAN    | <b>X</b> - |       | X                                     |           |

| Illiac IV | X          | X     |                                       |           |

| 8SP       | X          |       |                                       |           |

| MPP       | X          |       |                                       |           |

| CHIP      | X          |       |                                       |           |

| NON-VON   | X          |       |                                       |           |

| ODSP      |            | X     | X                                     |           |

| SERFRE    |            | X     |                                       |           |

| Cedar     | X          | X     |                                       |           |

| FMP       | X          | X     |                                       | X         |

| S-1       | x          | X     |                                       |           |

| Cm*       | X          | X     |                                       |           |

| HEP       | X          | X     |                                       |           |

| Empress   |            | x     |                                       |           |

| MP/C      | X          | x     |                                       |           |

| Ultra     | X          | x     |                                       | X         |

| TRAC      | X          | X     | · · · · · · · · · · · · · · · · · · · | X         |

Figure 41: Memory System

processors. The word length of the architectures ranges from 1 bit for STARAN and MPP, to 64 bits for Illiac IV, Cedar, FMP, S-1, and HEP.

Memory System Memory system can be either shared or local. In shared memory, different processors can access the same memory cell for communication and synchronization. Data stored in local memory can only be accessed by the processor attached to it. Some local memory are also used as instruction cache to reduce the traffic in the interconnection network. STARAN and DDSP have associative memory for content-addressable memory and matching store respectively. Ultra has adders in the memory system to support the fetch-and-add operation. TRAC has index registers residing in the memory modules so that a shorter 8-bit macro-instruction can be sent by the processor instead of a longer 16-bit full address. References to locations in memory modules are made by specifying one of the index registers.

Application These 18 machines are designed for different applications. In here, we have listed a few important and representative areas: general purpose, scientific, data base, image or signal processing, simulation, testbed, and divide-and-conquer.

|           | General<br>Purpose | Scien  | Data<br>Base | Image/<br>Signal | Simulat | Testbed | Divide<br>Conquer |

|-----------|--------------------|--------|--------------|------------------|---------|---------|-------------------|

| Systolic  |                    | x      |              |                  |         |         |                   |

| STARAN    | 1 · 1              |        |              | X                | X       |         |                   |

| Illiac IV |                    | X      |              |                  |         |         |                   |

| BSP       |                    | X      |              |                  |         |         |                   |

| MPP       | ]                  |        |              | X                |         |         |                   |

| CHIP      |                    | X      |              |                  |         |         |                   |

| NON-VON   | X                  | X      | X            | X                |         |         | X                 |

| DDSP      | · ·                |        |              | X                |         |         |                   |

| SERFRE    | X                  |        |              |                  |         |         |                   |