# Designing a Hardware in the Loop Wireless Digital Channel Emulator for Software Defined Radio

Janarbek Matai, Pingfan Meng, Lingjuan Wu, Brad Weals, and Ryan Kastner

Department of Computer Science and Engineering,

University of California, San Diego

Toyon Research Corporation

December 11 FPT'2012

#### **Motivation**

#### Problem

❖ Wireless system testing and verification → Difficult

# Current wireless system testing methods

- ❖ Field testing → Expensive, time consuming and difficult to repeat

- ❖ Simulation → limited by fidelity, excessive run time

#### Wireless Channel Emulator (WCE)

- Fills the gap left between simulation and field testing

- Repeatability, high-fidelity, and the opportunity to test complete radio

- Software implementation is not feasible due to amount of computation for large network

# Hardware in the Loop Wireless Channel Emulator (WCE)

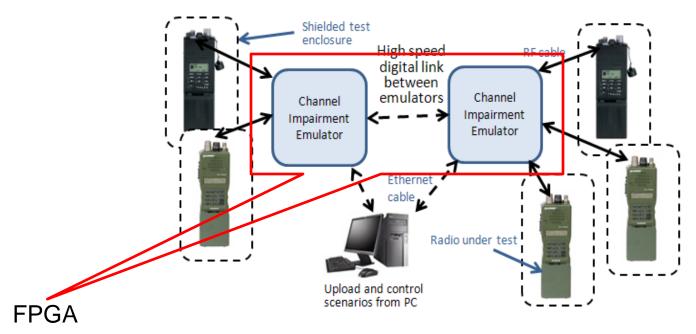

Hardware in the loop (HWIL) Wireless Channel Emulator (WCE) implementation on an FPGA platform is purposed using High-Level Synthesis Tool.

Top level concept of WCE

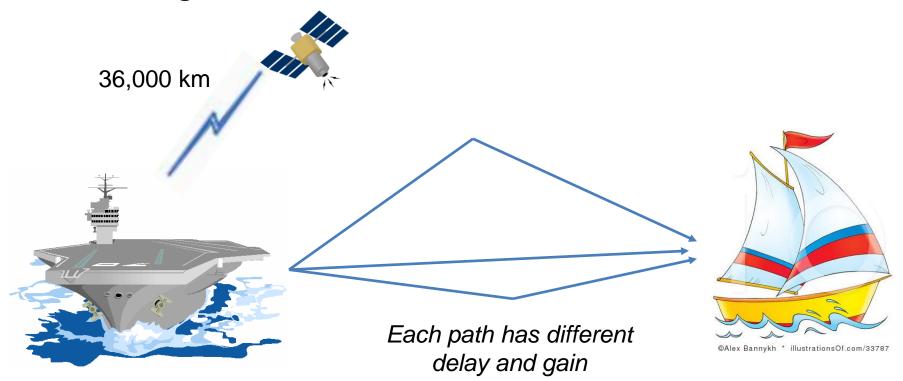

#### **Scenario**

The signal takes multiple paths each with a different Path delay and Path gain

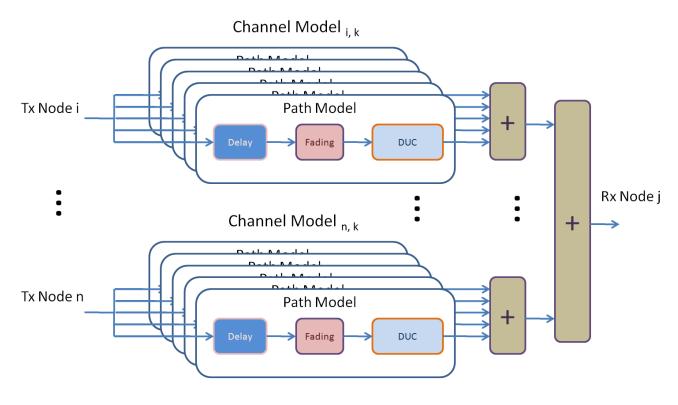

# Conceptual Multipath Channel Modeling in FPGA

- Each channel composed of multiple summed paths

- Delay, path gain, fading, and Doppler modeled in each path

- In this work, we focus on implementing a single channel emulator with multi path

# **Single Channel Emulator Model**

# Single channel emulator model

$$so_t = \sum_{i=0}^n si_{t-i\tau} w(t)_i$$

- ❖ si: Previous n+1 input complex samples

- so: Complex sample output at present time

- $\star$  w(t): Dynamically changing set of weights (gain and delay)

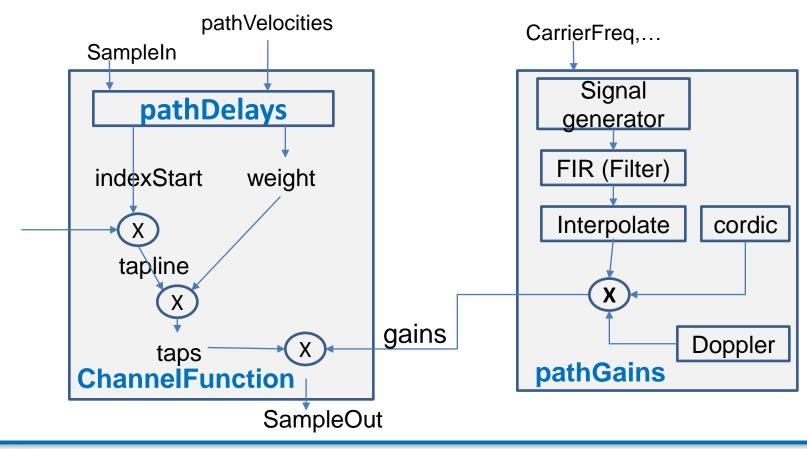

# Complex sample calculation (channel function)

$$tap line_{ij} = delay line_{index}$$

$$tap s_i = \sum_{i,j=0}^{N,K} tap line_{ij} * weight_{ji}$$

$$so_r_i = \sum_{i=0}^{N} gains_n * taps_r_i - gains_i * taps_i$$

$$so_i = \sum_{i=0}^{N} gains_r * taps_i - gains_i * taps_r_i$$

Path delays

Path gains

channelFunction

# **Block Diagram of WCE**

#### Target performance

- pathDelays and ChannelFunction: 30 Mhz

- pathGains: 40kHZ

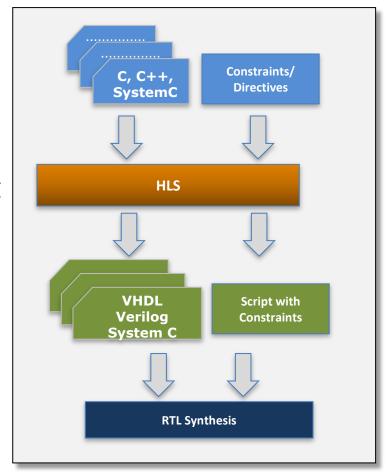

# **High Level Synthesis**

- High Level Synthesis

- Creates an RTL implementation from C level source code

- Why use HLS?

- A good digital WCE has to handle wide range of dynamically changing parameters such as Doppler effect, fast fading, and multipath

- HLS provides easy design space exploration with different parameters

- E.g., varying number of paths in a channel

Courtesy to Xilinx

#### **Process of WCE design with HLS**

#### 1. Baseline design

Synthesizable C code

#### 2. Restructured design

Manually optimizing C code for HW

#### 3. Bit accurate design

Bit-width optimization

# 4. Pipelining, Unrolling and Partitioning (PUP)

Parallelizing computation

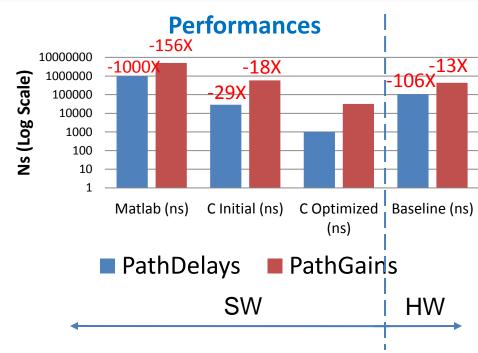

# 1. Baseline design

- Main goal:

- Synthesizable

- Things to be done

- ♦ Matlab → Initial C

- ❖Initial C → Optimized C

- Remove dependencies

- Remove dynamic memory...

#### 1. Baseline - Results

- Baseline

- ❖PathDelays: 3180X slower than target (30 Mhz)

- ❖PathGains: 17X slower than target (40 kHz)

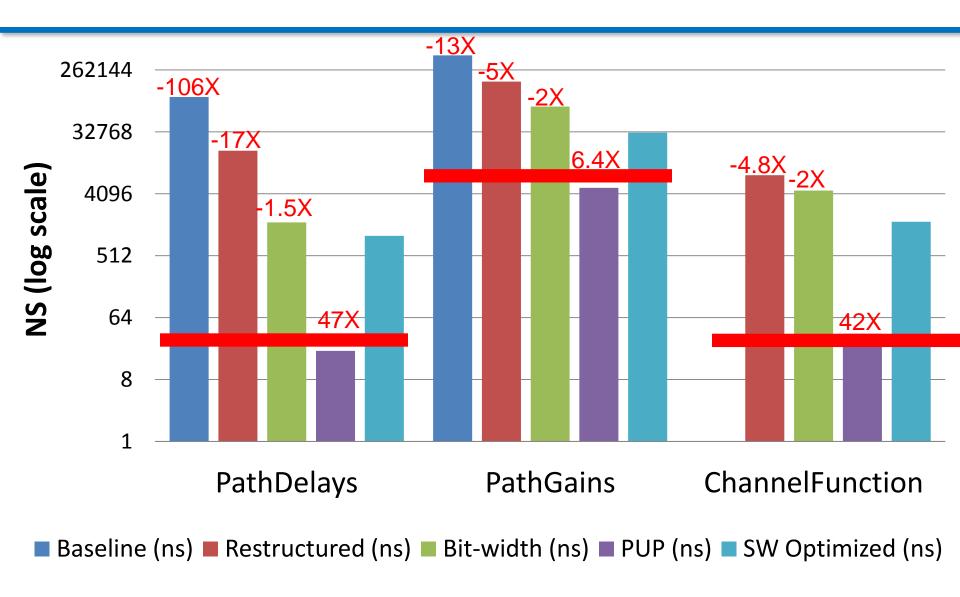

# 2. Restructured Design

- Two goals:

- To optimize the code itself without using any HLS pragmas

- To write a "C code" targeting the architecture

- **❖** E.g.,

- Loop merging

- Expression balancing

- Loop unrolling

- **...**

# 2. Restructured Design - Example

#### Clock cycle reduction of pathGains module

Loop merging

```

\begin{array}{l} \text{for (int p = 0; p < N; p + +)} \{ \\ \text{for (int i = 0; i < SIZE; i + +)} \{ \\ \text{t1 = t1 + js[i] * FIRin[p][i][0];} \\ \text{for (\underline{int i = 0; i < SIZE; i + +)}} \{ \\ \text{t2 = t1 + js[i] * FIRin[p][i][1];} \\ \end{array}

```

Expression balancing

```

\begin{array}{c} t1=t1+js[i]*FIRin[p][i][0];\\ t2=t1+js[i]*FIRin[p][i][1]; \end{array} \qquad \begin{array}{c} t1\_1=js[i]*FIRin[p][i][0];\\ t1=t1+t1\_1;\\ t2\_1=js\,[i]*FIRin[p][i][1];\\ t2=t2+t2\_1; \end{array} \qquad \begin{array}{c} 41250 \rightarrow 29730 \end{array}

```

Loop unrolling

# 2. Restructured Design – Results

- Restructured design vs. Target

- PathDelays: 523X slower than target (30 Mhz)

- PathGains: 7X slower than target (40 kHz)

- ChannelFunction: 229X slower than target (30 Mhz)

# 3. Bit accurate design

- ❖ By default, HLS C/C++ have standard types

- ❖ E.g., char (8-bit), int (32-bit),...

- Minimizing bit widths will result in smaller & faster hardware

- E.g., ap\_fixed and ap\_int

- Bit accurate design of PathGains module

- 55 types are set to use fixed point type

```

typedef ap_uint<6> AP_UINT6;

typedef ap_uint<12> AP_UINT12;

typedef unsigned int AP_UINT6;

typedef ap_uint<33> AP_UINT33;

typedef unsigned int AP_UINT12;

typedef unsigned long long int AP UINT33;

typedef ap uint<32> AP UINT32;

typedef unsigned long int AP_UINT32;

typedef ap int<32> AP INT32;

typedef int AP INT32;

typedef ap_uint<20> AP_UINT20;

typedef unsigned int AP UINT20

typedef ap_ufixed<15,2,AP_RND > AP_UFIXED20_3;

typedef double AP UFIXED20 3;

typedef ap_fixed<12,10,AP_RND > AP_FIXED12_10;

typedef double AP FIXED12 10;

typedef ap_fixed<10,9,AP_RND > AP_FIXED10_9;

ixed<8,

typedef ap fixed<15,5,AP RND

typedef ap fixed<22,16,AP RND

typedef ap fixed<18,16,AP RND

typedef ap_ufixed<33,1,AP_RND > AP_UFIXED33_1;

typedef ap_ufixed<32,1,AP_RND > AP_UFIXED32_1;

typedef double AP UFIXED33 1;

typedef ap_ufixed<27,1,AP_RND > AP_UFIXED27_1;

typedef double AP UFIXED32 1;

typedef ap_ufixed<20,1,AP_RND > AP_UFIXED20_1;

typedef double AP UFIXED27 1:

typedef double AP UFIXED20 1;

typedef ap_fixed<10,1,AP_RND > AP_FIXED10_1;

typedef double AP_FIXED10_1;

typedef ap_ufixed<6,1,AP_RND > AP_UFIXED6_1;

typedef double AP_UFIXED6_1;

typedef ap_ufixed<6,5,AP_RND > AP_UFIXED6_5;

typedef double AP UFIXED6 5;

typedef ap ufixed<20,15,AP RND > AP UFIXED20 15;

typedef double AP_UFIXED20_15;

typedef ap ufixed<18,14,AP RND > AP UFIXED18 14;

```

# 3. Bit accurate design - Results

- Bit accurate design vs. Target

- PathDelays: 47X slower than target (30 Mhz)

- PathGains: 3X slower than target (40 kHz)

- ChannelFunction: 133X slower than target (30 Mhz)

# 4. Pipelining and Partitioning

- On top of bit accurate design, PUP is applied

- Pipeline

- Improves throughput

- ❖ Default: Target initiation interval(II) of 1 II=2,II=3,...

- Partition

- ❖BRAMs limit pipelining → Partition large BRAMs into smaller BRAMS or into registers

# 4. Pipelining and Partitioning - Example

#### pathDelays

- Optimizations: Partition: 5 BRAM, Pipeline: II=1

- $\bullet$  DSP48: 19 $\rightarrow$ 30 (57%),

- ❖ FF: 424→786 (85%),

- ♦ LUT: 563 → 4230 (651%)

- Throughput: 47X than bit accurate design

#### pathGains

- Optimizations: Partition: 12 BRAM of 42, Pipeline/Unroll

- ◆ DSP48E: 47→86 (82%),

- ❖ FF: 20399 → 34421 (68%),

- ◆ LUT: 22121→38893 (75%)

- Throughput: 15X than bit accurate design

# 4. Pipelining and Partitioning -Results

- Bit accurate design vs. Target

- PathDelays 0.6X slower than target (30 Mhz)

- PathGains 0.2X slower than target (40 kHz)

- ChannelFunction 1.1X slower than target (30 Mhz)

#### **Final Results**

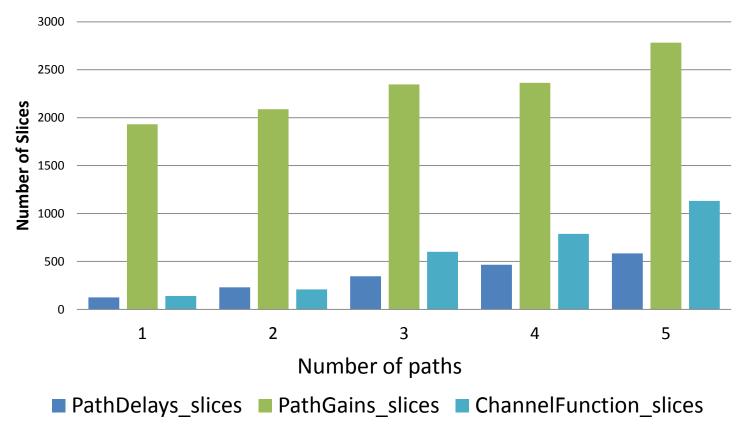

#### **DSE of WCE for Different Number of Paths**

HLS allows easy DSE of WCE for different parameters

E.g., number of paths 1,2,3,4,5

#### **Results for Five Paths**

# Resource (xc6vlx240t)

|                 | Slices | LUT  | FF   | DSP48E | BRAM |

|-----------------|--------|------|------|--------|------|

| PathDelays      | 584    | 1843 | 411  | 30     | 0    |

| PathGains       | 2783   | 8756 | 7044 | 53     | 30   |

| ChannelFunction | 1131   | 3469 | 1798 | 40     | 0    |

#### Performance

|                 | Clock<br>Cycles | Clock Period (ns)/ Frequency | Latency(ns)/Throughput |

|-----------------|-----------------|------------------------------|------------------------|

| PathDelays      | 4               | 5.394 /184 Mhz               | 21 / 47 Mhz            |

| PathGains       | 501             | 9.97 / 100 Mhz               | 4994 /0.2 Mhz          |

| ChannelFunction | 6               | 6.62 /151 Mhz                | 37 /26 Mhz             |

# **Design Effort**

| Design                             | Days spend               | Tasks                                                                                                        |

|------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|

| Baseline                           | <b>25.9%</b> (28 hours)  | Understanding the code Converting matlab to C++, Removing library dependency, Writing HLS synthesizable code |

| Restructured code                  | <b>22.2</b> % (24 hours) | Manually loop merging, Expression balancing, Loop unrolling                                                  |

| Bit Accurate Design                | <b>29.6%</b> (32 hours)  | Calculation of 57 fixed point type widths (pathGains: 36, PathDelays:19, ChannelFunction: 2)                 |

| Optimized Design                   | <b>7.4%</b> (8 hours)    | Optimizing using directives                                                                                  |

| Collecting Results/DSE/Present ing | <b>14.8%</b> (16 hours)  | DSE, Collecting results, Presenting                                                                          |

| Total                              | ~108 hours               |                                                                                                              |

#### **Conclusion**

- Designed single channel wireless emulator using HLS tool.

- HLS provides easy parameterization of WCE design.

- We plan to extend this work to multiple channel emulator and make end-to-end system

- Lessons Learned

- Achieving target performance and area depends

- Writing a "C Code" targeting architecture is essential

- Application and code size

- ❖2 optimization pragmas (pipeline, partition out of

33) + Restructured code+ Bit Width → Target goal