# Designing Parallel Algorithms for SMP Clusters

Dissertation

der Fakultät für Informations- und Kognitionswissenschaften der Eberhard-Karls-Universität Tübingen zur Erlangung des Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.)

> vorgelegt von Dipl.-Inform. Martin Schmollinger aus Reutlingen

> > Tübingen 2003

Tag der mündlichen Qualifikation: 29.10.2003Dekan:Prof. Dr. Martin Hautzinger1. Berichterstatter:Prof. Dr. Michael Kaufmann2. Berichterstatter:Prof. Dr. Wolfgang Rosenstiel

## Danksagungen

Es gibt Momente im Leben, in denen man wichtige und richtungweisende Entscheidungen treffen muss. Man sollte sich glücklich schätzen, wenn man rechtzeitig bemerkt, dass ein solcher Moment vorliegt. Ich möchte all denen danken, die mich ermuntert haben, mir die Zeit für die Promotion zu nehmen.

Vor allem möchte ich meinem Betreuer Prof. Dr. Michael Kaufmann danken, der mir die Möglichkeit gegeben hat diese Arbeit anzufertigen und mich dabei in allen Belangen unterstützt hat.

Bedanken möchte ich mich auch bei Prof. Dr. Wolfgang Rosenstiel für seine Arbeit als zweiter Berichterstatter.

Mein Dank gilt auch meinen aktuellen und früheren Kollegen des Arbeitsbereichs Paralleles Rechnen für die gute Atmosphäre und die vielen Unternehmungen wie Betriebssport, "Besseressen" oder Boule.

Zu guter Letzt bedanke ich mich auch bei meinen Freunden und Eltern, die im Gegensatz zu mir immer an den erfolgreichen Abschluss der Promotion geglaubt haben. iv

### Zusammenfassung

In der vorliegenden Dissertation untersuchen wir Entwurfs- und Optimierungsmethoden für die Entwicklung von parallelen Algorithmen für SMP *Cluster*. Dabei handelt es sich um eine spezielle Architektur von Parallelrechnern, die zwei verschiedene Konzepte in einem System vereint. SMP Cluster bestehen aus Rechenknoten, deren Prozessoren speichergekoppelt sind (shared-memory). D.h. die Prozessoren innerhalb eines Rechenknotens können über den gemeinsamen Speicher kommunizieren und synchronisieren. Die Rechenknoten selbst werden durch ein Verbindungsnetzwerk miteinander verknüpft. Die Kommunikation und Synchronisation von Prozessoren in verschiedenen Rechenknoten erfolgt über dieses Netzwerk und entspricht einem nachrichtengekoppeltem System bzw. einem System mit verteiltem Speicher (distributed-memory). Diese Organisation führt zum einen zu einer parallelen Hierarchie, denn Parallelität gibt es sowohl innerhalb als auch zwischen den Rechenknoten. Zum anderen entsteht eine Hierarchie bezüglich der Kommunikation. Im Allgemeinen ist die Kommunikation innerhalb eines Rechenknotens bei der ein gemeinsamer Speicher verwendet wird schneller, als die Kommunikation über ein Verbindungsnetzwerk. Es existieren demnach mindestens zwei Hierarchiestufen. Durch moderne Entwicklungen wie hierarchische Strukturen von Verbindungsnetzwerken, Metacomputing Technologien, bei der mehrere Parallelrechner verbunden werden oder Grid Computing Technologien, die das Internet verwenden um weltweit verteilte Rechenressourcen zu vereinen, kann es jedoch weitere Hierarchiestufen geben. Auch hier gilt, je "niedriger" die Ebene in der Netzwerkhierarchie, desto schneller ist die Kommunikation.

Aus diesem Grund müssen effiziente Algorithmen in der Art gestaltet werden, dass sowohl die parallele Hierarchie als auch die Kommunikationshierarchie berücksichtigt werden. Im Allgemeinen werden beim Entwurf von Algorithmen die Hierarchien vernachlässigt und die Maschine als nicht hierarchisch angesehen. Darüber hinaus ist die allgemeine Vorgehensweise bei der Erstellung von Programmen dominiert durch das jeweils verwendete Programmiermodell. Der Entwickler verlässt sich häufig auf die Effizienz der verwendeten Bibliotheken. Die Verwendung optimierter Bibliotheken führt sicherlich ebenfalls zu sehr schnellen Programmen, doch um wirklich das Optimum zu erreichen ist es nötig auch die Algorithmen an die hierarchische Umgebung anzupassen. Ein weiteres Problem ist, dass der Entwurfprozess paralleler Algorithmen in der Regel nicht gestützt ist durch die Verwendung von Methoden. Sicherlich kann die Entwicklung eines parallelen Algorithmus nicht auf ein einfaches Rezept reduziert werden, dennoch kann die Verwendung allgemeiner Methoden die Menge berücksichtigter Alternativen erhöhen und fehlerhafte Ansätze vermeiden.

In den folgenden Kapiteln zeigen wir einen alternativen Weg auf, der die Zusammenhänge zwischen theoretischen Kostenmodellen, Programmiermodellen und SMP Clustern aufzeigt und es dadurch ermöglicht eine theoretische Analyse eines Algorithmus in eine effiziente Implementierung für SMP Cluster münden zu lassen. Neben dieser Brücke von einer theoretischen Analyse zur effizienten Implementierung stellen wir verschiedene Methoden für den Entwurf und die Optimierung von parallelen Algorithmen für SMP Cluster vor. Anhand verschiedener Fallbeispiele erklären wir die Methoden und die Verwendung des Kostenmodells bei der Analyse der entwickelten Algorithmen.

Kapitel 1 ist eine Einführung in die Problematik der Entwicklung von parallelen Algorithmen. Neben einem motivierenden Beispiel wird der Zusammenhang zwischen theoretischen Kostenmodellen, Programmiermodellen und Architekturen dargestellt.

Kapitel 2 gibt dann eine Übersicht über parallele Architekturen, Kostenund Programmiermodelle und zeigt ihre mögliche Verwendung für den Entwurf von Algorithmen für SMP Cluster auf.

Wir beginnen mit der Formulierung eines theoretischen Kostenmodells für SMP Cluster (KNUMA) in Kapitel 3 und zeigen seine Verwendung anhand der Analyse von *broadcast* Problemen, bei denen ein Prozessor eine (individuelle oder einheitliche) Nachricht an jeden anderen Prozessor übermitteln muss. Wir betrachten das vorgestellte Modell als eine Obermenge für die Analyse von Algorithmen auf SMP Clusters. In Abhängigkeit der Eigenschaften eines speziellen SMP Cluster und aufgrund der Beschaffenheit des zu untersuchenden Problems kann die Verwendung eines reduzierten Modells ausreichend sein und macht die Analyse leichter.

Kapitel 4 stellt Methoden zur Entwicklung von parallelen Algorithmen und zur Optimierung für SMP Cluster vor. Die Methoden können auf den verschiedenen Ebenen des Entwicklungsprozesses angewendet werden, beginnend bei einer fein-granularen Zerlegung des gegebenen Problems bis hin zur Optimierung einzelner Aspekte paralleler Algorithmen für SMP Cluster.

Die weiteren Kapitel sind Fallstudien für die Verwendung der Methoden bei der Algorithmusentwicklung und die Verwendung des Kostenmodells bei der Analyse.

In Kapitel 5 zeigen wir anhand der parallelen Matrix-Vektor Multipli-

kation, wie ein paralleler Algorithmus auf die SMP Cluster Architektur übertragen wird, wie redundante Daten genutzt werden können um Kommunikationsoperationen einzusparen und wie eine unnötige Verwendung von redundanten Daten vermieden wird. Dazu werden verschiedene Datenverteilungen untersucht.

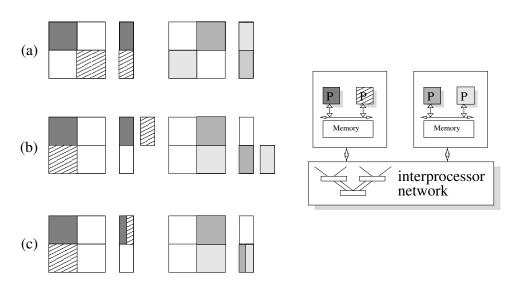

Kapitel 6 stellt anhand des Problems der Transponierung von verteilten Matrizen in paralleler Umgebung eine Optimierungsmethode vor, die versucht existierende Kommunikationsmuster durch geschickte Datenverteilung an die jeweilige Struktur des SMP Clusters anzupassen um die Kommunikationskosten zu reduzieren. Wir stellen eine Verteilung vor, durch die das Transponieren einer verteilten Matrix keine Kommunikation über das Netzwerk benötigt und gleichzeitig den Speicherbedarf je Prozessor minimiert.

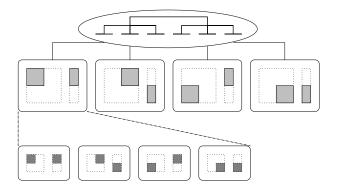

Kapitel 7 ist eine Fallstudie für den Entwurf eines hierarchisch-sensitiven Algorithmus. Die Methode schlägt vor ein Problem durch Informationsaustausch in immer niedrigere Ebenen der Hierarchie zu verschieben, bis am Ende lediglich lokale Berechnungen nötig sind. Als Beispiel wird das *Radix Sort* Verfahren untersucht. Dieses Verfahren ermöglicht es ganze Zahlen anhand ihrer Binärdarstellung in mehreren Iterationen zu sortieren. Dabei werden in jeder Iteration die Zahlen anhand eines Teils ihrer binären Darstellung in eine Reihenfolge gebracht. Wir zeigen den Weg von der sequentiellen Version bis zu einer hierarchisch sensitiven parallelen Version auf, die mit einem Minimum an Kommunikation auskommt und daher exzellent für SMP Cluster geeignet ist.

Die Ergebnisse der Arbeit sind in Kapitel 8 zusammengefasst. Der Anhang A gibt eine Übersicht der begutachteten Publikationen, die zu den einzelnen Kapiteln veröffentlicht wurden. viii

## Preface

In the following thesis, we observe methods for designing and optimizing parallel algorithms for SMP clusters. This particular architecture for parallel computers combines two different concepts. SMP cluster consist of computing nodes that are shared-memory systems, because the processors have access to common resources and especially to the local memory system. Hence, the processors within the same node are capable to communicate and synchronize using the shared-memory. An interconnection network connects the nodes. Communication and synchronization of processors from different nodes is done over this network and thus, correspond to a distributed memory system. In the first place, this organization leads to a parallel hierarchy, because parallelism is involved within and between the nodes. Secondly, a hierarchy is created concerning communication. In general, communication within a node is faster than communication between the nodes due to the use of shared-memory. Therefore, there are at least two levels of hierarchy. Due to modern trends like hierarchical interconnection structures, Metacomputing technology, where several parallel machines are connected, or Grid computing technology that use the Internet to unify distributed computing resources in the whole world, there might be even more levels of hierarchy. Basically, the lower the level of the network for a communication operation, the faster the communication can be done.

On this account, efficient algorithms have to be designed in the way that the parallel as well as the communication hierarchy is considered. Usually, this is not the case, and the SMP clusters are regarded as *non-hierarchic*. Moreover, the general approach for the design of a parallel application is dominated by the use of a particular programming model. The programmer relies on the efficiency of the implementation of the model for the respective platform. Of course, this strategy does also lead to fast programs, but in order to reach the optimum, it is additionally important to adapt the algorithms to the hierarchical environment. Another problem is that the design process of parallel algorithms is in general not supported by methods. Obviously, the design of a parallel algorithm cannot be reduced to a simple recipe, however, the consideration of general design methods maximizes the amount of considered options and minimizes the threat of wrong algorithm design approaches.

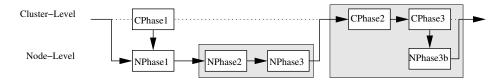

In the following chapters, we show an alternative way that shows the dependencies between theoretical cost models, programming models and SMP clusters. It enables the developer to convert a theoretical analysis of an algorithm into an efficient implementation for SMP clusters. Besides the bridge from a theoretical analysis to an efficient implementation, we present several methods for designing and optimizing parallel algorithms for SMP clusters. With the help of case studies, we explain the design methods and the usage of the cost model for the algorithm analysis.

Chapter 1 is an introduction to the issues of developing parallel algorithms. Besides a motivating example for parallel algorithms, the connections between theoretical cost models, programming models and parallel architectures are depicted.

Chapter 2 gives an overview on parallel architectures, cost- and programming models and shows their capability for the development of parallel algorithms for SMP clusters.

After that, we start with the formulation of a theoretical cost model for SMP clusters ( $\kappa$ NUMA) in Chapter 3 and show its usage by the analysis of *broadcast* problems, where one processor has to send one (individual or general) message to each of the other processors. The model can be regarded as a super-set for the analysis of algorithms for SMP clusters. Depending on the properties of a certain SMP cluster and because of the character of the analyzed problem, the usage of a reduced model may be sufficient and makes the analysis more feasible.

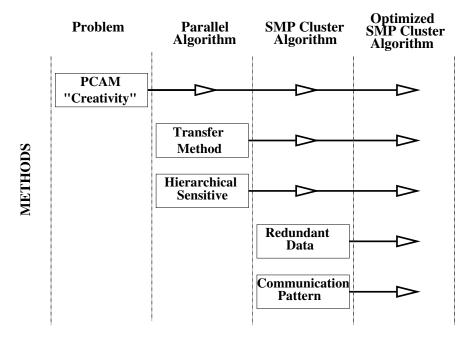

Chapter 4 introduces methods for designing and optimizing parallel algorithms for SMP clusters. The methods can be applied to different stages of the design process, beginning at the stage of a fine-grained problem partitioning and ending with the optimization of single aspects of parallel algorithms for SMP clusters.

Further chapters are case studies for the usage of the methods for algorithm design and for the usage of the cost model for the analysis.

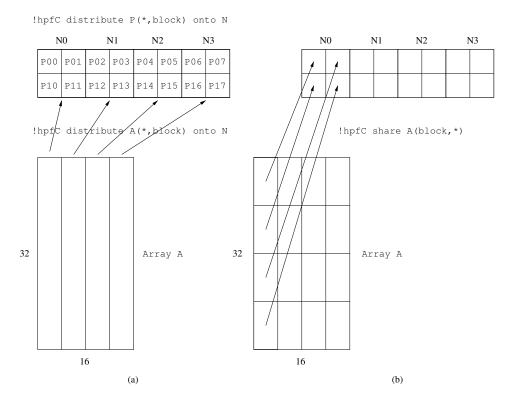

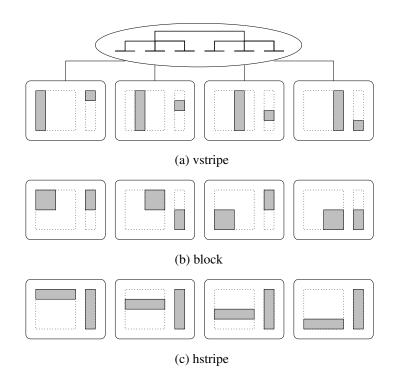

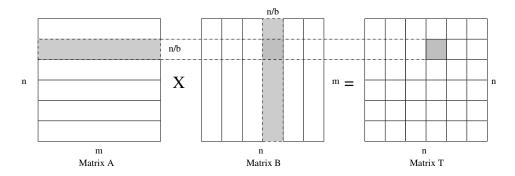

In Chapter 5, we show by means of the parallel dense matrix-vectormultiplication how a parallel algorithm is transferred to an SMP cluster, how redundant data can be used to reduce the number of communication operations and how an unnecessary usage of redundant data can be avoided. For that purpose, we analyze several data-distributions.

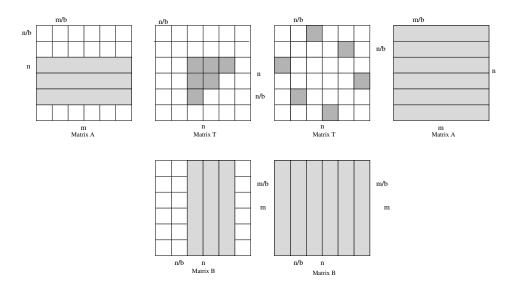

Chapter 6 presents an optimization method that tries to adapt existing communication patterns to the respective structure of an SMP cluster. Communication patterns of algorithms can often be influenced by data distribution. We attempt to distribute the data in order to reduce the communication cost maximally. The method is explained using the problem of transposing distributed matrices in a parallel setting. We present a data distribution with which an algorithm is able to transpose a distributed matrix without communication over the network. At the same time, the data-

х

distribution minimizes the amount of memory per processor.

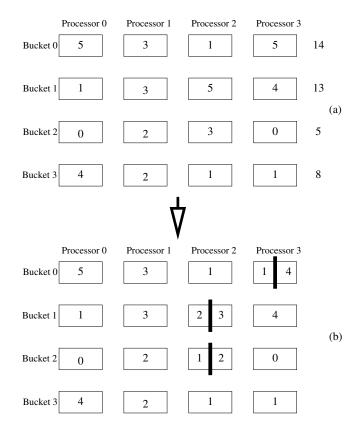

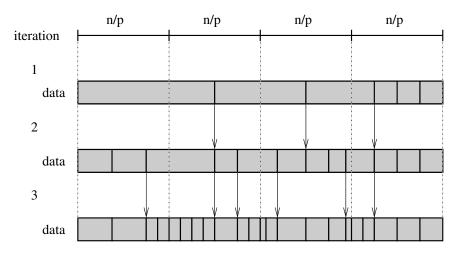

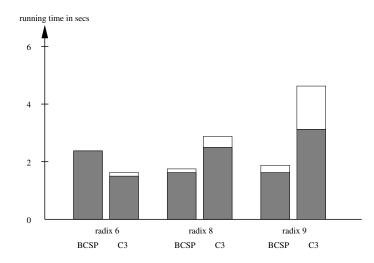

Chapter 7 is a case study for the design of a hierarchic-sensitive algorithm. The method suggests moving a problem in lower and lower levels of the hierarchy by exchanging informations, until only local computation remains. As an example, the *Radix Sort* algorithm is observed. This method enables to sort integer values by their binary representation within several iterations. In each iteration, the integers are sorted according to a certain part of their binary representation (the radix). We show the way from a sequential to hierarchical sensitive parallel algorithm that works with a minimum of communication operations and hence, is very suitable for SMP clusters.

The results of the thesis are summarized in Chapter 8. The Appendix A gives an overview on refereed publications that build the base for the chapters.

xii

# Contents

| 1 | Intr                                                 | oductio  | on                                                    | 1  |

|---|------------------------------------------------------|----------|-------------------------------------------------------|----|

|   | 1.1                                                  | Motiv    | vation for Parallel Computation                       | 1  |

|   | 1.2 Levels of Parallelism in Computer Programs       |          |                                                       |    |

|   | 1.3 Design Chain for Efficient Parallel Applications |          |                                                       |    |

|   | 1.4                                                  | The C    | Contribution of the Thesis                            | 8  |

|   | 1.5                                                  | Struct   | rure of the Thesis                                    | 10 |

| 2 | Arc                                                  | hitectu  | res, Models, Libraries                                | 11 |

|   | 2.1                                                  | Archi    | tectures                                              | 11 |

|   |                                                      | 2.1.1    | Motivation and Technological Perspective              | 18 |

|   | 2.2                                                  | Comp     | outational Cost Models                                | 20 |

|   | 2.3                                                  | Parall   | el Bridging Models                                    | 21 |

|   |                                                      | 2.3.1    | The Bulk Synchronous Parallel Model                   | 22 |

|   |                                                      | 2.3.2    | LogP Model                                            | 25 |

|   |                                                      | 2.3.3    | QSM model                                             | 26 |

|   |                                                      | 2.3.4    | A Comparison of Parallel Bridging Models              | 26 |

|   |                                                      | 2.3.5    | Parallel Bridging Models and Hierarchical Parallelism | 27 |

|   | 2.4                                                  | Progr    | amming Models                                         | 30 |

|   |                                                      | 2.4.1    | Parallel Programming Libraries                        | 30 |

|   |                                                      | 2.4.2    | Parallel-Hierarchical Programming                     | 36 |

|   | 2.5                                                  | Sumn     | nary                                                  | 46 |

| 3 | A M                                                  | lodel fo | or Hierarchical SMP Clusters                          | 49 |

|   | 3.1                                                  | Desig    | n Decisions for the Model                             | 49 |

|   | 3.2                                                  | кNUN     | MA Model                                              | 52 |

|   |                                                      | 3.2.1    | The Set of KNUMA-Parameters                           | 52 |

|   |                                                      | 3.2.2    | Execution of Parallel Algorithms                      | 53 |

|   |                                                      | 3.2.3    | One-to-All Broadcast Problem                          | 55 |

|   |                                                      | 3.2.4    | Remarks and Conclusions to the Broadcast Problem .    | 63 |

|   | 3.3                                                  | Sumn     | nary                                                  | 64 |

| 4 |     | igning Parallel Algorithms                               | 67  |

|---|-----|----------------------------------------------------------|-----|

|   | 4.1 |                                                          | 69  |

|   | 4.2 | Transferring Parallel Algorithms                         | 73  |

|   | 4.3 | Hierarchical Sensitive Design                            | 75  |

|   | 4.4 | 1                                                        | 76  |

|   | 4.5 | Usage and Avoidance of Redundant Data                    | 77  |

|   | 4.6 | Summary                                                  | 79  |

| 5 | Exp | 5                                                        | 81  |

|   | 5.1 | 1 0 0                                                    | 81  |

|   | 5.2 | 1                                                        | 82  |

|   |     | 0                                                        | 83  |

|   |     | 5.2.2 Data Distribution                                  | 84  |

|   |     | 5.2.3 Analysis                                           | 87  |

|   |     | 5.2.4 Problems Involved with a Non-Hierarchical Approach | 89  |

|   | 5.3 | Experimental Tests                                       | 91  |

|   | 5.4 | Summary                                                  | 93  |

| 6 | Ada | ptation of Communication Patterns                        | 95  |

|   | 6.1 | Problem Definition                                       | 98  |

|   | 6.2 |                                                          | 98  |

|   |     |                                                          | 99  |

|   |     |                                                          | 01  |

|   | 6.3 |                                                          | 02  |

|   |     | · ·                                                      | 03  |

|   |     |                                                          | 04  |

|   |     |                                                          | 07  |

|   |     |                                                          | 07  |

|   | 6.4 | ±                                                        | 09  |

| _ |     |                                                          |     |

| 7 |     | 0                                                        | 111 |

|   | 7.1 |                                                          | 11  |

|   | 7.2 | 0                                                        | 13  |

|   |     | 0                                                        | 13  |

|   |     |                                                          | 14  |

|   |     | 0                                                        | 14  |

|   |     |                                                          | 16  |

|   |     |                                                          | 17  |

|   | 7.3 | 1                                                        | 18  |

|   | 7.4 | 1                                                        | 23  |

|   |     |                                                          | 23  |

|   |     | 7.4.2 Worst-Case Data Distributions 1                    | 26  |

|   | 7.5 | Summary                                                  | 27  |

xiv

| CONTENTS |                                                               |     |  |  |  |

|----------|---------------------------------------------------------------|-----|--|--|--|

| 8        | Summary, Conclusions and Outlook                              | 129 |  |  |  |

| A        | Related PublicationsA.1ConferencesA.2JournalsA.3Book Chapters | 136 |  |  |  |

CONTENTS

xvi

### Chapter 1

## Introduction

#### **1.1** Motivation for Parallel Computation

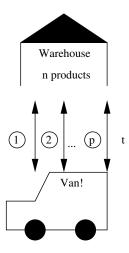

Parallel computing is based on the simple real world observation that generally several workers can finish a job much faster than only one. The speed*up* that can be achieved by parallelism mainly depends on the structure of the job. If we consider a set of products, which has to be carried from a warehouse into a van, then it is clear that several workers can accelerate this job optimally by their number. In the following analysis of the example, we neglect the arithmetic precision and assume that the products can be assigned evenly to the workers. If we have n products and p workers, then every worker carries n/p products to the van. Since each worker has to do the same amount of work, we can say that the work is balanced in an optimal manner. In computer science, the problem of distributing the work evenly is called *load balancing*. If t is the time a worker needs to carry one product to the van, then the total time for loading the van is tn/p. If only one worker (p = 1) loads the van, then the total time is tn. In computer science, the *speed-up* of a parallel algorithm is defined as the quotient between the running time of the fastest sequential algorithm for a problem and the running time of the parallel algorithm. Hence, if we use p workers then the job has a speed-up of tn/(tn/p) = p. This can be regarded as optimal, because we invest p workers and the job runs p times faster, see Fig. 1.1.

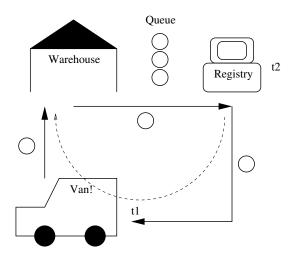

The described problem can be extended easily in the way that it is not possible to achieve an optimal speed-up. We simply introduce the rule that each product has to be unregistered in a global registry, and that only one worker in each time step can unregister one product, see Fig. 1.2.

Now, the time for carrying one product to the van is  $t_1$  and the time for the unregistering process is  $t_2$ . If we simply transfer the above algorithm then the van is completely loaded as soon as the last worker has loaded the n-th product. Hence, the total time is  $n/p(pt_2+t_1) = nt_2 + nt_1/p$ , because for each of his n/p products the last worker has to wait  $(p-1)t_2$  until he can

Figure 1.1: Simple warehouse example: Each worker has to carry n/p products from the warehouse to the van.

unregister his current product, which costs an additional time  $t_2$ . However, the optimal time would be  $n/p(t_1 + t_2)$ . Clearly, in this case, the registry is the bottleneck. Each worker has to unregister its actual product, carries it to the van and then returns to fetch the next product. If the time needed for the unregistering process is much bigger than the time to carry the product to the van and to fetch a new one (and there are many complex warehouse programs around) then the total time needed gets close to the time only one worker would need. As we can see in this worst-case scenario, the in-

Figure 1.2: Simple warehouse example: Each worker has to carry n/p products from the warehouse to the van. Additionally, each product has to be unregistered.

vestment in p workers might be useless depending on the structure of the job. On the other hand, a smart warehouse manager would try to invest in his warehouse software to reduce the time  $t_2$  or he would spend money in several registry workstations (e.g. p) to break the bottleneck and to increase the speed-up. Actually, the described process is nothing else than designing a *parallel algorithm*.

Now, the example does only cover the problem of distributing the work on several workers. After the distribution, the workers can do their job independently. Unfortunately, in the majority of problems it is necessary that the workers have to communicate during the execution of their job. They need partial results produced by the other workers, or knowledge only one worker has. Hence, the minimization of *communication cost* is a crucial issue for the design of a parallel algorithm. Assuming, that in our example there is one worker who has to tell all the other workers each time they come back to the warehouse which product they have to fetch next (perhaps because he is the only person who has the product list). We call this worker the boss. Let us denote the time needed for this communication as  $t_3$ . Then the total time for loading the van is  $nt_1/p + nt_2 + nt_3/p$ , because in each of the n/p steps such a communication operation has to be done. Therefore, it is obvious that  $t_3$  has great influence on the total time. Now the questions are, which way of communication reduces t<sub>3</sub> maximally? Moreover, how much time does the communication take?

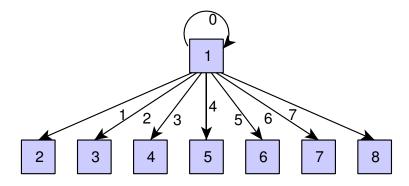

One possibility is that the boss tells each worker separately the next product he has to fetch. Let c be the time needed to tell a worker which product he has to take next. Hence, in this algorithm  $t_3 = pc$ , if we assume that he has to tell himself the next product, too (see Fig. 1.3).

Figure 1.3: Simple Communication Strategy (p = 8): The boss (node 1) tells each worker separately which product he has to fetch next. The numbers at the directed edges denote the time step at which the call is done.

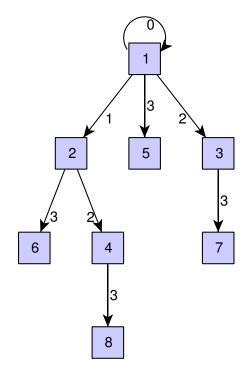

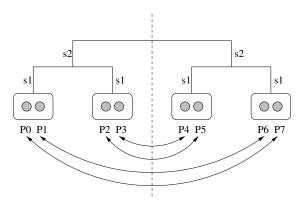

Another possibility is that the boss tells only one worker what they and the rest have to do. Then again each of the workers who know which products have to be fetched next (incl. the boss) chooses one additional worker and tells him what he and the rest have to do. This is repeated until all workers know which product to take next. The described communication pattern resembles a tree with p nodes and is illustrated in Fig.1.4. The height of the tree represents the number of time steps needed to perform the communication operation. Since in each step, the number of processors that know which products have to be fetched is doubled and each step takes time c, the total time for this operation is  $c \lfloor \log p \rfloor$ , which is better than the time for the last method.

Figure 1.4: Tree Communication Strategy (p = 8): The boss (node 1) starts telling the next products to another worker. Then each worker (incl. the boss) tells another innocent worker which product to fetch. This is repeated until all workers know what to fetch next. The numbers at the directed edges denote the time step at which the call is done.

Although the example seemingly has nothing to do with computers, it introduces some main concepts of parallel computing as there is the problem of *load balancing*, the problem of achieving as much *speed-up* as possible, and last but not least, the problem of minimizing *communication cost*.

Looking at the area of computer science, there is no unique mapping for the workers to a certain object. For example concerning parallel algorithms, the workers would have been denoted as processors. However, a processor is just a piece of hardware which can be used to make calculations. Hence, it may be better to say that a worker is a process which works on a processor. Nevertheless, perhaps the processor itself is not just one piece of hardware it may consist of several smaller units which are able to perform micro-operations of the process in parallel. Therefore, within a certain part of each process, again we have workers. Further, on a higher level, workers can also be regarded as applications consisting of multiple processes and working on sets of processors or computers. Again, the workers appear on a different level. In the following, we show in which levels parallelism can be exploited by computer programs and outline which is the level of interest for the thesis.

#### **1.2** Levels of Parallelism in Computer Programs

Concerning the execution of computer programs, the use of parallelism can be recognized in all levels, starting from applications down to microprocessor instructions [74].

- 1. Application level: Several applications can be executed in parallel on a set of computers. They all have their own working environment and do not know anything from each other. Normally, they even do not work on the same problem. Operating systems are responsible for the parallel or scheduled execution of such applications.

- 2. Process level: Applications may consist of several processes. Largely simplified a process can be seen as running program with a set of resources, which includes a private memory space. Parallelism in this level means that the processes try to solve the same problem together. In order to speed-up the application, they are executed on different processors at the same time. While their execution they are able to communicate with each other which is generally necessary to solve the common problem.

- 3. Thread level: Processes may have several threads of execution. A thread is an activity within a process and has its own control flow but shares resources and memory space with other threads in the same process. With the help of the operating system, it is possible to map the threads to different processors. Hence, several threads are executed in parallel and are able to communicate using the shared-memory space of the process.

- 4. Microprocessor instruction level: Microprocessor instructions can be executed in parallel, if the processor provides multiple pipelines for the execution of instructions (super-scalar). Optimizing compilers for super-scalar processors can analyze the instruction stream and are able to organize parallel executions by reordering of the instructions

in the streams. Another example for parallelism of instructions in this level are vector processors. They are able to perform the same operation on a vector of arguments at the same time. Consecutive vector operations can be executed in an overlapping parallel manner by the vector pipeline.

In the first level, operating systems are responsible for the execution and scheduling of applications. Parallelism is not used to reduce the time to solve a common problem; it is used to provide multitasking on computers which is a very important feature for workstations and servers.

The fourth level is a very low-level parallelism and is therefore normally done by compilers.

Hence, the levels of interests for developers of parallel programs are two and three, and this is the topic of this thesis. In these levels, it is possible to reduce the time for solving a problem by using several processes and threads on multiple processors or computers.

In the following sections, we will discuss the elements involved in the process of building a parallel application and we will show their interactions and interfaces.

### 1.3 Design Chain for Efficient Parallel Applications

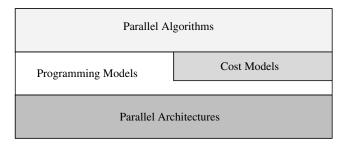

The development of parallel algorithms and applications is based on several assumptions on the existing environment. The elements that play a key-role for the design of an efficient parallel application are illustrated in Fig. 1.5 and explained next.

Figure 1.5: Elements of the parallel design process

• First, there is the *parallel computer* or *supercomputer* itself. There are many different architectures for parallel computers. Each *parallel architecture* has its own characteristics, which should be considered by a program. Critical issues are how the processors are connected to the memory banks, what kind of processors are used, or how fast they can communicate. We give a detailed overview in Chapter 2.

- Second, there are several *programming models* for the design of parallel programs. A programming model defines the way processes or threads can communicate or synchronize on the parallel computer. For each model, there might be several different libraries and each library has to be implemented for each parallel computer. Several programming languages can be used, but the focus in the area of high-performance computing is on C/C++ and FORTRAN. The closer a programming model fits to the underlying hardware the more efficient the implementation of the programming model can be realized.

- Third, a more abstract representation of the programming model is necessary with which algorithms can be designed and analyzed theoretically. We call these models *cost models*. They try to reflect the main characteristics of the underlying programming model and parallel architecture in a way that a significant cost analysis of an algorithm is possible. Hence, algorithms are getting comparable and running times are getting predictable only by the results of their theoretical analysis.

- The fourth key-role element are parallel algorithms. They are the building blocks of parallel libraries and applications. It is very important to develop efficient algorithms for problems, which appear very often, in order to offer a large collection for the development of complex applications.

Ideally, algorithms are designed on top of cost models. These cost models reflect the main characteristics of the underlying parallel architecture and therefore the analysis is a good estimate for the running time of following implementations. In order to implement algorithms developed on cost models, appropriate programming models must exist that implement the cost models. The programming models themselves consist of programming languages and libraries, and should fit to the underlying architecture as much as possible. In practice, programmers very often develop and implement algorithms using programming models directly. In this case, the usage of a cost model is implicitly done through the programming model. Hence, there is no accurate analysis of the algorithm, which implies the risk of being inefficient.

Obviously, in this chain from the algorithm to the architecture there might be loss of performance if the various levels do not fit properly. For example if the cost model is inadequate towards the architecture because it assumes an infinite memory space or an infinite number of processors, then the resulting algorithms might be useless or at least inefficient in practice for the underlying architecture. There might also be problems if the programming model does not fit to the architecture. If it assumes a sharedmemory for all processors but the underlying architecture consists of distributed memories, then there will be a loss of performance because the implementation of the programming model has to simulate a shared-memory.

Hence, there is a gap between parallel algorithms and real parallel machines and the models should try to build a bridge. A lot of important work has been done in order to build general-purpose cost models to overcome this gap. These models were called parallel bridging models. We will describe the most popular in Chapter 2.3.

Nearly independent of this process a huge variety of programming models were developed. The most important will be reviewed in Chapter 2.4.

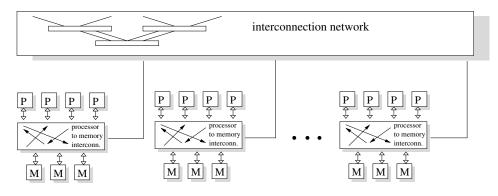

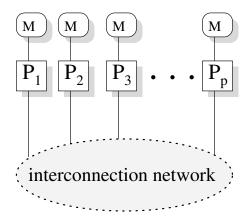

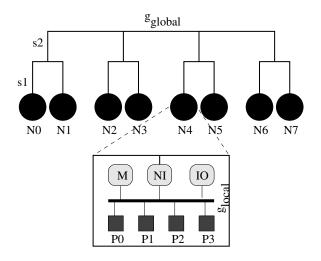

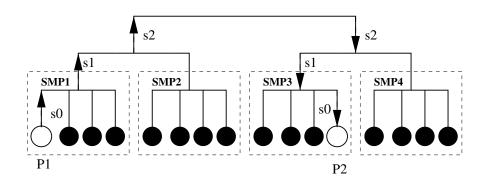

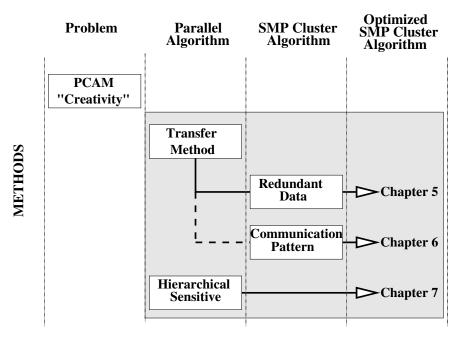

### **1.4** The Contribution of the Thesis

In the center of the thesis, there is a parallel architecture called Clusters of Symmetric Multi-Processors (*SMP Clusters*). This is a hybrid architecture concerning the way processors are connected to each other. The building blocks are multiprocessor nodes with shared-memory. These nodes are connected by an interconnection network. Hence, there is parallelism within the nodes exploiting shared-memory and between the nodes using the interconnection network, which creates a *parallel hierarchy* (see Fig. 1.6). Basically, the communication between nodes is more expensive than within the nodes which leads to a *hierarchical communication architecture*.

Figure 1.6: Outline of the SMP Cluster architecture

There has been an enormous trend towards this architecture in the last years because of economical and performance reasons. Together with the emerging of this architecture a debate has been started which programming model is the best for it. There are several approaches, which will be reviewed in Chapter 2.4.2. Most of these approaches just ignore the new communication hierarchy and make it transparent to the algorithm and application developer. One advantage of such a strategy is that existing programs can easily be ported by more or less recompiling. Another advantage is that a huge variety of programming models and libraries are thus available for the architecture.

On the other hand stopping the consideration of the architecture at the programming model level means to waste the chance of optimizing on the algorithmic level and thus, to get the maximal performance possible. Hence, the main part of the thesis it to show possibilities for algorithmic optimization on SMP Clusters. As explained above, the main difference of SMP Clusters is based in the communication hierarchy and the parallel hierarchy. Therefore, all optimizations presented in the thesis are based on communication operations and different data distributions.

According to the design chain for parallel applications depicted in Section 1.3, we define a cost model for SMP Clusters. This cost model reflects the main characteristics of SMP Clusters and of the *hybrid-programming model* that will be presented in Chapter 2.4.2. This model suggests using one process per SMP node. The processes can communicate over the interconnection network. Within the processes, multiple threads are responsible for the parallel execution. As mentioned earlier, there has been a lot of work in finding a general-purpose cost model for all architectures. Indeed, these models reflect the most important characteristics of parallel computers but not the communication hierarchy and the hybrid memory model of SMP Clusters. Despite of that our approach is to extend the most accepted general-purpose cost model named bulk synchronous parallel (BSP) model [76] with the characteristics of SMP Clusters.

The described design chain provides a quantitative basis for the analysis of algorithms and guarantees by the similarity of cost model, programming model and architecture that a transfer to an efficient implementation is possible. Although this is a pre-condition for developing parallel applications, it is not a methodology how parallel algorithms can be designed. Hence, there is a need for design methods that help the developer to create parallel algorithms for given problems. With the help of the methods parallel algorithms can be developed. By using the cost model for the analysis, different approaches can be evaluated and compared. In [31], a general methodology for developing parallel algorithms is presented. We use this methodology as a framework for the over-all design process of parallel algorithms for SMP clusters. We will review this methodology, show its usage for SMP clusters and present additional methods

- for the design of parallel algorithms from scratch,

- for an efficient transfer of parallel algorithms to SMP clusters and

- for optimizing distinct aspects of these algorithms.

All these methods can be regarded as additional modules of the over-all design methodology. They can be applied at different stages of the whole design process from the problem to a highly optimized algorithm for SMP

clusters. Some only assume the problem definition (or a sequential algorithm) as an input, some a parallel algorithm and others can be applied to optimize SMP cluster algorithms. Hence, in order to design an optimized parallel algorithm for SMP clusters, the methods can be applied consecutively one after the other, which corresponds to a path through the set of methods.

We will explain generally all methods whereby the explanation is supported by simple examples. Further, we present case studies for more complex algorithms that present several paths through the design methods.

In each case study, we present theoretical, and if necessary, practical evaluations of the algorithms. The cost model serves as a super-model for the analysis. It is not always necessary to use the whole model for the analysis of the sample algorithms. For each case study, another reduced instance of the cost model is sufficient, which makes the analysis more feasible.

In this sense, the thesis is an attempt to show the possibility of unifying the theoretical and the practical aspects of developing parallel applications considering SMP Clusters as example.

#### **1.5** Structure of the Thesis

- In Chapter 2, we will give an overview on parallel architectures, motivations for building SMP-Clusters, parallel bridging models and programming models for SMP-Clusters.

- We proceed in Chapter 3 with a theoretical cost model for SMP Clusters called KNUMA and show an analysis for broadcast problems.

- In Chapter 4, we review and present several methods for designing and optimizing parallel algorithms for SMP clusters.

- Chapter 5 is the first case study for designing algorithms for SMP Clusters. After using a method for transferring well-proven parallel algorithms, it is observed how data redundancies can be exploited in order to improve the performance of the algorithm. Hence, the case study is called *exploitation of redundant data*. The sample problem is the parallel dense matrix-vector-multiplication.

- Chapter 6 illustrates the second case study called *adaptation of communication patterns* using the example of parallel matrix transpose.

- In Chapter 7, the case study presents the method of *hierarchical-sensitive design*. We address to the problem of integer sorting using parallel radix sort.

- General conclusions can be found in Chapter 8.

### Chapter 2

# Overview on Parallel Architectures, Models and Libraries

### 2.1 Architectures

Computer architectures are classified according to their ability to realize the parallel program execution. Flynn's taxonomy [29] divides computer architectures into four categories depending on how the instruction streams and the data streams are implemented. A more actual interpretation of this taxonomy is given in [77].

- Single instruction stream and single data stream (SISD): These are systems containing one CPU and therefore are able to execute one instruction stream serially. Large mainframes that consist of multiple processors do also belong to this class, because each processor executes unrelated instruction streams. Hence, they can be regarded as a couple of SISD machines working on different data spaces.

- 2. Single instruction stream and multiple data stream (SIMD): Systems of this class are characterized by a huge number of processors, ranging from thousands to ten-thousands. There is a global clock and in each lock-step all processors execute the same instruction on different data. In one lock-step, one instruction works on many data items in parallel.

- Multiple instruction stream and single data stream (MISD): Theoretically, in such a machine different instructions are executed on the same data at the same time. Until now, no practical machine of this type has been constructed.

4. Multiple instruction stream and multiple data stream (MIMD): Several instructions are executed in parallel on different data. In contrast to the multi-processor SISD machines, the instruction streams and the data streams are related. They are all parts of a global program and hence work on the solution for a common problem. MIMD systems are used for running sub-tasks in parallel with the aim to reduce the time to solve the global problem. Most systems belong to this class and hence a further criteria will be introduced later to make a more accurate classification.

Although Flynn's taxonomy is very useful, it does not cover how processors are connected to each other and to memory units. However, parallel architectures are made up from multiple processors and memory units.

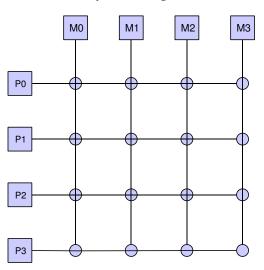

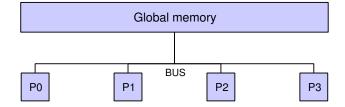

Networks that are connecting processors with memory units are called *dynamic networks* [52], because they are built using switches and communication links. Paths among processors and memory banks are established by connecting communication links dynamically using the switching elements. Extreme but realistic examples of these networks are the  $n \times n$  *crossbar*, see Fig. 2.1, and the *bus connection*, see Fig. 2.2. The former is a common hardware channel that can link only a pair of modules at a time. It has the least circuital complexity and cost. The latter is a square matrix of switches that can connect up to n non-conflicting pairs of modules. It achieves the highest connectivity at the highest circuital cost.

Figure 2.1:  $n \times n$  crossbar switch, with n = 4.

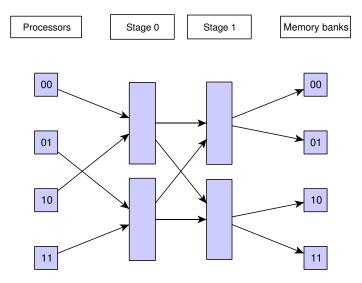

Many systems use structures that are in between these two, as a compromise between practical scalability and performance. These networks are called *multi-stage crossbars*. They are networks made of smaller interconnected crossbars. The *omega network* is illustrated in Fig. 2.3 as an exam-

Figure 2.2: Bus-based architecture with no cache

ple for a multi-stage network. The advantage of such networks in contrast to complete crossbar is that it only needs  $(n/2) \log n$  switching elements instead of  $n^2$ .

Figure 2.3: Example for a multi-stage crossbar: A complete omega network connecting four processors with four memory banks.

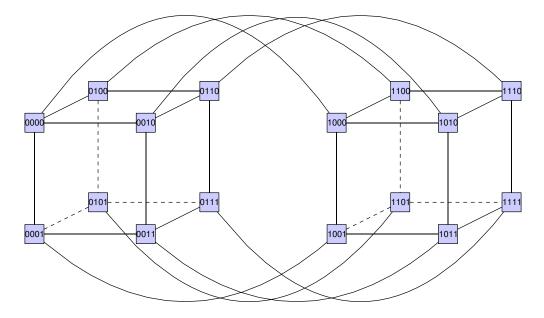

Networks which are connecting processors are called *static networks*, because they consist of point-to-point communication links among processors. Typical structures for these networks among others are the Fattree, Hypercube, 2D or 3D Meshes, and multi-stage networks like Butterfly, Omega, or Clos networks. Fig. 2.4 shows eight processors connected by a 4D hypercube interconnection network. These and derived networks are in use within a wide range of parallel computers and network elements like e.g. hi-speed-switches. Detailed descriptions and design issues of static and dynamic networks are discussed in [52, 53].

Efficiency of communication is measured by two parameters, *latency* and *bandwidth*. Latency is the time taken for a communication to complete, and bandwidth is the rate at which data can be communicated. Latency can also be imagined as the time needed to communicate zero data. In a

Figure 2.4: Example for a static network: A 4D hypercube connected architecture.

simple world, these metrics are directly related. For communication over a network, however, we must take into account several factors like physical limitations, communication start-up and clean-up times, and the possible performance penalty from many simultaneous communications through the network. A rule of thumb is that latency depends on the network geometry and implementation, and bandwidth increases with the length of the message, because of the decreasing influence of fixed overheads.

As already mentioned above, almost all modern parallel computers belong to the MIMD class of parallel architectures. Basically, this means that processing nodes can execute independent programs over possibly different data. The MIMD class is subdivided in [77] according to the characteristic of the physical memory, into SM MIMD (*shared-memory* MIMD) and DM MIMD (*distributed-memory* MIMD).

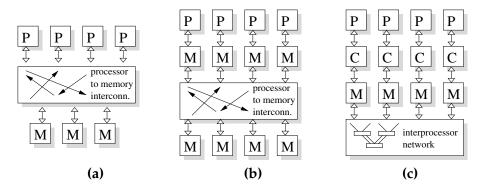

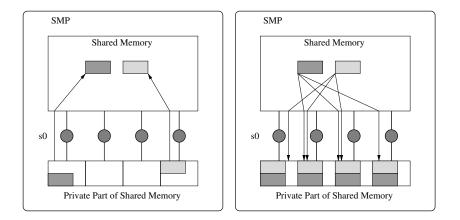

The memory banks of a SM MIMD machine form a common address space, which is actively supported by the network hardware (see Fig. 2.5a). Different processors can interfere with each other when accessing the same memory module, and race conditions may show up in the behavior of the programs. Therefore, hardware lock and update protocols have to be used to avoid inconsistencies in memory and among the caches <sup>1</sup>. Choosing the right network structure and protocols are critical design issues, which drive the performance of the memory system. Larger and larger shared-memory

<sup>&</sup>lt;sup>1</sup>We do neither analyze in depth here cache coherence issues, nor multi-stage networks, nor cache-only architectures [52].

Figure 2.5: Overall structure of DM and SM MIMD architectures. (a) Generic SM MIMD machines have multiple processors and memory banks (not necessarily the same number) – (b) example of NUMA SM MIMD with multiple local and global memory banks, and a bus interconnection – (c) example of a MIMD architecture composed of single-processor nodes and a more sophisticated interconnection network. Depending on the network implementation, this can be either a DM-MIMD or a NUMA SM-MIMD architecture.

machines lead to difficult performance problems.

Multi-stage crossbars are getting more and more important with an increasing number of processors in shared-memory machines. If a multi-stage crossbar connects the processors and each processor has some local memory banks, there is a memory hierarchy within the shared-memory of the system (see Fig. 2.5b).

Systems in which the access from a processor to some of the memory banks, e.g. its local one, is faster than access to the rest of the memory are called NUMA systems (Non-Uniform Memory Access), in contrast with UMA systems. Shared-memory architectures (both UMA and NUMA ones) are often called Symmetric Multiprocessors (SMP), because the architecture is fully symmetric from the point of view of the running programs.

In contrast to the shared-memory machines, in a distributed-memory machine each processing node has its own address space. Therefore, it is up to the user to define efficient data decompositions and explicit data exchange patterns for the applications. Each processing node has its own local memory, so distributed memory architectures obviously belong to the NUMA architectural class (see Fig. 2.5c). The network is inherently slower than local memory; hence, we have a memory hierarchy in DM MIMD machines, too. However, distributed-memory architectures are less demanding with respect to the interconnection network <sup>2</sup>, so they are much more

<sup>&</sup>lt;sup>2</sup>For instance, coherence and locking problems are not dealt with at the hardware level. This removes some design constraints, and reduces communication overheads.

| Classification | count | share  |

|----------------|-------|--------|

| MPP            | 211   | 42.2 % |

| Cluster        | 149   | 29.8 % |

| Constellations | 139   | 27.8 % |

| SMP            | 1     | 0.2 %  |

Table 2.1: Summary of the TOP500 list (June 2003) of the fastest supercomputers according to the architectural classification.

scalable than the shared-memory ones.

In recent years, a strong trend has emerged in the field of high performance computers towards two kinds of architectures, (1) clusters of vector computers and (2) clusters of scalar uni- and multiprocessors. Looking at the list of the fastest 500 supercomputers in the world [60], the majority of them belongs to these two classes, with the latter steadily gaining more share.

Especially clusters of SMP nodes (SMP clusters) are a more and more emerging architecture for building parallel computers. In the latest list of the fastest 500 supercomputers (June 2003), 29.8 % of the supercomputers were classified as clusters, whereby de facto all these systems are clusters of SMP nodes. Additionally, SMP clusters are also found in the other classes of the summary of the TOP500 list depicted in Table 2.1. Bell and Gray [8] define *constellations* as clusters of nodes with larger shared-memory multiprocessor nodes, where each node is more powerful than the casual PC uni- or dual-processor nodes. Additionally, clusters of vector processors do also belong to this class, because the performance of modern vector processors is comparable to that of larger SMP nodes. Massively parallel processing systems (MPP) can be characterized roughly by a very large number of processors with local memory that are connected by a special interconnection network. Nevertheless, despite of that, systems that clearly have the SMP cluster structure were classified as MPP systems in the list. For example, the number four in the current list, the *IBM ASCI White*, is an IBM RS/6000 SP system that consists of 512 nodes and each node has 16 Power3 processors. Probably this system was classified as a MPP system, because the number of 8192 processors is very high and typical for MPP systems. Hence, much more than 30% of the supercomputers in the list are SMP clusters. Further, 8 out of the fastest 10 supercomputers are SMP clusters, too. We did not count the number one of the list, the Earth-Simulator, because its 640 8-way nodes consist of vector processors. However, despite of that, these numbers clearly underline the importance of the SMP cluster architecture.

At different scales, these SMP cluster systems can be classified both as DM and as SM MIMD architectures, because SM MIMD processing nodes are connected together to form a larger DM machine. The result is a powerful parallel architecture, which combines the high effectiveness of small shared-memory computing nodes with the scalability of the distributed memory parallelism among the nodes.

In principle, we could classify SMP clusters either as SM or as DM MIMDs depending on the existence of a common address space abstraction for all the processors, eventually provided by firmware or software layers. However, even if a shared space is provided this way, algorithms that exploit memory locality within SMP nodes incur much fewer communication overheads, and can achieve a better performance. Thus, SMP clusters have a *parallel hierarchy* of at least two levels. The number of levels may actually be higher, depending on the topology of the intra- and inter-node networks.

Grid or meta-computing technologies, where supercomputers or clusters of workstations are connected with each other to run applications, result in even more levels and a less regular parallel hierarchy. Broadband connections, ranging from local area networks to geographic ones, add more levels to the hierarchy, with different communication bandwidth and latency [32].

Summing up, in modern parallel architectures we have the following hierarchy of memory and communication layers.

- shared-memory

- distributed-memory

- local area network

- wide area network

Each one of these layers may exhibit hierarchical effects, depending on its implementation choices.

The effects on latency and bandwidth of the parallel hierarchy are similar and combine with those of the ordinary memory hierarchy, consisting of several levels starting at the processor's registers up to the hard disks. A crucial observation is that there is no strict order among the levels of these two hierarchies, which we can easily exploit to build a unitary model. For instance in some systems, we can see that the communication layers (both SM and DM based ones) provide a bandwidth lower than main memory, and in some cases lower than that of local I/O. However, their latency is usually much lower than that of mechanical devices like disks. Thus, different access patterns lead to different relative performances of communication and I/O.

Assessing the present and future characteristics of the parallel hierarchy [19] and devising appropriate cost and programming models to exploit it

are among the main open issues in modern parallel/distributed computing research.

#### 2.1.1 Motivation and Technological Perspective

As we explained in the last section, parallel computing architectures employ memory and parallel hierarchies. In the following, we summarize arguments that explain the trend towards even more hierarchical architectures than SMP clusters, and we discuss possible future developments.

In [48] some main advantages of SMP cluster architectures are found, most of them being technological and economical considerations.

- Standard off-the-shelf processors are getting faster and faster, even with respect to special purpose architectures. Because of their quantity, development and production costs are getting lower and lower. Special purpose processors (e.g. vector processors) are no longer able to achieve significant advantages over the commercial product lines, so architectures employing multiple commodity processors are going to be preferred for massively parallel processing machines (MPP), SMP and cluster machines.

- A similar effect shows up due to mass-production of network and architecture components. For clusters of small SMP, which employ standard network and structural components, there will be a very fast capability growth. This will lead to cheaper and more scalable networks, which can compete with the special purpose connection structures of MPPs. As soon as the performance advantages of the special purpose networks will disappear, the SMP clusters will get into the position of the MPPs.

- SMP clusters are scalable and expandable. Their architecture is intrinsically more scalable, and it is practically expandable by adding more nodes and/or upgrading processing nodes. While it is usually not possible to add processors in a SMP or MPP, it is easy to build a SMP cluster step by step.

- The size of memory, disk subsystem capacity and bandwidth are critical resources in a supercomputer. A greater total memory size and number of disks characterize SMP clusters. Hence, it is possible to have more active jobs, which even have larger data storage available.

- Most software for MPPs or SMPs can easily be ported to SMP clusters achieving similar efficiency. With the knowledge of software for SMP machines and the already existing software for MPPs, it should be possible to provide a powerful environment for parallel software

#### 2.1. ARCHITECTURES

development and execution. We will give an overview of the efforts in this direction in Section 2.4.

Some of the preceding considerations have been recognized years ago, while others are a more recent discovery. According to Bell and Gray [8], the trend will last for more than a while. They depict a scenario of the evolution of parallel computer and computing grid architectures, which is described below.

Users of supercomputers and proprietary software will turn to proprietary clusters using standard software. The clusters themselves are built from commodity hardware and software. There will be an era of supercomputing mono-culture where every company or research institute will build its own supercomputer.

As a downside, applications that need a large shared-memory perform poorly on distributed-memory systems. For that reason, computing centers will migrate to super-application centers. They will provide application centric vector- or cellular supercomputers for special research areas.

Computing centers will have the role of fully distributed computation brokers. The centers will decide where, when and on which platform a job is executed, exploiting Grid [32] or meta-computing techniques to manage clusters of supercomputers. Furthermore, computing centers will become super-data centers. They will provide, through a faster Internet, storage for peta-scale data sets with efficient access methods. With the increased Internet bandwidth, cluster and Grid technologies will merge in the next decade. Hence, all LAN-based workstations will become part of clusters, all of them together are forming the Grid.

According to this prediction, hierarchical parallel systems will be the principal computing structure in the future. Therefore, investments and research in programming environments and in understanding hierarchical parallelism are very important. In this sense, this thesis can be regarded as one step in this effort.

#### 2.2 Computational Cost Models

In sequential computing algorithms were designed using the classical random access machine (RAM) model which is based on the Von Neumann computer. Due to the more complex structure of modern computers, concerning memory hierarchy this model does not properly account with the cost of memory access. Hence, more complex multi-level computational models have been suggested to obtain better predictions of the algorithm's practical behavior. The most known of them is the PDM model [78].

In parallel computing, we have a similar situation. A first approach of modeling a parallel computer was to extend the RAM model with multiple processors using a shared-memory. The resulting computational cost model is called the parallel random access machine (PRAM) model [30]. It is based on several precise assumptions on the parallel computer:

- There is an unlimited number of processors (simple processing units with local memories) that run the same program. They are connected by an unlimited global shared-memory where they can read and write in parallel.

- PRAM machines can be differentiated according to their capability

of accessing the shared-memory. Read and write operations can be

either exclusive or concurrent. In case of a concurrent write rules are

defined what happens to the memory location if several processors

manipulate it in the same time step.

- The execution of a program is done synchronously. There is a global clock and in each time step, all active processors always complete one instruction.

Hence, the PRAM model assumes the same costs for a computation step, a local memory access and a global memory access. Practical aspects like the memory hierarchy and bandwidth constraints due to certain interconnection networks are completely ignored. The focus is solely set on concurrent program execution. These assumptions cause the model to be very independent of the properties of a specific architecture, and hence the PRAM model can be used as an effective model for analyzing the abstract computational complexity of problems. On the other hand, these assumptions are not realistic for the majority of architectures described in Section 2.1. Real MIMD machines are much more complex and hence using the PRAM model contains the risk of getting misguiding results with respect to real computational costs.

Several extensions have been developed for the PRAM model in order to get the theoretical computational cost closer to real performance. A survey on these derived models is given in [35]. A second research part in parallelism considers efficiency of communication in interconnection networks. Different network structures are compared according to their ability to perform communication operations and costs concerning hardware elements. It is possible to embed certain network structures into others and hence to simulate efficient networks algorithms in the environment of other structures. Despite of that, networkspecific algorithms are often too tied to the geometry of the network and show a sub-optimal behavior when running on a different network structure.

A third research track started in the 1990s introducing the class of parallel bridging computational cost models. These models try to describe the main properties of complex parallel architectures without being too complex or being too imprecise. On the one hand, these models do not want to be architecture-specific, but on the other side they want to predict the real performance of a program as accurate as possible. These models are subject of the following section.

# 2.3 Parallel Bridging Models

Computational cost models have to find the right balance between abstraction and accuracy. They should reflect the real behavior of parallel algorithms without making the analysis too complex. A parallel cost model can be regarded as useful, if the results of analyses can be confirmed in practice. A model that achieves this aim without being limited to a special architecture is called *parallel bridging model*. A PBM separates the development of efficient algorithms and software from the underlying architecture. Several models of this class have been developed in the 1990s. They use a more abstract approach in modeling the interconnection architecture.

The most well-known and accepted PBM was introduced by Valiant [76]. The following goals of a PBM were formulated in the context of its initial definition.

- **Cost measure** A PBM has to define a cost measure that describes the individual operation costs and hence, guides the development of algorithms. In fact, the cost measure is the main element of the model because it defines which characteristic of a parallel computer is considered. The model should be independent of a specific architecture and technology, but it should reflect the fundamental constraints of parallel machines.

- **Efficient universality** Implementations of PBM algorithms on real machines should not lead to great loss of performance. While logarithmic simulation losses have to be avoided, constant bounded inefficiency is within the tolerance.

Figure 2.6: The BSP abstract architecture.

- **Neutrality** A PBM has to be neutral concerning the number of processors. Although the results are expressed asymptotically, they should be applicable to ranges from only a few to millions of processors. Hence, an approximate result is justified if the factors are small.

- **Portability** The programmer should not have to care about low-level problems like explicit memory management, complex communication operation or synchronizations. Thus, there has to be a programming model, which is close to the PBM supporting high-level functions.

- **Parallel slackness** A PBM algorithm designed for v virtual processors should be optimally simulated on p physical processors if p is smaller than v (e.g.  $v = p \log p$ ). This enables to overlap communication and computation of different virtual processors on a wide range of interconnection networks.

#### 2.3.1 The Bulk Synchronous Parallel Model

The *bulk synchronous parallel model* (BSP) (as described in [3]) is a set of processors with local memories and a complete interconnection network, see (Fig. 2.6). A router delivers messages between pairs of processors. The model uses three parameters to describe a BSP computer, see Fig. 2.7. The number p of processors, a latency parameter L, which is the maximum latency of a message or synchronization in the network, and a parameter g, which is the basic throughput of the network or the bandwidth inefficiency.

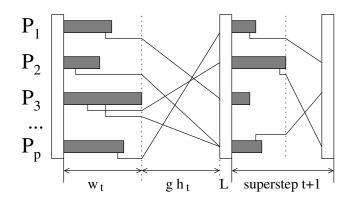

A BSP computation consists of *supersteps*. During a superstep, processors can do computations on their data in local memory and can send and receive a certain amount of messages with each other. Messages sent during superstep t are received only at the beginning of superstep t+1. Fig. 2.8 shows the phases of a superstep. Each superstep consists of computation

| pnumber of processorsLmessage latency / synchronizationgcost parameter for message-passing                                                                                      |                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| for processor i in superstep t                                                                                                                                                  |                                                                                                                                           |

| $\begin{split} & w_{i,t} \\ & \lambda_{i,t} \\ & \mu_{i,t} \\ & w_t = \max_i w_{i,t} \\ & h_t = \max_i \max\{\lambda_{i,t}, \mu_{i,t}\} \\ & w_t + g \cdot h_t + L \end{split}$ | local computation<br>num. of sent messages<br>num. of received messages<br>global work in t<br>global routing in t<br>cost of superstep t |

Figure 2.7: BSP symbols and parameters.

phase (gray stripes), a communication phase with varying communication pattern, and the constant bounded synchronization time L (white stripes).

The table of Fig. 2.7 summarizes the composition of the costs in the BSP model for a superstep t and a processing node i.

Let  $h_{i,t} = max(\lambda_{i,t}, \mu_{i,t})$  be the largest number of messages sent or received by processor i during the current superstep t. The communication pattern (set of all point-to-point communications in a superstep) has size  $h_t = max_i h_{i,t}$  for superstep t, and is called *h*-relation.

With these parameter definitions,  $w_t$  and  $h_t$  are the largest w and h values in superstep t.

Hence, the total time of a superstep is  $w_t+g \cdot h_t+L$ , because, this can be regarded as an upper bound, if we assume that synchronization after each superstep is only enforced when actually needed for the correctness of the algorithm. We can analyze a BSP algorithm by computing  $w_t$  and  $h_t$  for each superstep. If the algorithm terminates in T supersteps, the *local work*

Figure 2.8: BSP superstep execution

$W = \sum_{t} w_{t}$  and the *communication volume*  $H = \sum_{t} h_{t}$  of the algorithm lead to the cost estimate  $W + g \cdot H + L \cdot T$ .

Another useful criterion for judging BSP algorithms is the *c-optimality*. If  $T_{seq}$  is the time of the best known sequential algorithm then a BSP algorithm is called *c-optimal*, if  $W = c \cdot T_{seq}/p$  and  $g \cdot H + L \cdot T = o(T_{seq}/p)$  for a small constant  $c \ge 1$ .

In the next section, we will address to other parallel bridging models. We will present the CGM model, which is the closest to the BSP, the LogP and the QSM model.

#### The Coarse-Grained Multicomputer

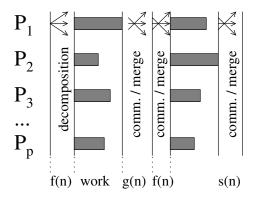

The *coarse-grained multicomputer* (CGM) model is similar to the BSP model concerning the superstep-based execution scheme of a parallel algorithm. In contrast to BSP, there are only two parameters. The number of processors p, and the problem size, n. Each node has O(n/p) local memory. No assumptions are made for the network structure. Algorithms exploit a reduced number of fixed, parallel primitives for computation and communication, which can be efficiently implemented over various interconnection networks.

Each CGM algorithm has a parametric cost depending on n and p. Further, the costs for the used primitives depending on the problem size n are added. In Fig. 2.9, they are represented by f, g, s. Depending on the network topology the time for each primitive can be inserted (e.g. complexity of exchanging O(n/p) keys in a hypercube of diameter  $\log_2 p$ , see Fig. 2.4 for an example of an hypercubic structure).

A CGM superstep consists of three phases. The decomposition phase (the work is distributed using parallel primitives), the local computation phase, and a merge phase (results of local computation are communicated) also exploiting the parallel primitives. The task of formulating a CGM al-

Figure 2.9: CGM supersteps

gorithm is to decompose the problem into coarse-grain independent subproblems using these global portable parallel primitives. The algorithm, which needs the smallest number of supersteps is the best.

During the years, in the common use CGM has become close to BSP. In recent works (e.g. [25, 26]), CGM algorithms are often defined as a special class of BSP algorithms.

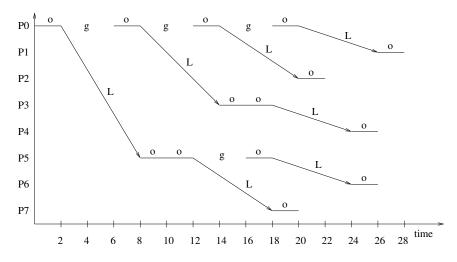

#### 2.3.2 LogP Model

The LogP model [24] ignores the network geometry like the BSP model. The processors communicate through point-to-point messages. The model defines four parameters. An upper bound on communication latency L, the overhead involved in a communication (for sending and receiving messages) o, a gap parameter g (the time a processor has to wait before the next communication can be started), and the number of processors P. As we can see the notion of the parameters are responsible for the name LogP. In the original model (*stalling* LogP) an explicit capacity constraint is assumed for the network. No processor can have more than  $\lceil l/g \rceil$  messages in transit to it at the same time. Senders that hurt the constraint are assumed to stall. *Non-stalling* LogP dismisses the network capacity constraint. Therefore, in the stalling model the messages are considered to be of small fixed length.

The design and analysis of LogP algorithm is more complex than for other models, because of the unstructured and asynchronous nature and the capacity constraint requirement. There are comparably fewer results with LogP, even if most basic algorithms (e.g. broadcasts or summing) have been analyzed in great detail. An outline of the LogP-broadcast is presented in Fig. 2.10.

Figure 2.10: LogP-Model: Optimal broadcast tree for P = 8, o = 2, g = 4 and L = 6. Processor P0 is the initiator of the broadcast.

### 2.3.3 QSM model

The *queuing shared-memory* (QSM) [34] model can be seen both as a PRAM evolution and as a shared-memory variant of the BSP. Each processor has a local memory. The processors communicate by reading and writing to a shared global memory. The execution of an algorithm is divided into phases, with reads and writes. The reads and writes to the shared-memory are posted at the end of each phase. Concurrent read (or writes, but not both) to a memory location are allowed.

Each processor performs a certain amount of local computation within each phase. The cost of each phase is defined as  $max(m_{op}, g \cdot m_{rw}, \kappa)$ , where  $m_{op}$  is the largest amount of local computation in the phase,  $m_{rw}$  is the largest number of read and writes from the same processor, and  $\kappa$  is the *maximum contention* of the phase, i.e. the maximum number of colliding accesses on any location in that phase. The gap parameter g has the same meaning as in the LogP model , whereas latency is not explicitly considered, and it is substituted by the contention. A large number of algorithms designed for variants of the PRAM can be easily mapped on the QSM.

#### 2.3.4 A Comparison of Parallel Bridging Models

It is possible to compare the models by emulating one model on the other. Emulations are *work-preserving* if the product  $p \cdot t$  (processors per execution time) on the emulating machine is the same (within a constant factor) as that on the machine being emulated. If the emulating machine has fewer processors than the emulated one, the emulation is characterized by a certain slowdown. This slowdown is O(f), if we are able to map an algorithm, running in t time on p processors, to one running on  $p' \leq p/f$  processors in time  $t' = O(t \cdot (p/p'))$ . If the slowdown is O(1) then the emulation has at most a constant factor of inefficiency.

Ramachandran [62] presents asymptotic slowdown results in a recent survey. If there are several work-preserving emulations with small slowdown, this indicates that these models are equivalent in their use as cost models for real parallel machines.

But despite of that, some models are preferable since there exist adequate programming models for them and since a more abstract view of the algorithm's structure and communication patterns allows an easier design and analysis.

From this point of view, the LogP and the QSM are less suitable, because they provide too much low-level analysis concerning communication behavior and memory access. It is very difficult to analyze complex algorithms with these models. The QSM can be used to evaluate the practical performance of many existing PRAM algorithms. A disadvantage of QSM is that it disregards hierarchical structures of the computation, and it has an abstract but fine-grain approach to communication cost.

In contrast, the BSP and the CGM can be used easier for the design of parallel algorithms, because of their coarse grain nature and their abstraction of complex communication patterns. Further, several programming models and software tools have been designed with which it is possible to implement BSP algorithms directly. The two main libraries are the Paderborn University BSP library (PUB) [15] and the Oxford BSPlib [42]. These are special libraries, which pretend to close the gap between the BSP model and real parallel machines. Unfortunately, these programming models do not play a major role in practical parallel programming. However, BSP algorithms can also be implemented using more "standard" programming models, which we will describe in section 2.4.

In the following section, we will have a look on extensions of the BSP model with respect to hierarchical network structures.

#### 2.3.5 Parallel Bridging Models and Hierarchical Parallelism

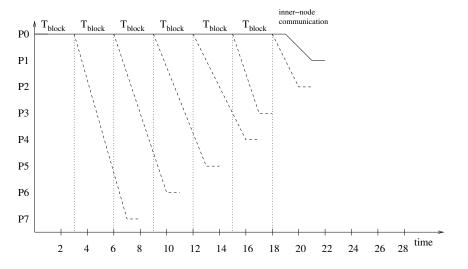

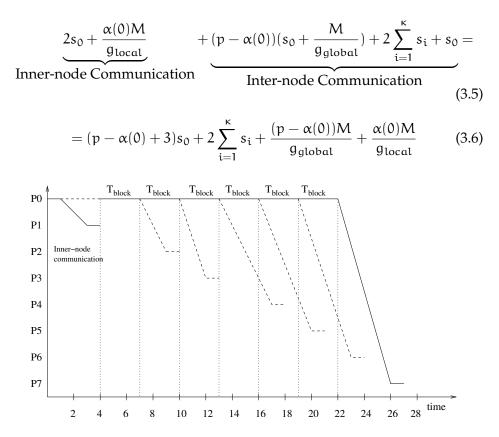

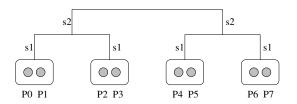

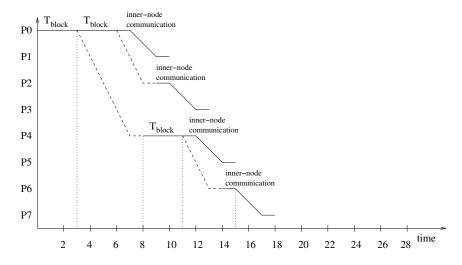

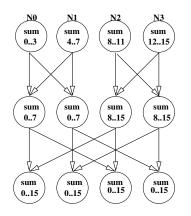

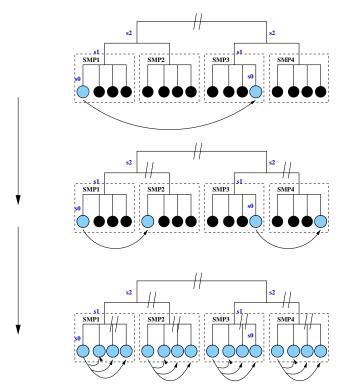

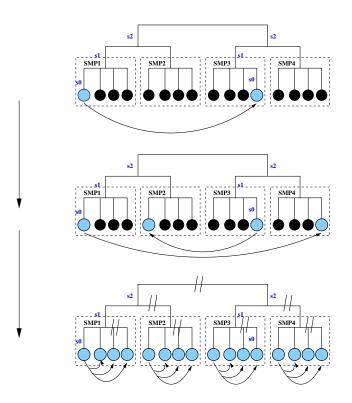

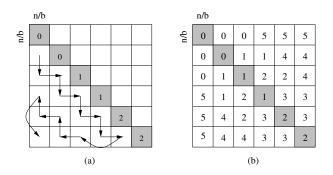

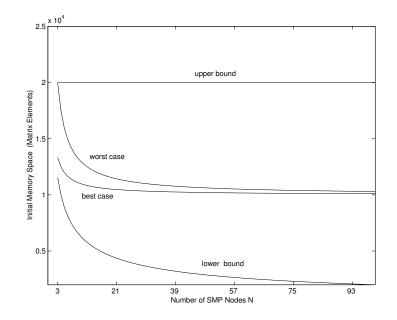

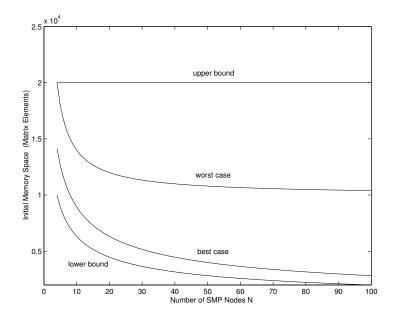

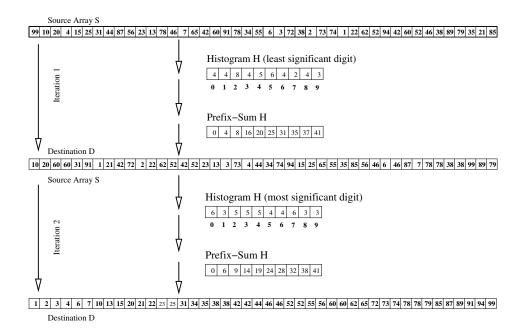

After the introduction of PBMs, research in this area focused on enhencing their accuracy. This is done by exploiting the concepts of processor locality and block-oriented communications.