OULU 2018 C 667

Tuomo Hänninen

ACTA

# DETECTION ALGORITHMS AND FPGA IMPLEMENTATIONS FOR SC-FDMA UPLINK RECEIVERS

UNIVERSITY OF OULU GRADUATE SCHOOL; UNIVERSITY OF OULU, FACULTY OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING; CENTRE FOR WIRELESS COMMUNICATIONS

## ACTA UNIVERSITATIS OULUENSIS C Technica 667

TUOMO HÄNNINEN

## DETECTION ALGORITHMS AND FPGA IMPLEMENTATIONS FOR SC-FDMA UPLINK RECEIVERS

Academic dissertation to be presented with the assent of the Doctoral Training Committee of Information Technology and Electrical Engineering of the University of Oulu for public defence in the OP auditorium (L10), Linnanmaa, on 10 July 2018, at 12 noon

## UNIVERSITY OF OULU, OULU 2018

Copyright © 2018 Acta Univ. Oul. C 667, 2018

Supervised by Professor Markku Juntti

Reviewed by Professor Kapil Dandekar Doctor John McAllister

Opponent Professor Jarmo Takala

ISBN 978-952-62-1968-4 (Paperback) ISBN 978-952-62-1969-1 (PDF)

ISSN 0355-3213 (Printed) ISSN 1796-2226 (Online)

Cover Design Raimo Ahonen

JUVENES PRINT TAMPERE 2018

## Hänninen, Tuomo, Detection algorithms and FPGA implementations for SC-FDMA uplink receivers.

University of Oulu Graduate School; University of Oulu, Faculty of Information Technology and Electrical Engineering; Centre for Wireless Communications *Acta Univ. Oul. C 667, 2018* University of Oulu, P.O. Box 8000, FI-90014 University of Oulu, Finland

#### Abstract

The demand in mobile broadband communications is increasing dramatically. It is expected that 1000 times more mobile-network capacity will be needed within 10 years. Multiple-input, multiple-output (MIMO) antenna configuration and spatial multiplexing are among the essential techniques for reaching the targets. This creates motivation for study of advanced receivers for combating inter-antenna interference (IAI) and inter-symbol interference (ISI). While various receiver structures have been extensively considered for MIMO receivers, the emphasis has been on those operating in downlink orthogonal frequency-division multiple access (OFDM) systems, wherein ISI is not a problem.

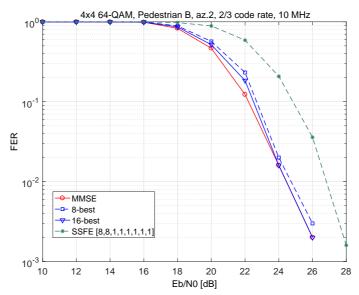

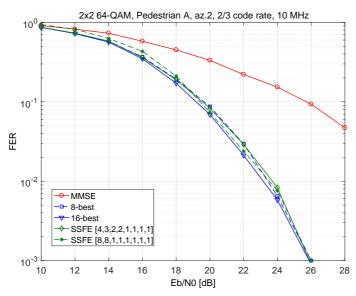

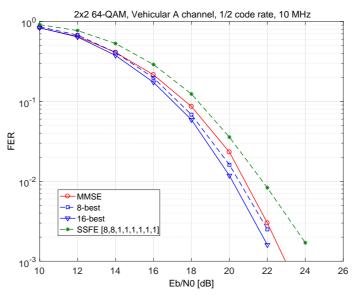

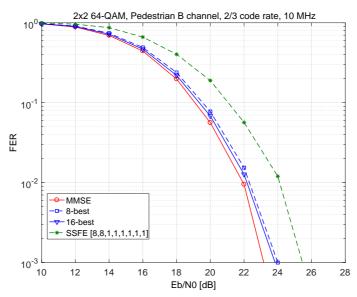

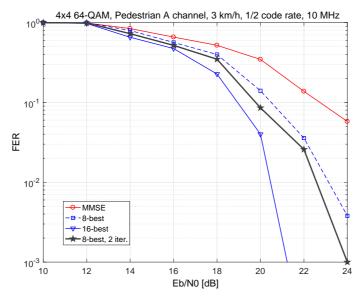

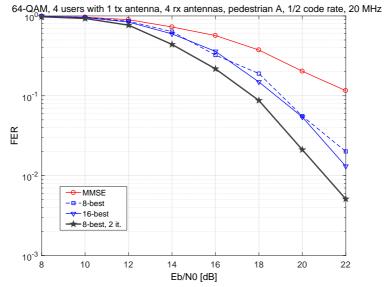

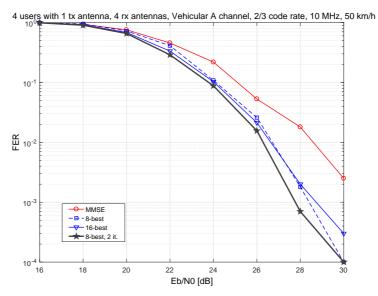

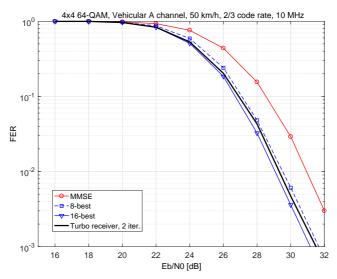

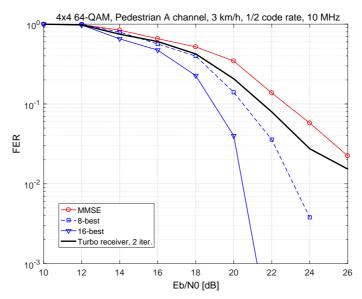

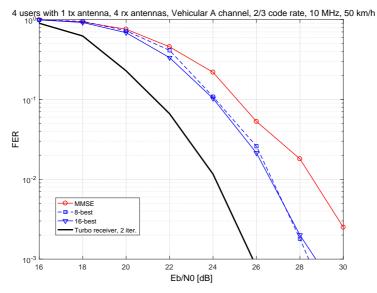

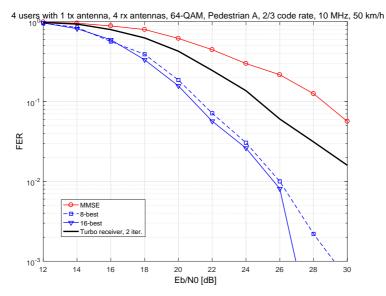

In this thesis, advanced receiver structures for single-carrier frequency-division multiple access (SC-FDMA) uplink systems were studied and analysed. Various receivers were compared via MATLAB simulations, with the objective being to gain solid understanding of how they perform in different channel environments. An efficient combination of IAI and ISI equalisation for SC-FDMA receivers is proposed. The proposed receiver architecture is shown to be a considerable improvement over the conventional linear minimum mean-square error (LMMSE) receiver. Several MIMO detector algorithms and their performance–complexity characteristics are presented. The *K*-best algorithm with a list size of 8 is shown to be the best option for practical MIMO detector implementation of this receiver in the  $4 \times 4$  MIMO 64-level quadrature amplitude modulation (QAM) scenario.

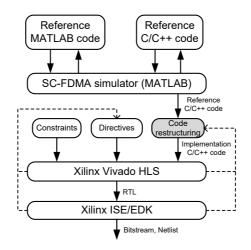

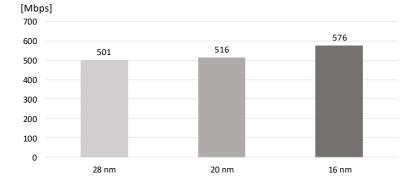

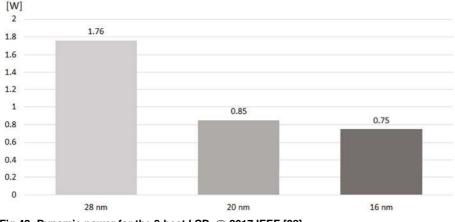

The second objective involved examining the implementation aspects of the 8-best receiver to achieve good understanding of the complexity of various implementation architectures. It emerged that avoiding the sorting operation in the 8-best list sphere detector (LSD) tree-search algorithm implementation is not recommendable in the 4 × 4 MIMO 64-QAM scenario. Several field-programmable gate array (FPGA) implementations were carried out, with a range of high-level synthesis (HLS) tools. It is shown that HLS tools have improved significantly and are especially favourable for prototyping of large designs. Additionally, the importance of FPGA technology selection is addressed. Smaller silicon technology should be exploited if base-station baseband processing power consumption is to be minimised. The potential performance or complexity-related gain with the latest FPGAs should be taken into account in comparison of the performance–complexity characteristics of the algorithms. Differences of a few tens of per cent in estimated complexity or performance between two algorithms are often below the threshold of what can be gained or lost in the practical implementation process.

*Keywords:* detection, FPGA, high-level synthesis, LTE, MIMO, receiver, SC-FDMA, uplink

## Hänninen, Tuomo, Tukiasemien moniantennivastaanotinalgoritmit tulevaisuuden matkaviestinjärjestelmissä.

Oulun yliopiston tutkijakoulu; Oulun yliopisto, Tieto- ja sähkötekniikan tiedekunta; Centre for Wireless Communications *Acta Univ. Oul. C 667, 2018* Oulun yliopisto, PL 8000, 90014 Oulun yliopisto

Tiivistelmä

Tiheään asuttujen kaupunkien uudet langattomat palvelut tarvitsevat tietoliikenneverkkoja, jotka mahdollistavat suuremman tiedonsiirtonopeuden ja kapasiteetin kuin sen, jonka nykyiset mobiiliverkot voivat tarjota. On arveltu, että mobiiliverkkojen kapasiteetin tarve tuhatkertaistuu seuraavan kymmenen vuoden aikana. Tuhatkertainen kapasiteetti on arvioitu saavutettavan kasvattamalla kolmea eri osa-aluetta kymmenkertaiseksi: taajuusspektrin määrä, spektrin käytön tehokkuus sekä tukiasematiheys. Tämä väitöskirja keskittyy spektrin käytön tehokkuuden kasvattamiseen. Moniantennitoteutus (multiple-input multiple-output, MIMO) on siinä välttämätön. MIMO-tekniikkaa hyödyntävien solukkojärjestelmien tukiasemavastaanottimissa tarvitaan melko monimutkainen kanavakorjain sekä ilmaisin, joiden algoritmien optimointi ja toteutus ymmärretään vielä sangen puutteellisesti.

Väitöskirjatutkimuksen päätavoitteena on tutkia edistyksellisiä vastaanotinrakenteita, joilla saavutetaan LTE-A-standardin tavoitetiedonsiirtonopeus kohtuullisella kompleksisuudella. Työs-sä keskitytään ns. nousevaan siirtosuuntaan (uplink) eli päätelaitteesta tukiasemaan tapahtuvaan tiedonsiirtoon, jossa käytetään yhden kantoaallon taajuusjakomonikäyttötekniikkaa (single-carrier frequency-division multiple-access, SC-FDMA) ortognaalisen taajuusjakomonikäytön (orthogonal frequency division multiple access, OFDMA) sijaan. Eri vastaanotinrakenteita ja näiden ilmaisinalgoritmeja vertaillaan tietokonesimuloinnein MATLAB-ympäristössä. Väitöskirjassa ehdotetaan kaksiosaista vastaanotinrakennetta, jossa antennien välinen keskinäishäiriö (inter antenna interference, IAI) ja symbolien välinen keskinäisvaikutus (intersymbol interference, ISI) poistetaan kahdessa eri vaiheessa. Tietokoneimulaatiot osoittavat ko. rakenteen parantavan suorituskykyä huomattavasti perinteiseen lineaariseen keskineliövirheen minimoivaan (linear minimum mean square error, LMMSE) vastaanottimeen verrattuna. Nk. *K* parasta polkua valitsevan MIMO-ilmaisinalgoritmin listan koolla kahdeksan todetaan tarjoavan 4  $\times$  4 MIMO 64-tasoisen kvadratuuriamplitudimodulaation (quadrature amplitude modulation, QAM) ympäristössä parhaan kompromissin suorituskyvyn ja kompleksisuuden suhteen.

Käytännön toteutettavuuden kannalta keskitytään ohjelmoitavaan digitaalipiiritoteutukseen (field-programmable gate array, FGPA) ja ns. korkean tason synteesi (high-level synthesis, HLS) -työkalujen käyttöön vastaanottimen suunnittelussa. *K* parasta polkua valitsevan MIMO-ilmaisinalgoritmin arkkitehtuurivertailut osoittavat, että sinänsä vaativaa lajittelualgoritmia ei aina kannata yrittää välttää kirjallisuudessa aikaisemmin ehdotetulla ratkaisulla. Useita eri HLS työkaluja käytetään FPGA toteutuksissa ja todetaan että työkalut ovat kehittyneet huomattavasti viimeisen kahdeksan vuoden aikana. Lisäksi todetaan, että 16 nm viivanleveyden piireillä voidaan saavuttaa noin 15 % suurempi ilmaisunopeus ja 60 % pienempi tehonkulutus verrattuna 28 nm viivanleveyttä käyttäviin piireihin. Erityisesti potentiaali tehonkulutuksen minimoiseksi kannattaa hyödyntää, mikäli signaalinkäsittely näyttelee merkittävää roolia vastaanottimen kokonaistehonkulutuksessa. Kokonaisuutena todetaan, että toteutukseen liittyvät valinnat sekä vaikutus lopputulokseen, tulisi ottaa huomioon jo algoritmien valinnassa. Pieni ero kahden eri algoritmin suorituskyvyn välillä häviää helposti toteutusvaiheen ratkaisujen vaikutusten alle.

Asiasanat: FPGA, HLS, ilmaisin, LTE, MIMO, SC-FDMA, vastaanotin

To my parents

## Preface

The research for this thesis was carried out at the Centre for Wireless Communications (CWC) of the University of Oulu, in Finland. I want to thank Professor Ari Pouttu, Dr Harri Posti, Professor Matti Latva-aho, Professor Jari Iinatti, and Professor Markku Juntti, the directors of CWC during my studies, for giving me the opportunity to work in such an inspiring environment and for enabling me to conduct my thesis-related research in parallel with my project-management responsibilities. I am especially grateful to my supervisor, Professor Juntti, for his invaluable guidance and encouragement throughout my postgraduate research and to Dr Posti for his support and inspiring discussions. In addition, I would like to thank follow-up group leader Dr Harri Saarnisaari and also Dr Johanna Vartiainen for overseeing my research. Matti Raustia deserves thanks for hiring me to work at CWC in 2008. Finally, I would like to express my gratitude to the reviewers of this thesis: Professor Kapil Dandekar, from the USA's Drexel University, in Philadelphia, and Dr John McAllister, from the UK's Queen's University, in Belfast, Northern Ireland. Their comments significantly improved the quality of the thesis.

The bulk of the work presented in this thesis was carried out in the Cooperative MIMO Techniques for Cellular System Evolution (CoMIT) and Baseband and System Technologies for Wireless Evolution (BASE) projects. I would like to thank project managers Visa Tapio (Lic. Tech.) and Dr Janne Janhunen, the technical steering group members, and my colleagues in those projects. I am grateful to my co-authors in related work Dr Johanna Ketonen, Dr Juha Karjalainen, Dr Janhunen, Muhammad Saad Saud, and Hamid Yadegar Amin for the co-operation.

I would like to extend particular thanks to my office-mates and regular lunch and travel companions Dr Harri Pennanen, Markku Jokinen, Hannu Tuomivaara, Raghavendra Sathyanarayana, Dr Ville Niemelä, Dr Teemu Nyländen, Dr Maria Kangas, Dr Timo Bräysy, Dr Marja Matinmikko, Marko Mäkeläinen, Kalle Lähetkangas, Dr Konstantin Mikhaylov, Dr Juha Petäjäjärvi, Jarkko Kaleva, Dr Heikki Karvonen, Dr Jussi Haapola, and Juho Markkula for the refreshing moments and fruitful discussions. The administrative support of Antero Kangas, Elina Komminaho, Kirsi Ojutkangas, Eija Pajunen, Hanna Saarela, Mari Lehmikangas, Renata Kordasne Sebö, Jari Sillanpää, Dr Juha-Pekka Mäkelä, and Timo Äikäs is highly appreciated too.

The research for this thesis was funded through project financing from the Finnish Funding Agency for Technology and Innovation (Tekes), Elektrobit, Nokia, Nokia Siemens Networks, and Xilinx, which is gratefully acknowledged. I was privileged to receive personal grants for doctoral studies from the following Finnish foundations: Emil Aaltosen Säätiö, Walter Ahlströmin Säätiö, Riitta ja Jorma J. Takasen Säätiö, and Tauno Tönningin Säätiö. This support encouraged me to carry on with my research work, and it is recognised with gratitude.

My deepest gratitude goes to my parents, for their love, support, and encouragement of education. The love they have given throughout my life is invaluable. I wish to thank my brother and all my friends who have been there for me. Finally, my warmest thanks go to my girlfriend for the love and understanding she has given me over these years.

Oulu, 19 June 2018

Tuomo Hänninen

## Abbreviations

| 1G                         | first generation                                      |

|----------------------------|-------------------------------------------------------|

| 2G                         | second generation                                     |

| $2.5\mathrm{G}$            | second and a half generation                          |

| 3G                         | third generation                                      |

| $3.5\mathrm{G}$            | third and a half generation                           |

| 3GPP                       | 3rd Generation Partnership Project                    |

| 3GPP2                      | 3rd Generation Partnership Project 2                  |

| $4\mathrm{G}$              | fourth generation                                     |

| $4.5\mathrm{G}$            | fourth and a half generation                          |

| $5\mathrm{G}$              | fifth generation                                      |

| $5 \mathrm{G} \mathrm{NR}$ | fifth-generation New Radio                            |

| 8-PSK                      | higher-order phase-shift keying (8 phases)            |

| AMPS                       | Advanced Mobile Phone Service                         |

| APP                        | a posteriori probability                              |

| ASIC                       | application-specific integrated circuit               |

| AWGN                       | additive white Gaussian noise                         |

| BER                        | bit error rate                                        |

| BF                         | breadth-first                                         |

| BPSK                       | binary phase-shift keying                             |

| BLAST                      | Bell Laboratories Layered Space-Time                  |

| BRAM                       | block random-access memory                            |

| BS                         | base station                                          |

| BW                         | bandwidth                                             |

| CDMA                       | code-division multiple access                         |

| CDMA2000                   | brand name for the IMT-MC mobile technology standards |

| cdmaOne                    | brand name for the IS-95 standard                     |

| CP                         | cyclic prefix                                         |

| CSI                        | channel state information                             |

| CWC                        | Centre for Wireless Communications                    |

| D-BLAST                    | Diagonal Bell Laboratories Layered Space-Time         |

| D-AMPS                     | Digital AMPS                                          |

| DAC                  | digital-to-analogue converter                         |

|----------------------|-------------------------------------------------------|

| DFT                  | discrete Fourier transform                            |

| DL                   | downlink                                              |

| DSP                  | digital signal processor                              |

| ED                   | Euclidean distance                                    |

| EDGE                 | Enhanced Data Rates for GSM Evolution                 |

| ETSI                 | European Telecommunications Standards Institute       |

| FD                   | frequency domain                                      |

| FDD                  | frequency-division duplex                             |

| FDMA                 | frequency-division multiple access                    |

| FEC                  | forward error control                                 |

| FER                  | frame error rate                                      |

| $\mathbf{FF}$        | flip-flop                                             |

| $\mathbf{FFT}$       | fast Fourier transform                                |

| FPGA                 | field-programmable gate array                         |

| GMSK                 | Gaussian minimum-shift keying                         |

| GPRS                 | General Packet Radio Service                          |

| GPU                  | graphics processing unit                              |

| GS                   | Gram–Schmidt                                          |

| $\operatorname{GSM}$ | Global System for Mobile Communications               |

| HDL                  | hardware description language                         |

| HLS                  | high-level synthesis                                  |

| HSDPA                | High Speed Downlink Packet Access                     |

| HSPA                 | High Speed Packet Access                              |

| HSPA+                | Evolved High Speed Packet Access                      |

| HSUPA                | High Speed Uplink Packet Access                       |

| HW                   | hardware                                              |

| IAI                  | inter-antenna interference                            |

| IDFT                 | inverse direct Fourier transform                      |

| IEEE                 | Institute of Electrical and Electronics Engineers     |

| $\mathbf{IFFT}$      | inverse fast Fourier transform                        |

| IMT-2000             | International Mobile Telecommunications 2000          |

| IMT-A                | International Mobile Telecommunications Advanced      |

| IMT-MC               | International Mobile Telecommunications Multi-Carrier |

| I/O                  | input/output                                          |

|                      |                                                       |

| IoT    | Internet of Things                                          |

|--------|-------------------------------------------------------------|

| IP     | Internet Protocol                                           |

| IR-SD  | increasing-radius sphere detector                           |

| IS-54  | Interim Standard 54                                         |

| IS-95  | Interim Standard 95                                         |

| IS-136 | Interim Standard 136                                        |

| ISI    | inter-symbol interference                                   |

| ITU    | International Telecommunication Union                       |

| kGE    | kilo-gate equivalent                                        |

| LLR    | log-likelihood ratio                                        |

| LMMSE  | linear minimum mean-square error                            |

| LORD   | layered orthogonal lattice detector                         |

| LP     | linearly precoded                                           |

| LPWAN  | Low-Power Wide-Area Network                                 |

| LSD    | list sphere detector                                        |

| LTE    | Long-Term Evolution                                         |

| LTE-A  | Long-Term Evolution Advanced                                |

| LTE-M  | Long-Term Evolution Advanced for machine-type communication |

| LUT    | lookup table                                                |

| MAP    | maximum a posteriori                                        |

| MGS    | modified Gram–Schmidt                                       |

| MIMO   | multiple-input, multiple-output                             |

| MISO   | multiple-input, single-output                               |

| ML     | maximum likelihood                                          |

| MMS    | Multimedia Message Service                                  |

| MMSE   | minimum mean-square error                                   |

| MNO    | mobile network operator                                     |

| MS     | mobile station                                              |

| MSE    | mean-square error                                           |

| NMT    | Nordic Mobile Telephony                                     |

| NTT    | Nippon Telegraph and Telephone                              |

| OFDM   | orthogonal frequency-division multiplexing                  |

| OFDMA  | orthogonal frequency-division multiple access               |

| OSIC   | ordered successive interference cancellation                |

| PAPR   | peak-to-average-power ratio                                 |

|        |                                                             |

| PDC                    | Personal Digital Cellular                                    |

|------------------------|--------------------------------------------------------------|

| PED                    | partial Euclidean distance                                   |

| PSK                    | phase-shift keying                                           |

| QAM                    | quadrature amplitude modulation                              |

| QoS                    | quality of service                                           |

| QPSK                   | quadrature phase-shift keying                                |

| QRD                    | QR decomposition                                             |

| RAM                    | random-access memory                                         |

| RTL                    | register-transfer level                                      |

| $\mathbf{R}\mathbf{X}$ | receiver                                                     |

| SC-FDMA                | single-carrier frequency-division multiple access            |

| SD                     | sphere detector                                              |

| SEE                    | Schnorr–Euchner enumeration                                  |

| SIC                    | successive interference cancellation                         |

| SIMO                   | single-input, multiple-output                                |

| SINR                   | signal-to-interference-plus-noise ratio                      |

| SIR                    | signal-to-interference ratio                                 |

| SISO                   | single-input, single-output                                  |

| $\mathbf{SM}$          | spatial multiplexing                                         |

| SNR                    | signal-to-noise ratio                                        |

| $\operatorname{SoC}$   | system on a chip                                             |

| SSFE                   | selective spanning with fast enumeration                     |

| STC                    | space-time code                                              |

| TD                     | time domain                                                  |

| TDD                    | time-division duplex                                         |

| TDMA                   | time-division multiple access                                |

| TTA                    | transport-triggered architecture                             |

| TU                     | typical urban                                                |

| TX                     | transmitter                                                  |

| UE                     | user equipment                                               |

| UL                     | uplink                                                       |

| UMTS                   | Universal Mobile Telecommunications System                   |

| V-BLAST                | Vertical Bell Laboratories Layered Space-Time                |

| VB                     | Viterbo–Boutros                                              |

| VHDL                   | Very High Speed Integrated Circuit Hardware Description Lan- |

|                        |                                                              |

|                              | guage                                                                |

|------------------------------|----------------------------------------------------------------------|

| VLSI                         | very-large-scale integration                                         |

| W-CDMA                       | Wideband Code Division Multiple Access                               |

| WiMAX                        | Worldwide Interoperability for Microwave Access                      |

| WLAN                         | wireless local area network                                          |

| $\mathbf{ZF}$                | zero-forcing                                                         |

|                              |                                                                      |

| $ \cdot $                    | absolute value                                                       |

| $\left\ \cdot\right\ _{2}$   | Euclidean norm                                                       |

| $(\cdot)^{\mathrm{H}}$       | Hermitian transpose                                                  |

| $(\cdot)^{-1}$               | inverse                                                              |

| $(\cdot)^{1/2}$              | square root                                                          |

| $\operatorname{Im}(\cdot)$   | imaginary part of the argument                                       |

| $\ln(\cdot)$                 | natural logarithm                                                    |

| $\operatorname{Re}(\cdot)$   | real part of the argument                                            |

| $p(\cdot)$                   | likelihood function                                                  |

| $\operatorname{chol}(\cdot)$ | Cholesky factorisation                                               |

| $E\{\cdot\}$                 | expectation                                                          |

| $\otimes$                    | Kronecker product                                                    |

| $\operatorname{diag}(\cdot)$ | diagonal values of matrix                                            |

| $\operatorname{tr}\{\cdot\}$ | matrix trace operator                                                |

|                              |                                                                      |

| $b_k$                        | kth transmitted bit                                                  |

| $C_0$                        | sphere radius                                                        |

| $\mathbb{C}$                 | complex plane                                                        |

| e                            | mean-square error                                                    |

| $\mathbf{F}_R$               | block diagonal DFT matrix $\mathbf{I}_R \otimes \mathbf{F}_K$        |

| $\mathbf{F}_{K}$             | DFT matrix                                                           |

| н                            | channel matrix                                                       |

| $\mathbf{H}^{r,t}$           | subchannel matrix between $t$ th transmit and $r$ th receive antenna |

| Ĥ                            | target channel matrix                                                |

| $\mathbf{I}_R$               | identity matrix                                                      |

| K                            | DFT size                                                             |

| K                            | list size of the tree-search detector                                |

| L                            | length of the channel impulse response                               |

|                              |                                                                      |

| L                       | list of candidate symbol vectors                          |

|-------------------------|-----------------------------------------------------------|

| Q                       | matrix with orthogonal columns                            |

| ∼<br>R                  | upper triangular matrix with positive diagonal elements   |

| R                       | number of receive antennas                                |

| r                       | received signal vector                                    |

| $\mathbb{R}$            | real plane                                                |

| S                       | transmitted symbol vector candidate                       |

| $\mathbf{s}^i$          | set of closest constellation points                       |

| T                       | number of transmit antennas                               |

| $\mathbf{U}$            | eigenvectors of $\Sigma_w$                                |

| $\mathbf{v}$            | complex Gaussian noise                                    |

| x                       | transmitted signal                                        |

| $\mathbf{Z}$            | equalised signal                                          |

| $\mathbf{z}_{w_{[n]}}$  | whitened symbol vector                                    |

| $\mathbf{z}_w$          | whitened vector                                           |

| $\mathbf{z}'_{w_{[n]}}$ | white<br>ned symbol vector multiplied by matrix ${\bf Q}$ |

| []                      |                                                           |

| Γ                       | frequency-domain channel matrix                           |

| $\Lambda$               | eigenvalues of $\Sigma_w$                                 |

| $\lambda$               | wavelength                                                |

| ${old \Sigma}_w$        | residual interference                                     |

| $\sigma^2$              | noise variance                                            |

| $\Phi$                  | channel matrix (equivalent channel)                       |

| Ω                       | MMSE filter coefficients                                  |

|                         |                                                           |

| cc                      | clock cycle                                               |

| dB                      | decibel                                                   |

| 0                       | degrees                                                   |

| $\operatorname{Gbps}$   | gigabits per second                                       |

| GHz                     | gigahertz                                                 |

| GOPS                    | giga-operations per second                                |

| Hz                      | hertz                                                     |

| k                       | thousand                                                  |

| kbit                    | kilobit                                                   |

| kHz                     | kilohertz                                                 |

|                         |                                                           |

| kilometres per hour |

|---------------------|

| megabits per second |

| megahertz           |

| microsecond         |

| milliwatt           |

| nanojoule           |

| nanosecond          |

| microsecond         |

| second              |

|                     |

## Contents

| ostra            | act                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ivist            | telmä                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| refac            | ce                                                                                                                                              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Abbreviations 11 |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| onte             | nts                                                                                                                                             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Inti             | roduction                                                                                                                                       | <b>21</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.1              | Evolution of mobile networks                                                                                                                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.2              | Multiple-antenna communications                                                                                                                 | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.3              | SC-FDMA technology                                                                                                                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.4              | Aims, outline and contributions of this thesis                                                                                                  | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Lite             | erature review                                                                                                                                  | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1              | MIMO detection                                                                                                                                  | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | 2.1.1 Optimal detection                                                                                                                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | 2.1.2 Suboptimal linear and non-linear detection                                                                                                | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | 2.1.3 Tree-search algorithms                                                                                                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2              |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | 2.2.1 QR decomposition                                                                                                                          | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | 2.2.2 Sorting                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | 2.2.3 Technology                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | 2.2.4 High-level synthesis                                                                                                                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\mathbf{Sys}$   | stem model and receiver structures                                                                                                              | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1              | System model                                                                                                                                    | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

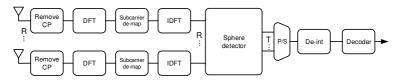

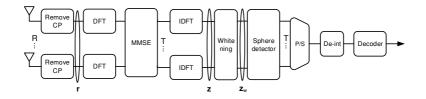

| 3.2              | SC-FDMA MIMO receiver structures                                                                                                                | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.3              |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

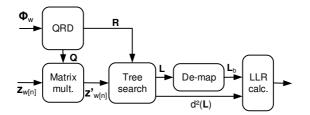

| 3.4              | Sphere detector                                                                                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.5              | 5 Possible receiver modifications                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | 3.5.1 Antenna grouping                                                                                                                          | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | 3.5.2 LLR iteration                                                                                                                             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sim              |                                                                                                                                                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.1              |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.2              | $2 \times 2$ MIMO system                                                                                                                        | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | ivis<br>reface<br>bbre-<br>onte<br>Int<br>1.1<br>1.2<br>1.3<br>1.4<br>Lit<br>2.1<br>2.2<br>Sys<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>Sim<br>4.1 | Introduction         1.1 Evolution of mobile networks .         1.2 Multiple-antenna communications .         1.3 SC-FDMA technology .         1.4 Aims, outline and contributions of this thesis .         Literature review         2.1 MIMO detection .         2.1.1 Optimal detection .         2.1.2 Suboptimal linear and non-linear detection .         2.1.3 Tree-search algorithms .         2.2 Implementation aspects .         2.2.1 QR decomposition .         2.2.2 Sorting .         2.2.3 Technology .         2.2.4 High-level synthesis .         System model and receiver structures         3.1 System model .         3.2 SC-FDMA MIMO receiver structures         3.3 MMSE filter .         3.4 Sphere detector .         3.5 Possible receiver modifications .         3.5.1 Antenna grouping .         3.5.2 LLR iteration . |

| R        | efere          | ences                                   | 101 |

|----------|----------------|-----------------------------------------|-----|

| 7        | $\mathbf{Dis}$ | scussion and future work                | 95  |

|          | 6.5            | Conclusions                             |     |

|          | 6.4            | FPGA technology evaluation              |     |

|          | 6.3            | Hand-written RTL language vs HLS tools  |     |

|          |                | 6.2.2 AutoPilot 2011 vs Vivado HLS 2017 |     |

|          |                | 6.2.1 Catapult C 2010 vs AutoPilot 2011 |     |

|          | 6.2            | HLS tool evaluation                     |     |

|          | 6.1            | Architecture comparison                 |     |

| 6        | Imj            | plementation results                    | 81  |

|          |                | 5.4.2 Embedded DSP usage                |     |

|          |                | 5.4.1 C-code parametrisation            |     |

|          | 5.4            | Examples of design optimisation         |     |

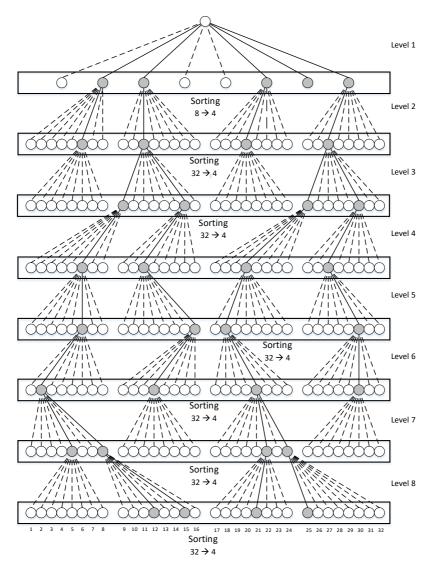

|          |                | 5.3.2 Sort-free architecture            | 76  |

|          |                | 5.3.1 Architecture with a sorter        | 74  |

|          | 5.3            | Macro-architecture specification        |     |

|          | 5.2            | Implementation requirements             | 74  |

|          | 5.1            | Development environment                 |     |

| <b>5</b> | MI             | MO detector implementations             | 71  |

|          | 4.7            |                                         |     |

|          | 4.6            | Complexity estimation                   |     |

|          | 4.5            | Turbo receiver                          | 65  |

|          | 4.4            | LLR iteration                           |     |

|          | 4.3            | $1 \times 4$ MIMO system                |     |

## 1 Introduction

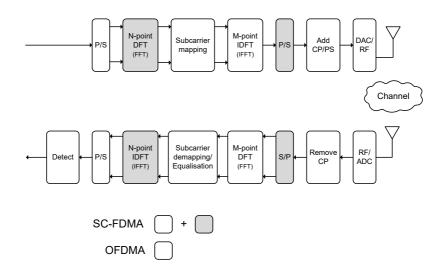

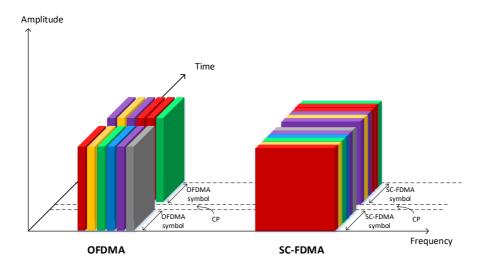

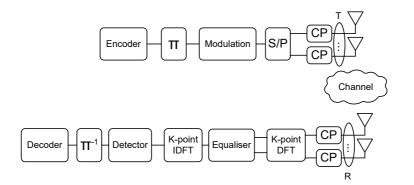

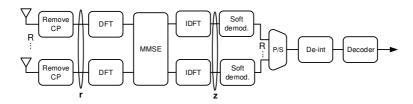

Use of mobile broadband communication has risen dramatically over the last decade. Increased processing power and screen size of smartphones have enabled heavy consumption of media (e.g., video content). In addition to smartphones, several other devices with mobile broadband connectivity have been introduced, with tablets and external laptop modems having made wireless mobile connectivity into a competitor to fixed-line home Internet access. It has been estimated that 1000 times more mobile-network capacity will be needed within the next 10 years [1]. A thousandfold increase could be achieved with, for example, an increase to tenfold the capacity in each of three areas: amount of spectrum, spectrum-efficiency, and base station (BS) density. The thesis focuses on increasing spectrum-efficiency, via efficient multiple-input, multiple-output (MIMO) configuration that uses multiple antennas at both the user equipment (UE) and the BS. This constitutes motivation for the study of advanced receivers for combating inter-antenna interference (IAI) and inter-symbol interference (ISI). Several receiver structures have been extensively considered for MIMO receivers, but the emphasis has been on those operating in downlink orthogonal frequency-division multiple access (OFDMA) systems, wherein ISI is not a problem. The focus in this thesis, in contrast, is on equalisation in single-carrier frequency-division multiple access (SC-FDMA) uplink BS receivers.

### 1.1 Evolution of mobile networks

Wireless telephone technology, nowadays referred to as mobile communications, is one of the few technologies to have adopted and retained classification terminology that refers to standard generations of technology. A new generation has been standardised approximately once each decade. The first-generation (1G) standards were introduced in the early 1980s. These were for analogue systems delivering voice services, with communication based on single-carrier transmission and with frequency-division multiple access (FDMA) being used as a method for multiple access. The first 1G communication system was launched in 1979 in Japan by Nippon Telegraph and Telephone (NTT) [2]. This was soon followed by a Nordic Mobile Telephony (NMT) system in the Nordic region, in 1981, and the Advanced Mobile Phone Service (AMPS) system in the USA, in 1983 [3].

Second-generation (2G) digital cellular systems were commercially launched in the early 1990s. Additional to voice services, new features such as text messages and the Multimedia Message Service (MMS) were supported. Both the phone conversation and messaging were digitally encrypted. Also, the 2G technologies were far more spectrum-efficient than the previous generation's analogue systems. The 2G systems applied either time-division multiple access (TDMA) or code-division multiple access (CDMA). In some TDMA-based 2G cellular systems, the users are divided into groups, with each group having its own channel while users in the same group share the resources via TDMA [3]. Accordingly, these systems are actually hybrid TDMA-FDMA systems. Launched in 1991 by Finland's Radiolinja, the TDMA-based Global System for Mobile Communications (GSM) was the first commercial 2G network. This system spread rapidly across Europe and eventually entered use all over the world, with the exception of North America. Another TDMA-based standard, Digital AMPS (D-AMPS), also known as IS-54 or IS-136, was deployed in 1993 in the USA and Canada. A third example of a TDMA-based 2G standard is the Personal Digital Cellular (PDC) system, familiar also as the Japanese Digital Cellular. It was commercially launched in 1993 and used exclusively in Japan. A CDMA variant of 2G technology can be found in cdmaOne, also known as IS-95. This was the first-ever CDMA-based cellular standard and came to be used in America and Asia. The cdmaOne standard was released in 1995.

The original circuit-switched 2G systems were not optimal for bursty data traffic. With the General Packet Radio Service (GPRS), a packet-oriented mobile data service for GSM was introduced. Originally standardised by the European Telecommunications Standards Institute (ETSI), GPRS is currently maintained by the 3rd Generation Partnership Project (3GPP). It provides data rates of up to 114 kbps. Enhanced Data Rates for GSM Evolution (EDGE) represented an evolution of GPRS networks, often referred to as 2.5G technology. Following on from the Gaussian minimum-shift keying (GMSK) of GPRS, higher-order phase-shift keying (8-PSK) was introduced. This enabled bit rates of up to 236.8 kbps. The first commercial EDGE network was deployed in 2003 by Cingular Wireless, now part of AT&T, in the USA.

Third-generation (3G) mobile networks enabled broadband wireless data

services. The first 3G networks were deployed in 2000–2001, in Korea and Japan. While 3G was often marketed as an enabler for such applications as video calls, video calls never became popular. However, this was still an important step in the evolution of mobile communications that would enable mobile Internet access. The 3G standards comply with the International Mobile Telecommunications-2000 (IMT-2000) specifications issued by the International Telecommunication Union (ITU). To fulfil these requirements, 3GPP and Third Generation Partnership Project 2 (3GPP2) standardised the Universal Mobile Telecommunications System (UMTS) and CDMA2000, respectively [4]. The UMTS approach entered use primarily in Europe, Japan, and China, while CDMA2000 was deployed mainly in North America and South Korea. The most widespread radio interface for UMTS is called Wideband Code Division Multiple Access (W-CDMA). This later evolved into High Speed Packet Access (HSPA) and Evolved High Speed Packet Access (HSPA+) [5], with the latter providing data rates as high as 42.2 Mbps in the downlink direction and 22 Mbps for uplink with 5 MHz bandwidth, a  $2\times2$  MIMO antenna configuration, and up to 64-level quadrature amplitude modulation (QAM). Both HSPA and HSPA+ technology are often denoted as 3.5G technologies.

International Mobile Telecommunications–Advanced (IMT-Advanced or IMT-A) is a set of requirements issued by the ITU to define fourth-generation (4G) mobile communications systems. Among the IMT-Advanced requirements are wireless services based on Internet Protocol (IP), a data rate of 100 Mbps while one is moving and 1 Gbps in stationary use, scalable bandwidth of 1.4 MHz to 20 MHz, high spectrum-efficiency, and global roaming [6]. Two examples of the 4G standards are Long-Term Evolution (LTE), by 3GPP, and Worldwide Interoperability for Microwave Access (WiMAX), by the WiMAX Forum. The first commercial mobile WiMAX service was deployed by Korea Telecom in Seoul, South Korea, in June 2006, and the first commercial LTE service was launched in Sweden and Norway in 2009. Actually, neither of these technologies fulfilled the peak data transmission requirements of IMT-Advanced, but both were marketed as 4G technology although the technology community often referred to them as 3.9G at the time. In 2010, the ITU announced that, while these beyond-3G technologies do not meet the IMT-Advanced peak data rate requirements, they still can be considered 4G technology. The LTE standard includes both frequency-division duplex (FDD) and time-division duplex (TDD) operation modes. The difference between LTE-FDD and LTE-TDD lies in how the data get uploaded and downloaded: the former has fixed paired frequency bands for the uplink and downlink, whereas LTE-TDD uses a single band for both. The LTE-TDD band resources can be adjusted in accordance with the estimated ratio between uplink and downlink traffic in the network. In LTE systems, downlink operations use OFDMA, while uplink uses SC-FDMA. A single-carrier transmission enables a lower peak-to-average-power ratio (PAPR) at the UE power amplifier and therefore better energy-efficiency.

The evolved version of LTE is LTE-Advanced (LTE-A). The LTE-A approach introduces additional features such as carrier aggregation and higher-level multiple-antenna configuration (i.e., eight antennas at the base station and four at the UE). These improvements enable a downlink peak date rate of up to 1 Gbps and in uplink up to 500 Mbps [7]. In other words, LTE-A was the first 3GPP standard to truly meet the original 4G requirements.

As we move toward next-generation mobile communications, the fifth generation (5G), it is important to remember that there are many smaller 'generations' and releases between the major ones in the 1G, 2G, 3G, 4G, 5G classification. An alternative way to list and compare mobile-communication technologies is to focus on the standard versions. Each of the standard releases introduces new features and improvements. Determining which specific release marks one mobile-communication generation giving way to a new one is sometimes difficult. This is especially true in the case of 5G: 3GPP standard release 8 (LTE) provided the launch for 4G. Release 10 (LTE-A), bringing such elements as carrier aggregation, is sometimes referred to as 4.5G technology. Specification is in progress for release 15, which could be the first 3GPP standard to bear the '5G' name. That said, mobile network operator (MNO) marketing, politics, etc. could mean that, before that, release 13 or 14 networks might begin to carry this title. Finally, as discussed above, definitions may be changed in retrospect as processes continue.

### 1.2 Multiple-antenna communications

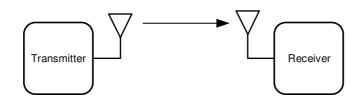

Multiple-antenna communication refers to a set of techniques wherein the transmitter, receiver, or both have several antennas. Advanced signal processing is required if benefit is to be gained from multi-antenna techniques. An MIMO technique can be used to increase the reliability of the transmission or to increase the data rate. Multiple antennas can be utilised to provide additional diversity against fading, shape the overall antenna beam in a certain direction, and/or create multiple parallel communication channels with spatial multiplexing [7]. A traditional single-antenna set-up, shown in Figure 1, can be considered to be a single-input, single-output (SISO) system.

Fig 1. A wireless SISO transmission system.

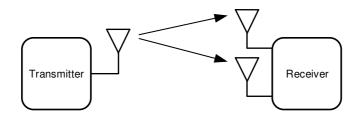

Single-input, multiple-output (SIMO), illustrated in Figure 2, is an antenna configuration with multiple receive antennas. This has historically been the most straightforward multi-antenna technology. It can be utilised for enhancing the signal at the receiver by combining the signals (in what is called array gain) or to obtain diversity at reception. The maximum achievable diversity order in the SIMO antenna configuration case is equal to the number of receive antennas [8].

Fig 2. A wireless SIMO transmission system.

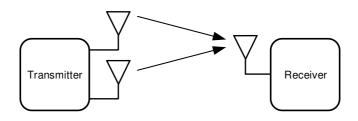

Multiple-input, single-output (MISO), illustrated in Figure 3, refers to antenna configuration with multiple transmit antennas. The transmitter diversity order in a MISO system is equal to the number of transmit antennas if independently faded streams can be assumed. Diversity can be achieved with space-time codes

(STCs) [9]. In addition to diversity, multiple transmit antennas can be exploited also for beamforming. Beamforming can increase the signal strength at the receiver or minimise the interference at the receiver [10].

Fig 3. A wireless MISO transmission system.

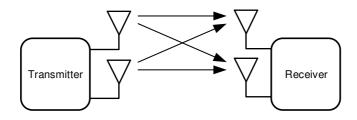

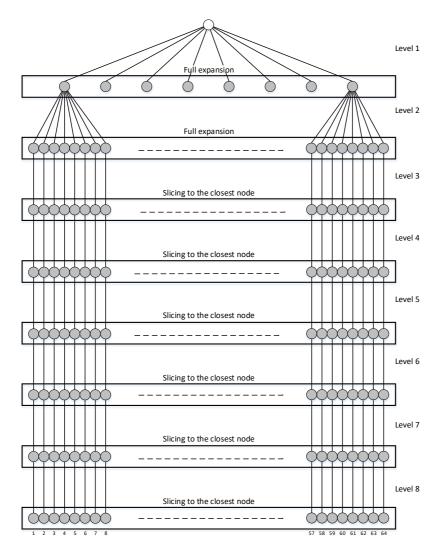

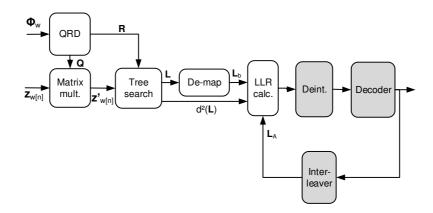

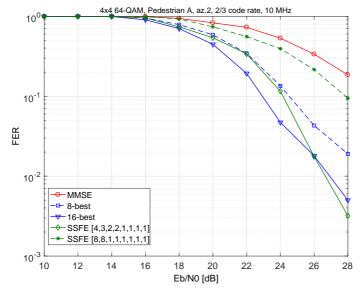

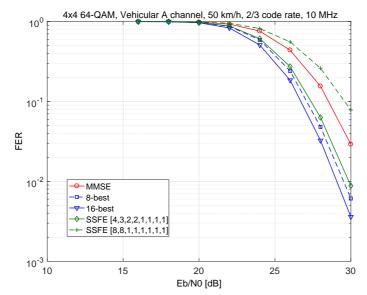

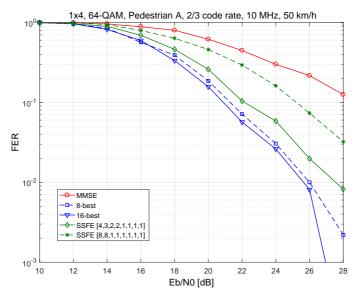

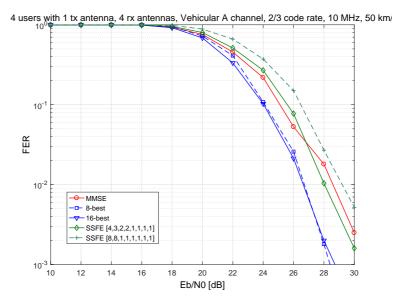

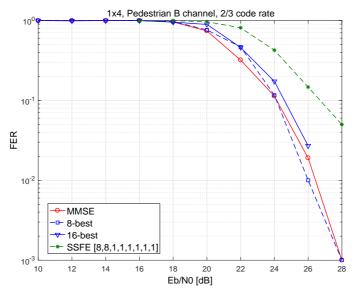

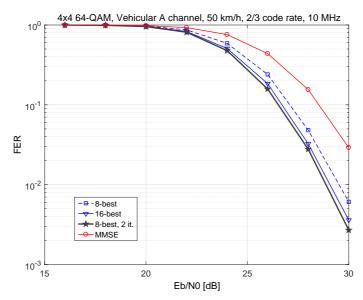

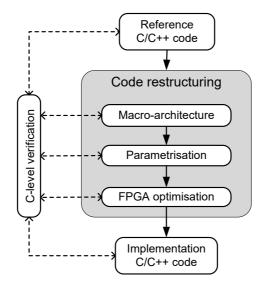

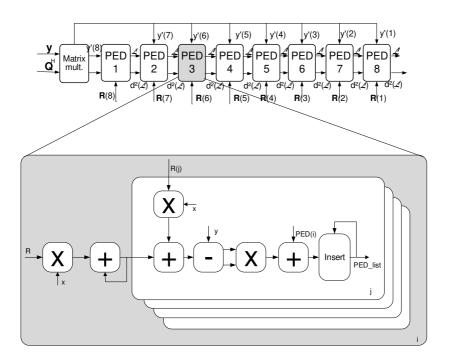

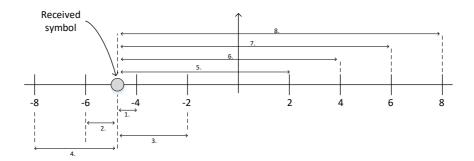

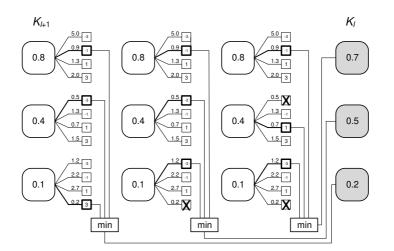

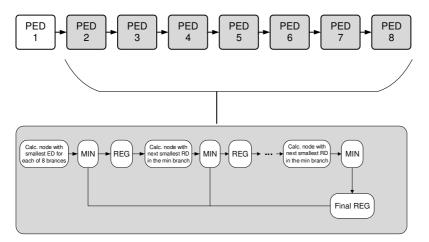

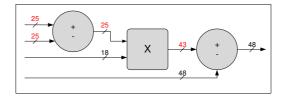

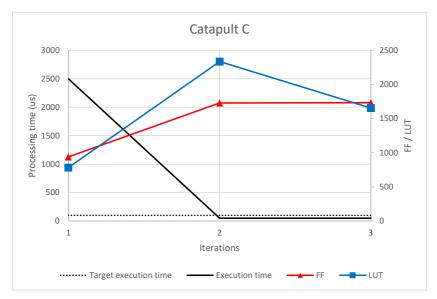

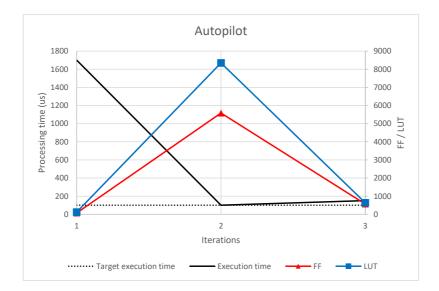

MIMO antenna configurations (as shown in Figure 4) – that is, having multiple receive and transmit antennas – can be used to obtain a diversity gain or an array gain. However, in the case of multiple receive and multiple transmit antennas there is also the possibility of spatial multiplexing [11]. In environments with a high signal-to-noise ratio (SNR), spatial multiplexing can increase the data rates significantly. Diversity and beamforming techniques can raise the SNR in proportion to the number of antennas, and a higher SNR enables higher data rates. However, this is true only for operation within a power-limited regime. If the system is bandwidth-limited, data rates will saturate with these techniques. In such a case, spatial multiplexing can increase the data rate. In optimal conditions, the capacity can be made to grow linearly with the number of antennas and without data rate saturation [7]. Diversity/beamforming and spatial multiplexing gain can be achieved simultaneously in MIMO communications; however, there is always a trade-off between lower error probability and higher data rates [12]. Spatial multiplexing gain can be better exploited in good channel conditions and diversity/beamforming schemes in poor channel conditions.