# M.Sc. Thesis

#### Determining Performance Boundaries and Automatic Loop Optimization of High-Level System Specifications

#### Wouter van Teijlingen

#### Abstract

Designers are confronted with high time-to-market pressure and an increasing demand for computational power. As a result, they are required to identify as early as possible the quality of a specification for an intended technology. The designer needs to know if this specification can be improved, and at what cost. Specification trade-offs are often based on the experience and intuition of a designer, which in itself is not enough to make design decisions given the complexity of modern designs. Therefore, we need to identify the performance boundaries for the execution of a specification on an intended technology.

The degree of parallelism, required resources, scheduling constraints, and possible optimizations, etc. are essential in determining design trade-offs (e.g., power consumption, execution time, etc). However, existing tools lack the capability of determining relevant performance parameters and the option to automatically optimize high-level specifications to make meaningful design trade-offs.

To address these problems, we present in this thesis a new profiler tool, *cprof*. The Clang compiler front-end is used in this tool to parse high-level specifications, and to produce instrumented source code for the purpose of profiling. This tool automatically determines, from high-level specifications, the degree of parallelism of a given source code, specified in C and C++ programming languages. Furthermore, cprof estimates the number of clock cycles necessary to complete a program, it automatically applies loop optimization techniques, it determines the lower and upper bound on throughput capacity, and finally, it generates hardware execution traces. The tool assumes that the specification is executed on a parallel *Model of Computation* (MoC), referred to as a *Polyhedral Process Network* (PPN).

The proposed tool adds new functionality to existing technologies: the estimated performance by cprof of PolyBench/C benchmarks, as compared to realistic implementations in *Field-Programmable Gate Arrays* (FPGA) platforms, showed to be almost identical. Cprof is capable of estimating the lower and upper bound on throughput capacity, making it possible for the designer to make performance trade-offs based on real design points. As a result, only the high-level specification is used by cprof to assist in *Design Space Exploration* (DSE) and to improve design quality.

## Determining Performance Boundaries and Automatic Loop Optimization of High-Level System Specifications Profiling of Polyhedral Process Networks

THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

Computer Engineering

by

Wouter van Teijlingen born in Leiderdorp, The Netherlands

This work was performed in:

Circuits and Systems Group Department of Microelectronics & Computer Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

**Delft University of Technology** Copyright © 2014 Circuits and Systems Group All rights reserved.

#### Delft University of Technology Department of Microelectronics & Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Determining Performance Boundaries and Automatic Loop Optimization of High-Level System Specifications" by Wouter van Teijlingen in partial fulfillment of the requirements for the degree of Master of Science.

Dated: November 28, 2014

Chairman:

prof. dr. ir. A. J. van der Veen

Advisors:

dr. ir. T. G. R. M. van Leuken

dr. ir. A. C. J. Kienhuis

Committee Members:

dr. C. Galuzzi

dr. ir. J. S. S. M. Wong

### Abstract

Designers are confronted with high time-to-market pressure and an increasing demand for computational power. As a result, they are required to identify as early as possible the quality of a specification for an intended technology. The designer needs to know if this specification can be improved, and at what cost. Specification trade-offs are often based on the experience and intuition of a designer, which in itself is not enough to make design decisions given the complexity of modern designs. Therefore, we need to identify the performance boundaries for the execution of a specification on an intended technology.

The degree of parallelism, required resources, scheduling constraints, and possible optimizations, etc. are essential in determining design trade-offs (e.g., power consumption, execution time, etc). However, existing tools lack the capability of determining relevant performance parameters and the option to automatically optimize high-level specifications to make meaningful design trade-offs.

To address these problems, we present in this thesis a new profiler tool, *cprof.* The Clang compiler front-end is used in this tool to parse high-level specifications, and to produce instrumented source code for the purpose of profiling. This tool automatically determines, from high-level specifications, the degree of parallelism of a given source code, specified in C and C++ programming languages. Furthermore, cprof estimates the number of clock cycles necessary to complete a program, it automatically applies loop optimization techniques, it determines the lower and upper bound on throughput capacity, and finally, it generates hardware execution traces. The tool assumes that the specification is executed on a parallel *Model of Computation* (MoC), referred to as a *Polyhedral Process Network* (PPN).

The proposed tool adds new functionality to existing technologies: the estimated performance by cprof of PolyBench/C benchmarks, as compared to realistic implementations in *Field-Programmable Gate Arrays* (FPGA) platforms, showed to be almost identical. Cprof is capable of estimating the lower and upper bound on throughput capacity, making it possible for the designer to make performance trade-offs based on real design points. As a result, only the high-level specification is used by cprof to assist in *Design Space Exploration* (DSE) and to improve design quality.

## Acknowledgments

First of all, I would like to express my gratitude to my advisor, professor Rene van Leuken. Without your support, this work would never have come into existence. I would like to thank Carlo Galuzzi, for taking an interest in my work and for proofreading my thesis.

I am also very grateful to my second advisor, professor Bart Kienhuis. Thank you for introducing me into the world of polyhedral process networks, and for sharpening my writing skills. I hope to continue our collaboration in the future

I am indebted to my colleague Johan Peltenburg, for taking the time to read my thesis and for providing me with feedback. I would like to thank my colleagues at the Rotterdam University of Applied Sciences, for taking an interest in my work.

Noela, thank you for your love and unconditional support. I would like to thank my family, and in particular, my parents, Piet and Petra. Thank you for your limitless support throughout the years.

Wouter van Teijlingen Delft, The Netherlands November 28, 2014

# Contents

| Al | ostra                                                                                                              | let                                                                                                                                                        | $\mathbf{v}$                                                                                      |

|----|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| A  | ckno                                                                                                               | wledgments                                                                                                                                                 | vii                                                                                               |

| Li | st of                                                                                                              | Figures                                                                                                                                                    | civ                                                                                               |

| Li | st of                                                                                                              | Tables                                                                                                                                                     | xv                                                                                                |

| Li | st of                                                                                                              | Algorithms x                                                                                                                                               | vii                                                                                               |

| Li | st of                                                                                                              | Acronyms                                                                                                                                                   | ix                                                                                                |

| 1  | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4                                                                            | <b>roduction</b> Motivation         Problem statement         Goals and contributions         Synopsis and Outline                                         | 1<br>2<br>3<br>4<br>4                                                                             |

| 2  | <ul> <li>Bac</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ul> | The LLVM/Clang Compiler Infrastructure                                                                                                                     | $\begin{array}{c} 5 \\ 5 \\ 5 \\ 6 \\ 7 \\ 8 \\ 8 \\ 9 \\ 10 \\ 10 \\ 11 \\ 11 \\ 12 \end{array}$ |

| 3  | Rel<br>3.1<br>3.2<br>3.3                                                                                           | SimulationAnalytical EstimationProfiling3.3.1General-Purpose Profilers3.3.2Hardware Profilers3.3.3Parallel and Memory Profilers3.3.4Critical Path Analysis | <b>13</b><br>13<br>14<br>14<br>14<br>14<br>14<br>15<br>16                                         |

| 4  | <b>Solu</b><br>4.1                                                                                                 | Concepts                                                                                                                                                   | 17<br>17<br>18<br>19<br>20<br>20                                                                  |

|   | 4.2          | Performance Estimation                                          |

|---|--------------|-----------------------------------------------------------------|

|   |              | 4.2.1 Absolute Throughput Estimation                            |

|   |              | 4.2.2 Unbounded Throughput Estimation                           |

|   | 4.3          | Case Studies                                                    |

|   |              | 4.3.1 Case Study: Absolute Throughput                           |

|   |              | 4.3.2 Case Study: Unbounded Throughput                          |

|   | 4.4          | Shadow Variables                                                |

|   | 4.5          | Control Variables                                               |

|   | 4.6          | Statement Execution Profile                                     |

|   | 4.0<br>4.7   | Global Execution Profile                                        |

|   |              |                                                                 |

|   | $4.8 \\ 4.9$ | Flow Dependencies                                               |

|   | 4.9          |                                                                 |

| 5 |              | sign and Implementation                                         |

|   | 5.1          | Overview                                                        |

|   | 5.2          | Input Processing                                                |

|   |              | 5.2.1 Input Specification                                       |

|   |              | 5.2.2 AST Construction                                          |

|   | 5.3          | Static Analysis and Instrumentation                             |

|   |              | 5.3.1 Static Analysis                                           |

|   |              | 5.3.2 Instrumentation                                           |

|   |              | 5.3.3 Source-to-Source Transformations                          |

|   | 5.4          | Dynamic Analysis                                                |

|   | 0.1          | 5.4.1 Compilation and Initialization                            |

|   |              | 5.4.2 Algorithms for Dynamic Analysis                           |

|   | 5.5          | Performance Analysis                                            |

|   | 0.0          | 5.5.1 Data Processing and Presentation                          |

|   |              | 5.5.2 Waveform Generation                                       |

|   |              |                                                                 |

|   | - 0          | 5.5.3 Program Profile Generation                                |

|   | 5.6          | Optimization                                                    |

|   |              | 5.6.1 Methods                                                   |

|   |              | 5.6.2 Implementation of Optimizations                           |

|   | 5.7          | Hierarchical Program Analysis                                   |

|   |              | 5.7.1 Static Analysis                                           |

|   |              | 5.7.2 Instrumentation $\ldots$                                  |

|   |              | 5.7.3 Dynamic Analysis                                          |

|   |              | 5.7.4 Performance Analysis                                      |

|   | 5.8          | The Cost of Profiling                                           |

|   | 5.9          | Summary and Conclusions                                         |

| 6 | Ver          | ification                                                       |

| - | 6.1          | Verification Approach                                           |

|   | 6.2          | Verification of the Communication Models                        |

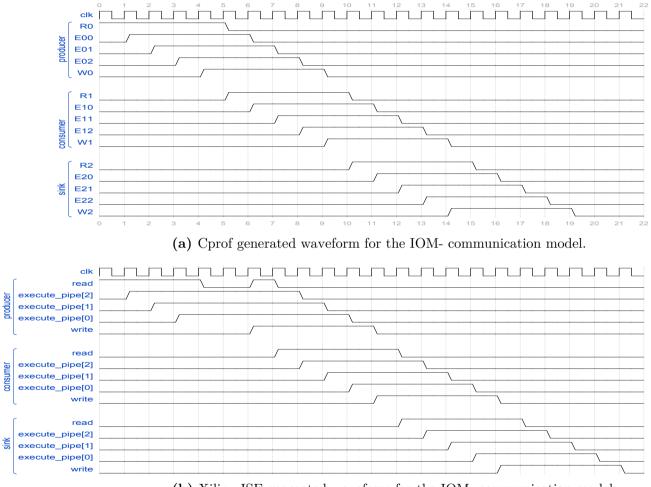

|   | 0.2          | 6.2.1 In-Order without Multiplicity (IOM-)                      |

|   |              | 6.2.2 In-Order with Multiplicity (IOM+)                         |

|   |              |                                                                 |

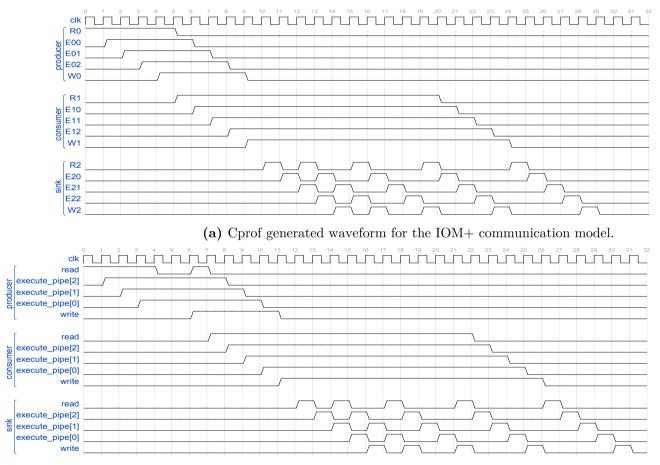

|   |              | 6.2.3 Out-of-Order without Multiplicity (OOM-)                  |

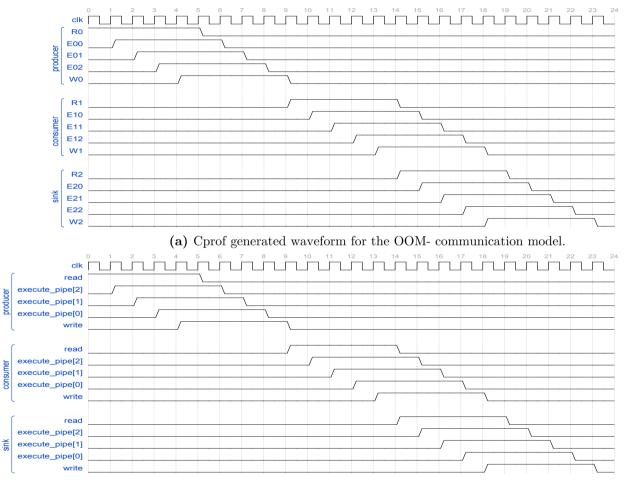

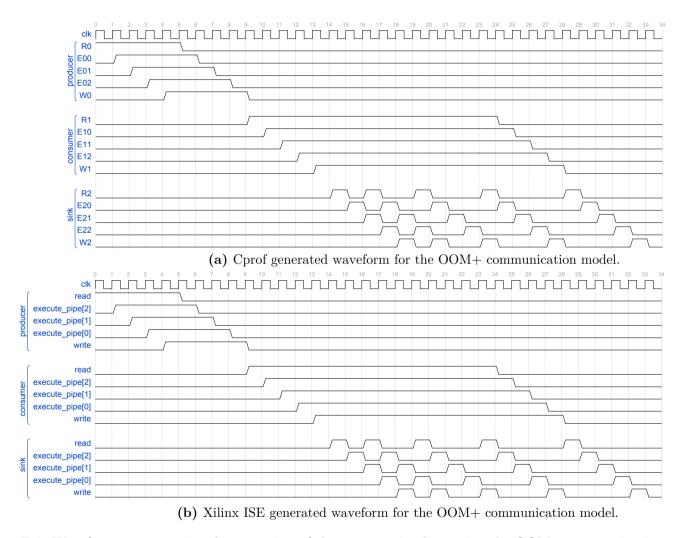

|   |              | 6.2.4 Out-of-Order with Multiplicity (OOM+)                     |

|   |              | 6.2.5 Results                                                   |

|   | 6.3          | Verification of the Absolute and Unbounded Throughput Estimates |

|   |              | 6.3.1 The Predictor Program                                     |

|   |              | 6.3.2 Optimization of Predictor                                 |

|   |              |                                                                 |

|   |              | 6.3.3 Results                                                   |

|              | 6.4.1 The Hierarchy Program                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | $6.4.2  \text{Results}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                     |

|              | 6.5 Summary and Conclusions                                                                                                                                  |

| 7            | Results 55                                                                                                                                                   |

|              | 7.1 Experimental Setup 5                                                                                                                                     |

|              | 7.2 Absolute Throughput Estimates of PolyBench/C                                                                                                             |

|              | 7.2         Insolute Throughput Estimates of FolyDenen/C         5           7.2.1         Execution Times         5                                         |

|              | 7.2.1 Execution Times                                                                                                                                        |

|              |                                                                                                                                                              |

|              | 7.3 Unbounded Throughput Estimates of Polybench/C                                                                                                            |

|              | 7.3.1 Execution Times $\ldots \ldots \ldots$ |

|              | 7.3.2 The Average and Maximum Degree of Parallelism                                                                                                          |

|              | 7.4 RTL Simulations                                                                                                                                          |

|              | 7.5 Design Space Boundaries                                                                                                                                  |

|              | 7.6 Optimization                                                                                                                                             |

|              | 7.7 Scalability                                                                                                                                              |

|              | 7.8       Summary and Conclusions       6                                                                                                                    |

|              |                                                                                                                                                              |

| 8            | Conclusions and Future Work 6                                                                                                                                |

| U            | 8.1 Contributions                                                                                                                                            |

|              | 8.2 Future Work                                                                                                                                              |

|              | 0.2 Future work                                                                                                                                              |

| Bi           | bliography 73                                                                                                                                                |

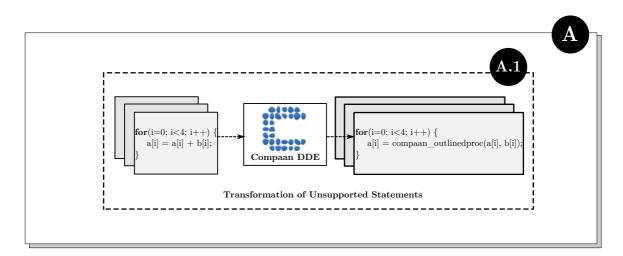

| ۸            | Compiler Extension for Compaan DDE 73                                                                                                                        |

| А            | A.1 Introduction                                                                                                                                             |

|              |                                                                                                                                                              |

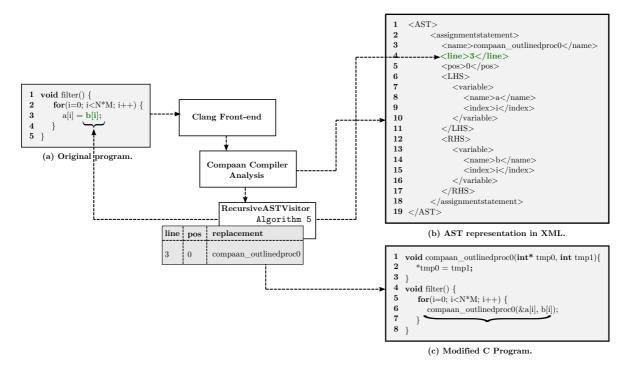

|              | A.1.1 Design and Implementation of the Compiler Extension                                                                                                    |

| в            | Cprof Usage Instructions 75                                                                                                                                  |

| Ъ            | I O                                                                                                                                                          |

|              |                                                                                                                                                              |

|              | B.2 Installation                                                                                                                                             |

|              | B.3 Usage 79                                                                                                                                                 |

| ~            |                                                                                                                                                              |

| С            | Predictor Optimized Versions 8:                                                                                                                              |

|              | C.1 Inner Loop Unrolled                                                                                                                                      |

|              | C.2 Outer loop Unrolled                                                                                                                                      |

|              | C.3 Inner/Outer Loops Unrolled                                                                                                                               |

|              | C.4 Inner/Outer/Sink Loops Unrolled                                                                                                                          |

|              | C.5 Source/Inner/Outer Loops Unrolled                                                                                                                        |

|              | C.6 Source/Inner/Outer/Sink Loops Unrolled                                                                                                                   |

|              |                                                                                                                                                              |

| D            | PolyBench/C 3.1 Benchmarks 88                                                                                                                                |

| $\mathbf{E}$ | Support of Control Flow Architectures in Cprof 93                                                                                                            |

|              | E.1 Modification of Algorithms                                                                                                                               |

|              | E.1.1 Read Operations                                                                                                                                        |

|              | -                                                                                                                                                            |

|              | E.1.2 Write Operations                                                                                                                                       |

| F            | Verification Waveforms 93                                                                                                                                    |

| г            |                                                                                                                                                              |

|              | F.1 IOM- Waveforms                                                                                                                                           |

|              | F.2 IOM+ Waveforms                                                                                                                                           |

|              | F.3 OOM- Waveforms                                                                                                                                           |

|              | F.4 OOM+ Waveforms                                                                                                                                           |

# List of Figures

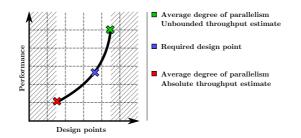

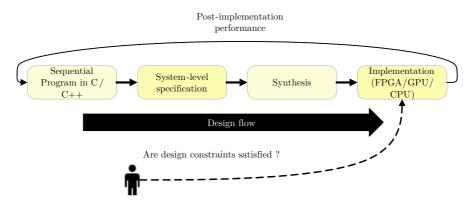

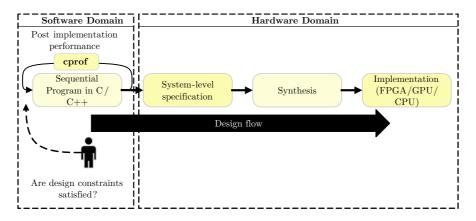

| 1.1<br>1.2   | Exploring the Design Space, using the absolute and unbounded throughput estimation.<br>Traditional design flow in high-level synthesis. |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1.3          | Reducing the feedback loop in the design flow in high-level synthesis                                                                   |  |  |  |  |

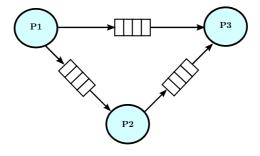

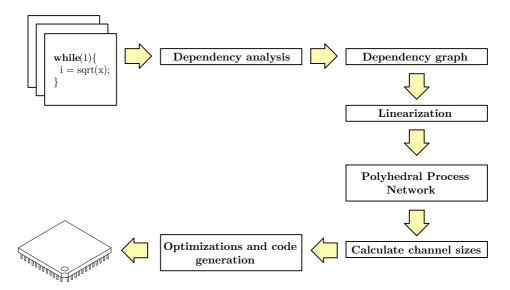

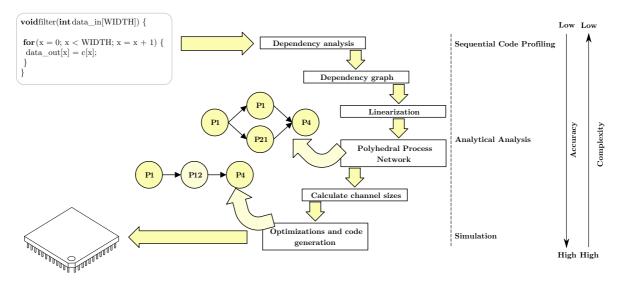

| $2.1 \\ 2.2$ | An example of a Polyhedral Process Network with FIFOs between processes 66<br>Derivation of Polyhedral Process Network                  |  |  |  |  |

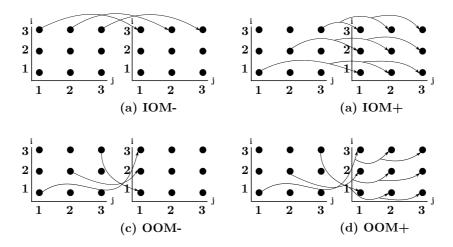

| 2.2<br>2.3   | Communication models for Polyhedral Process Networks                                                                                    |  |  |  |  |

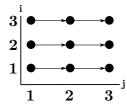

| $2.3 \\ 2.4$ | Dependency analysis of Listing 2.2                                                                                                      |  |  |  |  |

| $2.4 \\ 2.5$ | Selection of independent computational tasks                                                                                            |  |  |  |  |

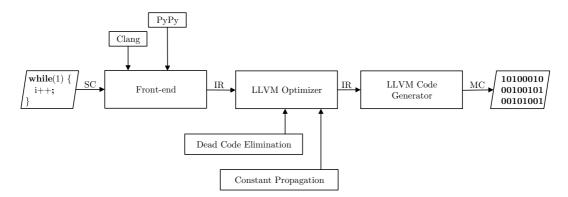

| $2.0 \\ 2.6$ | LLVM Compiler Infrastructure                                                                                                            |  |  |  |  |

| 2.0          |                                                                                                                                         |  |  |  |  |

| 3.1          | Level of accuracy and complexities in performance estimation                                                                            |  |  |  |  |

| 4.1          | Mapping of a C program to a Polyhedral Process Network                                                                                  |  |  |  |  |

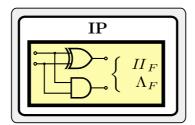

| 4.2          | Example IP block                                                                                                                        |  |  |  |  |

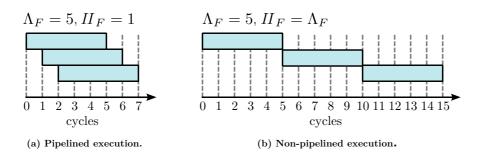

| 4.3          | The initiation interval and function latency of the execute stage                                                                       |  |  |  |  |

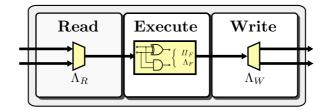

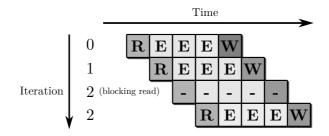

| 4.4          | The Read, Write, and Execute units in a polyhedral process                                                                              |  |  |  |  |

| 4.5          | Pipelined execution of the read, execute and write stages                                                                               |  |  |  |  |

| 4.6          | Mutual Exclusion in Processes                                                                                                           |  |  |  |  |

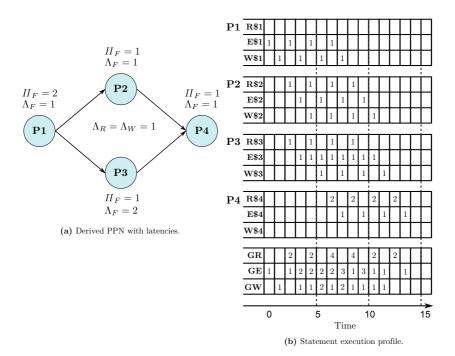

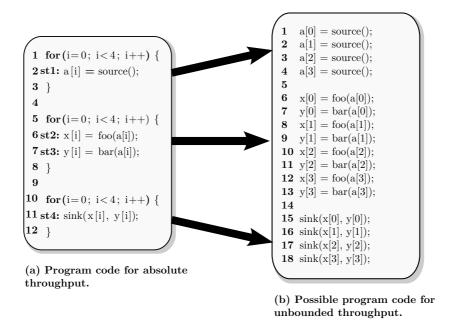

| 4.7          | Absolute and unbounded throughput                                                                                                       |  |  |  |  |

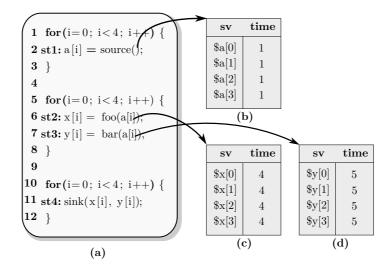

| 4.8          | The shadow variables and their values for absolute throughput estimates                                                                 |  |  |  |  |

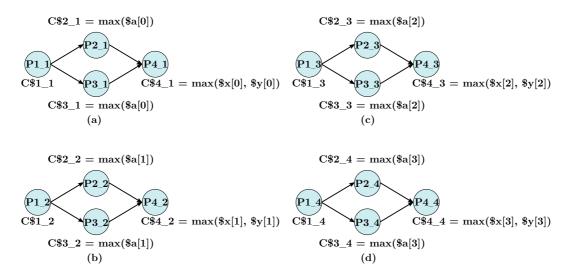

| 4.9          | Control variables associated with each process in a polyhedral process network 22                                                       |  |  |  |  |

|              | Absolute throughput statement profiles                                                                                                  |  |  |  |  |

|              | Example C Program                                                                                                                       |  |  |  |  |

|              | The shadow variables and their values for unbounded throughput estimates                                                                |  |  |  |  |

|              | Determiniation of control variables for unbounded throughput                                                                            |  |  |  |  |

|              | Unbounded throughput statement profiles                                                                                                 |  |  |  |  |

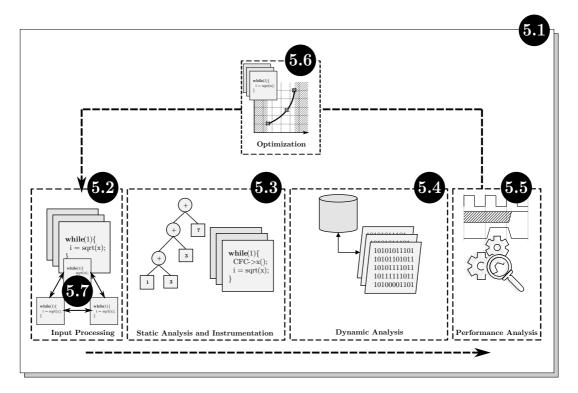

| 5.1          | Overview of the cprof profiler                                                                                                          |  |  |  |  |

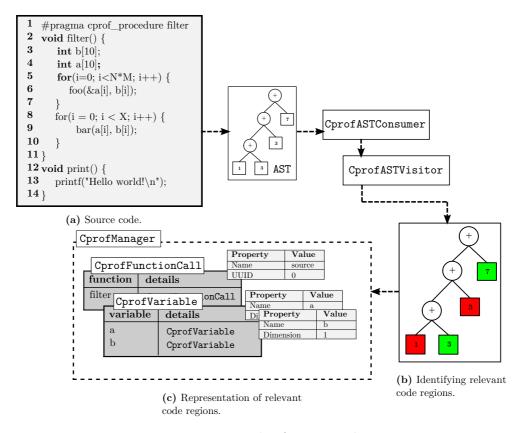

| 5.2          | Example of static analysis                                                                                                              |  |  |  |  |

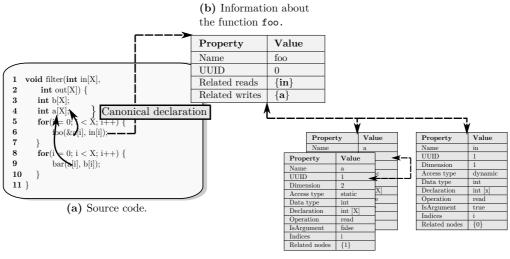

| 5.3          | The canonical declaration and its relation to variable references                                                                       |  |  |  |  |

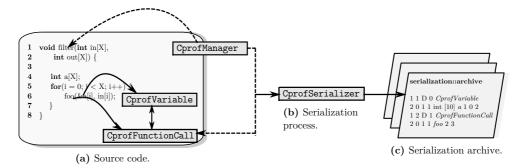

| 5.4          | Serialization of cprof objects                                                                                                          |  |  |  |  |

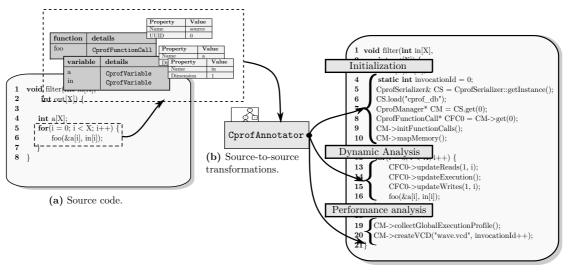

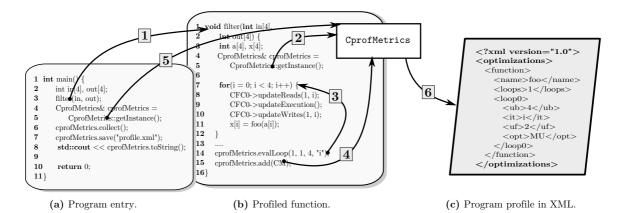

| 5.5          | Source code after instrumentation by cprof                                                                                              |  |  |  |  |

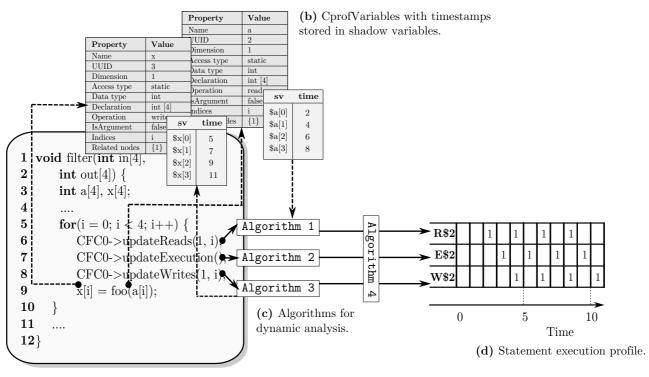

| 5.6          | Overview of algorithms used in dynamic analysis                                                                                         |  |  |  |  |

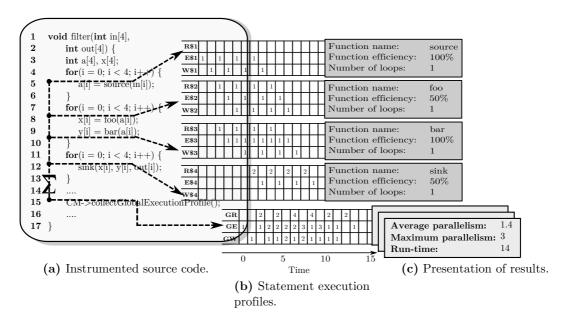

| 5.7          | Overview of processing and presenting the output of dynamic analysis                                                                    |  |  |  |  |

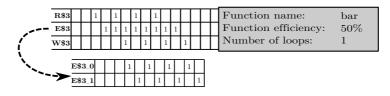

| 5.8          | Performance of the function bar after a closer inspection                                                                               |  |  |  |  |

| 5.9          | Generation of program profile                                                                                                           |  |  |  |  |

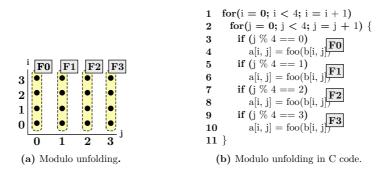

| 5.10         |                                                                                                                                         |  |  |  |  |

| 5.11         | Modulo unfolding applied                                                                                                                |  |  |  |  |

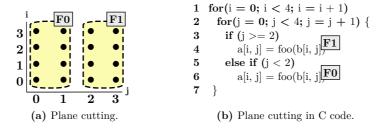

| 5.12         | Plane cutting aplied                                                                                                                    |  |  |  |  |

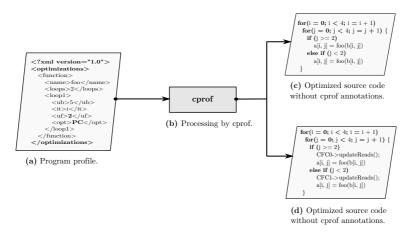

| 5.13         | Overview of the optimization flow in cprof                                                                                              |  |  |  |  |

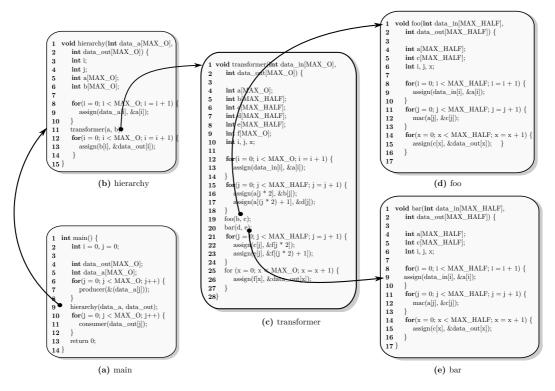

| 5.14         | Example program with hierarchy used for HPA 44                                                                                          |  |  |  |  |

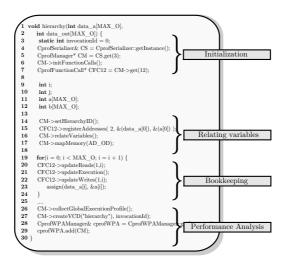

| 5.15         | The hierarchy function instrumented with support for HPA                                                                                |  |  |  |  |

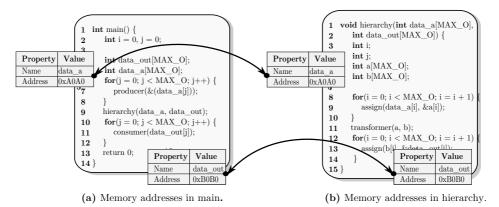

| 5.16         | Inter-procedural relations between variables                                                                                            |  |  |  |  |

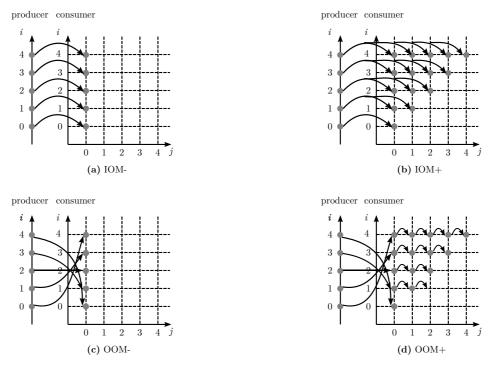

| 6.1          | Communication models in PPNs                                                                                                            |  |  |  |  |

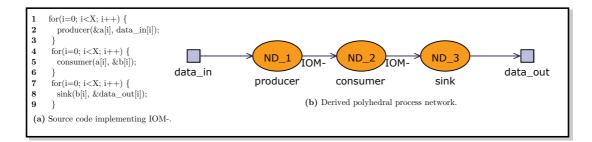

| 6.2          | Example implementation of the IOM- communication model                                                                                  |  |  |  |  |

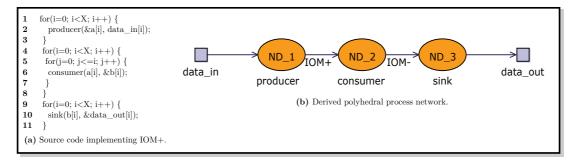

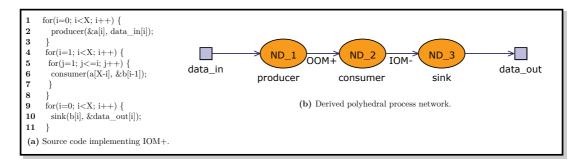

| 6.3          | Example implementation of the IOM+ communication model                                                                                  |  |  |  |  |

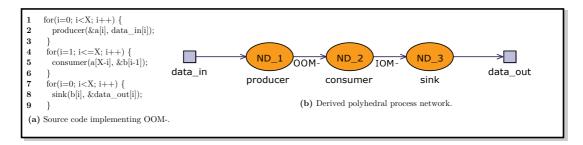

| 6.4          | Example implementation of the OOM- communication model                                                                                  |  |  |  |  |

| 6.5          | Example implementation of the OOM+ communication model                                                                                  |  |  |  |  |

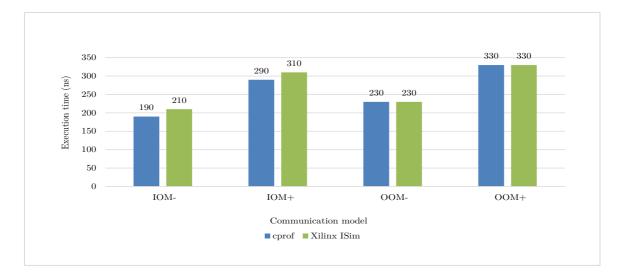

| 6.6  | Execution times of the communication models measured by cprof and ISim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

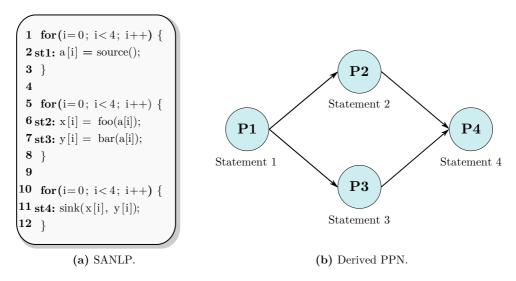

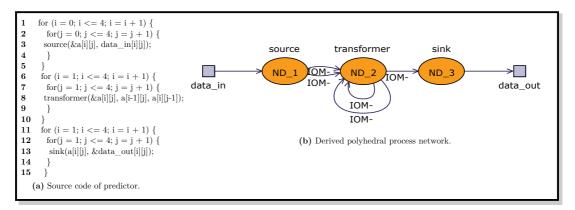

| 6.7  | The source code and derived PPN of predictor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51  |

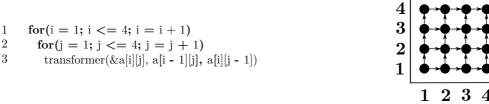

| 6.8  | The dependency graph of the transformer function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52  |

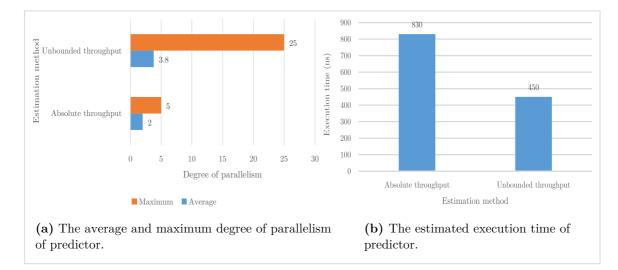

| 6.9  | The absolute and unbounded throughput estimates for the predictor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52  |

| 6.10 | Iteration dependencies in the predictor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53  |

| 6.11 | Two possible optimizations of predictor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53  |

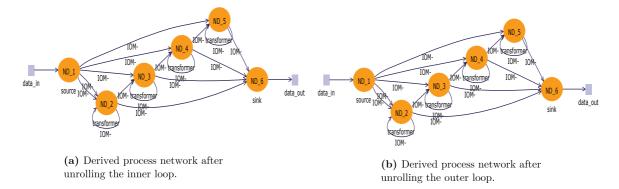

| 6.12 | Polyhedral process network of the predictor with the inner and outer loop unrolled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54  |

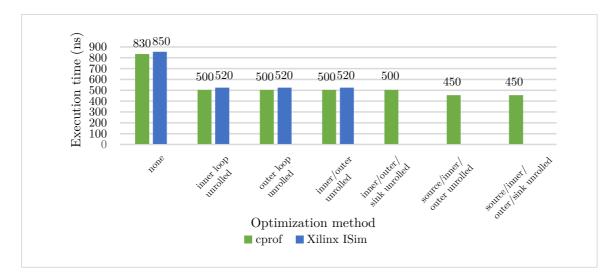

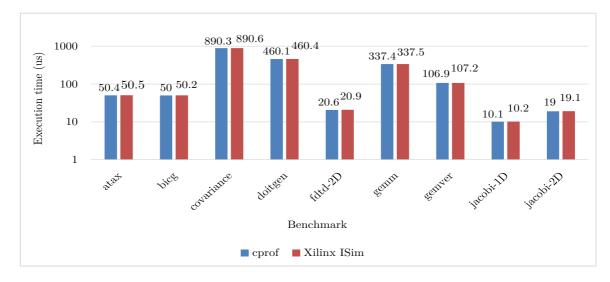

| 6.13 | Execution times of the predictor measured by cprof and by Xilinx ISim.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55  |

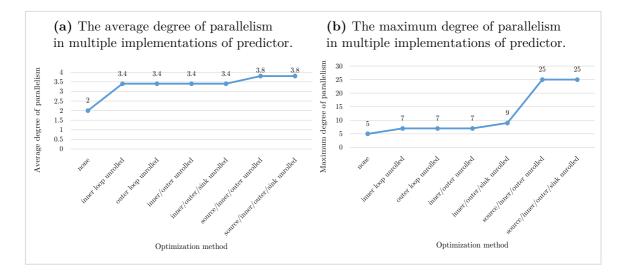

| 6.14 | The average and maximum degree of parallelism available in the predictor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56  |

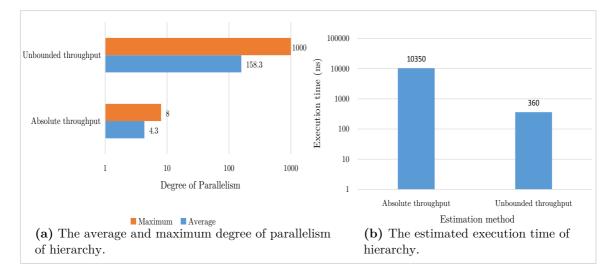

| 6.15 | The absolute and unbounded throughput estimates for hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57  |

|      | The execution finish times of hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58  |

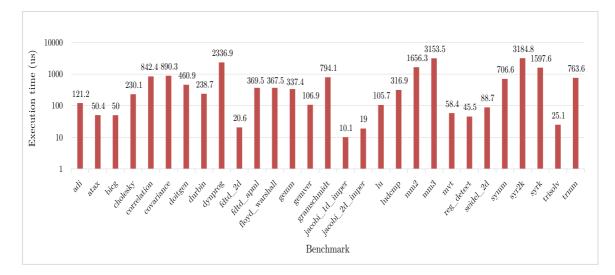

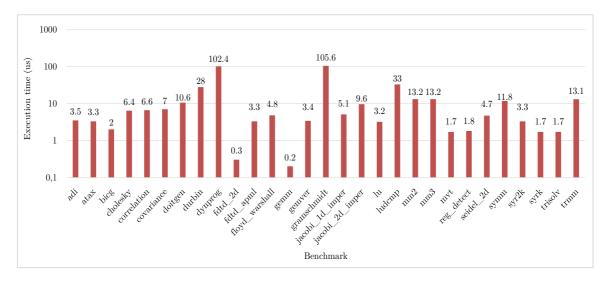

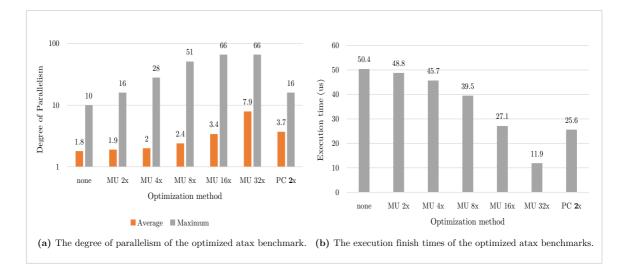

| 7.1  | Absolute throughput estimates of the execution finish times of PolyBench/C kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60  |

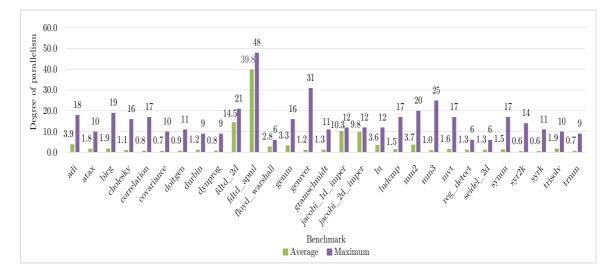

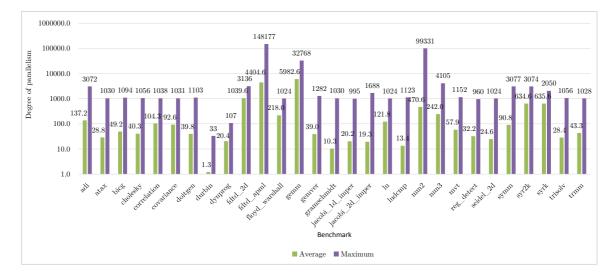

| 7.2  | Absolute throughput estimates of the average and maximum degree of parallelism in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|      | PolyBench/C kernels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60  |

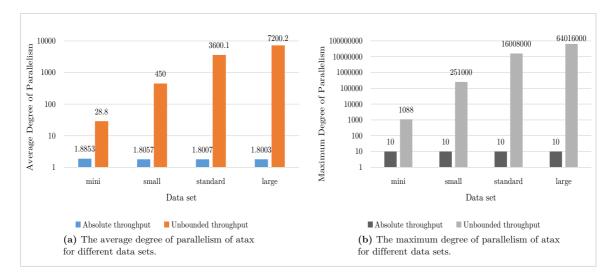

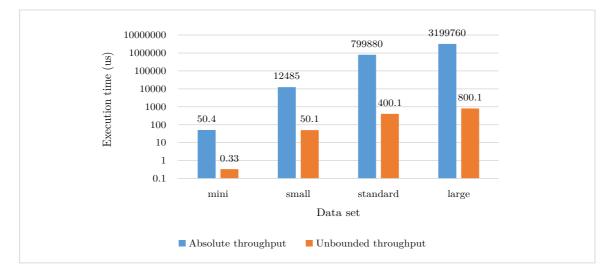

| 7.3  | Unbounded throughput estimates of the execution finish times of PolyBench/C kernels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61  |

| 7.4  | Unbounded throughput estimates of the average and maximum degree of parallelism in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|      | PolyBench/C kernels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62  |

| 7.5  | $Absolute \ throughput \ estimates \ of \ the \ execution \ finish \ time \ of \ PolyBench/C \ kernel \ versus$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|      | the execution finish time of RTL implementations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62  |

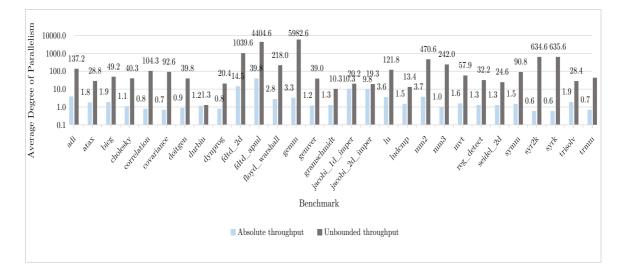

| 7.6  | Design space boundaries: the average degree of parallelism found by the absolute and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

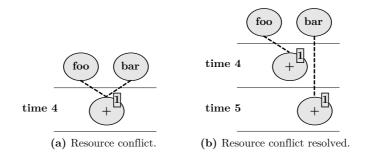

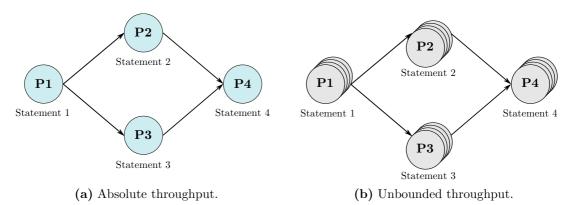

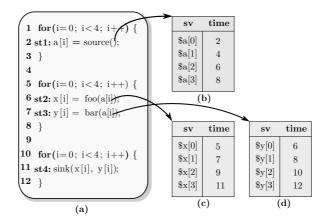

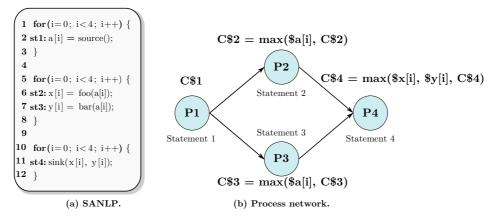

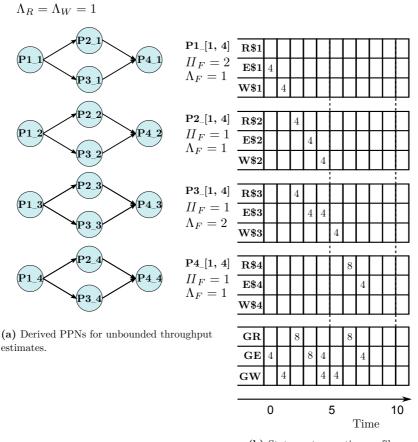

|      | unbounded throughput estimates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63  |