# Development and Analysis of the Software Implemented Fault-Tolerance (SIFT) Computer

Jack Goldberg Milton W. Green William H. Kautz Karl N. Levitt P. Michael Melliar-Smith Richard L. Schwartz Charles B. Weinstock

SRI International Menlo Park, California 94025

Contract NAS1-15428

February 1984

Langley Research Center Hampton, Virginia 23665

# Table of Contents

| I. | Summary of Results                                                   |

|----|----------------------------------------------------------------------|

|    | A. GOALS OF THE SIFT DEVELOPMENT                                     |

|    | 1. Introduction                                                      |

|    | 2. Design Criteria                                                   |

|    | B. DESIGN APPROACHES AND SOLUTIONS                                   |

|    | 1. Basic Redundancy Issues                                           |

|    | 2. Reconfiguration                                                   |

|    | 3. The SIFT Approach                                                 |

|    | 4. A Hierarchical Design View                                        |

|    | 5. Verification and Testing                                          |

|    | 6. Proof Of Correctness                                              |

|    | 7. Software Methodology                                              |

|    | 8. Operational Support Equipment                                     |

|    | 9. Test Environment                                                  |

|    | C. DEVELOPMENT HISTORY                                               |

|    | D. RESULTS                                                           |

|    | E. ACKNOWLEDGMENTS                                                   |

| П  | . SIFT Hardware                                                      |

|    | A. SIFT HARDWARE DESIGN                                              |

|    | 1. Introduction                                                      |

|    | 2. General Structure                                                 |

|    | 3. Interconnection System 20                                         |

|    | 4. CPU 2                                                             |

|    | 5. Memory                                                            |

|    | 6. Discrete Functions 2                                              |

|    | 7. External I/O                                                      |

|    | 8. Test Control                                                      |

|    | 9. Comparative Analysis of the Original and Final SIFT Bus Systems 3 |

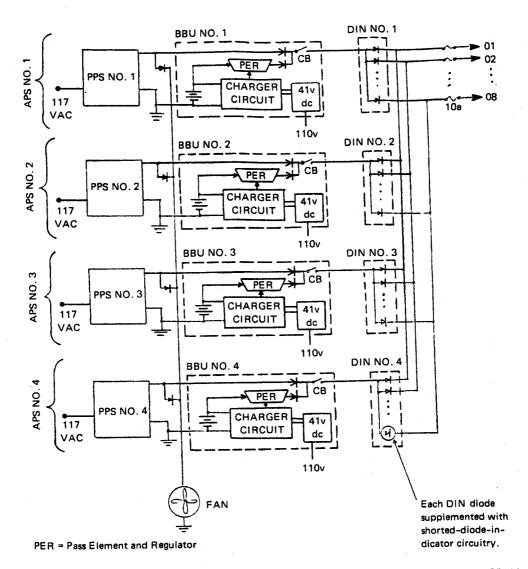

|    | B. THE SIFT FAULT-TOLERANT POWER SUPPLY  3                           |

|    | 1. Introduction 3                                                    |

|    | 2. Brief Description of the FTPS                                     |

|    | 3. Testing Strategy 4                                                |

|    | 4. Conclusions                                                       |

| П  | I. SIFT Software                                                     |

|    | A. ORGANIZATION AND DESIGN 4                                         |

|    | 1. Introduction 4                                                    |

|    | 2. Processing and Inter-process Communication 4                      |

|    | a. Processing Structure 4                                            |

|    | b. Inter-process Communication 4                                     |

|    | 3. The SIFT operating system 4                                       |

|    | a. The SIFT Hierarchy 4                                              |

|    | b. Design for Provability 4                                          |

| c. Organization of Processing and Communication in SIFT      | 49        |

|--------------------------------------------------------------|-----------|

|                                                              | 50        |

|                                                              | 51        |

| f. The Voter                                                 | <b>52</b> |

| ·                                                            | 54        |

| h. Fault Diagnosis and Reconfiguration                       | 54        |

| i. Clock Synchronization 5                                   | 57        |

| B. SIFT EXECUTIVE SOFTWARE SPECIFICATIONS                    | 64        |

| 1. Introduction                                              | 64        |

| 2. The Type Declarations                                     | 65        |

| 3. The Parameter Declarations                                | 65        |

| 4. The Definitions                                           | 66        |

| 5. The Parameter Invariants                                  | 67        |

| 6. The Specification Functions                               | 68        |

| C. PASCAL CODE FOR THE VOTER                                 | 69        |

| IV. Validation and Verification 7                            | 75        |

| A. THE MARKOV RELIABILITY MODEL                              | 75        |

|                                                              | 95        |

| VERIFICATION OF THE DESIGN OF SIFT                           |           |

| 1. The Role of Formal Proof                                  | 95        |

| 2. Mechanized Specification and Verification                 | 98        |

| 3. An Outline of the Specification Hierarchy                 | 98        |

| 4. Input/Output Specification                                | 00        |

| 5. The Replication Specification                             | 02        |

| 6. The Activity Specification                                | 05        |

| 7. PrePost and Imperative Levels                             | 10        |

| 8. Conclusions and Further Work                              | 12        |

| Appendix A. SIFT Test Plan                                   | 21        |

| 1 Test Philosophy and Goals                                  | 21        |

| 2 Test Strategy and Approach                                 | 23        |

|                                                              | 35        |

| 4 SIFT Software Needed for Diagnosis and Testing             | 39        |

| Appendix B.                                                  | 45        |

| 1. Introduction                                              | 45        |

|                                                              | 46        |

|                                                              | 49        |

|                                                              | <b>52</b> |

|                                                              | 64        |

| Appendix C. Summary of the SPECIAL Specification Language 16 |           |

|                                                              | 67        |

|                                                              | 67        |

| 3. Expressions in SPECIAL                     | 17 | 0          |

|-----------------------------------------------|----|------------|

| 4. Role of "?" in SPECIAL                     | 17 | 1          |

| 5. Specification of "stacks"                  | 17 | 1          |

| 6. Specification of V-functions               | 17 | 2          |

| 7. Specification of O- and OV-functions       | 17 | 3          |

| Appendix D. SIFT Specifications in SPECIAL    | 17 | 5          |

| Appendix E. The 1553A Aircraft I/O Controller | 18 | 8          |

| 1. Introduction                               | 18 | 38         |

| 2. General Characteristics                    | 18 | }{         |

| 3. Detailed Design                            | 18 | 36         |

| Appendix F. Task Programming                  | 19 | 7          |

| 1. Introduction                               | 19 | )7         |

| 2. Task Dependency Analysis                   | 19 | )7         |

| 3. Application Program Scheduling             | 19 | )7         |

| 4. Table Creation                             | 19 | <b>)</b> { |

| Dufferences                                   | 20 | 13         |

•

# List of Figures

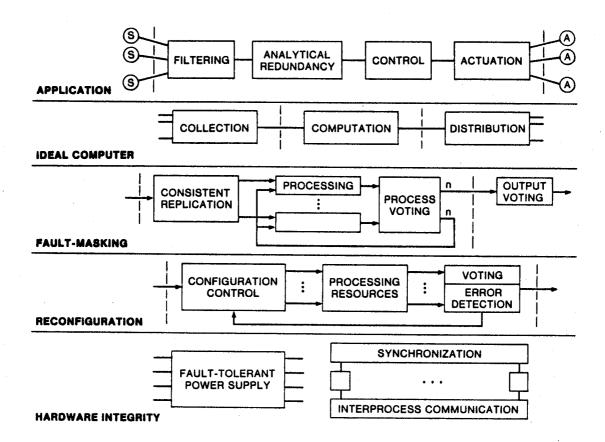

| Figure I-1:   | SIFT Virtual-Machine Hierarchy                                  | 8         |

|---------------|-----------------------------------------------------------------|-----------|

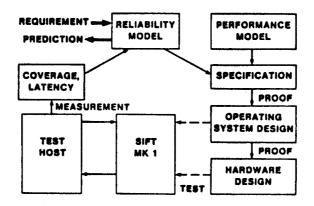

| Figure I-2:   | SIFT Validation Scheme                                          | 10        |

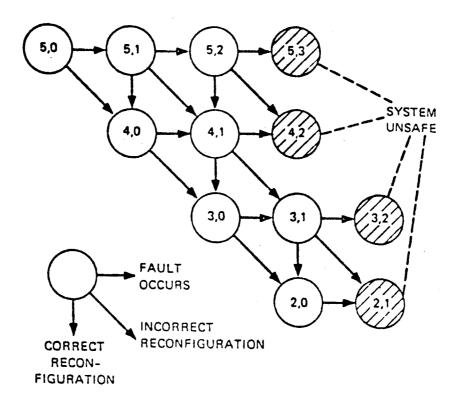

| Figure I-3:   | A Partial View of the Reliability Model                         | 10        |

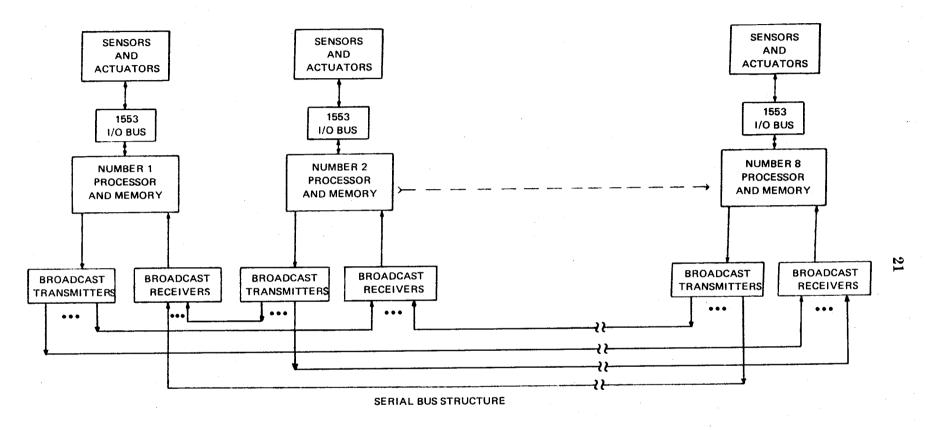

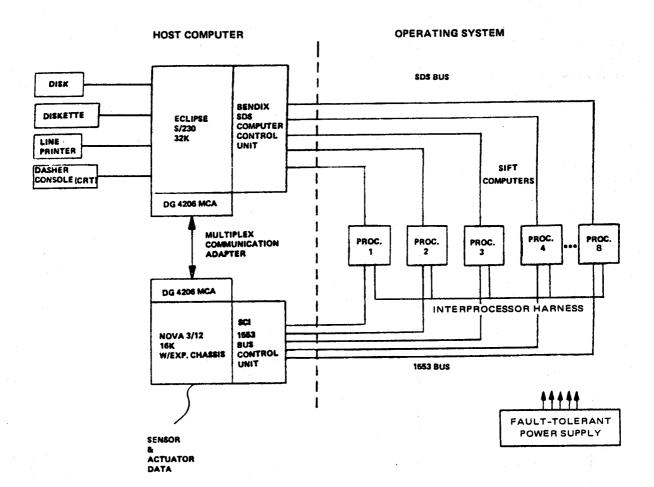

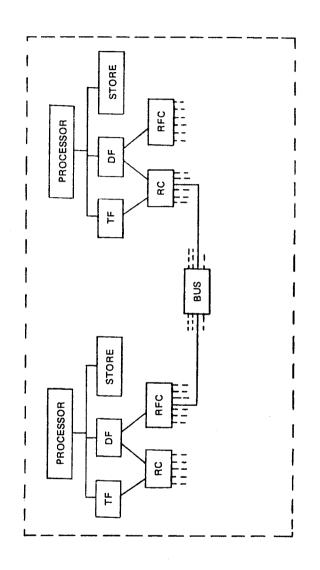

| Figure II-1:  | SIFT Architecture                                               | 21        |

| Figure II-2:  | SIFT Processor Design                                           | 22        |

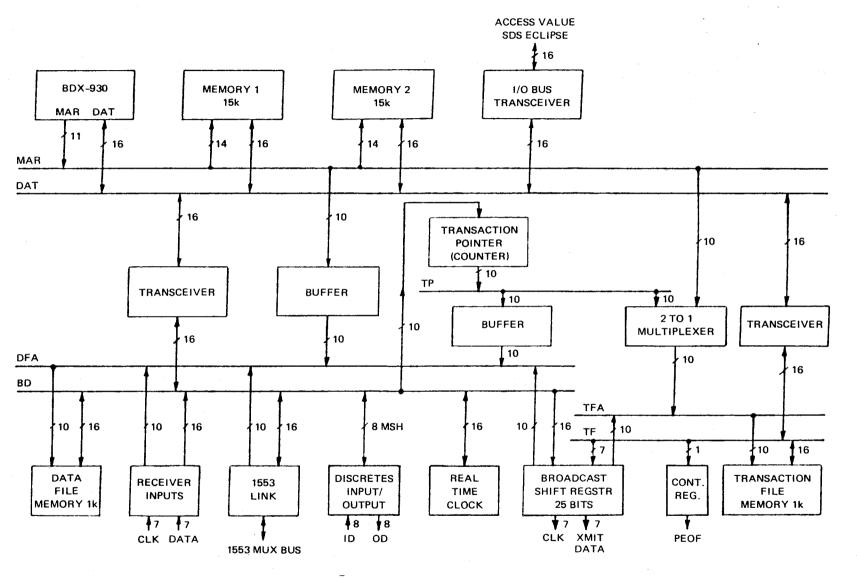

| Figure II-3:  | Broadcast Sequencer                                             | 24        |

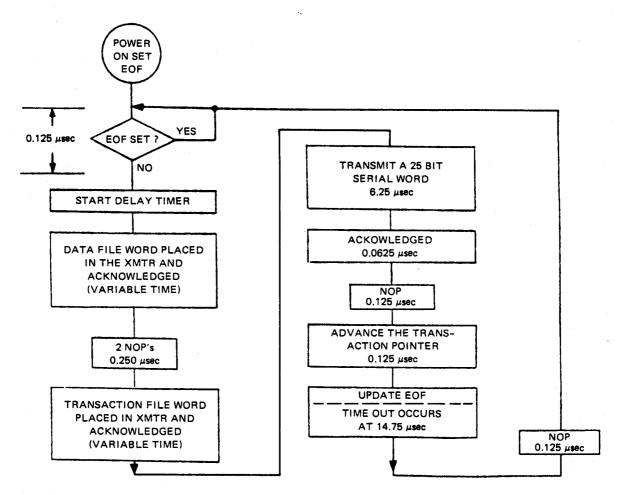

| Figure II-4:  | Serial Word Format                                              | 24        |

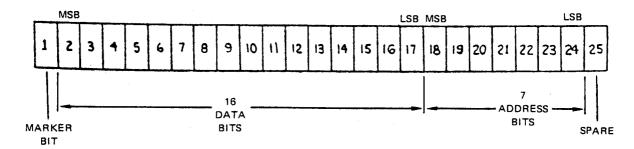

| Figure II-5:  | Receiver Module                                                 | <b>25</b> |

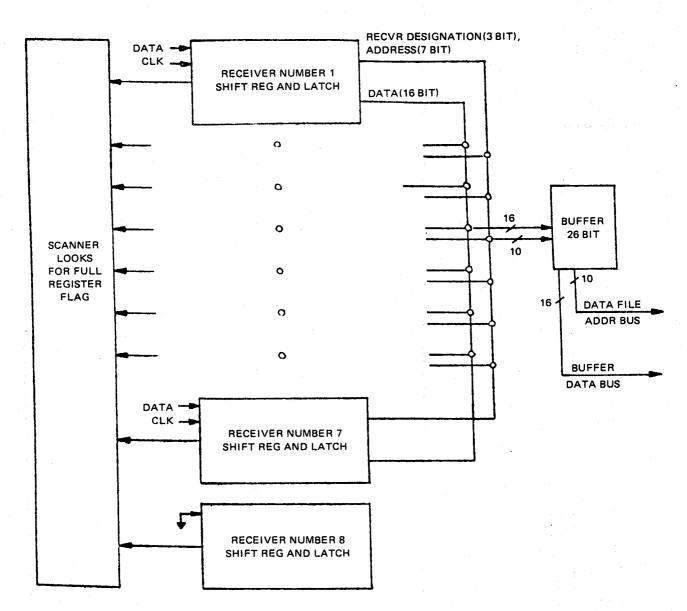

| Figure II-6:  | Receiver Sequencer                                              | 26        |

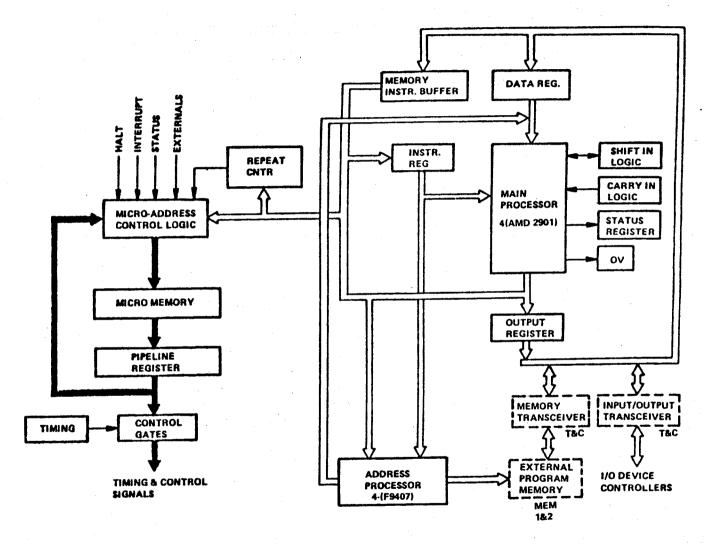

| Figure II-7:  | BDX-930 Processor Block Diagram                                 | <b>27</b> |

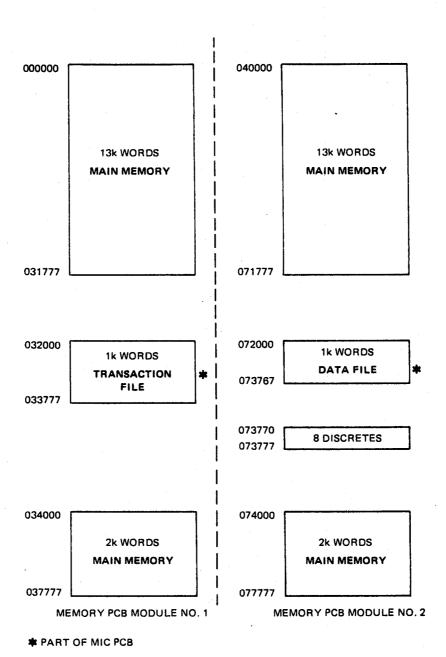

| Figure II-8:  | Memory Map                                                      | 29        |

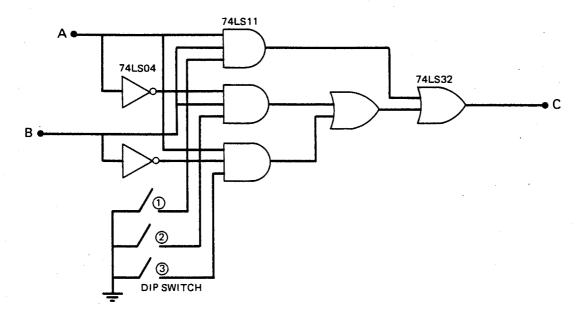

| Figure II-9:  | Discretes                                                       | 30        |

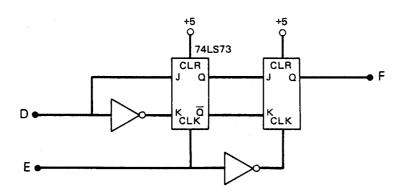

| Figure II-10: | Test Control System                                             | 31        |

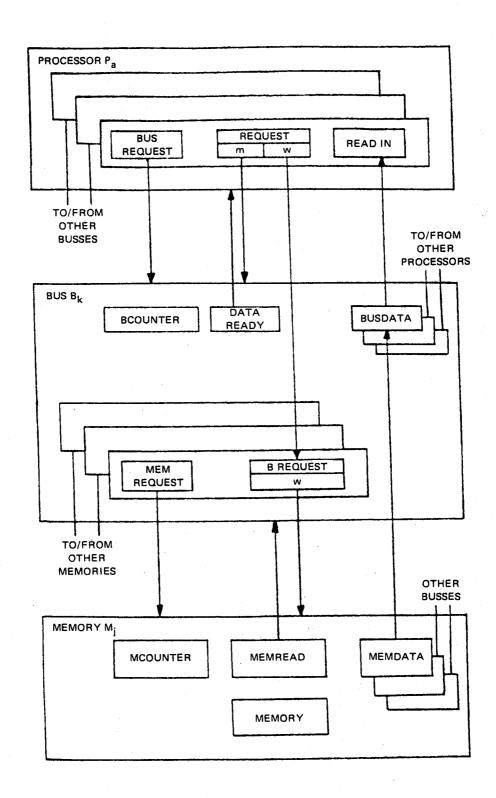

| Figure II-11: | Original Demand-Bus Design                                      | 32        |

| Figure II-12: | Interprocessor Communication in the Demand-Bus Design           | 33        |

|               | (Superseded)                                                    | ~         |

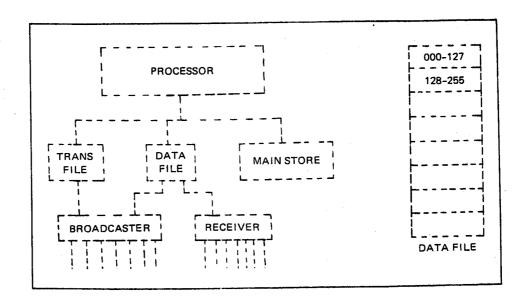

| Figure II-13: | Final (Broadcast) Design for Interprocessor Communication       | 37        |

| Figure II-14: | Schematic Diagram of Fault-Tolerant Power Supply                | 41        |

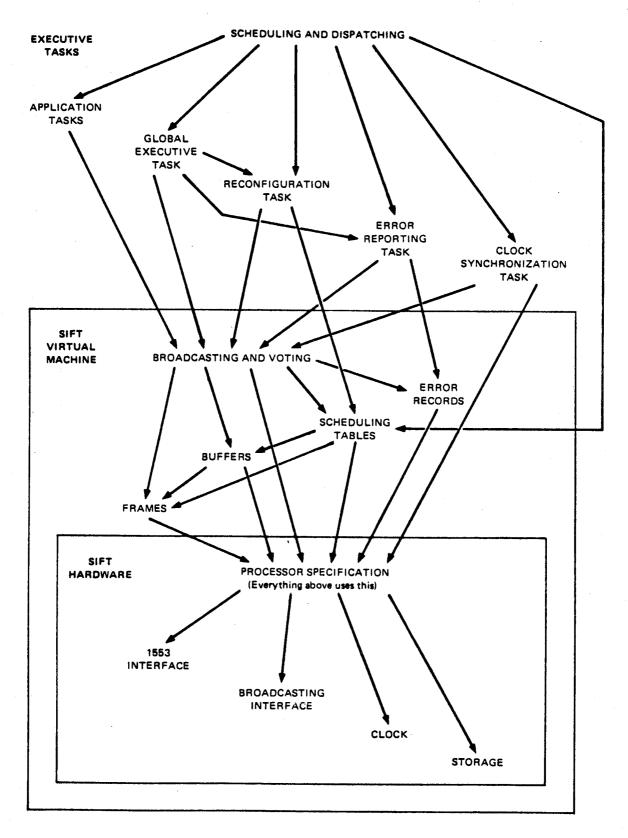

| Figure III-1: | The SIFT Specification Hierarchy                                | 48        |

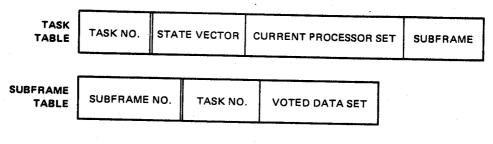

| Figure III-2: | Schedule Tables                                                 | 51        |

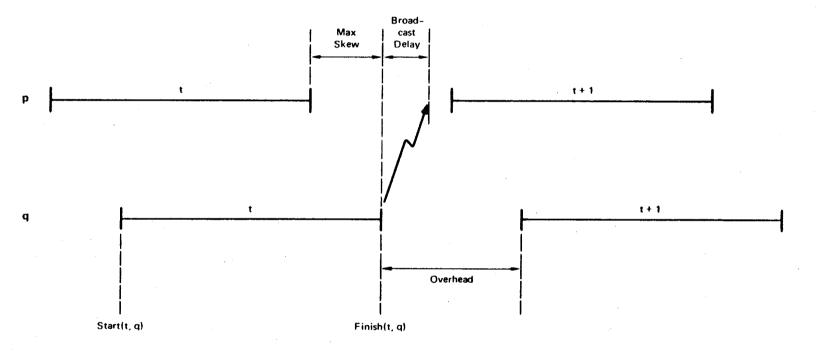

| Figure III-3: | Subframe Structure                                              | 52        |

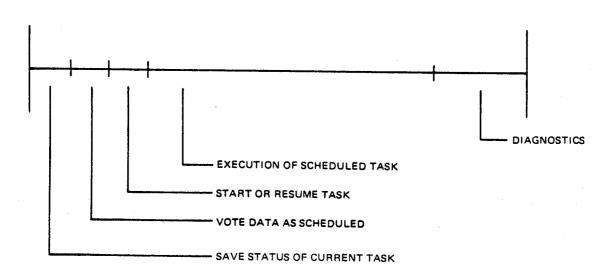

| Figure III-4: | Structure of a Typical Frame                                    | 53        |

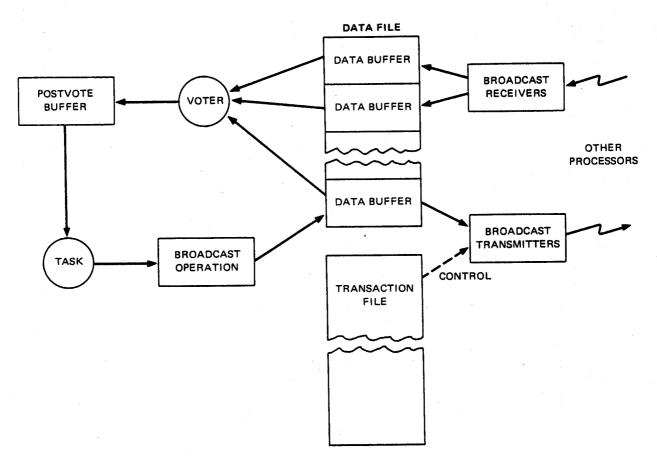

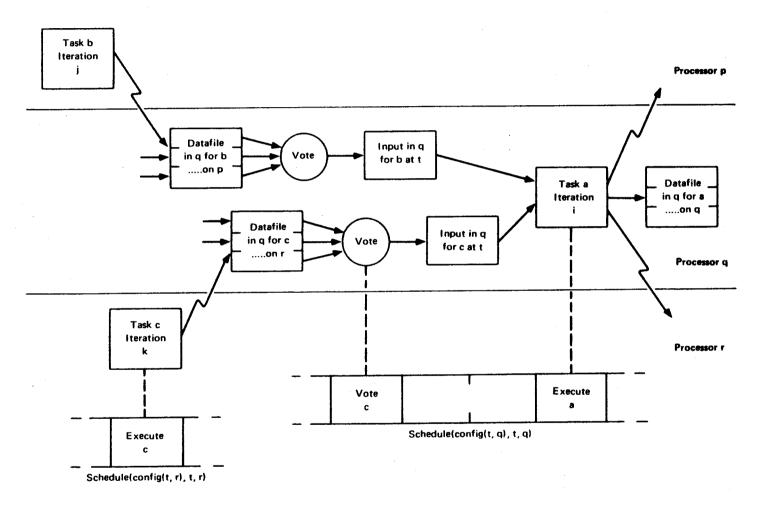

| Figure III-5: | System Data Flow                                                | 55        |

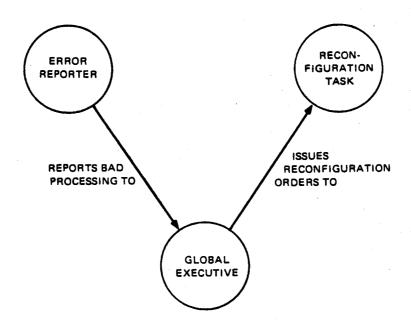

| Figure III-6: | Tasks Concerned with Reconfiguration                            | 57        |

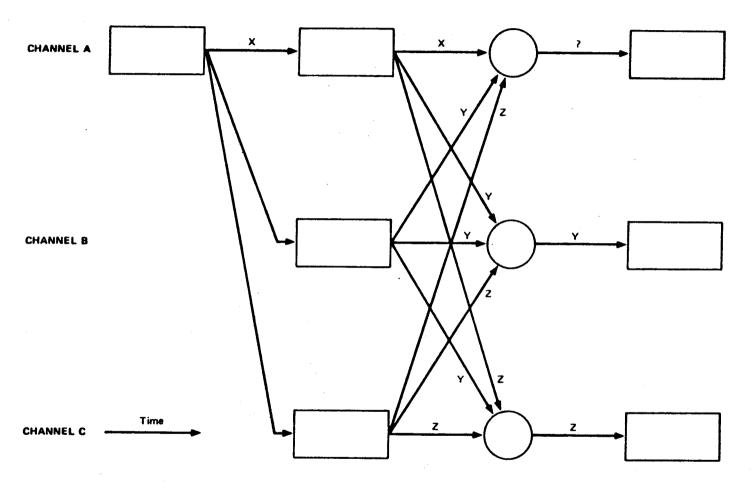

| Figure III-7: | Loss of Interactive Consistency in a Three-Channel System       | 62        |

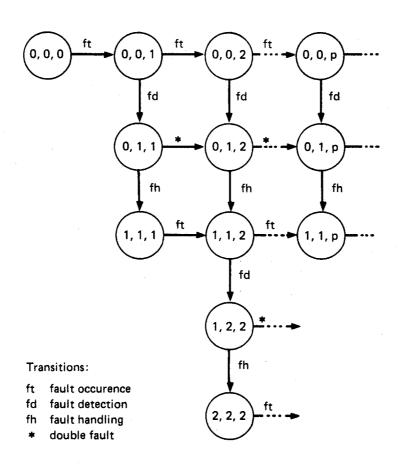

| Figure IV-1:  | Initial Reliability Model                                       | 77        |

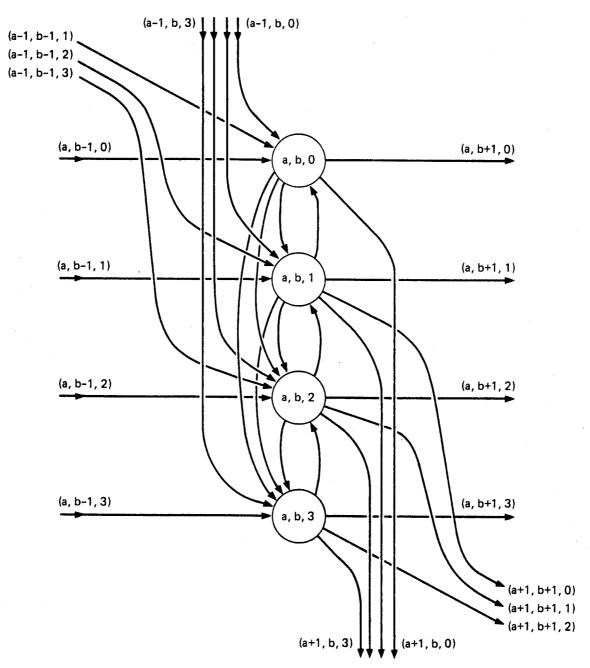

| Figure IV-2:  | The States of the New Markov Model for a 5 Processor            | 80        |

|               | System, Projected into the Plane of the First Two Indices       | 0.1       |

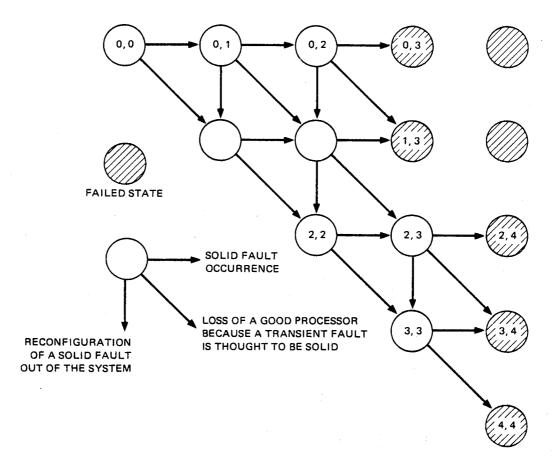

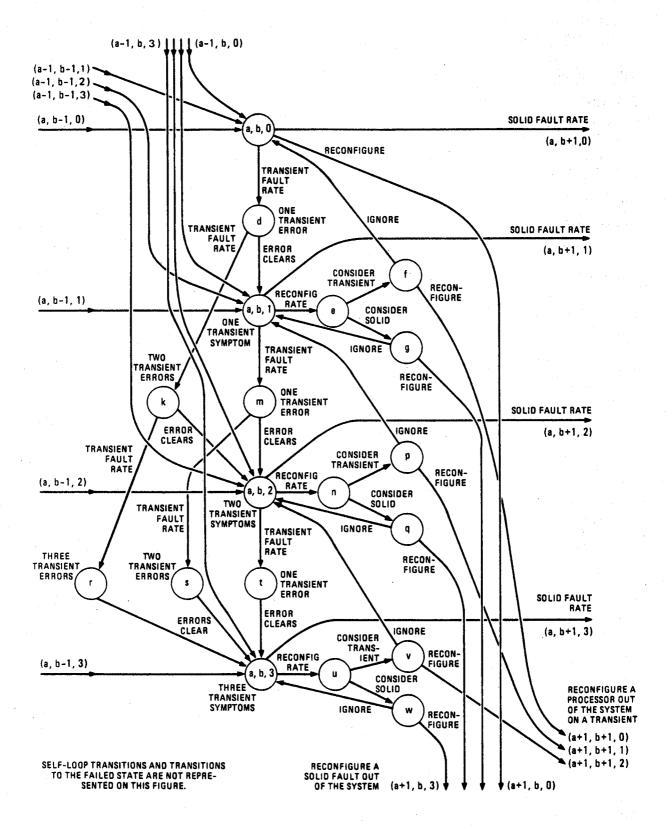

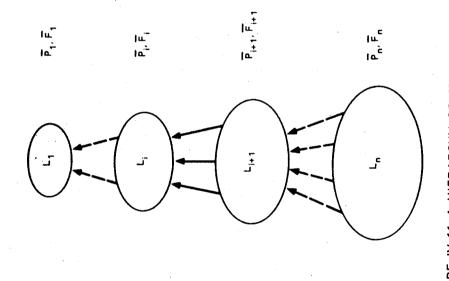

| Figure IV-3:  | A set of states and transitions resulting from transient errors | 81        |

|               | for one of the states of Figure IV-2.                           | 0.4       |

| Figure IV-4:  | A reduced set of equivalent states and transitions              | 84        |

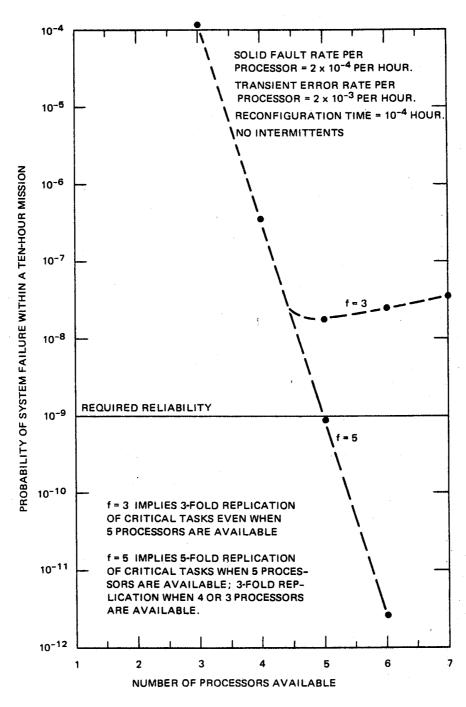

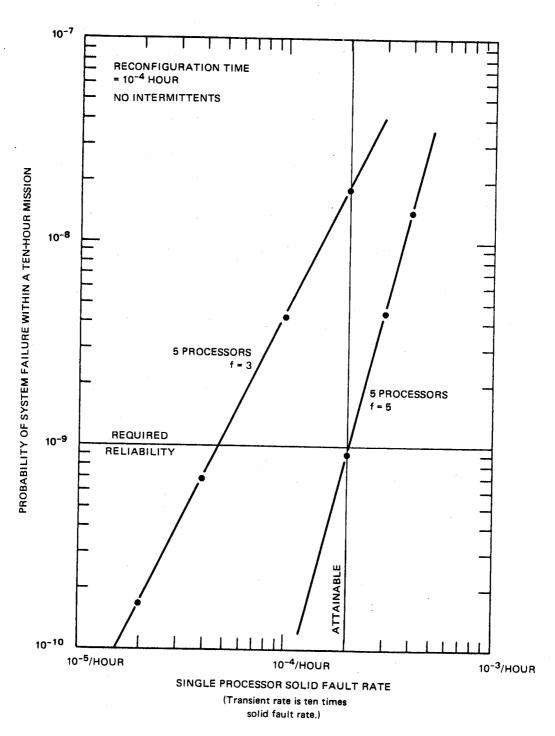

| Figure IV-5:  | Probability of System Failure Within a Ten Hour Mission vs.     | 87        |

|               | Number of Processors                                            | -00       |

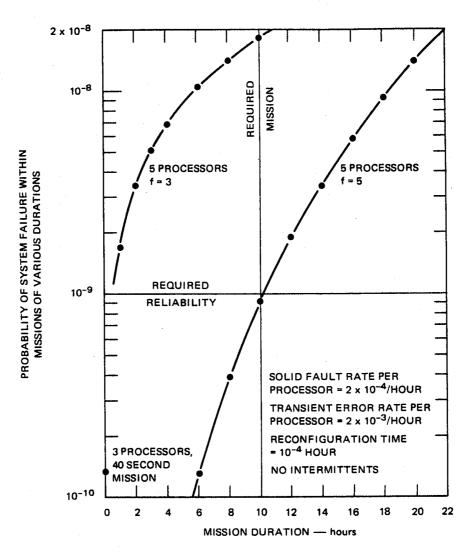

| Figure IV-6:  | Probability of System Failure Within Missions of Various        | 89        |

|               | Durations                                                       | 00        |

| Figure IV-7:  | Probability of System Failure Within a Ten Hour Mission vs.     | 90        |

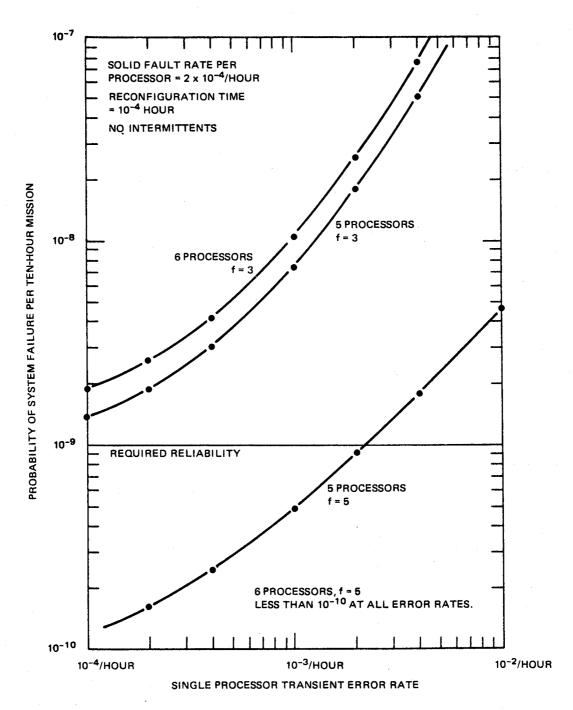

|               | Solid Fault Rate                                                | 01        |

| Figure IV-8:  | Probability of System Failure Per Ten Hour Mission vs.          | 91        |

| ·<br>·        | Transient Error Rate                                            | 92        |

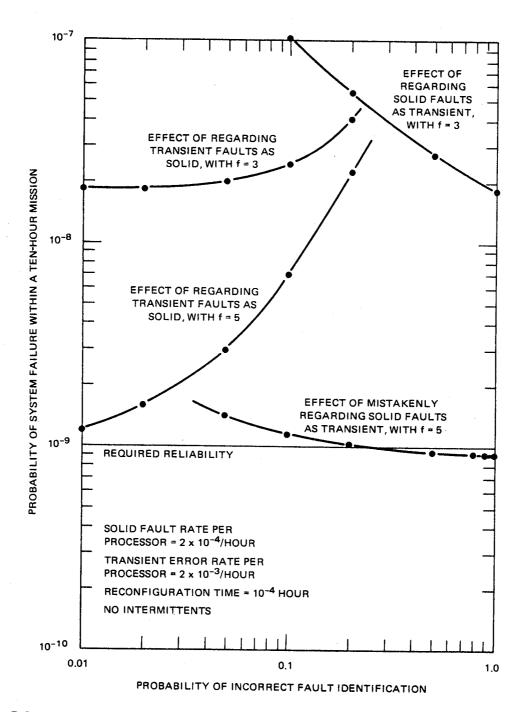

| Figure IV-9:  | Probability of System Failure Within a Ten Hour Mission vs.     | 92        |

|               | Probability of Incorrect Fault Identification                   | 94        |

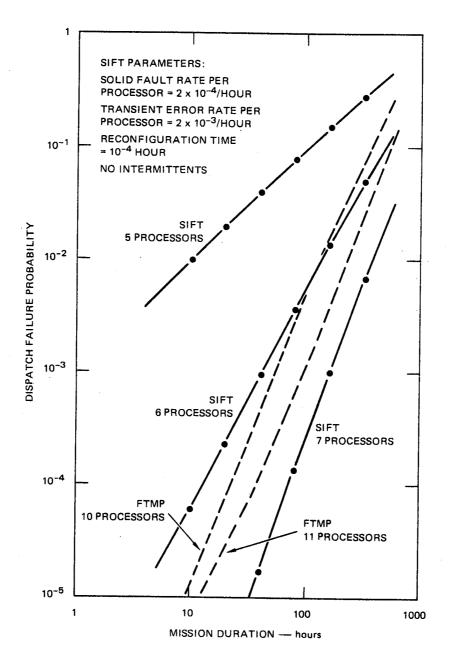

| Figure IV-10: | Dispatch Failure Probability                                    | 94        |

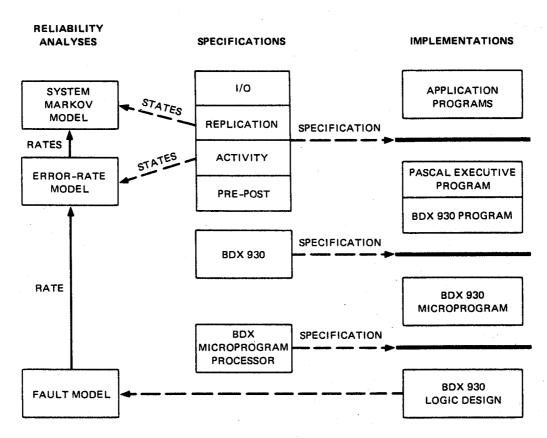

| Figure IV-11:                                              | A Hierarchy of Specifications                               | 114 |  |  |  |  |

|------------------------------------------------------------|-------------------------------------------------------------|-----|--|--|--|--|

| Figure IV-12:                                              | The Hierarchy of Specifications and Analyses Used to        | 115 |  |  |  |  |

|                                                            | Substantiate the Reliability of SIFT                        |     |  |  |  |  |

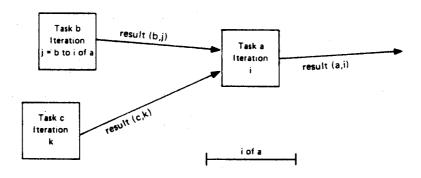

| Figure IV-13: Three Tasks in the I/O Specification         |                                                             |     |  |  |  |  |

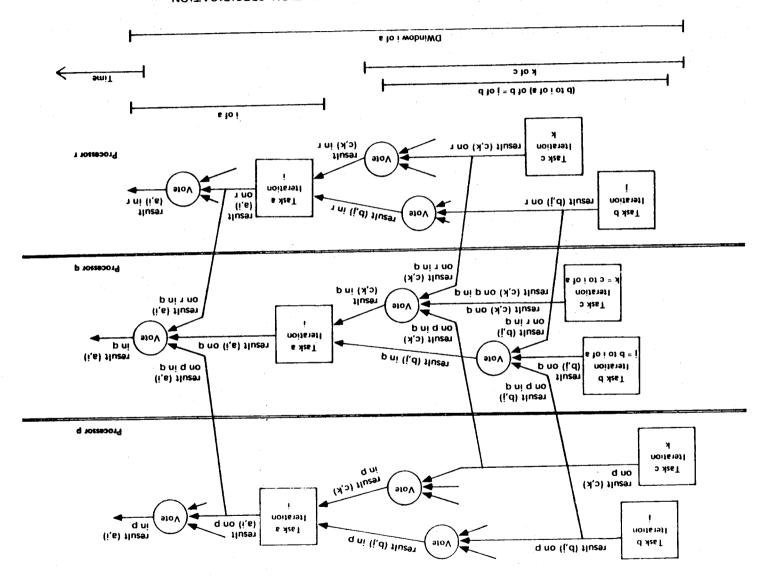

| Figure IV-14: Three Tasks in the Replication Specification |                                                             |     |  |  |  |  |

| Figure IV-15:                                              | The Timing Relationships Between Subframes on               | 118 |  |  |  |  |

| _                                                          | Asynchronous Processors                                     |     |  |  |  |  |

| Figure IV-16:                                              | A Partial View of Three Tasks in the Activity Specification | 119 |  |  |  |  |

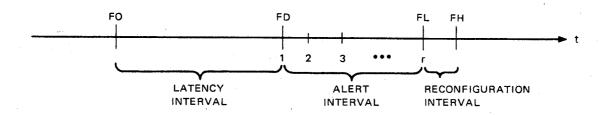

| Figure A-1:                                                | 'igure A-1: Life Cycle of a Permanent Fault 12              |     |  |  |  |  |

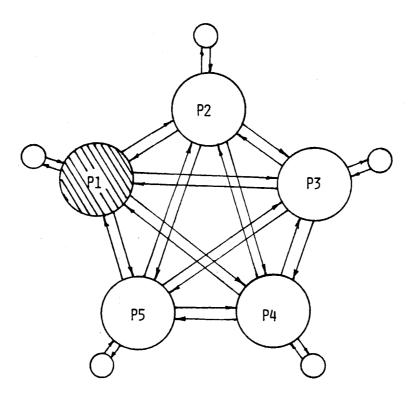

| Figure A-2:                                                | Five-Processor SIFT Configuration 128                       |     |  |  |  |  |

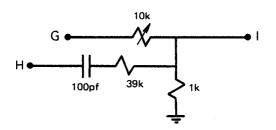

| Figure A-3:                                                | Figure A-3: Test Board Circuits                             |     |  |  |  |  |

| Figure C-1:                                                | C-1: Specification of the STACKS module 169                 |     |  |  |  |  |

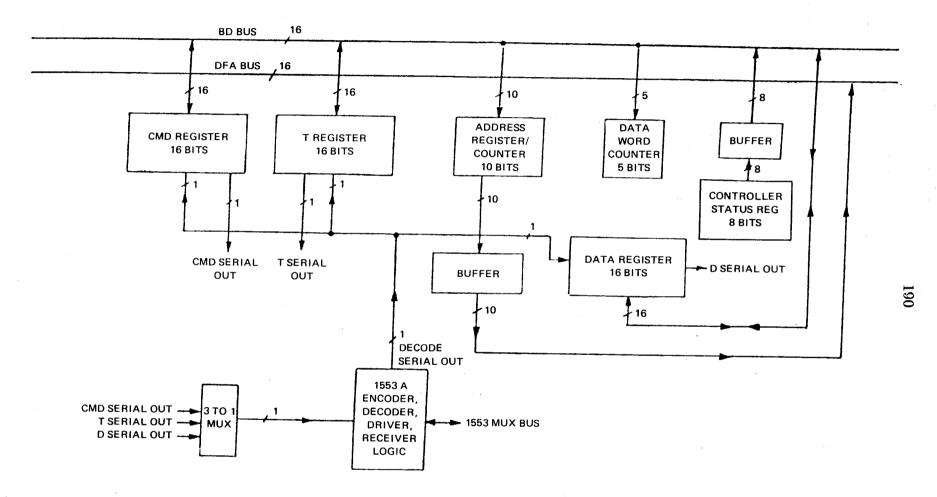

| Figure E-1:                                                | 1553 Link                                                   | 190 |  |  |  |  |

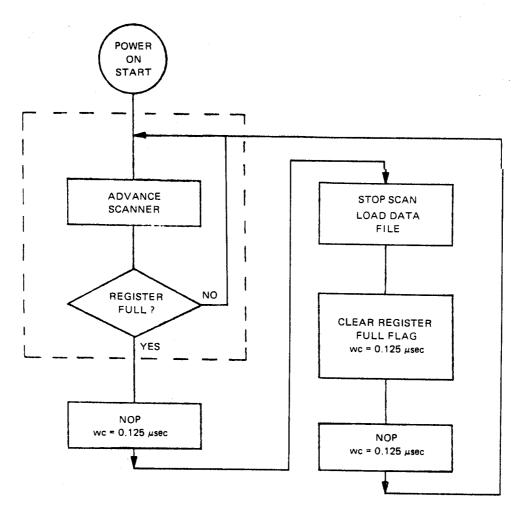

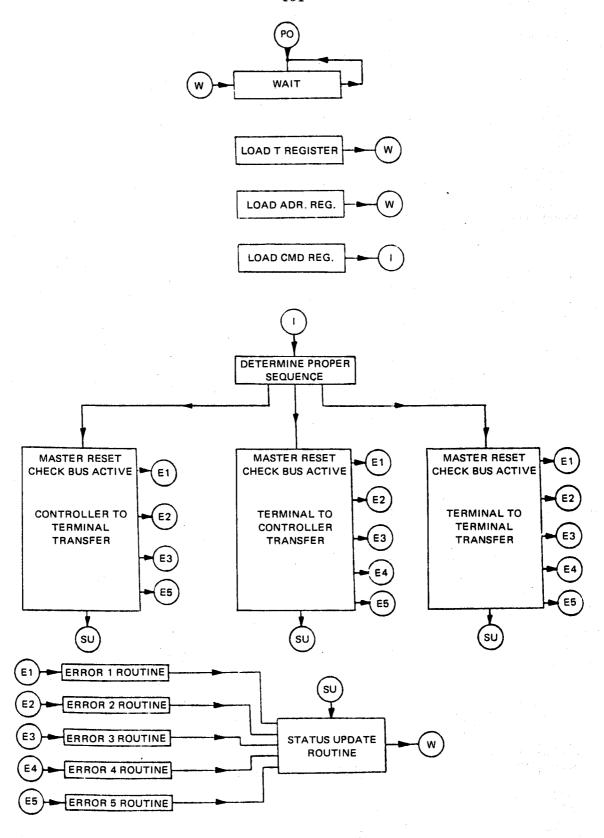

| Figure E-2:                                                | 1553A Flow Chart                                            | 191 |  |  |  |  |

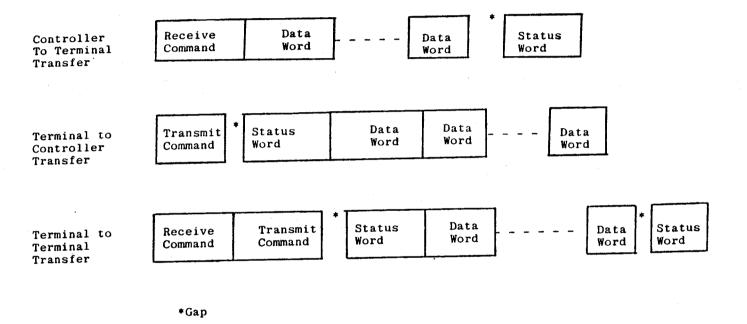

| Figure E-3:                                                | Message Formats                                             | 193 |  |  |  |  |

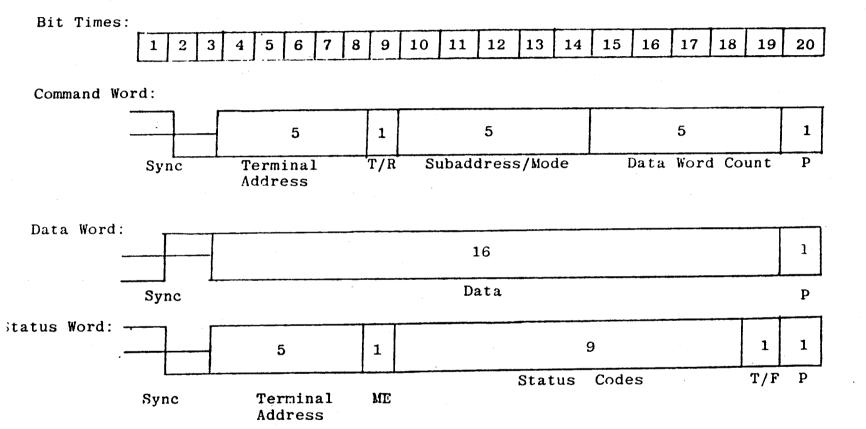

| Figure E-4:                                                | Word Formats                                                | 195 |  |  |  |  |

# List of Tables

| Table II-1: | Interconnecting-Bus System (8 processors, 8 busses) - No                                 | 35         |  |  |  |

|-------------|------------------------------------------------------------------------------------------|------------|--|--|--|

|             | Bus- or Memory-Contention Delays                                                         |            |  |  |  |

| Table II-2: | Time to Complete Specified Operations in Receiver Sequencer                              | 38         |  |  |  |

|             | Loop                                                                                     |            |  |  |  |

| Table IV-1: | Failure Probability for Various Causes                                                   | <b>7</b> 8 |  |  |  |

| Table IV-2: | : The transition rates between the states of Figure IV-3                                 |            |  |  |  |

| Table IV-3: | A set of transition rates appropriate to the reduced set of states shown in Figure IV-4. | 85         |  |  |  |

| Table IV-4: | The meanings of symbols used in the rates of Tables IV-2 and IV-3                        | 85         |  |  |  |

| Table A-1:  | Test Board Connection Points for Fault Injection                                         | 132        |  |  |  |

| Table A-2:  | Permutation Tests                                                                        | 136        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | p• v |  | - |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|---|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·    |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |   |  |

| and the second s |      |  |   |  |

# I. Summary of Results

This chapter presents an overview of the SIFT computer system and its development. Successive sections describe technical goals, design approaches and solutions, development history and significant technical results.

#### A. GOALS OF THE SIFT DEVELOPMENT

This section describes the goals of the SIFT development and the primary criteria that guided its design.

#### 1. Introduction

SIFT (Software-Implemented Fault Tolerance) is an experimental computer system designed to provide extremely reliable computing service for critical functions in advanced air transports. An example of such critical use is the control of dynamically unstable aircraft, designed for high energy efficiency. The SIFT design is intended to assure correct execution of aircraft control programs despite the occurrence of computer hardware malfunctions. The design does not address other sources of system unreliability, such as incorrect flight-control programs and faulty sensors, actuators, and communication channels, but techniques for program correctness were employed that have significant potential for the goal of highly reliable aircraft software.

The SIFT development was intended to apply techniques of fault-tolerant computer architecture to a very demanding aircraft application. Early in the effort, it became clear that the problem of estimating the reliability of machines designed for this application was beyond the state of the art, due to (1) the extremely low acceptable probability of system failure, which made life-testing totally impractical, and (2) the potentially high complexity of fault-tolerant systems, which made logical analysis very difficult. These characteristics will inevitably cast doubt on any reliability predictions for fault-tolerant systems, because the model used for the prediction either might not truly represent the real system, or it might be so highly simplified that the important parameters might be effectively unmeasurable. For this reason, project goals were extended to include development of new techniques for analyzing the reliability of fault-tolerant computer systems.