## Development of a Highly Integrated 10 kV SiC MOSFET Power Module with a Direct Jet Impingement Cooling System

B. Mouawad<sup>\*</sup>, C. DiMarino<sup>+</sup>, R. Skuriat<sup>\*</sup>, J. Li<sup>\*</sup>, C. M. Johnson<sup>\*</sup> \*Power Electronics, Machines and Control, University of Nottingham, Nottingham, UK <u>bassem.mouawad@nottingham.ac.uk</u> \*Center for Power Electronics Systems, Virginia Tech, Blacksburg, VA, USA

dimaricm@vt.edu

## **Purpose of Work**

This paper presents a novel, highly integrated packaging design for Wolfspeed's 10 kV SiC MOSFETs. These devices offer faster switching performance and lower losses than silicon devices. However, it has been shown that the package can have profound impacts on the module performance<sup>1</sup>. So, to reap the full benefits of these unique devices an optimized power module package must be developed. This work proposes a wire-bond-less, sandwich structure with embedded decoupling capacitors and stacked ceramic substrates in order to realize a high-density module with low parasitic inductance and low thermal resistance.

## Approach

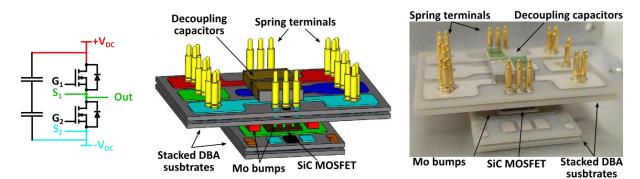

Figure 1 shows the designed power module. It is a half-bridge configuration with one 10 kV, 350 m $\Omega$  SiC MOSFET per switch. The module uses molybdenum (Mo) posts and a direct bonded aluminum (DBA) substrate for the interconnections instead of wire bonds. To address the enhanced electric field associated with a 10 kV, high-density design, two DBAs are stacked together, as reported in the work<sup>2</sup>. Mo posts were used in order to provide sufficient insulation distance between the top and bottom DBAs. It should especially be noted that the DBAs have filled vias to form the electrical connection between the MOSFETs and the top DBA.

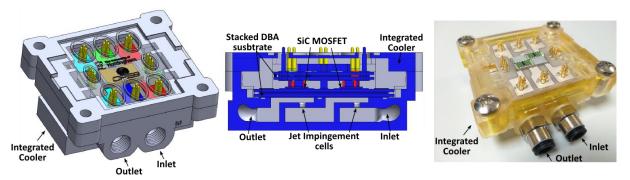

Instead of mounting the module onto a baseplate, a direct-substrate jet impingement cooling system was custom designed and fabricated. Each jet impingement cell is located under one SiC MOSFET where the coolant is sprayed on the bottom side of the stacked DBAs to extract the heat generated by the SiC MOSFETs, (see Fig. 2). As far as we are aware, this is the first time when a highly integrated design for 10 kV SiC MOSFETs with an integrated cooler is being reported.

## **Results and Significance**

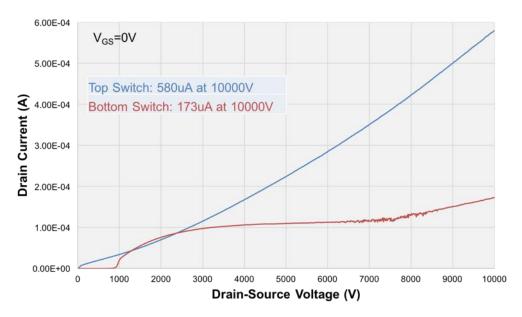

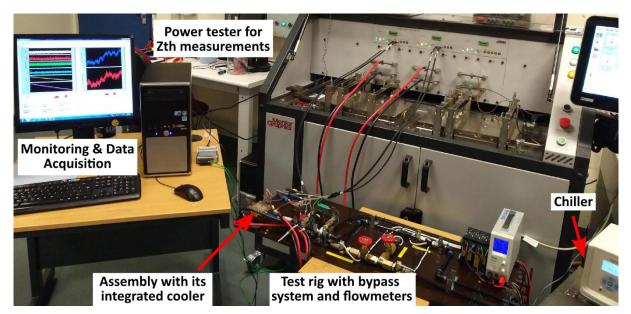

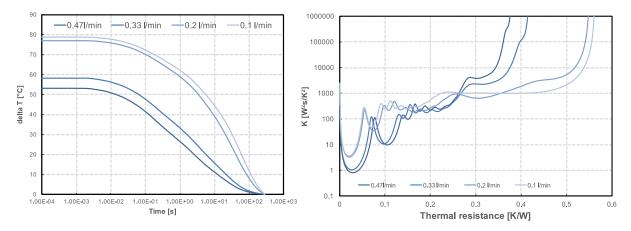

The proposed design was first assembled; see Fig. 1. Then it was installed in the designed integrated cooler and filled with silicone gel, see Fig. 2. The breakdown voltage tests verified that both switches have the capability of blocking the voltage up to 10 kV, see Fig. 3. To evaluate the performance of the designed cooler at different flowrates, a test rig with a bypass system was also designed and house made, see Fig. 4. It included four flowmeters, thermocouples and the pressure sensors at the inlet and outlet of the power module. Thermal impedance measurements were carried out on a Mentor Graphics power tester. The measured  $\Delta T$  and the differential structure function of transient thermal analysis of the assembled module are shown in Fig. 5. The lowest junction-to-ambient thermal resistance of the module was measured to be 0.38 K/W for a flowrate of 0.47 l/min with the integrated cooler. This value is lower than reported in the literature when using a stacked substrate structure<sup>3</sup>.

<sup>&</sup>lt;sup>1</sup> Z. Chen et *al.*, "Modeling and simulation of 2 kV 50 A SiC MOSFET/JBS power modules," in *IEEE Electric Ship Technologies Symposium (ESTS 2009)*, 2009, pp. 393–399

<sup>&</sup>lt;sup>2</sup> O. Hohlfeld et *al.*, "Stacked substrates for high voltage applications," in 7th International Conference on Integrated Power Electronics Systems (CIPS 2012), 2012.

<sup>&</sup>lt;sup>3</sup> F. Kato et *al.*, "Evaluation of Thermal Resistance Degradation of SiC Power Module Corresponding to Thermal Cycle Test," in *Conference & Exhibition on High Temperature Electronics Network (HiTEN 2017)*, 2017.

**Fig. 1:** Schematic and 3D model of the complete assembly. The color in the 3D model correspond to the node in the schematic with the same color. The right photo shows the assembled module with stacked DBAs, spring terminals and embedded capacitors.

**Fig. 2:** 3D model of the assembly with its integrated cooler. A cross-section of the 3D model shows the jet impingement cells cooling directly each SiC MOSFET at the back of the stacked DBA substrates. The right photo shows the assembled module embedded with its integrated cooler and filled with silicone gel.

Fig. 3: Breakdown voltage test preformed on the assemble module. It should be noted that the devices used for the assembly were semi-functional. However, they were able to block the voltage up to 10 kV with a leakage current of 580  $\mu$ A and 173  $\mu$ A for top and bottom switch, respectively. No breakdown or partial discharge could be detected.

**Fig. 4:** Test setup for thermal impedance measurements showing Mentor Graphics power tester; a chiller with DI water at 20°C; test rig with bypass system to regulate the flowrates through the assembled module, accomodating flowmeters, thermocouples and pressure sensors; and a PC for monitoring and data acquisition.

Fig. 5: Results of the thermal impedance measurement showing the  $\Delta T$  at different flowrates (left) and the differential structure function of the power module with the stacked DBA substrate at different flowrates (right). It should be noted that the thermal impedance measurements were performed on individual devices using the bodydiode of the 10 kV SiC MOSFET as a heating source with a heating power of 139 W.