Allport, P.P., Ashby, J., Bates, R.L., Blue, A., Burdin, S., Buttar, C.M., Casse, G., Dervan, P., Doonan, K., Forshaw, D., McMullen, T., Pater, J., Lipp, J., Stewart, A., and Tsurin, I. (2014) Development of planar pixel modules for the ATLAS high luminosity LHC tracker upgrade. Nuclear Instruments and Methods in Physics Research. Section A: Accelerators, Spectrometers, Detectors, and Associated Equipment, 765. pp. 109-113.

http://eprints.gla.ac.uk/95092/

Deposited on: 30 July 2014

Enlighten – Research publications by members of the University of Glasgow http://eprints.gla.ac.uk

ELSEVIER

Contents lists available at ScienceDirect

# Nuclear Instruments and Methods in Physics Research A

journal homepage: www.elsevier.com/locate/nima

# Development of planar pixel modules for the ATLAS high luminosity LHC tracker upgrade

P.P. Allport <sup>b</sup>, J. Ashby <sup>a</sup>, R.L. Bates <sup>a</sup>, A. Blue <sup>a</sup>, S. Burdin <sup>b</sup>, C.M. Buttar <sup>a,\*</sup>, G. Casse <sup>b</sup>, P. Dervan <sup>b</sup>, K. Doonan <sup>a</sup>, D. Forshaw <sup>b</sup>, J. Lipp <sup>d</sup>, T. McMullen <sup>a</sup>, J. Pater <sup>c</sup>, A. Stewart <sup>a</sup>, I. Tsurin <sup>b</sup>

- <sup>a</sup> SUPA, School of Physics and Astronomy, University of Glasgow, UK

- <sup>b</sup> Department of Physics, University of Liverpool, UK

- <sup>c</sup> School of Physics and Astronomy, University of Manchester, UK

- <sup>d</sup> The Science and Technology Facilities Council, Rutherford Appleton Laboratory, UK

#### ARTICLE INFO

Available online 1 July 2014

Keywords: HL-LHC Silicon detector Pixel detector ATLAS

#### ABSTRACT

The high-luminosity LHC will present significant challenges for tracking systems. ATLAS is preparing to upgrade the entire tracking system, which will include a significantly larger pixel detector. This paper reports on the development of large area planar detectors for the outer pixel layers and the pixel endcaps. Large area sensors have been fabricated and mounted onto 4 FE-I4 readout ASICs, the so-called quad-modules, and their performance evaluated in the laboratory and testbeam. Results from characterisation of sensors prior to assembly, experience with module assembly, including bump-bonding and results from laboratory and testbeam studies are presented.

© 2014 The Authors. Published by Elsevier B.V. This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/3.0/).

## 1. Introduction

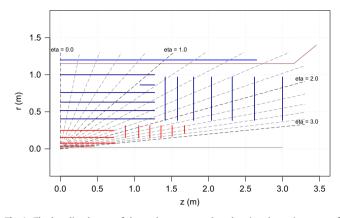

The Large Hadron Collider will undergo a series of upgrades over the next decade, increasing both the energy and the luminosity, culminating in the Phase-II upgrade that will deliver an unprecedented instantaneous luminosity of  $5 \times 10^{34} \, \mathrm{cm}^{-2} \, \mathrm{s}^{-1}$  at an energy of 14 TeV, with the aim of delivering 3000 fb<sup>-1</sup> to ATLAS over 10 years. The extended LHC running will exceed the lifetime of the current ATLAS tracker. The increase in the instantaneous luminosity will increase the multiplicity of pp interactions from  $\sim 55$  at the Phase-I luminosity to  $\sim 140$  requiring a tracking detector with greater granularity to maintain the occupancy at  $\sim 1\%$ , which has been shown to give good tracking performance with the current tracker. The integrated luminosity will require the trackers to operate after integrated fluences of  $2 \times 10^{16} \, 1 \, \mathrm{MeVn}_{eq} \, \mathrm{cm}^{-2}$  at the inner radius. It is proposed to develop and construct a new tracker for ATLAS over the next 10 years [1] ready for the start of Phase-II operation around 2024. The proposed layout is shown in Fig. 1.

This paper focusses on the development of large area pixel modules for the outer barrel layers and forward disks of the pixel system. These areas will be exposed to a maximum integrated fluence of  $1.8 \times 10^{15}$  1 MeVn<sub>eq</sub> cm<sup>-2</sup> and 0.9 MGy [1]. The leading

silicon based technology for this region is n-in-p as it has demonstrated radiation hardness at these levels and can be manufactured at a scale and cost suitable for particle physics experiments. To cope with the increased occupancy the pixel size is reduced from 50  $\mu m \times 400~\mu m$ , as used in the current detector, to 50  $\mu m \times 250~\mu m$ . To minimise material, the active area of the pixel modules should be  $\geq 90\%$  and the thickness of the modules should be reduced by thinning the modules i.e. both the sensors and readout ASICs to 150  $\mu m$  or less. The upgraded pixel system will be significantly larger than the current system, increasing in area from 1.7  $m^2$  to 8.2  $m^2$ , corresponding to an increase in the number of channels from 80 million to 638 million.

#### 2. Sensor design

The construction of the upgraded pixel system, which has an area about 4 times larger than the current system, requires the yield and cost of pixel sensor production to be optimised. This can be partially addressed by using large area readout ASICs and sensors as this reduces the cost of bump-bonding, which scales approximately with the number of chips processed rather than by the total area. The "quad" sensor is a large area sensor that is compatible with the geometry of the outer barrel layers and forward disks of the upgraded pixel tracker, and is read out with 4 FE-I4 readout ASICs, [2]. It has an active area of 40.4 mm × 34.4 mm for "test" FE-I4s and

<sup>\*</sup>Corresponding author.

E-mail address: craig.buttar@glasgow.ac.uk (C.M. Buttar).

**Fig. 1.** The baseline layout of the replacement tracker showing the active areas of silicon detectors arranged on cylinders and disks. The strip system is shown in blue and the pixel system is shown in red. (For interpretation of the references to colour in this figure caption, the reader is referred to the web version of this paper.)

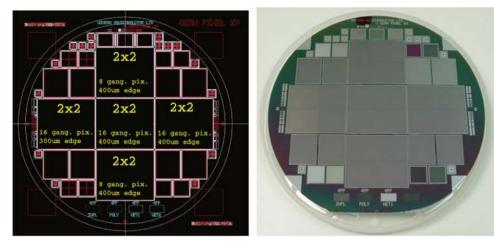

40.4 mm × 34 mm for "production" FE-I4s. As discussed in the introduction, it is important to maximise the active area of the sensor and to avoid inactive regions at the borders of the FE-I4 chips. Long pixels of 450  $\mu m$  are added to bridge the gap along the long pixel direction. Sets of ganged pixels are used to bridge the gap along the short pixel direction. Two designs of ganged pixels were made for the "test" and "production" FE-I4 chips. The "test" chips have an additional row of test circuits, and extend the length of the FE-I4 by about  $100 \, \mu m$  along the short pixel direction, while the "production" chips have had the additional circuitry removed. Depending on the design 4 or 8 pixels were added in the region between the FE-I4s and connected via top metal layer to pixels that are bump-bonded to the FE-I4. This results in an ambiguity in the hit position that will have to be resolved in reconstruction. The sensors have been manufactured on 300  $\mu m$  thick 10  $k\Omega$  cm<sup>-1</sup> p-type Si 6" wafers by Micron Semiconductor Ltd.<sup>1</sup> with the segmented side made using a heavily doped n-type implant and p-spray isolation. The wafers contained five quad sensors and eight sensors with a geometry corresponding to a single FE-I4. The layout together with a manufactured wafer is shown in Fig. 2.

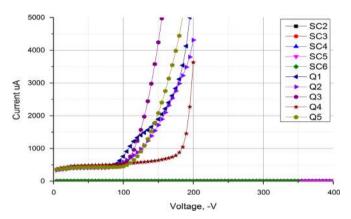

The sensor yield has been measured on the wafer based on measuring the current-voltage (I–V) curve. Sensor yields of 97% for quad sensors, based on evaluating 35 devices from 7 wafers, and 78% for single devices, based on evaluating 49 devices from the same 7 wafers, have been achieved, using the criteria that the leakage current measured at 50 V above the depletion voltage (70 V) is less than 1.5  $\mu A$  and there is no sharp breakdown. The I–V for the quads and single chip sensors from a typical wafer is shown in Fig. 3. On the wafer, the devices are biased via a punchthrough structure. The leakage currents of the quad sensors at 20 °C were measured to be  $\sim$  500 nA at a bias voltage of 100 V, corresponding to  $\sim 40 \text{ nA cm}^{-2}$ . After assembly into a module, when the pixels are biased through the FE-I4, the current is found to be  $\sim 100$  nA, corresponding to 8 nA cm<sup>-2</sup> and which is comparable to the currents measured for single chip modules of  $\sim 3 \text{ nA cm}^{-2}$  [3]. This indicates that the punchthrough bias structure needs to be optimised and a new design was implemented on a later wafer design [4]. As mentioned above, it is important to maximise the active area of the sensor. The guard-ring represents a significant inactive area on the sensor. To investigate if this can be reduced, two guard ring designs were implemented: a standard design with 7 guard rings, corresponding to an inactive edge distance of 450 µm and a design with 5 guard rings, corresponding to an inactive edge distance of 300  $\mu m$ . The reduced guard ring design could lead to increased leakage current or lower breakdown voltages, but no difference in the I–V between the two designs was observed.

#### 3. Module assembly

The quad modules were assembled at VTT² where both the FE-I4 and sensor wafers had under bump metallisation, UBM, and PbSn solder bumps deposited. The four FE-I4 chips were then flipped on to the sensor, one at a time, and a tack bond formed. The assembly was then moved to a reflow oven, where the assembly was heated to 260 °C [3]. As discussed in the introduction the target thickness for both the sensor and the FE-I4 is around 150 µm to minimise the material. For the first attempt to assemble a module with a thinned sensor and readout chip, one of the FE-I4 and sensor wafers was back thinned to 200 µm after the UBM and bumps were deposited. The I–V of the sensors was monitored throughout the process and no significant differences were observed between the measured on-wafer I–V curve prior to UBM deposition and after processing and dicing [3].

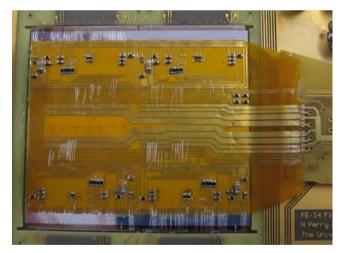

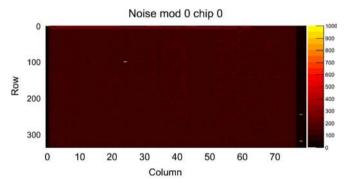

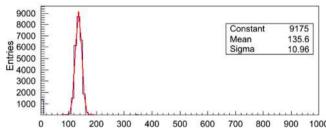

Power and data connections were made via a hybrid flex supplied by the University of Bonn that was glued to the rear of the sensor and wire bond connections made between the hybrid and the FE-I4. The assembly was then mounted on a PCB and the end of the flex connected to the PCB via wire bonds, as shown in Fig. 4. The assembly was then operated using the USBpix readout system. This provides the control sequences required to configure and readout the FE-I4 and a switch on the PCB allowed each chip to be characterised. A chip was tuned to a threshold of 3200 e and 1600 e. Tuning to 1600 e with a bias of 100 V applied, gave a measured threshold of 1645 e with a standard deviation of 32 e, and a noise of 133 e, comparable to that measured for single chip modules [3]. The noise map and distribution are shown in Fig. 5. The bump yield of the thinned module was evaluated by comparing the noise distribution after tuning with and without bias applied. The channels for which the noise does not decrease when the bias is applied are assumed to be disconnected. A large fraction of channels around the edge of the module were found to be disconnected, giving a bond yield of around 75%. This has been attributed to the bowing of the FE-I4 die during the reflow process when bump bonding. Similar bond yields were found with single chip modules [3].

#### 3.1. Bump-bonding for thinned module assembly

The difficulties of low bump-bonding yield when manufacturing modules using thinned readout wafers are well known. Thinned devices have been made by IZM for the ATLAS IBL project using a support wafer and laser release method [5], but this process is not optimal for the large production required for the outer barrel and forward disk modules. An alternative method to address the issue of the bowing of the FE-I4 during solder based bump bonding is being investigated with Cea-Leti.<sup>3</sup> After deposition of a TiCu UBM and Cu micro-pillars with SAC solder bumps, the FE-I4 wafer will be thinned and a compensating layer will be deposited on the rear of the chip. This thin layer compensates for the bowing of the chip due to the mismatch in the coefficient of thermal expansion between the elements of the CMOS circuitry: metal, oxide and passivation layers, and the bulk silicon when undergoing high temperature processing such as solder based bump bonding. In addition to

<sup>&</sup>lt;sup>1</sup> Micron Semiconductor Ltd., www.micronsemiconductor.co.uk.

$<sup>^{2}\,</sup>$  VTT Technical Research Centre of Finland, http://www.vtt.fi.

<sup>&</sup>lt;sup>3</sup> Cea-Leti, http://www.leti.fr.

Fig. 2. Layout of pixel mask and device showing five quad sensors (left) and wafer manufactured by Micron Semiconductor Ltd (right).

**Fig. 3.** Current–voltage curves of quad and single chip sensors measured on a wafer at room temperature.

Fig. 4. Quad module with flex hybrid glued on the rear of the sensor.

addressing the issue of chip bowing during production, this will also make modules more robust against thermal shocks in the experiment. As a first step in evaluating this process a set of single chip sensors, manufactured by Micron Semiconductor Ltd [4], had UBM deposited and were then bump-bonded by Advacam<sup>4</sup> to full thickness FE-I4s that had been processed by Cea-Leti. The

Fig. 5. Noise map and distribution measured for FE-I4 readout chip mounted on quad sensor, with a bias voltage of 100 V.

preliminary studies of the bump-bond yield on three full thickness single chip modules was found to be > 99.9%. The next step of this programme is to evaluate the bow of thinned chips as a function of temperature to estimate the thickness of compensating layer required. A compensating layer can then be deposited on the rear of thinned FE-I4 chips, which can then be bump bonded to sensors and the bump yield evaluated.

The origin of the issue of bump-bonding thinned devices is the bowing during the high temperature solder reflow process. An alternative method using indium based connections is being investigated at the Science and Technologies Facilities Council (STFC) and has been used in the construction of the ATLAS and CMS pixel systems [6,7]. Indium bump bonding can be made using room temperature compression or thermo-compression. STFC has developed an indium process that has shown > 99.9% good electrical connections with a typical resistance per bump in the range  $0.20-0.31~\Omega$  on daisy chains with a bond density of 2125 bumps/cm². The daisy chains underwent thermal cycling to test their mechanical and electrical robustness. After 500 120 s cycles of -50~°C to +50~°C no defects were introduced over more than 10,000 bumps. Mechanical tests have shown

<sup>&</sup>lt;sup>4</sup> Advacam, http:/www.advacam.com.

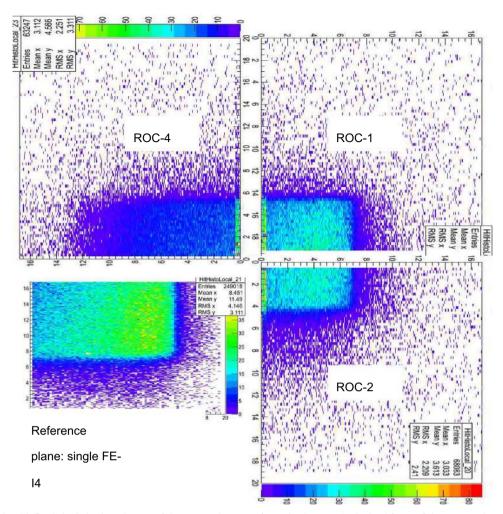

Fig. 6. Quad module with flex hybrid glued on the rear of the sensor. The axes refer to the distances in the local frame of the FE-14 readout chip (ROC), in mm.

shear strengths of 9 mN/bump have been achieved, corresponding to  $\sim\!250$  N across the FE-I4.

### 4. Quad module characterisation in testbeam

A full thickness quad module, bump bonded at VTT was taken to the ACONITE testbeam at DESY [8] as part of the ATLAS PPS programme [9]. Three of the four FE-I4 readout chips were operational and were readout using the USBPix system. The data from the three FE-I4s have been reconstructed separately as single chip devices using the testbeam reconstruction software package. Software to reconstruct 4 FE-I4s in a quad as a single object together with the tracks reconstructed in the telescope is under development. The reconstructed hit maps in the reference frame of each readout chip are shown in Fig. 6. The hits are reconstructed over an area of approximately  $20~\text{mm} \times 10~\text{mm}$  corresponding to the full area of the trigger scintillator, indicating that there are no issues with disconnected bumps that have been observed in the quad modules with thinned sensors and readout chips.

#### 5. Summary

Quad sensors compatible with 4 FE-I4 readout chips with designs including slim edges and structures to bridge the gaps between the FE-I4 chips have been manufactured with high yield. Characterisation

of a single FE-I4 in a quad module has shown that it behaves in a similar way to a single chip module in terms of noise and threshold. Thinned modules show low bump yield and this is being addressed by investigating other assembly methods: the use of a compensating layer to reduce the bow of the FE-I4 chip during solder based bump bonding and investigating room temperature bump bonding using indium.

### Acknowledgements

This work is supported by the Science and Technology Facilities Council (U.K.) (ST/J001/205/1).

#### References

- ATLAS Collaboration, Phase-II Upgrade, Letter of Intent, 2012, URL (cds.cern.ch/record/1502664).

- [2] M. Garcia-Sciveres, et al., Nuclear Instruments and Methods in Physics Research Section A 636 (2009) S155.

- [3] R.L. Bates, et al., Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 731 (0) (2013) 219, http://dx.doi.org/10.1016/j.nima.2013.04.043, URL (http://www.sciencedirect.com/science/article/pii/S0168900213004646).

- [4] H. Hayward, et al., Development of pixel sensors with 25 × 500 μm<sup>2</sup> pitch for the ATLAS HL-LHC upgrade, Nuclear Instruments and Methods in Physics Research Section A 765 (2014) 114.

- [5] ATLAS Collaboration, Prototype ATLAS IBL Modules Using the FE-I4A Front-End Readout Chip, Journal of Instrumentation 7, P11010. 2012, http://dx.doi.org/10. 1088/1748-0221/7/11/P11010.

- [6] C. Merioni, et al., Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 572 (1) (2007) 92, http://dx.doi.org/10.1016/j.nima.2006.10.351, URL \http://www.sciencedirect.com/science/article/pii/S0168900206020080).

- [7] C. Broennimann, et al., Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 565 (1) (2006) 303, http://dx.doi.org/10.1016/j.nima.2006.05.011, URL <a href="http://www.sciencedirect.com/science/article/pii/S0168900206007741">http://www.sciencedirect.com/science/article/pii/S0168900206007741</a>).

- [8] I. Rubinskiy, Physics Procedia 37 (0) (2012) 923, http://dx.doi.org/10.1016/j. phpro.2012.02.434, URL (http://www.sciencedirect.com/science/article/pii/ \$1875389212017889).

- [9] J. Weingarten, et al., Planar pixel sensors for the ATLAS upgrade: beam tests results, Journal of Instrumentation 7, P10028. 2012, http://dx.doi.org/10.1088/ 1748-0221/7/10/P10028.