# **Device Scaling Limits of Si MOSFETs and Their Application Dependencies**

DAVID J. FRANK, MEMBER, IEEE, ROBERT H. DENNARD, FELLOW, IEEE, EDWARD NOWAK, MEMBER, IEEE, PAUL M. SOLOMON, FELLOW, IEEE, YUAN TAUR, FELLOW, IEEE, AND HON-SUM PHILIP WONG, FELLOW, IEEE

Invited Paper

This paper presents the current state of understanding of the factors that limit the continued scaling of Si complementary metaloxide-semiconductor (CMOS) technology and provides an analysis of the ways in which application-related considerations enter into the determination of these limits. The physical origins of these limits are primarily in the tunneling currents, which leak through the various barriers in a MOS field-effect transistor (MOSFET) when it becomes very small, and in the thermally generated subthreshold currents. The dependence of these leakages on MOSFET geometry and structure is discussed along with design criteria for minimizing short-channel effects and other issues related to scaling. Scaling limits due to these leakage currents arise from application constraints related to power consumption and circuit functionality. We describe how these constraints work out for some of the most important application classes: dynamic random access memory (DRAM), static random access memory (SRAM), low-power portable devices, and moderate and high-performance CMOS logic. As a summary, we provide a table of our estimates of the scaling limits for various applications and device types. The end result is that there is no single end point for scaling, but that instead there are many end points, each optimally adapted to its particular applications.

**Keywords**—CMOS, device design, discrete dopants, double-gate MOSFET, DRAM, high-k dielectrics, high-performance logic, leakage currents, limits, low power, MOSFET, nanotechnology, power density, scale length, scaling, SRAM, tunneling.

#### I. INTRODUCTION

In 1930, Lilienfeld [1] patented the basic concept of the field effect transistor (FET). Thirty years later, in 1960, it was finally reduced to practice in Si–SiO<sub>2</sub> by Kahng and Attala [2]. Since that time, it has been incorporated into integrated circuits and has grown to be the most important device in the electronics industry. Progress in the field for at least the

Manuscript received March 30, 2000; revised September 26, 2000. The authors are with the IBM Thomas J. Watson Research Center, Yorktown Heights, NY 10598 USA (e-mail: djf@us.ibm.com; pwong@watson.ibm.com).

Publisher Item Identifier S 0018-9219(01)02066-7.

last 25 years has followed an exponential behavior that has come to be known as Moore's Law [3]. Since 1994, the semiconductor industry has been projecting these exponentials into the future to provide technology development targets. The most recent of these projections is the 1999 International Technology Roadmap for Semiconductors (ITRS99) [4]. It contains projections for complementary metal-oxide-sesmiconductor (CMOS) technology out to 2014, including 32-Gb dynamic random access memory (DRAM) entering production and processors with gate lengths down to 20 nm and  $2\times10^{10}$  FETs per chip.

But will these exponential projections come to pass or will physical limits make them impossible? Many reviews have been written about the current state and future prospects for Si MOS field-effect transistors (MOSFETs) and CMOSs [5]–[9]. In particular, many different scaling limits for MOSFETs have been proposed and discussed. In this work, we describe the current state of understanding of these scaling limits and seek to advance this state of understanding by addressing the ways in which application requirements must be intertwined with the setting of limits. The result in the end is that there will be no single "end to scaling," but rather, a wide range of limiting FET technologies, each optimally adapted to its applications.

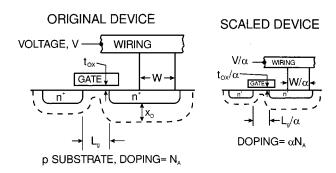

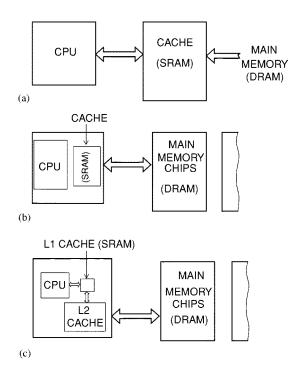

Much of our discussion centers on bulk-like MOSFET scaling, as illustrated in Fig. 1, but this is not intended to exclude other device geometries for MOSFETs. In particular, partially depleted silicon-on-insulator (PD-SOI) MOSFETs are considered to be part of this bulk-like category, since most of the same limits apply to PD-SOIs as to bulk. Consequently, PD-SOI is not explicitly discussed except when there are significant device design differences. At the circuit level, there are, of course, some important features of SOIs, such as the floating body effects, but these are for the most part outside the scope of this paper. The scaling behavior of fully depleted silicon-on-insulator (FD-SOI) MOSFETs depends a great deal on the

0018-9219/01\$10.00 © 2001 IEEE

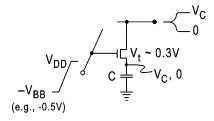

thickness of the buried oxide. For thick buried oxide, there is no backside screening of the drain potential, resulting in relatively poor scaling characteristics compared to other device types [10]–[13]. Since such devices are not likely to be used at the limits of scaling they are not discussed here. We do, however, discuss the scaling advantages of the more novel double gated type of FD-SOI MOSFETs, wherein both the insulator on the back side of the Si channel layer and the Si layer itself are very thin so that both sides of the channel are gated. There are also in-between FD-SOI MOSFETs with buried oxide thin enough to offer some screening, but not thin enough for use in active switching. These devices are interesting from a circuit point of view since the back gate can be used to dynamically adjust the threshold voltage, but are not discussed here for lack of space.

The outline of the paper is as follows. Section II addresses some of the more fundamental limitations to the continued scaling of MOSFETs that appear to be on the horizon. Based only on these fundamental limits, it may be possible to scale FETs down to very small dimensions, e.g., 10-nm channel length or smaller. Section III describes research results related to this fundamental limit regime: very tiny one-of-a-kind FETs. In the more practical world of manufacturing, however, there are many types of variations and fluctuations that require the design of MOSFETs with tolerances. In Section IV, we look at some of these practical limitations and their consequences for device design. Section V describes how the concepts of the previous sections play out when they are applied to meeting the needs of specific classes of applications. The paper ends in Section VI by summarizing all of the limits into a large table, followed by the conclusion in Section VII.

## II. FUNDAMENTAL SCALING LIMITS

#### A. Scaling Theory

For many years now, the shrinking of MOSFETs has been governed by the ideas of scaling [14], [15]. The basic idea is illustrated in Fig. 1: a large FET is scaled down by a factor  $\alpha$  to produce a smaller FET with similar behavior. When all of the voltages and dimensions are reduced by the scaling factor  $\alpha$  and the doping and charge densities are increased by the same factor, the electric field configuration inside the FET remains the same as it was in the original device. This is called constant field scaling, which results in circuit speed increasing in proportion to the factor  $\alpha$  and circuit density increasing as  $\alpha^2$ . These scaling relations are shown in the second column of Table 1 along with the scaling behavior of some of the other important physical parameters.

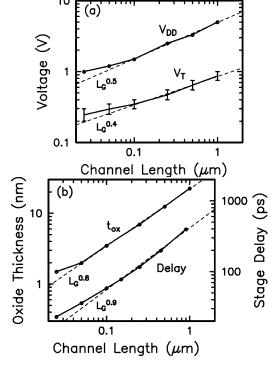

Fig. 2 illustrates the actual past and projected future scaling behavior of several of these parameters versus the channel length [16]. As can be seen, the voltages have not been scaled at the same rate as the length, in violation of the simple scaling rules outlined above. In earlier generations of MOSFETs, this occurred because carrier velocities were increasing with increasing field, yielding higher performance, while deleterious high-field effects were kept in check by the gradually descending voltage. More recently, carrier velocities have become saturated, but voltage scaling has

**Fig. 1.** Schematic illustration of the scaling of Si technology by a factor alpha. Adapted from [5].

**Table 1** Technology Scaling Rules for Three Cases

|                          | Constant-      | Generalized              | Generalized                       |  |  |

|--------------------------|----------------|--------------------------|-----------------------------------|--|--|

| Physical parameter       | Electric Field | Scaling                  | Selective                         |  |  |

|                          | Scaling Factor | Factor                   | Scaling Factor                    |  |  |

| Channel length, Insu-    | $1/\alpha$     | $1/\alpha$               | $1/\alpha_d$                      |  |  |

| lator thickness          |                |                          |                                   |  |  |

| Wiring width, channel    | $1/\alpha$     | $1/\alpha$               | $1/\alpha_w$                      |  |  |

| width                    |                |                          |                                   |  |  |

| Electric field in device | 1              | ε                        | ε                                 |  |  |

| Voltage                  | $1/\alpha$     | $\varepsilon/\alpha$     | $\varepsilon/lpha_d$              |  |  |

| On-current per device    | $1/\alpha$     | $\varepsilon/\alpha$     | $arepsilon/lpha_w$                |  |  |

| Doping                   | α              | $\varepsilon \alpha$     | $arepsilon lpha_d$                |  |  |

| Area                     | $1/\alpha^2$   | $1/lpha^2$               | $1/\alpha_w^2$                    |  |  |

| Capacitance              | $1/\alpha$     | $1/\alpha$               | $1/\alpha_w$                      |  |  |

| Gate delay               | $1/\alpha$     | $1/\alpha$               | $1/\alpha_d$                      |  |  |

| Power dissipation        | $1/\alpha^2$   | $\varepsilon^2/\alpha^2$ | $\varepsilon^2/\alpha_w\alpha_d$  |  |  |

| Power density            | 1              | $\varepsilon^2$          | $\varepsilon^2 \alpha_w/\alpha_d$ |  |  |

$\alpha$  is the dimensional scaling parameter,  $\varepsilon$  is the electric field scaling parameter, and  $\alpha_D$  and  $\alpha_W$  are separate dimensional scaling parameters for the selective scaling case.  $\alpha_D$  is applied to the device vertical dimensions and gate length, while  $\alpha_W$  applies to the device width and the wiring.

been slow because of the nonscaling of the subthreshold slope and the OFF current. To accommodate this trend, more generalized scaling rules have been created, in which the electric field is allowed to increase by a factor  $\varepsilon$  [17]. Furthermore, the device widths and wiring dimensions have not been scaled as fast as the channel lengths, leading to a further scaling parameter for those dimensions. These generalized rules are also shown in Table 1 and are described in more detail in [5], [9], and [18].

The preceding scaling rules do not tell a designer how short he can make a MOSFET for given doping profiles and layer thicknesses; they only describe how to shrink a known good design. Furthermore, since the built-in potentials are not usually scaled, the rules are inaccurate anyway. To find the minimum gate length at each generation of technology, one must analyze the two-dimensional (2-D) field effects inside the FET. This is often done numerically using complex 2-D simulation tools, but the recent analytic analysis by Frank *et al.* [19] reveals the primary dependencies. Other

**Fig. 2.** Past and projected future scaling trends for CMOS logic. (a) Supply voltage and threshold voltage versus channel length. (b) Gate oxide thickness and 2-in NAND delay versus channel length. Adapted from [16].

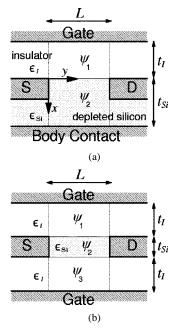

**Fig. 3.** Idealized schematic cross section diagrams of (a) a bulk MOSFET and (b) a DG-FET, defining the insulator thickness  $t_I$  and the depleted Si thickness  $t_{\rm Si}$ .  $\epsilon_{\rm Si}$  is the dielectric constant of silicon and  $\epsilon_I$  is the dielectric constant of the gate insulator(s). Adapted from [19].

analyses have been made in the past [10], [20], [21], but we prefer this approach because it allows us to treat the high-k dielectric case accurately.

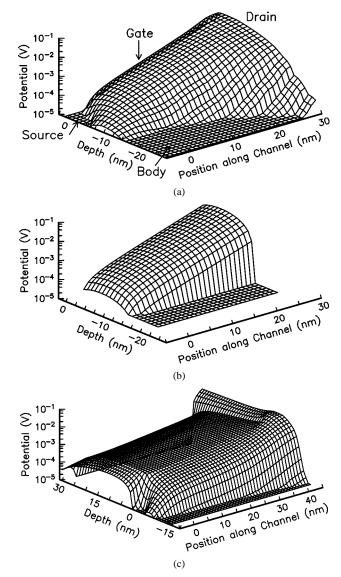

According to this theory, the details of which are summarized in the Appendix, the potential variations in the channel

**Fig. 4.** 2-D potential perturbations in nFETs caused by a 20-mV variation in the drain potential. (a) 2-D numeric simulation for realistic doping profiles. (b) Simple analytic theory using the same conditions as (a). (c) 2-D numeric simulation for a high-k gate insulator (k = 78, 30 nm thick) with extreme ground-plane-like doping profiles and shallow source and drain. From [33].

of an idealized MOSFET structure such as that in Fig. 3(a) can be expressed analytically using functions of the form  $\sinh(n\pi y/\Lambda_n)\sin(n\pi x/\Lambda_n)$ . The full dielectric boundary conditions can be satisfied by matching these functions at the interface, leading to an implicit equation for the scale length  $\Lambda_1$ , which characterizes the lowest order solution

$$0 = \epsilon_{Si} \tan(\pi t_I / \Lambda_1) + \epsilon_I \tan(\pi t_{Si} / \Lambda_1)$$

(1)

where the symbols are defined in Fig. 3. In the most common regime,  $\mathbf{t}_I/\Lambda_1\ll 1$  and (1) can be approximately solved as  $\Lambda_1\simeq\mathbf{t}_{\mathrm{Si}}+(\epsilon_{\mathrm{Si}}/\epsilon_I)\mathbf{t}_I-(\pi^2/3)(\epsilon_{\mathrm{Si}}/\epsilon_I)(\epsilon_{\mathrm{Si}}^2/\epsilon_I^2-1)(\mathbf{t}_I/\mathbf{t}_{\mathrm{Si}})^2\mathbf{t}_I$ . There is also an analogous scale length for the double-gate MOSFET (DG-FET), which is a three-layer structure with a gate and a thin gate insulator on both sides of the channel, as shown schematically in Fig. 3(b). Its equation is given in the Appendix. Fig. 4(a) and (b) shows

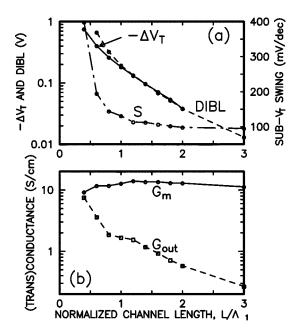

Fig. 5. Plots of (a)  $\Delta V_T$ , DIBL, and inverse subthreshold slope and (b) transconductance  $(G_m)$  and output conductance  $(G_{\rm out})$ , all versus the  $L/\Lambda_1$  ratio, showing the dependence of short channel effects on channel length. Based on 2-D FIELDAY simulations of idealized FET structures with  $\Lambda_1=13.6$  nm ( $t_{\rm ox}=1.5$  nm,  $t_{\rm Si}=10$  nm).  $\Delta V_T$  is determined at  $V_{\rm DS}=0.05$  V, DIBL is defined as  $V_T(V_{\rm DS}=0.05)-V_T(V_{\rm DS}=1.0)$ , the transconductance is measured at  $V_{\rm DS}=1.0$  V,  $V_{\rm G}=V_T(V_{\rm DS}=0.05)+0.5$  V and the output conductance is measured at the same  $V_{\rm G}$ , and  $V_{\rm DS}=0.75$  V

a comparison between the numerically calculated 2-D potential change in a conventional MOSFET due to a change in drain voltage and the first-order analytic approximation. Clearly, the simple approximation accurately captures the functional form of the potential variation along the channel, where it is most important. The only substantial difference is in the deep depletion under the drain, but this does not significantly influence the subthreshold behavior.

For this lowest order solution, the source-drain component of the potential in the center of the channel varies as  $(b_{21}+c_{21})\sinh(\pi L/2\Lambda_1)/\sinh(\pi L/\Lambda_1)$ , where  $b_{21}$  and  $c_{21}$ are bias dependent. Since this gives a length dependence of  $\sim \exp(-\pi L/2\Lambda_1)$ , the  $L/\Lambda_1$  ratio is a fundamental measure of the quality of the FET. For  $L/\Lambda_1 \gg 1$ , the FET will behave nearly ideally according to the one-dimensional (1-D) gradual channel approximation, but for small  $L/\Lambda_1$  there will be strong 2-D effects, including drain-induced barrier lowering (DIBL), high-output conductance, and V<sub>T</sub> rolloff. The dependence of these effects on  $L/\Lambda_1$  is shown in Fig. 5 for a particular case using 2-D numerical simulations of FETs with idealized doping profiles like those in Fig. 3(a). Evidently,  $L/\Lambda_1 \gtrsim 0.4$  is a fundamental limit on MOSFET aspect ratio for this idealized design since voltage gain, given by  $G_m/G_{\text{out}}$ , needs to be greater than one for CMOS logic

This scale length thus transforms the minimum gate length question into a question of maximum tolerable 2-D effects. From an idealized theoretical point of view, these effects can be large and  $L/\Lambda_1$  down to around one can be considered, as

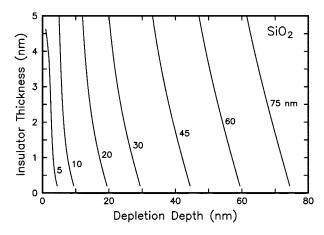

Fig. 6. Plot of constant  $\Lambda_1$  contours versus  $t_I$  and  $t_{Si}$  for  $\epsilon_{Si}/\epsilon_I = 3$ . From Frank *et al.* [19].

discussed in Section III. For current manufacturing tolerance ratios and circuit design techniques, however, it appears that the minimum practical worst case short FETs have  $L/\Lambda_1 \simeq$ 1.2 (for DIBL < 150 mV), so that the minimum practical nominal design point is around  $L_{\rm nom}/\Lambda_1 \simeq 1.5$ , allowing for  $\pm 20\%$  gate length variation. This is only possible because the V<sub>T</sub> rolloff in bulk MOSFETs is partially compensated by lateral doping nonuniformity (e.g., halo doping, see Section IV-A). For uniform lateral doping (e.g., an undoped DG-FET), it is probably necessary to have  $L_{\rm nom}/\Lambda_1 \simeq 1.7$ just to keep  $\Delta V_T$  below  $\sim 100$  mV, although the exact ratio probably depends on the desired  $V_T$ . The bulk limit can be seen, for example, in recent manufacturing technology [23] in which the minimum gate length (100 nm) FETs have DIBL of  $\sim$ 120 mV (at  $V_{DS} = 1$  V) and  $G_m/G_{out}$  of  $\sim$ 10, which correspond well to the  $L/\Lambda_1=1.2$  point in Fig. 5. High V<sub>DD</sub> threshold rolloff at this point would be unacceptably high, except that it is largely canceled out by careful halo doping.

As a specific example of this scale length, Fig. 6 shows the numerically evaluated dependence of  $\Lambda_1$  from (1) on  $t_I$  and  $t_{\rm Si}$  for the Si–SiO $_2$  system. The simple linear approximation  $\Lambda_1=t_{\rm Si}+(\epsilon_{\rm Si}/\epsilon_I)t_I$  corresponds well to the  $\Lambda_1=75$  nm case in Fig. 6, but note that the slope of the contours increases dramatically for shorter scale lengths, indicating a significant departure from this approximate solution. This increased slope is beneficial to highly scaled FETs since it implies that the penalty for using insufficiently scaled oxide thickness is less than might have been expected.

By their nature, none of these scaling rules contain in their formulation any limit on how far they can be applied. The limits enter due to physical phenomena that are not included in the scaling. The physical dimensions are limited by quantum mechanical tunneling currents that pass through the various barriers in the MOSFET when they are sufficiently thin, degrading the device's behavior. Voltage scaling is limited on several fronts. The built-in junction voltages are set by the 1.1-eV bandgap of Si which does not scale. Consequently, as the applied voltages are scaled down toward 1 V, the internal fields do not automatically scale as desired. A similar difficulty occurs in trying to scale

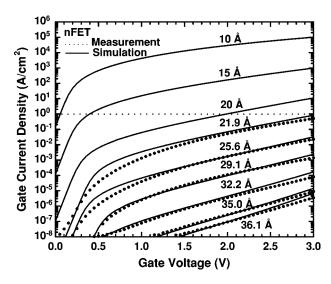

**Fig. 7.** Calculated (lines) and experimental (dots) results for tunnel currents from inversion layers through thin oxides. Adapted from Lo *et al.* [24].

the threshold voltage  $V_T$ , which is tied to the nonscaling behavior of the subthreshold slope and its influence on the OFF current. At very low values, the supply voltage is also fundamentally limited by the need for sufficient gain to provide logic functionality. These and other issues associated with scaling are examined in more detail below. Currently, the scaling of physical dimensions is also limited in a practical sense by the discreteness of dopants since present manufacturing techniques do not control the exact placement of dopant atoms. Consequently, since very small device volumes contain only a small number of dopants, large statistical variations become likely. Although single devices can be built, large functional circuits may be unmanufacturable by present techniques. This effect is discussed in Section IV-C.

## B. Tunneling Limits

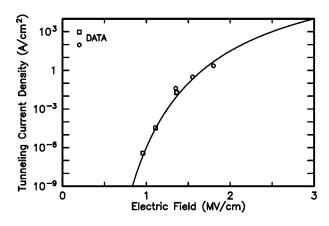

Tunneling current through the gate insulator is one of the most constraining limits to scaling. For SiO2, the conventional gate insulator, this leakage (see Fig. 7) exceeds the requirements of some applications (e.g., DRAM) already at 2.5–3 nm, even though high-performance logic technology is currently pushing 2-nm oxide thickness [23] to achieve the desired performance. According to Fig. 7 [24], 2-nm SiO<sub>2</sub> will have a leakage current of about 0.1 A/cm<sup>2</sup> at 1.2 V. For conventional designs this will only contribute a few milliwatts to the overall chip dissipation, which is only problematic for very low power applications, but is indicative of where things are headed. Several writers suggest that the upper limit of acceptable gate leakage is in the 1–10-A/cm<sup>2</sup> range [25]-[27] or even 100 A/cm<sup>2</sup> [28], although if one assumes more aggressively that up to 10% of the total power dissipation could be due to gate leakage (see Section V-A), then it may be possible to tolerate leakage  $\sim 1000 \text{ A/cm}^2$  in very high performance chips and even higher densities in small areas (unless reliability problems prevent it, see Section V-A). Either way, the minimum pure SiO2 gate insulator thickness for high-performance applications is in the 1.0–1.5-nm range, which should be reached in one or two generations. Lower power applications require thicker minimum oxide thickness and are already near their limits.

What can be done to circumvent this limit? There are at least three paths of attack, all of which may be useful. The first approach is to stop scaling the oxide, but attempt to continue scaling the rest of the FET in such a manner as to compensate for the thicker oxide. A related approach is to change the device structure in such a way that the MOSFET can be scaled further, even with the relatively thicker oxide. DG-FETs are an example of this approach. The third approach is to try to change the gate insulator to another material such that the effective capacitive thickness can be reduced without increasing the tunneling current.

The first approach has two aspects: 1) one can reduce the depletion depth (or the Si layer thickness for DG-FETs) as far as possible, to minimize  $\Lambda_1$  without further thinning of the oxide and 2) one can seek ways to reduce the minimum acceptable  $L/\Lambda_1$ , such as improving the halo doping. The depletion depth can be reduced by increasing the doping and/or by forward biasing the body-source junction, but this has two drawbacks: body leakage currents and a degraded ideality factor. The leakage currents are due to forward bodysource junction current and band-to-band tunneling between the body and drain, which is described below. The ideality factor  $\eta$  is the reciprocal of the rate of change of the channel surface potential as a function of  $V_G$  (in the subthreshold regime) and is approximately equal to  $1 + \epsilon_{Si} t_I / \epsilon_I t_{Si}$  for bulk MOSFETs. It enters into the subthreshold slope, thus impacting the OFF current. Applications that can be refrigerated may particularly benefit in this regime, since forward junction current and degraded subthreshold slope can both be ameliorated by running at low operating temperature.

As mentioned briefly in the preceding section, a laterally nonuniform doping distribution can at least partially compensate for the  $V_T$  rolloff that occurs for  $L/\Lambda_1 < 2$ . Of all the 2-D effects, V<sub>T</sub> rolloff has the worst effect on circuit margins, so this compensation is very important and enables worst case  $L/\Lambda_1$  to be reduced from  $\sim 1.5$  for no compensation to  $\sim$ 1.2 for current generation halo doping. Halo doping achieves this lateral nonuniformity by angling in shallow body-type doping from the source and drain ends of the FET with the gate as a mask creating a "halo" around the source and drain. For shorter FETs, these halo profiles work to create a higher average doping in the channel than is seen by a longer channel FET, thus tending to raise the  $V_{\rm T}$  in opposition to short-channel effects that are lowering it. Such halos are used to achieve the 25-nm bulk CMOS design described in Section IV-A. The other 2-D effects, however, are not compensated and for  $L/\Lambda_1$  much below 1.2, device performance becomes severely impacted anyway.

The second approach involves changing the device structure to one in which the gate essentially surrounds the channel. The most investigated form is the DG-FET in which there are a gate and a thin gate insulator on both sides of the channel, as shown schematically in Fig. 3(b). This geometry has been shown to have better scaling properties than the conventional bulk MOSFET [11], [12], [29] at least

for room temperature operation and is described in some detail in Section IV-B. The three-dimensional (3-D) version of these devices in which the channel is a thin post and the gate wraps around it cylindrically has the best electrostatic scaling properties of all and has been investigated by several groups [30], [31], but may prove to be impractical because of the high quantization energy levels for such a channel. (The lowest quantum energy level of the confined channel adds to the classical  $V_T$  of the MOSFET, creating an additional  $V_T$ control issue [6].) The primary advantages of these alternate device structures are a better ideality factor, near unity, and the possibility of thinner Si channels than would be possible in bulk devices except at very low temperature. It is not yet known to what extent V<sub>T</sub> rolloff can be compensated in these structures, although it seems that at least in principle, it may be possible to do so. For planar forms of the device, one could implant halo doping profiles into the channel although this would be subject to more fluctuations than for bulk devices because the volume available for such doping is smaller due to the thinness of the channel. Lateral variations in the gate workfunction might also be possible [32].

Finally, there is much work aimed at reducing the gate tunneling problem by changing to a higher permittivity (k) gate insulator. This is largely a materials problem since its success depends upon achieving high layer uniformity, integration with other Si processes, minimal/controlled reactions with Si and the gate electrode, and low fixed-charge, defect, and trap densities in the insulator and at the interface between the insulator and the Si substrate. Interface chemistry might also necessitate the use of metallic gate electrodes in which case metals must be found with workfunctions near those of nand p-poly-Si to achieve low  $V_{\mathrm{T}}s$ . If a suitable insulator can be found, it would be characterized by three thicknesses: its physical thickness t<sub>I</sub>, its equivalent oxide tunneling thickness t<sub>oxTeq</sub>, and its equivalent oxide capacitive thickness  $t_{oxCeq}$ . Although  $t_I$  would be larger than the (application dependent) minimum SiO<sub>2</sub> film thickness for most high-k dielectrics, the goal is to find an insulator with the property that when its  $t_{oxTeq}$  is equal to the minimum  $SiO_2$  thickness, its  $t_{oxCeq}$  is significantly less than the minimum  $SiO_2$  thickness. This would enable further scaling since when the gate insulator permittivity varies, at least initially, all of the other device dimensions and voltages can be scaled in keeping with  $t_{oxCeq}$  rather than the physical thickness  $t_I$  (since this maintains the scaling of charge density).

There are, however, some constraints on high-k insulators. The scale length theory of Section II-A shows that the physical thickness of the high-k insulator becomes important as k increases, increasing the scale length and the drain potential penetration under the gate [19], [33]. This is illustrated in Fig. 4(c), which shows the potential perturbation in the channel of a MOSFET with k=78 gate insulator and the same  $t_{\rm oxCeq}$  as in (a) and (b). Note that the potential falls much more slowly in (c) than in (a) and (b), even though the channel is longer in (c). A more detailed analysis of  $\Lambda_1$  from (1) shows that the physical insulator thickness should always be less than the Si depletion depth under the channel since otherwise the scale length will actually increase with

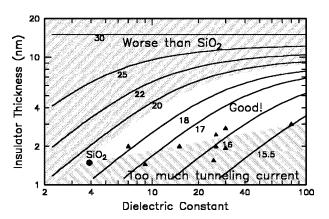

Fig. 8. Contours of constant scale length versus dielectric constant and insulator thickness, showing the useful design space for high-k gate dielectrics. Data points are rough estimates of the tunneling constraints for various high-k insulators. Depletion depth is 15 nm here. Useful design space will shrink with decreasing depletion depth. From [33].

increasing k [19]. This may be thought of as a case of "majority rule": when there is more insulator than Si, one approaches the situation in which  $\Lambda_1=\mathrm{t}_I+(\epsilon_I/\epsilon_{\mathrm{Si}})\mathrm{t}_{\mathrm{Si}},$  i.e., the Si gets converted to equivalent insulator thickness rather than the insulator being converted to equivalent Si.

The overall implications of the scale length considerations on high-k dielectrics are illustrated in Fig. 8, which indicates the regime in which these dielectrics can usefully contribute to further scaling of Si MOSFETs. The contours of constant  $\Lambda_1$  are equivalent to contours of minimum gate length since minimum gate length is proportional to  $\Lambda_1$ . Since it is undesirable to retreat from scaling and be forced to make larger FETs, the upper region that corresponds to larger minimum FETs than can be achieved with Si-SiO<sub>2</sub> is blocked out. The lower region is blocked out by the approximate tunneling leakage limits of high-k materials and reflects the empirical observation that insulator bandgaps tends to decrease with increasing k. Only the unhatched region is usefully available for high-k improvements to scaling. Based on the ratio between  $\Lambda_1$  for SiO<sub>2</sub> (19 nm) and the best accessible  $\Lambda_1$  at high k (15.5 nm), it appears that high-k materials can offer about one additional generation of gate length scaling at fixed tsi, but probably not more.

The gate insulator is not the only barrier through which tunneling currents may flow in very small MOSFETs. The body-to-drain junction can also experience tunneling currents if the field is high enough. Fig. 9 shows the field dependence of such band-to-band tunneling currents. Since the cross-sectional area of the highest field body-to-drain junction region is  $\sim 1/3$  that of the gate insulator, it may be possible to tolerate higher tunneling current density, perhaps up to 3000 A/cm<sup>2</sup> for aggressive high-end applications. According to Fig. 9, this puts the scaling limit for body-to-drain electric field at ~2.7 MV/cm, which corresponds to peak body doping around 3×10<sup>19</sup> cm<sup>-3</sup> for bulk MOSFETs, depending on bias and doping gradients, for a minimum depletion depth  $t_{\rm Si}$  of 8–13 nm. For low-power applications, the limit is likely to be below 1 A/cm<sup>2</sup> or 1.7 MV/cm and 0.8-1.2×10<sup>19</sup> cm<sup>-3</sup> body doping for a minimum t<sub>Si</sub> of

**Fig. 9.** Plot of band-to-band pn junction tunneling current versus electric field for 1 V reverse bias. Adapted from [27].

13–15 nm. In SOI MOSFETs with floating bodies, including DG-FETs, this tunneling current is potentially more problematic because, in addition to creating dissipation, it can charge up the floating body, lowering the effective threshold voltage. This body charging reaches steady state when the body voltage is low enough that the thermionic current into the source balances out the tunneling injection from the drain. Since the tunneling current depends strongly on the drain-to-source voltage, so does the body bias, which can create very high output conductance. For DG-FETs, the situation is not quite so bad: the rate at which carriers that have tunneled from the drain into the body can thermionically exit the body into the source is approximately the same as the rate at which carriers are thermally injected into the channel from the source. Therefore, as long as the drain-to-body tunneling current does not exceed the subthreshold channel current, the device should behave reasonably well. For more conventional SOI FETs, however, the barrier for carriers to leave the body can be much higher than the channel barrier and therefore very little drain-to-body tunneling can be tolerated before the  $V_{\mathrm{T}}$  is shifted significantly. The only apparent way around this floating body problem for FD-SOI is to lower the supply voltage so that there is no direct tunneling path available between drain and body. This imposes an approximate constraint on V<sub>DD</sub> for conventional FD-SOI of the form  $V_{DD} \leq E_G/e - V_T/\eta$ . For PD-SOI, there is also a second solution available: use a body contact.

It must be pointed out that these tunneling estimates could easily be too optimistic because the currents in Fig. 9 are for ideal band-to-band tunneling. Such tunneling can be greatly enhanced by deep traps in the junction, resulting in much higher junction leakage currents that would depend on the statistical distribution of deep traps in the junctions. This problem particularly impacts DRAM retention time distributions [34], [35].

For *very* small MOSFETs, direct subthreshold source-to-drain tunneling through the potential barrier below the gate is another possible source of leakage current. This effect has been reported in electrically variable shallow junction MOSFETs (EJ-MOSFETs) operating at 77 K with physical gate lengths of 8 nm [36] and is expected to become important

at room temperature for channel lengths around 10 nm (see Section III). It currently appears that scaling for most applications will stop due to minimum insulator thickness problems before this source-to-drain tunneling limit is reached.

One last tunneling-related constraint on scaling MOSFETs is tied to the need for FETs in most applications to provide greater than unity power gain, not to mention voltage gain. For sufficiently leaky gate insulators, the power required to drive the input leakage current could exceed the power available at the output especially if the output conductance is high. This would turn the FET into an attenuator rather than an amplifier and so represents perhaps the ultimate limit on thinning the gate insulator. For practical very large scale integration (VLSI) applications, however, power density problems are likely to limit scaling long before this limit is reached.

## C. Voltage Limits

The most conspicuous nonscaling voltage in the conventional Si MOSFET is the Si bandgap potential  $E_G/e = 1.1 \text{ V}$ (where e is the elementary charge), which can only be changed significantly by changing the semiconductor itself. This nonscaling behavior does not actually limit operating voltage, but it does complicate device design. In traditional circuit design, the body is tied to the source supply voltage and, consequently, as the supply voltage is scaled down into the 1-V range, the effect of the bandgap potential is increasing. The primary effect is to increase the junction fields and/or depletion depths in the FET above what they would be for ideal scaling. For the body-to-source and -drain junctions, the higher field necessitates higher junction doping, but the nonscaled  $E_G$  tends to suppress the band-to-band tunneling compared to what it would be if the bandgap were scaled. For the channel depletion region, the increasing field perpendicular to the oxide interface confines channel carriers closer to the interface, reduces their mobility, increases their quantum confinement energy, and increases gate depletion. Since these effects tend to increase the threshold voltage, they make it very hard to lower  $V_{\mathrm{T}}$ to the levels needed for high-performance applications. The first step in achieving a lower V<sub>T</sub> and channel surface field while still getting a scaled shallow depletion depth is to use retrograde doping profiles with low doping at the surface and high doping near the desired depletion depth [6]. If this does not lower  $V_{\mathrm{T}}$  sufficiently for some applications, one could consider very shallow counterdoping of the surface of the retrograde-doped channel to further lower the V<sub>T</sub> without significantly increasing the depletion depth. Alternately, most of these  $E_G$  scaling problems can be addressed by forward biasing the body relative to the source [37] in a manner which in effect scales  $E_G$ . The problems with forward biasing the body include the need to generate and distribute more supply voltages and the forward-biased diode current, which would add to dissipation. Since the latter problem might be solved by low-temperature operation, forward body bias may indeed be a viable solution for high-performance computing applications and is discussed more extensively in Section IV-A. Note that PD-SOI MOSFETs tend to acquire moderate forward body bias automatically in the process of equalizing the impact ionization and tunneling currents entering and leaving the body.

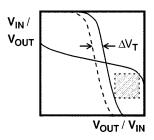

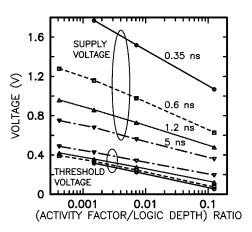

The biggest limit to scaling  $V_T$  is that the OFF current  $I_{\rm off}$ of the FET is constrained by application considerations and  $I_{\rm off} \cong I_{\rm VT}10^{-{\rm V_T/S}}$ , where S is the inverse subthreshold slope and  $I_{\rm VT}$  is the current at which  $V_{\rm T}$  is defined. Since  $S \simeq (\ln 10) \eta kT/e$ , where  $\eta$  is the ideality, k is Boltzmann's constant, and T is the temperature, the only way to scale  $V_T$  without also changing  $I_{off}$  is to scale T. For high-end applications, this is beginning to happen to some extent, but for many applications (e.g., cell phones), significant cooling is not an option. For these low-to-moderate power applications, the maximum dissipation-limited active-mode  $I_{\rm off}$  may range between  $10^{-7}$  and  $10^{-4}$  A/cm, resulting in minimum V<sub>T</sub>s varying between 0.54 and 0.27 V, respectively. These thresholds assume  $I_{\rm VT}=0.1$  A/cm and S = 90 mV/decade. Very high-performance circuits might tolerate thresholds near 100 mV (by this  $V_{\mathrm{T}}$  definition). Note that these are worst case thresholds at high V<sub>DD</sub>. Nominal threshold voltages must be set higher to allow for manufacturing tolerances. As noted before, double-gate structures generally have smaller inverse subthreshold slope, perhaps 70 mV/decade at room temperature, allowing the threshold and, hence, the supply voltage to be scaled further.

For very low-power applications, there is an interest in reducing the supply voltage as far as possible as a way of reducing the power by trading off performance [38]. From a fundamental point of view, in binary digital logic, the minimum permissible logic swing is the smallest swing that is still large enough to maintain two distinct logic states and it was shown long ago that this level is around  $4\eta kT$  [22]. This estimate can be refined by considering the self consistency required for a combinatorial logic gate. In this regime, each logic state is identified with a relatively small range of voltages, either high or low. Self consistency means that a combinatorial logic gate with any possible combination of inputs taken from the logic state ranges will always produce an output state that lies in one of the logic state ranges.

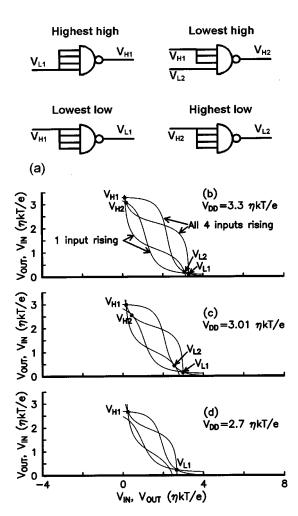

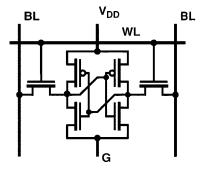

Conventional combinatorial logic circuits are built using series and/or parallel combinations of input devices, one (or two for CMOS) device(s) for each input. To find the fundamental limits, imagine circuits in which the usual sources of logic state degradation (noise) are absent: there are no voltage drops in the wiring, no capacitive coupling between wires, no process-induced parameter variations among the devices, no variations in the supply voltages, no extrinsic resistances, and no thermal noise. The nonlinearity of the active devices serves to compress the variety of input logic states into just two output states, but since the devices are not "infinitely nonlinear," a finite voltage range is required to achieve adequate compression. As an example, Fig. 10 illustrates this for a simple CMOS four-input NAND gate, where (a) shows the bias conditions which lead to the upper and lower logic state ranges. In Fig. 10(b), the logic swing is "large"; the "eye" diagram shows a small amount of noise margin between the earliest switching gate with only one input changing and the latest switching gate with all of its in-

Fig. 10. Illustration of minimum swing determination using ideal four-input CMOS NAND gates. (a) Set of schematics defining conditions for best- and worst case logic outputs. (b)–(d) Transfer characteristics in the form of "eye" diagrams. Output voltage versus input voltage and input voltage versus output voltage for the cases when only one input is switching and when all four inputs are switching. Inputs that are not switching are held at  $\rm V_{H1}$ . (b) Logic swing is above the minimum. Self-consistent low output states are between  $\rm V_{H1}$  and  $\rm V_{H2}$  and self-consistent high output states are between  $\rm V_{H1}$  and  $\rm V_{H2}$ . (c) Logic swing is exactly at minimum. (d) Logic swing is below the minimum; there are no fully self-consistent output logic states.

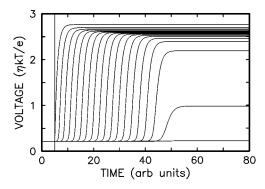

puts changing and the output state ranges are isolated and self consistent, even though the range of input states does create some spread. This logic swing is above the minimum limit. When the logic swing is reduced too far [see Fig. 10(d)], the earliest and latest curves no longer cross, indicating that there is no self-consistent solution for  $V_{L2}$  and  $V_{H2}$  (as defined in the figure). The lack of a self-consistent state means that operating a long chain of such logic gates can result in the loss of the logic signal (Fig. 11). Fig. 10(c) shows the minimum logic swing condition: the earliest and latest curves are exactly tangent at their intersection points (and the noise margin is reduced to zero).

Using this type of minimum logic swing condition, analogous curves can be found for other logic families and fan-ins and analytic calculations and simple circuit simulations can be carried out to determine the minimum logic swing or supply voltage; some results for MOSFETs are given in

Fig. 11. Output signal versus time for every second gate in a series chain of subthreshold CMOS four-input NAND gates when operated with logic swing of  $2.99\eta kT$ , which is below the minimum  $(3.01\eta kT)$ . Logic gates are configured in worst case fashion: low-going stages receive all four inputs from the previous stage, while high-going stages receive only one input from the previous stage, having the other inputs tied high. Note that for this case the logic signal is lost after 35 stages.

Table 2

Minimum Self-Consistent Supply Voltage for Fixed Fan-In Logic

Gates for Several Circuits and Conditions

|                            | Minimum Supply Voltage |      |      |                  |  |  |  |

|----------------------------|------------------------|------|------|------------------|--|--|--|

| Circuit family             | FI=2                   | FI=4 | FI=8 | Units            |  |  |  |

| CMOS NAND                  |                        |      |      |                  |  |  |  |

| well below $V_T$           | 2.27                   | 3.01 | 3.72 | $\eta { m kT/e}$ |  |  |  |

| CMOS NAND                  |                        |      |      |                  |  |  |  |

| $V_T = V_{DD}/4$ , T=300 K | 144.                   | 207. | 274. | mV               |  |  |  |

| Resistor Pull-up nFET      |                        |      |      |                  |  |  |  |

| NOR, well below $V_T$      | 4.22                   | 5.2  | 6.08 | $\eta { m kT/e}$ |  |  |  |

Minimum design points assume that the device sizes and/or bias voltages have been optimized to center the input/output curves. For random logic, the minimum logic swing would be determined by the average or typical fan-in rather than by the worst case, since high fan-in gates would be buffered by lower fan-in circuits.

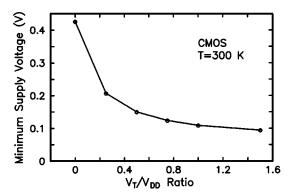

Table 2. These limits vary roughly as  $(\eta kT/e) \ln(FI)$  for conventional devices in their exponential regime, where FI is the fan-in. Note that the lowest voltage FET results are achieved by using the FETs in their subthreshold regime, where they present their maximum exponential nonlinearity. To achieve smaller minimum logic swing, one would need devices with stronger nonlinearities since the greater the nonlinearity, the smaller the voltage range required for logic state compression. Using MOSFETs in the conventional above-threshold manner decreases their overall nonlinearity and increases the required minimum supply voltage, as shown in Fig. 12, from 75 mV (FI = 4) for pure subthreshold CMOS to 207 mV for  $V_{\rm T} = V_{\rm DD}/4$ at 300 K. Adding more contact resistance may also increase the minimum supply voltage since it decreases overall nonlinearity[39]. Another consideration is that transient simulations show increased timing variability (dependence on input state) near the minimum logic swing limit because of the asymmetric switching.

Fig. 12. Minimum supply voltage versus  $V_{\rm T}$  as a fraction of  $V_{\rm DD}$  for four-input CMOS NAND gates. These calculations use a constant mobility Brews model [97] to simulate 1.0- $\mu m$  channel length surface channel FETs with thin oxide (4.5 nm) and realistic source–drain contact resistances. Threshold voltage here is defined by the extrapolation to zero of the source–drain conductance for very low drain voltages.

The introduction of realistic nonidealities such as noise, tolerances, and short-channel MOSFET behavior into the above analysis will create a statistical spread of scenarios requiring higher voltages to guarantee logic state consistency. On the other hand, from a theoretical but impractical point of view, one could buffer the output of every multiple input logic gate with a chain of inverters, effectively increasing the gain and decreasing the minimum required supply voltage somewhat, although the power consumed by the buffers seems likely to eliminate any real advantage from this approach.

# D. Resistance Issues

It is implicitly assumed in the scaling theories that the parasitic resistance in series with the intrinsic MOSFET is either negligible or scalable along with the channel resistance. Otherwise, the performance gains derived from scaling are quickly lost. For example, recent experimental work on 20-nm gate length MOSFETs reported current levels much below today's optimized 100-nm devices because of excessive series resistance [40].

In spite of this case, series resistance is not expected to impose a fundamental limit on CMOS scaling. Technological advances, e.g., self-aligned silicide for contact resistance reduction and rapid thermal annealing for abrupt source-drain formation, allow today's state-of-the-art high-performance bulk nMOSFETs to achieve a series resistance below 100  $\Omega$   $\mu$ m [23]. This is less than 10% of the effective device resistance  $(V_{DD}-V_{T})/I_{on} \simeq 1000~\Omega~\mu \text{m}.$ Ultimately, the intrinsic device resistance of an ideal ballistic MOSFET approaches  $(C_{ox}v_s)^{-1}$ , where  $C_{ox}$  is the effective gate capacitance per unit area including quantum effects and  $v_s$  is the thermal injection velocity at the source [41]. For a physical or equivalent tox of 1.0 nm, the limiting intrinsic device resistance is about 500  $\Omega$   $\mu$ m. Even without further reduction in series resistance below currently achieved values, no serious performance degradation is expected.

For bulk CMOSs, there is a tendency for the series resistance to increase as the junction depth is scaled down for

shorter channel devices. But this is unlikely to pose a fundamental problem as it can be dealt with by structural solutions such as raised source—drain using selective epi. Furthermore, it is shown in Section IV-A that for an optimized halo design, strict junction depth scaling is not required for short channel control. This can be understood from the principle of the scale length model in which the source—drain depth only enters the preexponential factor of the threshold voltage rolloff.

Particular attention is needed to avoid high series resistance in SOI and/or DG-FETs that use thin silicon films. Ideally, the source and drain regions should fan out to a much thicker film for reduction of both the electrical and the thermal resistance.

#### III. ULTIMATE MOSFETS

As indicated in the discussion about scale length and minimum channel length in Section II-A, the primary constraint on shrinking channel length is the coupling between 2-D short channel effects and tolerances. When 2-D effects become large at very short channel length, random variations in gate length, dopant positions, and other structural parameters cause very large changes in device characteristics. If one is only interested in a single FET or if one assumes that ways can eventually be found to reduce process variations to insignificance and to place dopants exactly, then tolerances are not an issue and one can design and build extremely short gate-length MOSFETs. These can be very useful for exploring the physics of small FETs even if they do not reflect manufacturable processes.

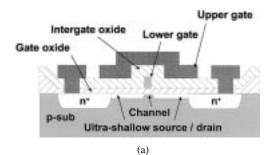

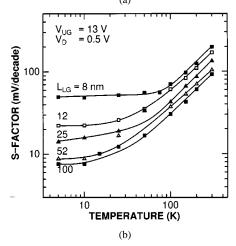

The smallest reported experimental FETs are 8-nm EJ-MOSFETs made by Kawaura et al. [36]. As shown in the cross-sectional diagram in Fig. 13(a), these electrically variable shallow junction nMOSFETs use a second gate over the top of the first gate to induce inversion layers in the source and drain regions. Such inversion layers are much shallower than the usual implanted source-drain extensions, which reduces to a minimum the influence of the drain on the channel of the FET. The lower gates were patterned by e-beam lithography and lateral etching to achieve a minimum physical gate length of 8 nm. This FET has substrate doping of  $2\times10^{18}$  cm<sup>-3</sup>, a depletion depth of 25–30 nm,  $t_{\rm ox}=5$  nm, and consequently  $\Lambda_1$  ~40 nm (see Fig. 6). If the effective channel length is of the same order as the gate length, this MOSFET has  $L/\Lambda_1 \sim 0.2$ , which is extremely small and seems unlikely since its V<sub>T</sub> shift, DIBL, and  $g_m/g_{\rm out}$  ratio are all consistent with  $L_{\rm eff}/\Lambda_1 \sim 0.5-0.6$ , judging by Fig. 5. By this analysis, it appears likely that this FET has an effective channel length of ~22 nm with the extra  $\sim$ 14 nm due to fringe screening of the upper gate field by the lower gate. Nevertheless, for transport measurements, this FET is very interesting. It appears to be so short that it shows evidence of direct tunneling between source and drain through the channel barrier. This is demonstrated by the inverse subthreshold slope measurements versus temperature shown in Fig. 13(b). The saturation of the inverse slope at low temperatures for the shortest FETs is consistent with the

**Fig. 13.** (a) Cross-sectional view of 8-nm channel length EJ-MOSFET. (b) Temperature dependence of the inverse subthreshold slope at various channel lengths. Reprinted from [39] by permission of H. Kawaura.

idea that the current in this regime is dominated by direct tunneling through the channel barrier since such tunneling is not very temperature dependent. Tunneling through the 22-nm effective channel length appears plausible for this device because the barriers are low,  $< \sim 50$  mV, and the effective mass of the lowest quantum level is quite low in the transport direction. Furthermore, the ideality factor of  $\sim 3$  for this FET increases the apparent tunneling inverse slope significantly above what it would be in a more ideal device.

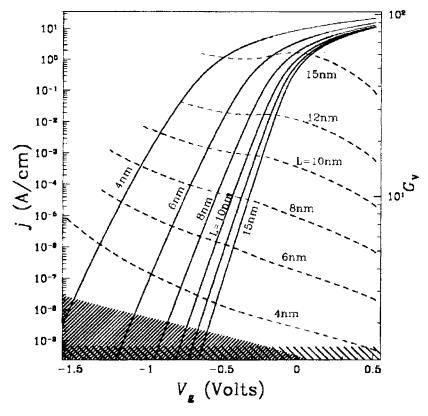

On the theoretical device design front, recent work by Pikus et al. [42], [43] has shown that it should be possible to scale DG-FETs [see Fig. 3(b)] down to 8-nm channel lengths for logic and DRAM. These simulations use a ballistic transport model to predict device IV characteristics such as those shown in Fig. 14 for a Si channel 1.5-nm thick with 2.5-nm SiO<sub>2</sub> gate insulators on both sides of the channel. These particular curves do not include source-to-drain tunneling, but their later work does, showing that the effect becomes important at ~8-nm channel length at 300 K. Using the three-layer generalization of the scale length theory [see (A5) in the Appendix], these FETs have  $\Lambda_1 = 9$  nm so to allow for reasonable gate length and  $\ensuremath{V_\mathrm{T}}$  tolerances in an FET without  $V_{\mathrm{T}}$  rolloff compensation the minimum channel length should be  $\sim$ 13 nm. However, if the design criteria for use in logic is only that there be sufficient gain, then these simulations show that such MOSFETs could be useful for logic down to about 8 nm or  $L/\Lambda_1 = 0.9$ . For DRAM, the most important thing is ON-OFF ratio and the simulations suggest that a sufficient ON-OFF ratio can also

Fig. 14. Drain current and voltage gain  $G_{\rm V}={\rm dV/dV_G}$  (at constant current) versus gate voltage for very short channel DG-FETs. Reprinted from [42] by permission of K. Likharev and the American Institute of Physics, © 1997.

be obtained for channel length down to 8 nm, at which point source-to-drain tunneling becomes significant.

Finally, consider the ultimate limit for conventional bulk-like MOSFETs. According to Section II-B, the thinnest possible depletion depth for bulk FETs at maximum body doping is about 8 nm. Coupling this with a 1.2-nm very leaky gate insulator and 0.7-nm gate poly-Si depletion gives a scale length of  $\sim$ 11 nm, which ought to make it possible to consider FETs with channel length of order 10 nm, in keeping with the preceding examples. Unfortunately, it will be very difficult to get the desired low-threshold voltages with this design because quantum confinement effects will raise  $V_T$  at least 200–250 mV at such high fields [6]. If a high-k gate insulator is not available, it will be even more difficult because the resulting high-ideality factor  $\eta \simeq$ 1.5 will cause a high  $V_T$  due to the built-in field and will necessitate a high  $V_T$  due to the low-subthreshold slope.

It appears possible to approach this regime, however, by cooling the CMOS chip to low temperatures and forward biasing the body. While low-temperature operation by itself does not help 2-D effects, some of the improvements in subthreshold slope can be traded off for a narrower gate depletion width to attain better control of short-channel effects. A forward body bias in this case is helpful in several ways. First, a forward body bias reduces the built-in potential and adjusts  $V_{\rm T}$  to lower values, both directly and by decreasing the field and the quantum confinement energy. If the body is

forward biased by 0.5 V, the depletion depths can probably be reduced to  $\sim 5$  nm, making it possible to achieve a 10–12-nm channel length. Second, a forward body bias lowers the reverse bias and therefore the field across the drain-to-body junction, hence suppressing the band-to-band tunneling current. Meanwhile, the leakage current of the source junction, although forward biased by the applied body voltage, is insignificant at low temperature as long as the body bias does not exceed  $\sim 0.5$  V.

The steeper subthreshold slope at low temperature allows  $V_T$  and, therefore,  $V_{DD}$  to scale further below their room-temperature limits given in Fig. 2(a). With the threshold voltage scaled to 0.1 V or so for 100-K operation, we estimate that it is possible to extend CMOS to  $\sim\!\!11\text{-nm}$  channel length with a 1.2-nm  $t_{ox}$  and 0.5 V  $V_{DD}$ . 2-D drift-diffusion simulations show inverse subthreshold slope of 40 mV/decade even for 1.5 nm  $t_{ox}$  at 100 K and 10-nm channel length, so achieving a low  $V_T$  with low OFF current appears quite feasible, but these simulations do not include source-to-drain tunneling current. Separate estimates indicate that this tunneling current will start to dominate the thermal OFF current somewhere in the 10–12-nm regime, thus creating the  $\sim\!\!11\text{-nm}$  channel length limit.

These design points by their definitions do not include any tolerances and, thus, serve as reference points for what may be possible if process variations could be completely controlled.

## IV. PRACTICAL LIMITS ON MOSFETS

As shown in the previous section, the ultimate theoretical limit on the size of a MOSFET is very small indeed. Unfortunately, the commercial use of FET technology is constrained by a variety of factors that (at least presently) preclude reaching the ultimate limit, except in one-of-a-kind devices. Perhaps the most important of these factors is the manufacturing reality of tolerances. These tolerances arise both from processing variations and from circuit conditions.

On the processing side, there are lithographic variations due both to exposure conditions and to photoresist variations. At the finest level, the molecules of the photoresist are discrete and may cause a certain level of fundamental coarseness. From a device point of view, the most important consequence of these lithographic variations is a random variation in the gate length. This variation occurs both from device to device within a chip, due to exposure nonuniformities, proximity effects, stochastic effects, etc., and as an average variation from wafer to wafer and chip to chip, due to imperfect control of processing conditions. All other aspects of manufacturing are subject to control tolerances, too, including layer growth or deposition thicknesses, etch depths and profiles, ion implantation conditions, and annealing conditions. None of the current manufacturing processes controls the exact atomic position of each dopant atom and this uncertainty by itself can lead to substantial  $V_T$  variations in very small FETs, as described Section IV-D.

There are also circuit related tolerances due to the capacitive coupling between signal lines. Since a computer has a very large set of possible states, there is a statistical distribution of noise coupled onto each signal line. For very low supply voltages, the logic state variations described in Section II-C are another source of such noise.

Both of the above forms of uncertainty must be accounted for in designing optimized devices and circuits. Several studies have been done at the circuit level characterizing the effects of these tolerance on  $V_{\rm T}$  and  $V_{\rm DD}$ . The basic result is that optimized threshold and supply voltages must be raised somewhat to accommodate these effects compared to what they would be for perfectly controlled FETs with nominal characteristics [44]–[47]. Section IV-A and Section IV-B describe practical attempts to address the scaling limits of MOSFETs in the context of tolerances, Section IV-C addresses one of the sources of variations, namely discrete dopant effects, and Section IV-D briefly discusses power dissipation.

#### A. Bulk CMOS

Bulk CMOS has been the mainstream VLSI technology for the past two decades. Below 100-nm linewidth, however, CMOS design options are severely constrained by the fundamental issues of oxide tunneling and voltage nonscaling discussed in Section II. To explore in more detail the limit of bulk (and PD-SOI) CMOS scaling, we present a feasible design for 25-nm (channel length) bulk CMOS without complete scaling of oxide thickness and power supply voltage [27]. Such channel lengths can be achieved at a lithography

generation of 75-nm resolution in year 2008 according to the ITRS roadmap [4]. Key issues such as gate work function, channel and source—drain doping requirements, poly-Si depletion effect, and nonequilibrium carrier transport in 25-nm CMOS are addressed. As discussed in Section VI, it may be possible to scale a little further than this, but only at extremely high power.

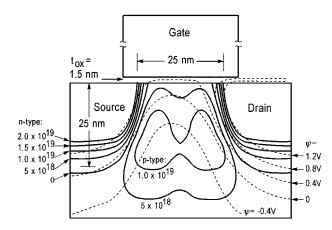

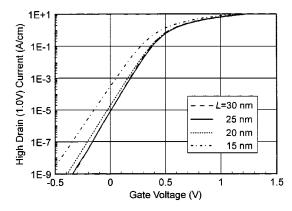

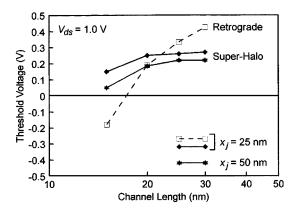

While straightforward 2-D scaling calls for a gate oxide around 1 nm for 25-nm MOSFETs [see Fig. 2(b)], direct tunneling leakage in oxide/nitrite gate insulators is very high for such thin insulators as already discussed, so we take  $t_{\rm oxCeq} = 1.5$  nm, which is near the limit described in Section II-B. To maintain reasonable OFF currents on the order of 100 nA/ $\mu$ m for an integration level of  $10^8$ – $10^9$ devices per chip, the room-temperature threshold voltage is kept at a minimum of about 0.2 V under the worst case conditions. The power supply voltage is set at 1.0 V, which represents a reasonable tradeoff among active power, device performance, and high field effects. With the nonscaled gate oxide and supply voltage, an optimized vertically and laterally nonuniform doping profile called the superhalo [16] is needed for controlling short-channel effects. Fig. 15 shows such a doping profile along with simulated potential contours for a 25-nm MOSFET. In principle, such a profile can be realized by ion implantation self-aligned to the gate edges with very restricted amount of diffusion. The highly nonuniform profile sets up a higher effective doping concentration toward shorter devices, which counteracts short-channel effects. This results in OFF currents insensitive to channel length variations and allows CMOS scaling to the shortest channel length possible. In the 25-nm CMOS design shown in Fig. 16,  $I_{\text{off}}$  is nearly independent of channel length variations between 20 and 30 nm. The superior short-channel effect obtained with the superhalo is shown in Fig. 17 compared with a nonhalo retrograde profile. Because of the nearly flat V<sub>T</sub> dependence on channel length, superhalo allows a nominal device to operate at a lower threshold voltage, thereby gaining significant performance benefit: 30%-40% over nonhalo devices for 25-nm CMOS at 1.0 V [27]. It should be pointed out that DIBL, which is still present in superhalo devices, has only a minor effect on the delay performance for a given high-drain  $V_T$ .

The above 25-nm device design does not require stringent scaling of junction depth. Fig. 17 shows that the  $V_T$  rolloff is rather insensitive to the vertical junction depth with only a slight change when the junction depth is doubled from 25 to 50 nm for the same halo profile. This allows the junction depth to decouple from the channel length, thus avoiding the high-resistance problem with very shallow extensions. The lateral source-drain gradient, however, is much more critical. As CMOS channel length is scaled down, the lateral doping profile of source and drain junctions should also sharpen in step and be kept abrupt on the scale of a fraction of the channel length. Otherwise, short-channel effects degrade rapidly [27]. This is because channel length is largely determined by the points of current injection from the surface layer (inversion or accumulation) into the bulk, which takes place at a source-drain doping concentration

**Fig. 15.** Source, drain, and superhalo doping contours in a 25-nm nMOSFET design. The channel length is defined by the points where the source–drain doping concentration falls to  $2\times10^{19}$  cm<sup>-3</sup>. Dashed lines show the potential contours for zero gate voltage and a drain bias of 1.0 V.  $\psi=0$  refers to the midgap energy level of the substrate. From [27].

**Fig. 16.** Subthreshold currents for channel lengths from 30 to 15 nm.  $I_{\rm off}=10^{-5}$  A/cm (1 nA/ $\mu$ m) for 20, 25, and 30 nm devices. From [27].

of about  $2\times10^{19}~{\rm cm^{-3}}$  [48]. Any source–drain doping that extends beyond this point into the channel tends to compensate or counterdope the channel region and aggravate the short-channel effect. The abruptness requirements of both the source–drain and the halo doping profiles dictate absolutely minimum thermal cycles after the implants. Note that a raised source–drain structure may help making contacts, but does not by itself satisfy the abruptness requirement discussed here.

As discussed in Section II-B, a key issue with the high p-type doping level and narrow depletion regions in this 25-nm design is the band-to-band tunneling through the high-field region between the p-halo and the drain. For the peak field intensity (1.75 MV/cm) at high drain and zero gate biases shown in Fig. 15, the tunneling current density is on the order of 1 A/cm<sup>2</sup> (Fig. 9). This should not constitute a major component of the device leakage current given the narrow width of the high-field region,  $\sim$ 15 nm according to Fig. 15.

The threshold design in Fig. 17 assumes dual n<sup>+</sup>/p<sup>+</sup> Si work function gates for nMOS/pMOS, respectively. A midgap work function metal gate would clearly result in

**Fig. 17.** Short-channel threshold rolloff for superhalo and retrograde (nonhalo) doping profiles. Threshold voltage is defined as the gate voltage where  $I_{ds}=1~\mu\text{A}/\mu\text{m}$ . From [27].

threshold voltage magnitudes far too high for both devices [48]. With doped poly-Si gates, a frequently raised issue is the effect of poly-Si depletion on CMOS performance. Depletion effects occur in polysilicon in the form of a thin-space charge layer near the gate oxide interface, which acts to reduce the gate capacitance and inversion charge density for a given gate drive. The percentage of gate capacitance attenuation becomes more significant as the oxide thickness is scaled down. Actually, the net performance loss due to poly-Si depletion effects is much less severe than is suggested by C–V measurements. As it happens, the delay of intrinsic, unloaded circuits is only slightly degraded  $(\sim 5\%)$  because although poly-Si depletion causes a loss in the drive current, it also decreases the charge needed for the next stage. These two effects tend to cancel each other. For the heavily loaded case in which the devices drive a large fixed capacitance, the delay degradation approaches those of the ON currents ( $\sim$ 15%). This can be compensated to some extent by using wider devices. On the average, the performance loss due to poly-Si depletion effect is about 10% for partially loaded 25-nm CMOS circuits with a 1.5-nm-thick oxide [27].

Extensive 3-D statistical simulations have been carried out on the effects of dopant fluctuations on threshold voltage for the above 25-nm device design [49]. Some of the details are presented in Section IV-C.

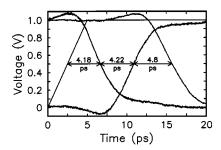

To evaluate the potential ON-state performance of 25-nm CMOS, detailed Monte Carlo simulations were performed using the simulator DAMOCLES [50]. Both n- and p-channel MOSFETs have been simulated, yielding low-output conductance high-performance I-V characteristics for both device types [27]. The transconductance exceeds 1500 mS/mm for this nFET, with an estimated  $f_{\rm T}$  higher than 250 GHz. Transient Monte Carlo simulations were also done for a three-stage chain of 25-nm CMOS inverters. Fig. 18 shows the output waveforms. The estimated delay time is 4–4.5 ps, about three to four times faster than 100-nm CMOS operated at 1.5 V.

One way to go beyond 25-nm bulk CMOS is to cool the CMOS chip to low temperatures as discussed in connection to the 11-nm bulk MOSFET described in Section III. This is

**Fig. 18.** Monte Carlo simulation of 25 nm CMOS inverter delay. pFET is twice the width of nFET. There is a third stage loading the output of the second stage.

feasible at least for high-end systems and offers the advantages of higher carrier mobilities and a steeper subthreshold slope that allows  $V_T$  and, therefore,  $V_{DD}$  to scale further below their room-temperature limits given in Fig. 2(a). To gain the most performance out of low-temperature CMOS, therefore, the threshold voltage should be tuned to lower values while maintaining the same OFF current as the temperature decreases [16]. If the 11-nm MOSFET can be realized as a worst case design point, then it should be possible to establish a nominal design point for low-temperature ( $\sim\!100\,\mathrm{K})$  bulk CMOS at around 15-nm channel length. Of particular interest is the case when the p-type substrate (body to nFET) is biased at  $V_{DD}=0.5\,\mathrm{V}$  and the n-well (body to pFET) is biased at ground potential. No extra power supply or on-chip voltage generator is needed.

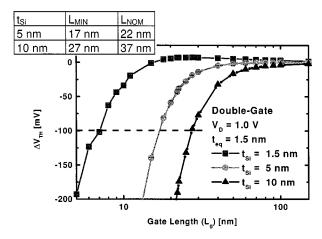

## B. Limits for DG-FET

The merits of the DG-FET have been analyzed by many researchers [11], [12], [29], [51]. There is a consensus that the electrostatic design of such FETs, with the gate completely surrounding the channel, is quite ideal and offers the potential to scale somewhat further than bulk devices [9]. Fig. 19 shows that DG-FET can be scaled to a channel length of about 20 nm [12] using 5-nm-thick Si and 1.5-nm gate oxide. This assessment is critically dependent on the assumptions that: 1) the silicon channel thickness can be controlled to within a reasonable tolerance; 2) the transport properties of DG-FETs are similar to those of single-gated bulk FETs despite the thin channel; and 3) the fabrication of DG-FETs does not impose additional constraints as compared to bulk FETs. This section addresses the three aforementioned assumptions.

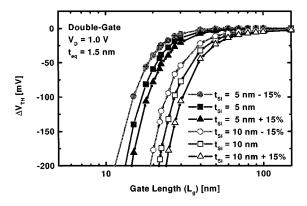

Silicon channel thickness variations lead to threshold voltage variations from several sources: 1) short-channel effects due to the electrostatics of the device geometry; 2) quantization induced threshold voltage dependence on the silicon channel thickness; 3) threshold voltage dependence on the channel doping; and 4) random fluctuation of dopant number and dopant placement in a doped channel. Fig. 20 illustrates the threshold voltage variation due to short-channel effects, comparing the threshold voltage rolloff curves for channel thickness  $\pm 15\%$  from the nominal thickness. Analytically, by differentiating the Suzuki scale length [19], [52], the effect of channel thickness variation can be

**Fig. 19.** Threshold voltage rolloff for DG-FET with equivalent gate oxide thickness ( $t_{\rm eq}$ ) of 1.5 nm and silicon channel thickness  $t_{\rm Si}$  of 1.5, 5, and 10 nm. 1.5-nm thickness is not practical and is included here only as a reference. DIBL is taken into consideration by plotting the threshold voltage rolloff at a drain voltage  $V_{\rm D}$  equal to the power supply voltage.

**Fig. 20.** Threshold voltage roll-off for DG-FET with equivalent gate oxide thickness ( $t_{\rm cq}$ ) of 1.5 nm. Silicon channel thickness ( $t_{\rm Si}$ ) is 5 nm and 10 nm with  $\pm$  15% variation.

converted to an equivalent variation in the channel length for a constant  $L/\Lambda_1$  ratio [29]

$$\frac{\Delta L}{L} = \frac{2\epsilon_{\rm Si}t_{\rm ox} + \epsilon_{\rm ox}t_{\rm Si}}{4\epsilon_{\rm Si}t_{\rm ox} + \epsilon_{\rm ox}t_{\rm Si}} \cdot \frac{\Delta t_{\rm Si}}{t_{\rm Si}}.$$

(2)

In this way, the short-channel consequences of thickness variation can be accounted for as a part of the overall gate length variation budget. For high-k dielectrics, a more general formula can be found in the Appendix.

The quantization induced threshold voltage variation can be estimated from the particle-in-a-box approximation for the lowest subband [11], [12], [53], giving  $\Delta V_T = -(h^2/4qm^*t_{\rm Si}^2)(\Delta t_{\rm Si}/t_{\rm Si})$ . Since this uncertainty grows rapidly with decreasing  $t_{\rm Si}$ , it appears impractical to use a channel thickness very much below 5 nm [11], [12]. Consequently, although the  $t_{\rm Si}=1.5$  nm case in Fig. 19 appears to offer very promising channel lengths down to  $\sim\!\!7$  nm, it cannot currently be considered practical because it would have unacceptably large threshold variations. In the case where channel doping is employed to adjust the threshold voltage, the variation of

threshold voltage (for n-channel FET) with silicon channel thickness is  $\Delta V_T = q N_A t_{\rm Si} t_{\rm ox}/2\epsilon_{\rm ox}$  for accepters and  $\Delta V_T = (q N_D t_{\rm Si}/2)((t_{\rm ox}/\epsilon_{\rm ox}) + (t_{\rm Si}/4\epsilon_{\rm Si}))$  for donors. For thin channels, thin insulators and reasonable doping, it will be difficult to adjust the  $V_T$  by more than  $\pm 100$  mV. Random dopant fluctuation accounts for about 20–50 mV (one sigma) [49], [54] for practical doping levels employed to set the threshold voltages. Taking the above four factors into account, the tolerance for a  $\geq 5$ -nm silicon channel thickness needs to be about 10%.

This silicon channel thickness tolerance requirement is quite stringent (about 0.5 nm for a 5-nm channel) considering the present state of the art for thickness control in SOI materials. Thickness tolerance of SOI wafers are typically  $\pm 2-5$  nm over an 8-in wafer. Bonded wafers typically have better tolerances than SIMOX wafers, both in terms of global thickness uniformity and local thickness variations (roughness). Over a smaller area (5-in diameter), bonded wafers show variations of  $\pm 1$  nm. This suggests that it may be possible to control the thickness to the required tolerances as technology for making bonded wafers progresses.

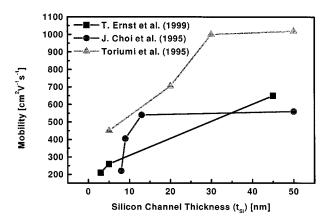

There have been few reports and predictions on the transport properties of short-channel DG-FETs [11], mostly due to the difficulty of modeling the physics precisely including the full 2-D quantum solution in the channel [55], [56] and the effects of dynamic switching [57]. There have been theoretical speculations on degradation of phonon-limited electron mobility in ultrathin silicon channels [58]–[60] due to the electronic structures of the confined thin silicon channel. Experimental verification of such degradation has not been made. Little has been said about carrier mobility at high normal fields where the FET operates.

Generally, the experimental data show mobility decreasing rapidly below 10 nm (see Fig. 21). However, most experiments on mobility for thin silicon channels reported in the literature contain too many uncertainties to be conclusive. Toriumi *et al.* [61] attributed the mobility reduction to Coulomb scattering from the interface traps at the back interface of the thin SOI. Choi *et al.* [62] ascribed the mobility reduction to silicon film stress for the thin silicon channel. Ernst *et al.* [63] showed mobility reduction, but did not offer any possible explanations. In all these experiments, the silicon channel was thinned by oxidation from a SIMOX wafer. This procedure introduces uncertainty due to the quality of the back interface. The source—drain series resistance tended to be high, which introduced more uncertainty to the measurements.

The fabrication of the ideal DG-FET is extremely difficult [54]. The "ideal" DG-FET should have [64]: 1) a uniform silicon channel, thin compared to the channel length, with  $t_{\rm Si} \leq 0.4L$  (see Section VI); 2) a thick source–drain fan-out structure to reduce the series resistance; and 3) top and bottom gates that are perfectly aligned to each other and to the source–drain dopings and fan-out in order to reduce overlap capacitance and series resistance of the ungated region. It may also require metal gates with specifically chosen workfunctions in order to obtain the desired threshold voltages since doping can only shift the  $V_{\rm T}$  by  $\sim 100$  mV and it would be preferable not to require any

**Fig. 21.** Experimentally measured electron mobilities in thin silicon channels drop substantially below about 10-nm channel thickness. Lines are visual guides and do not suggest trends in the data. Mobility data of Choi *et al.* [62] and Toriumi *et al.* [61] are the peak mobility at low effective fields. Electric field corresponding to the mobility data of the Ernst *et al.* [63] was not specified in their paper and is presumed to be the low field mobility.

doping at all to avoid discrete dopant effects. Conventional layer-by-layer-type fabrication techniques, which have served the microelectronics industry well for the past 25 years, are difficult to apply to the DG-FET structure that is somewhat 3-D. Various methods have been attempted, including selective epitaxial growth through a tunnel [64], forming a vertical silicon channel with side gates [65], [66], and wafer bonding with the channel and gates in place followed by selective epitaxial growth of the source—drain fan-out [67]. While these experiments generally show high series resistance and lower ON-current than expected, further innovations and perfection in the fabrication techniques should improve device characteristics in the future.

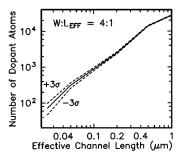

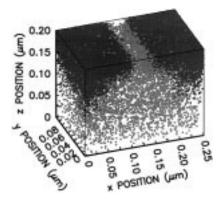

## C. Doping Fluctuations

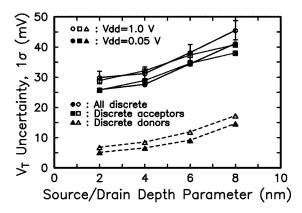

As was already mentioned, one of the potentially significant sources of variation in MOSFETs at the limits of scaling is randomness in the exact location of dopant atoms. Although the average concentration of doping is quite well controlled by ion implantation and annealing processes, these processes lead to randomness at the atomic scale in the form of spatial fluctuations in the local doping concentration, which in turn cause device-to-device variation in MOSFET threshold voltages. These fluctuations were anticipated long ago [68], but at the time most FETs had sufficiently many dopants that it was not a genuine problem. Since then, however, the number of dopants in the depletion region of an FET has been decreasing steadily with scaling, as illustrated in Fig. 22. The decrease has been roughly in proportion to  $L_G^{1.5}$  due to the incomplete scaling of the electric fields, so that we are now into a regime in which the smallest FETs have fewer than 1000 dopants determining the threshold voltage. Since fluctuations in dopant number have a standard deviation equal to the square root of the number of dopants, in keeping with Poisson statistics, the  $\pm 3\sigma$  bounds shown in Fig. 22 become extremely large by the time channel lengths reach 25 nm.

**Fig. 22.** Number of doping atoms in the depletion layer of a MOSFET versus channel length [49].