Received September 10, 2019, accepted September 25, 2019, date of publication October 2, 2019, date of current version October 11, 2019. *Digital Object Identifier* 10.1109/ACCESS.2019.2945065

# Digital Implementation of Fractional Order PID-Type Controller for Boost DC-DC Converter

# SANG-WHA SEO<sup>1</sup> AND HAN HO CHOI<sup>D2</sup>

<sup>1</sup>Propulsion System Research Team, Korea Railroad Research Institute, Uiwang-si 16105, South Korea

<sup>2</sup>Division of Electronics and Electrical Engineering, Dongguk University, Seoul 04620, South Korea

Corresponding author: Han Ho Choi (hhchoi@dongguk.edu)

This work was supported in part by the Basic Science Research Program through the National Research Foundation of Korea, Ministry of Education, under Grant 2017R1D1A1B03030652, and in part by the Railroad Technology Research Program through the Ministry of Land, Infrastructure and Transport of Korean Government under Grant 19RTRP-B146008-02.

**ABSTRACT** In this paper, the problem of designing a fractional order PID-type controller is considered for a boost converter. By using the output capacitance and input inductance values this paper characterizes integer order PID-type control gains which will make the closed-loop system transfer function approximately equal to a first order system with a unit DC gain and prescribed time constant  $\tau$ . Next, a procedure to compute the design parameters of a fractional order PID-type controller is given together with a descritized control algorithm for DSP implementation. By using a floating-point DSP, the proposed control algorithm is implemented in real time. Finally, experimental results are given to show the practical feasibility and effectiveness of the proposed fractional order PID-type control system under several operating conditions. The results illuminate that the proposed controller can be better than a conventional integer order PID-type controller.

**INDEX TERMS** Boost converter, PID control, fractional order system, DSP, DC-DC converter.

# I. INTRODUCTION

DC-DC converters have been popular in many industrial applications, including power supplies and power drives. DC-DC converters have several different operation modes. And they are represented by nonlinear continuous-time dynamical equations which can exhibit nonlinear phenomena such as chaos, bifurcation, periodic behavior, and multiple equilibrium points or so [2], [4], [5], [7]. The input value is confined in the set {0, 1} or it is assumed that the input is within the interval [0, 1] and the state representing the inductor current should be equal to or larger than zero. Due to these nonlinearity and constraints on the input or state variables, it is difficult to design a high performance DC-DC converter control system. DC-DC converters are usually subject to parameter or load uncertainties that can significantly degrade control system performances. In order to solve these problems, various advanced DC-DC converter control design methods have been proposed in the literature. In [1], [10],

The associate editor coordinating the review of this manuscript and approving it for publication was Zhong  $Wu^{\textcircled{D}}$ .

[12], [19]–[21], [25], [28], [42], [45], [46], [48], the model predictive control approach has been applied for converters. In a model predictive control method, an optimal control input is constructed through optimizing a user-defined cost function which is usually selected as a weighted sum of the input and state variables. A model predictive control method can make a trade-off among several control performance criteria by setting the cost function as a weighted sum of the control performance criteria with appropriately chosen weighting factors. And, the model predictive control methods can easily consider the constraints on the input or state variables in the design procedure. The nonlinear control methods [14], [17], [30], [31], [34], [36] have also been developed under nonlinearity and constraints on the input or state variables. The sliding mode approach has been applied for robust DC-DC converter controller design problems in [29], [35], [37], [39], [47]. It should be noted that the sliding mode approach has been very effective to attack the robust feedback control design and analysis problem for uncertain nonlinear systems where the uncertainties can be lumped into unknown but bounded functions. The sliding mode control methods

can improve the robustness against nonlinear uncertainties. The sliding mode control methods yield good performances such as fast transient response, insensitiveness to external disturbances, and invariance to internal parameter variations. On the other hand, several authors [3], [11], [16], [27], [32] have proposed intelligent control methods based on the fuzzy control theory which has been successfully applied for nonlinear system modeling and control. In [3], a Takagi-Sugeno fuzzy model for a boost converter has been derived and a global stabilizing fuzzy controller for the fuzzy model has been designed. The authors of [16] have proposed a fuzzy controller for a buck converter and they have shown that the fuzzy controller can be better than a proportional-integralderivative (PID) controller via some experimental comparison. In [27] a PI-like fuzzy controller design method has been proposed. The authors of [32] have improved the PI-like fuzzy controller design procedure based on a conventional PI controller tuning method. The previous advanced DC-DC converter control design methods yield not only good transient responses but satisfactory steady-state performances. However, the PID-type control methods are widely adopted to control the DC-DC converters because they are simple, practical, effective, and easily tuned [14], [16], [23], [24], [32], [49].

On the other hand, the fractional order control system approach has been widely used to improve control system performances. And various fractional order PID-type control system analysis and design methods have been developed in the literature [6], [8], [9], [18], [22], [26], [33], [40], [41], [43], [44]. Motivated by the fact that a fractional order PID controller can outperform conventional integer order PID controllers, this paper considers the problem of designing a fractional order PID-type controller for a boost converter. Firstly, this paper characterizes integer order PID-type control gains which will make the closed-loop system transfer function approximately equal to a first order system with a unit DC gain and prescribed time constant  $\tau$ . These gains are used for the PID gains of the fractional order PID-type controller. A systematic procedure to tune the fractional orders of the fractional order PID-type controller is given together with a descritized control algorithm for DSP implementation. The descritized control algorithm is implemented on a Texas Instruments TMS320F28335 DSP in order to verify the feasibility and practicality of the proposed method. Finally, experimental results are presented to verify that the proposed algorithm can be effectively applied to realtime control of a boost converter in response to load or input voltage variations. The fractional order control system design problem for converters has also been considered in [6], [8], [18]. However, only [6] has considered a boost converter and none of the previous results of [6], [8], [18] has given an explicit formula of PID gains.

In Section 2, a continuous-time boost converter dynamic equation is given and the design problem is formulated. Section 3 gives a parameterization of a class of integer order PID-type controllers enabling the closed-loop system transfer

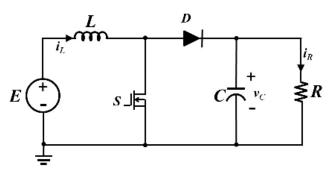

FIGURE 1. Topology of boost DC-DC converter.

function approximately equal to a first order system with a unit DC gain and prescribed time constant  $\tau$ . Section 3 also presents a procedure to determine the design parameters of fractional order PID-type controllers, together with a descritized algorithm for DSP implementation. Section 4 compares the experimental results performed under different operating conditions. Finally, Section 5 gives some concluding remarks.

# II. MODEL DESCRIPTION AND PROBLEM FORMULATION

A boost DC-DC converter of Figure 1 can be represented by the following nonlinear continuous-time dynamic equation [3], [14], [35], [36]:

$$\dot{i}_L = -\frac{1}{L}v_C\zeta + \frac{1}{L}v_Cu + \frac{E}{L}\zeta$$

$$\dot{v}_C = \frac{1}{C}i_L\zeta - \frac{1}{RC}v_C - \frac{1}{C}i_Lu$$

(1)

where  $i_L$ ,  $i_R$ ,  $v_C$ , u are the input inductor current, the output capacitor voltage, the output load resistor current, the discrete-valued control input confined in the set {0, 1}, and E, R, L, C represent the external source voltage value, the output load resistance, the inductance of the input circuit, the capacitance of the output filter, respectively. S and D of Figure 1 are an active controllable switch and a diode. The symbol  $\zeta$  means the auxiliary binary variable defined by

$$\zeta = \begin{cases} 1, & If \ u = 1, \ or \ u = 0 \ and \ i_L > 0 \\ 0, & If \ u = 0 \ and \ i_L = 0 \end{cases}$$

(2)

It should be noted that the converter operates in continuous conduction mode in case of  $\zeta = 1$  whereas the converter is in discontinuous conduction mode when  $\zeta = 0$ . This paper will use the following assumptions:

- A1:  $i_L$  and  $v_C$  are available.

- A2: The inductor current can never be zero, i.e. the converter is in continuous conduction mode.

As [14], [34]–[36], we assume that the control input u is generated via a PWM device controlled by the duty ratio input function  $d(\cdot)$  ranging on the interval [0, 1]. Then under A2 we can obtain the following approximate averaged model

$$\dot{i}_{L} = \frac{1}{L}v_{C}(d-1) + \frac{E}{L} \\ \dot{v}_{C} = -\frac{1}{C}i_{L}(d-1) - \frac{1}{RC}v_{C}$$

The previous results of [14], [36] imply that for given desired reference output voltage  $V_r$  satisfying  $V_r \ge E > 0$  the equilibrium points for the current  $i_L$  and the input d are uniquely determined as  $V_r^2/RE$  and  $1 - E/V_r$ , respectively. Along the similar line of [14], we introduce the following error terms

$$x_{1} = \frac{V_{r}^{2}}{RE} - i_{L}, \quad x_{2} = V_{r} - v_{C},$$

$$x_{3} = \int_{0}^{t} (V_{r} - v_{C}) ds, \quad v = d + \frac{E}{V_{r}} - 1$$

(3)

then

$$\dot{x}_1 = -\dot{i}_L = -\frac{1}{L}(V_r - x_2)\left(v - \frac{E}{V_r}\right) - \frac{E}{L}$$

$$\dot{x}_2 = -\dot{v}_C = \frac{1}{C}\left(\frac{V_r^2}{RE} - x_1\right)\left(v - \frac{E}{V_r}\right) + \frac{1}{RC}(V_r - x_2)$$

$$\dot{x}_3 = x_2$$

After all, the following approximate averaged state space error model can be obtained

$$\dot{x} = Ax + Bv + \Delta Bv \tag{4}$$

where  $x = [x_1, x_2, x_3]^T$  and

$$A = \begin{bmatrix} 0 & -\frac{E}{LV_r} & 0\\ \frac{E}{CV_r} & -\frac{1}{RC} & 0\\ 0 & 1 & 0 \end{bmatrix},$$

$$B = \begin{bmatrix} -\frac{V_r}{L}\\ \frac{V_r^2}{RCE}\\ 0 \end{bmatrix}, \quad \Delta B = \begin{bmatrix} \frac{x_2}{L}\\ -\frac{x_1}{C}\\ 0 \end{bmatrix}$$

(5)

The nonlinear model (4) can be linearized at the operating point x = 0 as follows:

$$\dot{x} = Ax + Bv \tag{6}$$

Since the Lyapunov's linearization method implies that the original nonlinear system is stable if the linearized system is stable [38], the previous converter control methods such as [14], [16], [23], [24], [32], [49] have used PID-type controllers similar to the following integer order control law which stabilizes the linearized boost DC-DC converter model (6)

$$v = -K_1 x_1 - K_P e - K_I \int_0^t e d\theta - K_D \dot{e}$$

(7)

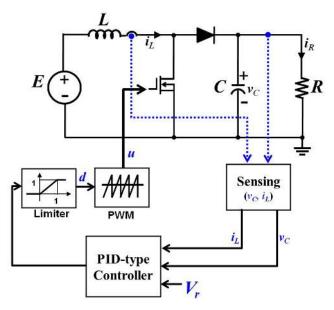

where  $K_1$ ,  $K_P$ ,  $K_I$ , and  $K_D$  are the gains, and e is the output error, i.e.  $e = v_C - V_r = y = x_2$ . It should be noted that if  $x_2$  is noisy then the control performance can be significantly degraded due to the derivative term  $K_D \dot{x}_2$ . Figure 2 shows a block diagram of a PID-type controller for a boost converter. The control law (7) can be rewritten as

$$v = -K_1 x_1 - K_P x_2 - K_I x_3 - K_D \dot{x}_2 \tag{8}$$

FIGURE 2. Block diagram of PID-type controller for boost DC-DC converter.

On the other hand, motivated by the fact that a fractional order PID controller can outperform conventional integer order PID controllers, this paper will consider the following fractional order PID-type control law

$$v = -K_1 x_1 - K_P x_2 - K_I D^{\mu} x_3 - K_D D^{\lambda} x_2 \tag{9}$$

where  $0 \le \mu \le 1$  and  $0 \le \lambda \le 1$ . The term D represents the continuous differential operator and thus  $D^{\mu}$  means  $d^{\mu}/dt^{\mu}$ . It should be noted that the integer order PID-type controller (7) corresponds to the special case of the proposed fractional order PID-type control law with  $\mu = 0$  and  $\lambda = 1$ . The proposed fractional order controller gives more flexibility to adjust the dynamic performances of the closed-loop control system.

After all, our design problem can be formulated as determining the design parameters  $\lambda$ ,  $\mu$ ,  $K_1$ ,  $K_P$ ,  $K_I$ , and  $K_D$ .

#### **III. MAIN RESULTS**

# A. CHARACTERIZATION OF INTEGER ORDER PID-TYPE CONTROL LAW

Consider the PID-type control law (7) with the following gains:

$$K_{1} = k_{1}, \quad K_{P} = \frac{LE + k_{1}RCEV_{r}}{\tau RE^{2} + LV_{r}^{2}},$$

$$K_{I} = \frac{RE^{3} + 2k_{1}EV_{r}^{3}}{\tau RE^{2}V_{r}^{2} + LV_{r}^{4}}, \quad K_{D} = \frac{RLCE}{\tau RE^{2} + LV_{r}^{2}} \quad (10)$$

where  $k_1 > 0$  and  $\tau > 0$ . In order to derive the closed-loop transfer function,  $G_{cl}(s)$ , where *s* is the Laplace variable, let's decompose the PID-type control law (7) as

$$v = v_1 + v_2,$$

$v_1 = -K_1 x_1, v_2 = -K_P y - K_I \int_0^t y d\theta - K_D \dot{y}$  (11)

VOLUME 7, 2019

then we can obtain the following equations

$$v_1 = -k_1 x_1 = -k_1 [1, 0, 0]x,$$

$$\dot{x} = (A - k_1 B[1, 0, 0])x + Bv_2,$$

$$v = x_2 = [0, 1, 0]x$$

and thus we can obtain

$$sX(s) - x(0) = (A - k_1 B[1, 0, 0])X(s) + BV_2(s),$$

$Y(s) = [0, 1, 0]X(s)$

where *A* and *B* are defined in (5), and X(s),  $V_2(s)$ , and Y(s) are the Laplace transforms of *x*,  $v_2$ , and *y*, respectively. After all, we can obtain the transfer function from  $v_2$  to *y*,  $G_1(s)$ , as follows:

$$G_1(s) = [0, 1, 0](sI - A + k_1B[1, 0, 0])^{-1}B$$

=  $\frac{N_G(s)}{D_G(s)}$  (12)

The terms  $N_G(s)$  and  $D_G(s)$  are given by

$$N_{G}(s) = RE^{2}V_{r}^{2} - LV_{r}^{4}s,$$

$$D_{G}(s) = RLCEV_{r}^{2}s^{2} + (LEV_{r}^{2} + k_{1}RCEV_{r}^{3})s$$

$$+RE^{2} + 2k_{1}EV_{r}^{3}$$

(13)

The equation (11) implies that  $V_2(s) = H(s)(Y_r(s) - Y(s))$ where  $Y_r(s)$  is the Laplace transforms of the reference input of  $G_{cl}(s)$ , and

$$H(s) = K_P + \frac{K_I}{s} + K_D s = \frac{N_H(s)}{D_H(s)}$$

(14)

where  $N_H(s)$  and  $D_H(s)$  are defined by

$$N_{H}(s) = RLCEV_{r}^{2}s^{2} + (LEV_{r}^{2} + k_{1}RCEV_{r}^{3})s +RE^{2} + 2k_{1}EV_{r}^{3}, D_{H}(s) = (\tau RE^{2}V_{r}^{2} + LV_{r}^{4})s$$

(15)

It should be noted that  $N_H(s) = D_G(s)$  leading to  $G_1(s)H(s) = N_G(s)/D_H(s)$ . By using (12), (14), and the following equation

$$Y(s) = G_1(s)V_2(s) = G_1(s)H(s)[Y_r(s) - Y(s)] = \frac{N_G(s)}{D_H(s)}[Y_r(s) - Y(s)]$$

(16)

we can show that  $D_H(s)Y(s) = N_G(s)Y_r(s) - N_G(s)Y(s)$ leading to  $[N_G(s) + D_H(s)]Y(s) = N_G(s)Y_r(s)$ . After all, we can obtain  $G_{cl}(s)$  as

$$G_{cl}(s) = \frac{Y(s)}{Y_r(s)} = \frac{N_G(s)}{N_G(s) + D_H(s)}$$

=  $\frac{RE^2 V_r^2 - LV_r^4 s}{RE^2 V_r^2 + \tau RE^2 V_r^2 s} = \frac{1 - \omega_c^{-1} s}{1 + \tau s}$  (17)

where  $\omega_c = LV_r^2/RE^2$ . It should be noted that usually  $0 < L \ll 1 \ll R$  leading to

$$1 \ll \omega_c = \frac{RE^2}{LV_r^2} \tag{18}$$

Therefore, if we set the desired time constant  $\tau$  as

$$\tau > \frac{1}{\omega_c} = \frac{LV_r^2}{RE^2} \tag{19}$$

then by the rules to draw a Bode plot straight-line approximation [15] the closed-loop transfer function  $G_{cl}(s)$  of (17) can be approximated within the frequency range  $\omega \in [0 \ \omega_c)$ as the following first order system with a unit DC gain and prescribed time constant  $\tau$ :

$$G_{cl}(s) \approx \frac{1}{\tau s + 1} \tag{20}$$

After all, the following theorem can be obtained:

*Theorem 1:* Consider the linearized boost DC-DC converter model (6) and the PID controller (8) with the gains (10). Then the closed-loop system dynamics is given by the stable first order system (17). Additionally, if the desired time constant  $\tau$  satisfies (19) then the closed-loop system dynamics can be approximated by the first order system with a unit DC gain and prescribed time constant  $\tau$ , (20), within the frequency range  $\omega \in [0 \omega_c)$ .

#### **B. FRACTIONAL ORDER PID-TYPE CONTROL LAW**

Now, consider the fractional PID-type control law (9) with the gains of (10). It should be noted that fractional order control systems have been widely introduced to improve control system performances. Various fractional order PID-type control system analysis and synthesis methods have been developed in the literature and it has been shown that a fractional order PID controller can outperform conventional integer order PID controllers [6], [8], [9], [18], [22], [26], [33], [40], [41], [43], [44]. In the proposed control law (9), the term  $K_D D^{\lambda} x_2 =$  $K_D D^{\lambda} e$  can be rewritten as  $K_D D^{\lambda-1} \dot{e}$  where  $-1 \leq \lambda - 1 \leq 0$ . The derivative term  $K_D \dot{e}$  of the conventional integer order control law (7) is replaced with the  $(\lambda - 1)$ th integration term  $K_D D^{\lambda-1} \dot{e}$  in the proposed control law. This implies that the proposed control law can reduce performance degradation due to the high frequency noise magnified by the derivative term  $K_D \dot{e}$ .

In order to practically implement a fractional order controller, we should obtain a finite dimensional approximation of the fractional order integral and differential operators. Several methods have been proposed to obtain finite dimensional approximations in frequency domain and in the time domain. In obtaining a practical approximation, we must consider the computation time and the amount of the required memory. Thus the approximation should have a minimal set of parameters [9], [40], [41], [43], [44]. In the recent papers [41], [43], [44], various approximation methods have been extensively compared via mathematical analysis and simulations. The previous works implies that if  $\mu > 1$  the approximation methods can yield unsatisfactory characteristics but if  $-1 \le \mu \le 1$  the following first order approximation gives desirable characteristics

$$D^{\mu} = \left(\frac{2}{T_s}\right)^{\mu} \frac{1 - \mu z^{-1}}{1 + \mu z^{-1}}$$

(21)

where  $z^{-1}$  is the unit delay operator and  $T_s$  is the sampling period. By using a higher order approximation instead of the above first order approximation, we may obtain better performances. However, we will consider the above first order approximation for efficient and simple implementation of the proposed fractional order PID-type control law. Denote  $D^{\mu}x_3(k), D^{\lambda}x_2(k), \text{ and } x_3(k) = D^{-1}x_2(k) \text{ as } D^{\mu}x_3(k) = a(k),$  $D^{\lambda}x_2(k) = b(k)$ , and  $x_3(k) = D^{-1}x_2(k)$  at the sampling instant  $kT_s$ , respectively. Then the above approximation (21) implies that

$$a(k) + \mu a(k-1) = \left(\frac{2}{T_s}\right)^{\mu} [x_3(k) - \mu x_3(k-1)]$$

$$b(k) + \lambda b(k-1) = \left(\frac{2}{T_s}\right)^{\lambda} [x_2(k) - \lambda x_2(k-1)]$$

$$x_3(k) - x_3(k-1) = \frac{T_s}{2} [x_2(k) + x_2(k-1)]$$

After all, the fractional order differential value  $D^{\mu}x_3$  at the sampling instant  $kT_s$  is computed by using the following update equation:

$$a(k) = \left(\frac{2}{T_s}\right)^{\mu} [x_3(k) - \mu x_3(k-1)] - \mu a(k-1) \quad (22)$$

the value  $D^{\lambda}x_2(k)$  is constructed by

$$b(k) = \left(\frac{2}{T_s}\right)^{\lambda} \left[x_2(k) - \lambda x_2(k-1)\right] - \lambda b(k-1) \quad (23)$$

and the state variable  $x_3(k)$  is updated by

$$x_3(k) = \frac{T_s}{2} [x_2(k) + x_2(k-1)] + x_3(k-1)$$

(24)

Using the above update equations the fractional order PIDtype control law can be computed by

$v(k) = -K_1 x_1(k) - K_P x_2(k) - K_I a(k) - K_D b(k)$  (25)

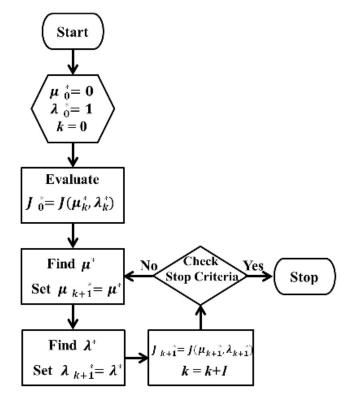

The control performances of the proposed fractional order PID-type controller (9) with the gains (10) depend heavily on the values of  $\mu$  and  $\lambda$ . Because the integral performance index  $J(\mu, \lambda) = \int_0^{t_f} e^2 dt$  is the most popular one to compare the control performances of PID controllers where  $t_f$  is the final time, this paper considers the integral performance index Jto find the optimal orders  $\mu$  and  $\lambda$ . The problem of finding the optimal orders  $\mu$  and  $\lambda$  minimizing J is difficult to solve analytically, however we can easily find a minimum solution by the following simple direct search algorithm:

*Tuning Algorithm of*  $(\mu, \lambda)$

- TA1: Set  $\mu_0^* = 0$ ,  $\lambda_0^* = 1$ , and k = 0. TA2: Evaluate the integral performance index  $J_k^* = J(\mu_k^*, \lambda_k^*) = \int_0^{t_f} e^2 dt$  with  $\mu_k^*, \lambda_k^*$ , and the gains of (10).

- TA3: Find an optimal  $\mu^* \in [0, 1]$  guaranteeing  $J(\mu^*, \lambda_k^*) \leq$  $J_k^* = J(\mu_k^*, \lambda_k^*)$  by iterating  $\mu$  for the given fixed  $\mu_k^*$ ,  $\lambda_k^*$ , and the gains of (10). Set  $\mu_{k+1}^* = \mu^*$ . TA4: Find an optimal  $\lambda^* \in [0, 1]$  guaranteeing

- $J(\mu_{k+1}^*, \lambda^*) \leq J(\mu_{k+1}^*, \lambda_k^*)$  by iterating  $\lambda$  for the given fixed  $\mu_{k+1}^*, \lambda_k^*$ , and the gains of (10). Set  $\lambda_{k+1}^* = \lambda^*$ .

**FIGURE 3.** Flow chart of tuning algorithm of  $(\mu, \lambda)$ .

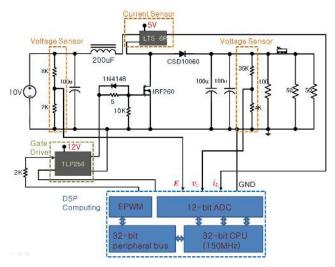

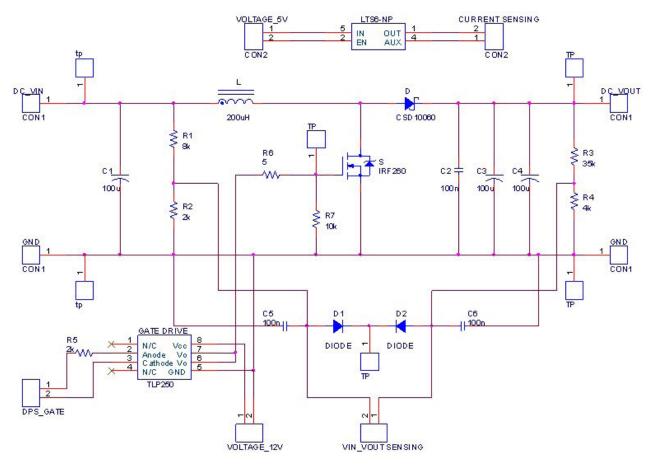

FIGURE 4. Schematic diagram of experimental testbed.

TA5: Set  $J_{k+1}^* = J(\mu_{k+1}^*, \lambda_{k+1}^*)$  and k = k + 1. TA6: If stop criteria hold then stop, otherwise go to TA3.

Remark 1: Figure 3 shows a flow chart of the Tuning Algorithm of  $(\mu, \lambda)$ . The following stop criteria can be used for the *Tuning Algorithm of*  $(\mu, \lambda)$ : The maximum iteration number  $k_{max}$  is reached;  $J_k^*$  converges or becomes smaller than a prescribed value.

Remark 2: Our results can be summarized as the following design procedure:

Step1: Set the initial gain  $k_1 > 0$  and time constant  $\tau > 1/\omega_c$ .

FIGURE 5. Power stage circuit schematic diagram of boost DC-DC converter.

- Step2: Compute the PID gains  $K_P$ ,  $K_I$ , and  $K_D$  by using (10). Step3: Find optimal orders  $\mu$  and  $\lambda$  by using the *Tuning* Algorithm of  $(\mu, \lambda)$ .

- Step4: If the control performances are unsatisfactory then select alternative  $k_1$  and  $\tau$  and go to Step2. Otherwise stop.

*Remark 3*: From the fact that the integer order PID-type controller corresponds to the special case of the proposed fractional order PID-type control law (25) with  $\mu = 0$  and  $\lambda = 1$ , we can easily see that the integer order PID-type controller requires 6 multiplications and 7 additions whereas the proposed fractional order PID-type control law (25) requires 9 multiplications and 9 additions, thus the total execution time increase is 3 multiplications and 2 additions. This increase is not serious considering traditional powerful and fast DSPs. The experimental study given below also verifies that the total execution time increase is small compared to the sampling period.

Remark 4: In order to design the integer order PID-type controller (7), the four design parameters  $K_1$ ,  $K_P$ ,  $K_I$ , and  $K_P$ should be selected within the conventional frameworks such as [14] while only the two design parameters  $K_1$  and  $\tau$  have to be specified within our framework. The design parameters of the proposed fractional order controller (25) are  $K_1$ ,  $\tau$ ,  $\mu$ ,

VOLUME 7, 2019

and  $\lambda$ . Thus, the number of the design parameters of the proposed fractional order controller is 4. In the conventional integer order PID controllers, the derivative term  $\dot{e}(k) = \dot{x}_2(k) = b(k)$  at the sampling instant  $kT_s$  is usually computed by using the following update equation

$$b(k) = \frac{2}{T_s + 2\epsilon} [x_2(k) - x_2(k-1)] - \frac{T_s - 2\epsilon}{T_s + 2\epsilon} b(k-1)$$

r

0

$$b(k) = \frac{1}{T_s + \epsilon} [x_2(k) - x_2(k-1)] + \frac{\epsilon}{T_s + \epsilon} b(k-1)$$

where  $\epsilon \geq 0$  is a filter time constant which is tuned to reduce performance degradation due to the high frequency noise magnified by the derivative term. This implies that the discretized conventional integer order PID-type control design methods may require to select the parameter value  $\epsilon$ besides  $K_1$ ,  $K_P$ ,  $K_I$ , and  $K_P$ .

*Remark 5:* Denote  $H_F(s)$  and  $\Delta(s)$  as

$$H_F(s) = K_P + K_I s^{\mu - 1} + K_D s^{\lambda}$$

<sup>(26)</sup>

$$\Delta(s) = [H_F(s) - H(s)]/H(s)$$

=  $[K_I(s^{\mu-1} - s^{-1}) + K_D(s^{\lambda} - s)]/H(s)$  (27)

142657

FIGURE 6. Experimental testbed.

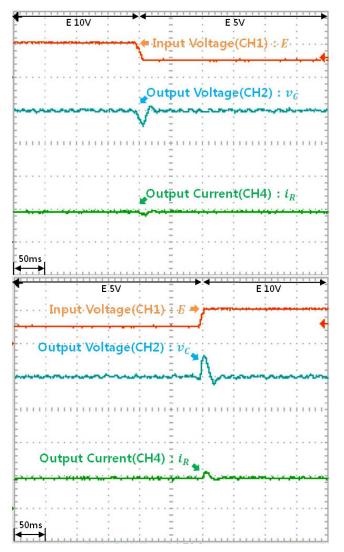

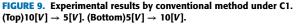

**FIGURE 7.** Experimental results by proposed method under C1. (Top) $10[V] \rightarrow 5[V]$ . (Bottom) $5[V] \rightarrow 10[V]$ .

where H(s) is defined in (14). Then by using (17) and the small gain theorem [13], we can show that the linearized boost DC-DC converter model (6) with the proposed fractional order PID-type controller (9) is stable if the following

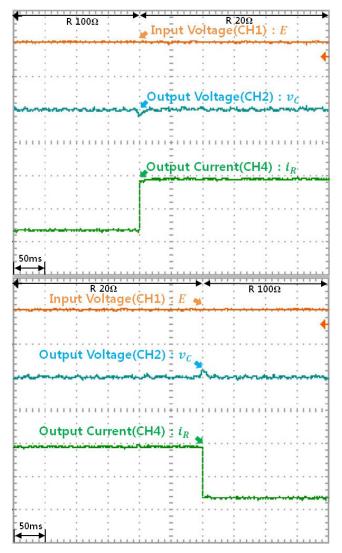

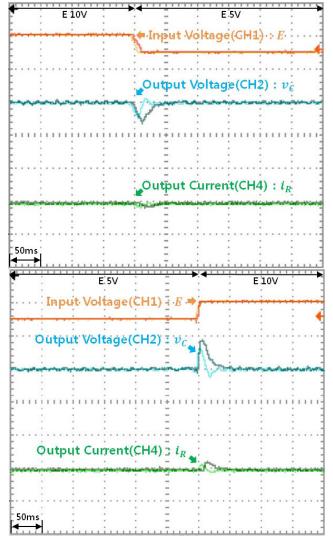

**FIGURE 8.** Experimental results by proposed method under C2. (Top)100[ $\Omega$ ]  $\rightarrow$  20[ $\Omega$ ]. (Bottom)20[ $\Omega$ ]  $\rightarrow$  100[ $\Omega$ ].

condition is satisfied

$$\|\Delta(j\omega)\| < \frac{1}{\max \|G_{cl}(j\omega)\|} \tag{28}$$

for all frequency range. We can see that

$$\|G_{cl}(j\omega)\| = \sqrt{\frac{1 + \omega_c^{-2}\omega^2}{1 + \tau^2\omega^2}} \le \max(1, \frac{1}{\tau\omega_c})$$

(29)

which implies that the stability condition (28) can be rewritten as

$$\|\Delta(j\omega)\| < \min(1, \tau\omega_c) \tag{30}$$

For the case of  $\tau > 1/\omega_c$ , the stability condition (30) can be reduced to  $||\Delta(j\omega)|| < 1$ . The stability condition (30) is only a sufficient one, thus the closed-loop control system can be stable even (30) does not hold. The stability condition (30) is trivially satisfied in the case of the integer order PID-type controller (7) because  $\Delta(s) = 0$ . We can see that if the nonnegative design parameters  $\mu$  and  $\lambda$  are chosen as  $\mu \ll 1$

and  $0 \le 1 - \lambda \ll 1$ , then the above stability condition (30) can be easily satisfied.

## **IV. EXPERIMENTAL VERIFICATION**

For experimental study, we consider a boost converter with  $L = 200[\mu H]$  and  $C = 200[\mu F]$ . We assume that the nominal output load resistance and external source voltage are  $R_0 = 100[\Omega]$  and  $E_0 = 10[V]$ , respectively. The sampling frequency  $f_s$  is set as  $f_s = 1/T_s = 50[kHz]$ . The parameter values used for experimental study are summarized in Table 1.

By using (4),  $R_0 = 100[\Omega]$ ,  $E_0 = 10[V]$ , and the boost converter parameters given in Table I, we can derive the following boost converter model

$$\dot{z} = \begin{bmatrix} 0 & -2500 & 0\\ 2500 & -50 & 0\\ 0 & 1 & 0 \end{bmatrix} z + \begin{bmatrix} \frac{v_c}{L}\\ -\frac{i_L}{C}\\ 0 \end{bmatrix} v \quad (31)$$

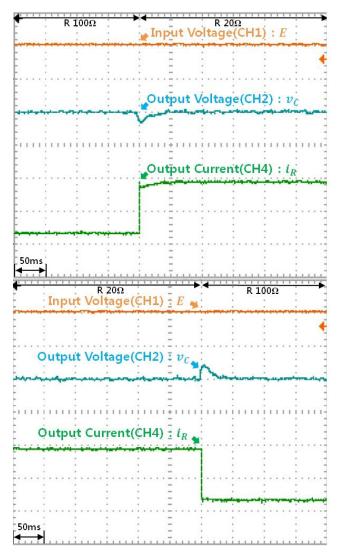

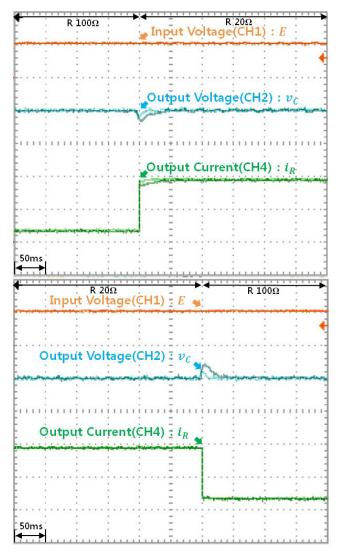

**FIGURE 10.** Experimental results by conventional method under C2. (Top) $100[\Omega] \rightarrow 20[\Omega]$ . (Bottom) $20[\Omega] \rightarrow 100[\Omega]$ .

TABLE 1. Boost converter parameters for simulation and experiment.

| External source voltage $(E)$  | 5 - 10 [V]     |

|--------------------------------|----------------|

| Current sensor                 | LTS 6-NP       |

| Sampling frequency $(f_s)$     | 50[kHz]        |

| Load resistance $(R)$          | 100 [Ω]        |

| Output capacitance $(C)$       | $200  [\mu F]$ |

| Input inductance (L)           | $200  [\mu H]$ |

| Output diode (D)               | CSD10060       |

| Main switch $(S)$              | IRFP26N60      |

| Digital Signal Processor (DSP) | TMS320F28335   |

In order to verify the practical feasibility and effectiveness of the proposed method, we consider the following two cases C1-2:

C1: The external source voltage *E* changes from  $10[V] \rightarrow 5[V] \rightarrow 10[V]$  while the output load resistor *R* and the reference voltage  $V_r$  are kept constant at the nominal values  $R = 100[\Omega]$  and  $V_r = 20[V]$ , respectively.

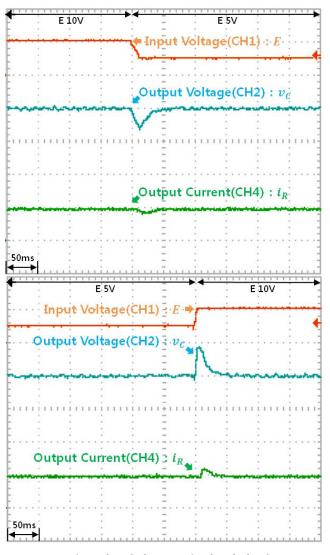

**FIGURE 11.** Experimental results under C1. (Top) $10[V] \rightarrow 5[V]$ . (Bottom) $5[V] \rightarrow 10[V]$ .

C2: The output load resistor *R* changes from  $100[\Omega] \rightarrow 20[\Omega] \rightarrow 100[\Omega]$  while the external source voltage *E* and the reference voltage  $V_r$  hold constant at the nominal values E = 10[V] and  $V_r = 20[V]$ , respectively.

A Texas Instruments TMS320F28335 floating-point DSP with the clock speed of 150[MHz] is used to implement the proposed fractional order PID-type control algorithm. A 12-bit ADC module with a built-in sample-and-hold circuit is used for analog-to-digital conversion of the input inductor current  $i_L$  and the output capacitor voltage  $v_C$ . A Tektronix TDS5140B digital oscilloscope is employed to measure and plot the input voltage E, the output capacitor voltage  $v_C$ , and the output load resistor current  $i_R$ . Figure 4 shows the schematic diagram of the experimental testbed. Figure 5 depicts the circuit scheme of the power stage used for experimental study. Figure 6 illustrates the experimental setup. We assume that the desired time constant  $\tau$  is 0.001 leading to a 3-dB bandwidth of 1000, a rise time

**FIGURE 12.** Experimental results C2. (Top) $100[\Omega] \rightarrow 20[\Omega]$ . (Bottom) $20[\Omega] \rightarrow 100[\Omega]$ .

of  $2.2\tau = 0.0022$ , and a 2% settling time of  $4\tau = 0.004$ . By referring to the method presented in the previous section, we find optimal  $\lambda = 0.88$  and  $\mu = 0.06$ , and we obtain the proposed fractional order PID-type control law as follows:

$$v(k) = -0.1x_1(k) - 0.0399x_2(k) - 28.770a(k) -3.968 \times 10^{-6}b(k)$$

(32)

where a(k) and b(k) are updated by the following recursive equations

$$a(k) = \left(\frac{2}{T_s}\right)^{0.06} [x_3(k) - 0.06x_3(k-1)] - 0.06a(k-1)$$

(33)

$$b(k) = \left(\frac{2}{T_s}\right)^{0.88} [x_2(k) - 0.88x_2(k-1)] - 0.88b(k-1)$$

(34)

Under the clock speed of 150[MHz], the maximum, minimum, and average calculation times of the above proposed fractional order control law v(k) of (32) are 1.26  $\mu$ sec, 0.86  $\mu$ sec, and 1.06  $\mu$ sec, respectively. Figure 7 shows the time trajectories of the external source voltage *E*, the output capacitor voltage  $v_C$ , and the output load resistor current  $i_R$ subject to *E* changing abruptly from  $10[V] \rightarrow 5[V] \rightarrow$ 10[V] with  $R = 100[\Omega]$  and  $V_r = 20[V]$ . Figure 8 illustrates the histories of *E*,  $v_C$ , and  $i_R$  when the output load resistor *R* changes abruptly from  $100[\Omega] \rightarrow 20[\Omega] \rightarrow 100[\Omega]$  while *E* and  $V_r$  hold constant at E = 10[V] and  $V_r = 20[V]$ .

By setting  $\mu = 0$  and  $\lambda = 1$ , a conventional integer order PID-type controller can be obtained as follows:

$$v(k) = -0.1x_1(k) - 0.0399x_2(k) - 28.770x_3(k) -3.968 \times 10^{-6}b(k)$$

(35)

where b(k) are updated by the following recursive equations

$$b(k) = \frac{2}{T_s} [x_2(k) - x_2(k-1)] - b(k-1)$$

(36)

The maximum, minimum, and average calculation times of the above conventional integer order control law v(k) of (35) are 0.98  $\mu$ sec, 0.58  $\mu$ sec, and 0.78  $\mu$ sec, respectively. Figures 9 and 10 show the time trajectories by the above conventional integer order PID-type controller (35). Figure 9 illuminates the time trajectories of the external source voltage E, the output capacitor voltage  $v_C$ , and the output load resistor current  $i_R$  subject to E changing abruptly from  $10[V] \to 5[V] \to 10[V]$  with  $R = 100[\Omega]$  and  $V_r = 20[V]$ . Figure 10 depicts the histories of E,  $v_C$ , and  $i_R$  when the output load resistor R changes abruptly from  $100[\Omega] \rightarrow$  $20[\Omega] \rightarrow 100[\Omega]$  while E and  $V_r$  hold constant at E = 10[V]and  $V_r = 20[V]$ . In order to highlight the differences of the control performances, Figures 7 and 9 are superimposed into Figure 11, and Figures 8 and 10 are also superimposed into Figure 12. Figures 7 through 12 imply that the proposed controller achieves 25 % reduction in maximum output voltage error, 25 % reduction in maximum output current error, and 25 % reduction in recovery time for the case C1 compared to the conventional integer order controller (35). The proposed controller achieves 50 % reduction in maximum output voltage error, and about 70 % reduction in recovery time for the case C2 compared to the conventional controller. The increase in average calculation time caused by using the proposed fractional order PID-type controller instead of the conventional controller is 0.36  $\mu$ sec. The maximum and average calculation times of the proposed fractional order PID-type controller are 1.26  $\mu$ sec and 1.06  $\mu$ sec. These are much less than the sampling period 20  $\mu$ sec. Thus the execution time cannot be a constraint when the proposed controller is implemented on a DSP. And the experimental results given in Figures 7 to 12 imply that the proposed fractional order PID-type controller may require a slight increase in calculation time but it gives a much faster recovery time, less overshoot, smaller maximum output error compared to the conventional controller.

### **V. CONCLUSION**

We proposed a fractional order PID-type control algorithm for a boost DC-DC converter. We also gave simulation and experimental results to verify the effectiveness and practicality of the proposed control system under several operating conditions. Via experimental study we verified that the proposed method can give a less overshoot and faster recovery time compared to the conventional integer order controller under abrupt load or input voltage variations. Finally, we remark that fractional order PID-type controllers for buck converters and buck-boost converters can also be designed using formulations similar to that provided in this paper.

### REFERENCES

- R. P. Aguilera and D. E. Quevedo, "Predictive control of power converters: Designs with guaranteed performance," *IEEE Trans Ind. Informat.*, vol. 11, no. 1, pp. 53–63, Feb. 2015.

- [2] S. Banerjee and K. Chakrabarty, "Nonlinear modeling and bifurcations in the boost converter," *IEEE Trans. Power Electron.*, vol. 13, no. 2, pp. 252–260, Mar. 1998.

- [3] S. E. Beid and S. Doubabi, "DSP-based implementation of fuzzy output tracking control for a boost converter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 1, pp. 196–206, Jan. 2014.

- [4] O. A. Beg, H. Abbas, T. T. Johnson, and A. Davoudi, "Model validation of PWM DC-DC converter," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7049–7059, Sep. 2017.

- [5] M. di Bernardo and F. Vasca, "Discrete-time maps for the analysis of bifurcations and chaos in DC/DC converters," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 2, pp. 130–143, Feb. 2000.

- [6] N. Bouarroudj, D. Boukhetala, B. Benlahbib, and B. Batoun, "Sliding model control based on fractional order calculus for DC-DC converters," *Int. J. Math. Model. Comput.*, vol. 5, no. 4, pp. 319–333, 2015.

- [7] D. Cafagna and G. Grassi, "Bifurcation analysis and chaotic behavior in boost converters: Experimental results," *Nonlinear Dyn.*, vol. 44, nos. 1–4, pp. 251–262, 2006.

- [8] A. J. Calderón, B. M. Vinagre, and V. Feliu, "Fractional order control strategies for power electronic buck converters," *Signal Process.*, vol. 86, pp. 2803–2819, Oct. 2006.

- [9] Y. Q. Chen and K. L. Moore, "Discretization schemes for fractionalorder differentiators and integrators," *IEEE Trans. Circuit Syst. I, Fundam. Theory Appl.*, vol. 49, no. 3, pp. 363–367, Mar. 2002.

- [10] L. Cheng, P. Acuna, R. P. Aguilera, J. Jiang, S. Wei, J. E. Fletcher, and D. D. C. Lu, "Model predictive control for DC-DC boost converters with reduced-prediction horizon and constant switching frequency," *IEEE Trans. Power Electron.*, vol. 33, no. 10, pp. 9064–9075, Oct. 2018.

- [11] G.-B. Chung and S.-G. Kwack, "Application of fuzzy integral control for output regulation of asymmetric half-bridge DC/DC converter with current doubler rectifier," *J. Power Electron.*, vol. 7, no. 3, pp. 238–245, 2007.

- [12] P. Cortés, M. P. Kazmierkowski, R. M. Kennel, D. E. Quevedo, and J. Rodríguez, "Predictive control in power electronics and drives," *IEEE Trans. Ind. Electron.*, vol. 55, no. 12, pp. 4312–4324, Dec. 2008.

- [13] J. C. Doyle, B. A. Francis, and A. R. Tannenbaum, *Feedback Control Theory*. New York, NY, USA: Macmillan, 1992.

- [14] G. Escobar, R. Ortega, H. Sira-Ramírez, J. Vilain, and I. Zein, "An experimental comparison of several nonlinear controllers for power converters," *IEEE Control Syst.*, vol. 19, no. 1, pp. 66–82, Feb. 1999.

- [15] G. C. Goodwin, S. F. Graebe, and M. E. Salgado, *Control System Design*. London, U.K.: Pearson, 2000.

- [16] L. Guo, J. Y. Hung, and R. M. Nelms, "Evaluation of DSP-based PID and fuzzy controllers for DC–DC converters," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 2237–2248, Jun. 2009.

- [17] S. Hiti and D. Borojevic, "Robust nonlinear control for the boost converter," *IEEE Trans. Power Electron.*, vol. 10, no. 6, pp. 651–658, Nov. 1995.

- [18] S. H. Hosseinnia, I. Tejado, B. M. Vinagre, and D. Sierociuk, "Booleanbased fractional order SMC for switching systems: Application to a DC-DC buck converter," *Signal, Image Video Process.*, vol. 6, no. 3, pp. 445–451, 2012.

- [19] P. Karamanakos, T. Geyer, and S. Manias, "Direct model predictive current control strategy of DC–DC boost converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 1, no. 4, pp. 337–346, Dec. 2013.

- [20] P. Karamanakos, T. Geyer, and S. Manias, "Direct voltage control of DC–DC boost converters using enumeration-based model predictive control," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 968–978, Feb. 2014.

- [21] S. Kouro, P. Cortes, R. Vargas, V. Ammann, and J. Rodriguez, "Model predictive control—A simple and powerful method to control power converters," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 1826–1838, Jun. 2009.

- [22] J. Kumar, V. Kumar, and K. P. S. Rana, "A fractional order fuzzy PD+I controller for three-link electrically driven rigid robotic manipulator system," *J. Intell. Fuzzy Syst.*, vol. 35, no. 6, pp. 1–13, Jul. 2018.

- [23] W. R. Liou, W. B. Lacorte, A. B. Caberos, M.-L. Yeh, J.-C. Lin, S.-C. Lin, C.-S. Sun, "A programmable controller IC for DC/DC converter and power factor correction applications," *IEEE Trans. Ind. Informat.*, vol. 9, no. 4, pp. 2105–2113, Nov. 2013.

- [24] K. Mandal, S. Banerjee, and C. Chakraborty, "A new algorithm for smallsignal analysis of DC–DC converters," *IEEE Trans. Ind. Informat.*, vol. 10, no. 1, pp. 628–636, Feb. 2014.

- [25] M. M. Mardani, M. H. Khooban, A. Masoudian, and T. Dragicevic, "Model predictive control of DC-DC converters to mitigate the effects of pulsed power loads in naval DC microgrids," *IEEE Trans. Ind. Electron.*, vol. 66, no. 7, pp. 5676–5685, Jul. 2019.

- [26] C. I. Muresan, S. Folea, G. Mois, and E. H. Dulf, "Development and implementation of an FPGA based fractional order controller for a DC motor," *Mechatronics*, vol. 23, no. 7, pp. 798–804, 2013.

- [27] P. Mattavelli, L. Rossetto, G. Spiazzi, and P. Tenti, "General-purpose fuzzy controller for DC-DC converters," *IEEE Trans. Power Electron.*, vol. 12, no. 1, pp. 79–86, Jan. 1997.

- [28] F. M. Oettmeier, J. Neely, S. Pekarek, R. DeCarlo, and K. Uthaichana, "MPC of switching in a boost converter using a hybrid state model with a sliding mode observer," *IEEE Trans. Ind. Electron.*, vol. 56, no. 9, pp. 3453–3466, Sep. 2009.

- [29] S. Oucheriah and L. Guo, "PWM-based adaptive sliding-mode control for boost DC–DC converters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 8, pp. 3291–3294, Aug. 2013.

- [30] J. Moreno-Valenzuela and J. Guzman-Guemez, "Experimental evaluations of voltage regulators for a saturated boost DC-to-DC power converter," *Trans. Inst. Meas. Control*, vol. 38, no. 3, pp. 327–337, 2016.

- [31] J. Moreno-Valenzuela and O. Garcia-Alarcon, "On control of a boost DC-DC power converter under constrained input," *Complexity*, vol. 2017, Dec. 2017, Art. no. 4143901.

- [32] A. G. Perry, G. Feng, Y.-F. Liu, and P. C. Sen, "A design method for PI-like fuzzy logic controllers for DC–DC converter," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 345–355, Oct. 2007.

- [33] P. Shah and S. Agashe, "Review of fractional PID controller," *Mechatron*ics, vol. 38, pp. 29–41, Sep. 2016.

- [34] H. Sira-Ramirez, "Nonlinear P-I controller design for switchmode DC-to-DC power converters," *IEEE Trans. Circuits Syst.*, vol. 38, no. 4, pp. 410–417, Apr. 1991.

- [35] H. Sira-Ramirez, "On the generalized PI sliding mode control of DC-to-DC power converters: A tutorial," *Int. J. Control*, vol. 76, nos. 9–10, pp. 1018–1033, 2003.

- [36] H. Sira-Ramírez, R. A. Pérez-Moreno, R. Ortega, and M. García-Esteban, "Passivity-based controllers for the stabilization of DC-to-DC power converters," *Automatica*, vol. 33, no. 4, pp. 499–513, Apr. 1997.

- [37] S.-C. Tan, Y. M. Lai, C. K. Tse, and M. K. H. Cheung, "Adaptive feedforward and feedback control schemes for sliding mode controlled power converters," *IEEE Trans. Power Electron.*, vol. 21, no. 1, pp. 182–192, Jan. 2006.

- [38] J. J. Slotine and W. Li, *Applications of Nonlinear Control*. Upper Saddle River, NJ, USA: Prentice-Hall, 1991.

- [39] S.-C. Tan, Y. M. Lai, and C. K. Tse, "Indirect sliding mode control of power converters via double integral sliding surface," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 600–611, Mar. 2008.

- [40] N. Ullah, A. Ullah, A. Ibeas, and J. Herrera, "Improving the hardware complexity by exploiting the reduced dynamics-based fractional order system," *IEEE Access*, vol. 5, pp. 7714–7723, May 2017.

- [41] D. Valerio and J. S. da Costa, "Time-domai implementatio of fractional order controllers," *IEE Proc.-Control Theory Appl.*, vol. 152, no. 5, pp. 539–552, Sep. 2005.

- [42] S. Vazquez, J. I. Leon, L. G. Franquelo, J. Rodriguez, H. A. Young, A. Marquez, and P. Zanchetta, "Model predictive control: A review of its applications in power electronics," *IEEE Ind. Electron. Mag.*, vol. 8, no. 1, pp. 16–31, Mar. 2014.

- [43] B. M. Vinagre, Y. Q. Chen, and I. Petras, "Two direct Tustin discretization methods for fractional-order differentiator/integrator," *J. Franklin Inst.*, vol. 340, no. 5, pp. 349–362, Aug. 2003.

- [44] B. M. Vinagre, I. Podlubny, A. Hernandez, and V. Feliu, "Some approximations of fractional order operators used in control theory and applications," *Fractional Calculus Appl. Anal.*, vol. 3, no. 3, pp. 231–248, 2000.

- [45] B. Wang, V. R. K. Kanamarlapudi, L. Xian, X. Peng, K. T. Tan, and P. L. So, "Model predictive voltage control for single-inductor multiple-output DC-DC converter with reduced cross regulation," *IEEE Trans. Ind. Electron.*, vol. 63, no. 7, pp. 4187–4197, Jul. 2016.

- [46] Q. Wei, B. Wu, D. Xu, and N. R. Zargari, "Model predictive control of capacitor voltage balancing for cascaded modular DC-DC converter," *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 752–761, Jan. 2017.

- [47] I. Yazici and E. K. Yaylaci, "Fast and robust voltage control of DC–DC boost converter by using fast terminal sliding mode controller," *IET Power Electron.*, vol. 9, no. 1, pp. 120–125, 2016.

- [48] H. A. Young, M. A. Perez, J. Rodríquez, and H. Abu-Rub, "Assessing finite-control-set model predictive control: A comparison with a linear current controller in two-level voltage source inverters," *IEEE Ind. Electron. Mag.*, vol. 8, no. 1, pp. 44–52, Mar. 2014.

- [49] Y. Zhang, H. Liu, J. Li, M. Sumner, and C. Xia, "DC–DC boost converter with a wide input range and high voltage gain for fuel cell vehicles," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4100–4111, May 2019.

**SANG-WHA SEO** received the B.S. degree in electronic engineering from Seokyeong University, Seoul, South Korea, in 2007, and the M.S. and Ph.D. degrees in electrical engineering from Dongguk University, Seoul, in 2010 and 2017, respectively. He is currently with Propulsion System Research Team, Korea Railroad Research Institute.

**HAN HO CHOI** received the B.S. degree in control and instrumentation engineering from Seoul National University, Seoul, South Korea, in 1988, and the M.S. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea, in 1990 and 1994, respectively. He is currently with the Division of Electronics and Electrical Engineering, Dongguk University, Seoul. His research interest includes control theory and its applications to real-world problems.

....