### **Digital Phase Locked Loops for Radio Frequency Synthesis**

Mahmoud, Ahmed

2017

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Mahmoud, A. (2017). Digital Phase Locked Loops for Radio Frequency Synthesis. Department of Electrical and Information Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Digital Phase Locked Loops for Radio Frequency Synthesis

### Ahmed Mahmoud

Doctoral Thesis Electrical Engineering Lund, December 2017

Ahmed Mahmoud Department of Electrical and Information Technology Electrical Engineering Lund University P.O. Box 118, 221 00 Lund, Sweden

Series of licentiate and doctoral theses ISSN 1654-790X; No. 106 ISBN 978-91-7753-419-8 (print) ISBN 978-91-7753-420-4 (pdf)

© 2017 Ahmed Mahmoud Typeset in Palatino and Helvetica using IATEX  $2_{\mathcal{E}}$ . Printed in Sweden by Tryckeriet i E-huset, Lund University, Lund.

No part of this thesis may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author.

# Popular Science

The demand of handsets with high data rate capability, more complex features and long battery life at an affordable cost has been the driving force behind most innovations in wireless communication systems for consumer electronics. These innovations have made radio communication smooth and efficient, thereby maximizing its impact worldwide and reshaping the way data is shared between people.

Central to wireless communication systems are the radio transmitter and receiver, which are responsible for transmitting and receiving data between wireless devices. A key function in both is *frequency generation*, which is needed to place the transmitted data in a very well controlled region of the frequency spectrum (typically, at radio-frequency, RF), and, conversely, to transfer the received data from RF to the original low frequency. Frequency generation is usually accomplished by means of a *phase-locked loop* (PLL), where, starting from a very stable reference frequency of a few tens of MHz, very precise frequencies up to several GHz are synthesized.

The wireless communication environment is very hostile, with many interference sources potentially able to contaminate the often tiny desired signal. This poses tough requirements on the purity of the RF signal generated by the PLL, since the PLL must coexist with a number of other radio blocks integrated on the same silicon die. In particular, the ever larger digital signal processing units in the typical radio fabricated in a modern CMOS process generate a large amount of switching noise, caused by all commutations between logic 0 and logic 1 occurring there, which may easily affect the integrity of the PLL.

At the same time, the conventional circuit design of analog functions, of which the PLL is an example, is becoming increasingly problematic, as ultrascaled CMOS technologies mandate the use of very low power supply voltages, as a consequence of the extremely reduced dimensions of the CMOS devices.

Furthermore, the effort associated to bring about such a technology scaling has turned once cheap CMOS processes into very expensive ones, and the relatively large area occupied by analog circuits is weighing heavily on the total cost of the radio transceiver.

Because of the above reasons, we are witnessing an unrelenting migration of analog functions towards the digital domain, and the foremost example of this is the digital PLL, which can exploit all the advantages, in terms of programmability, reconfigurability, adaptivity, and compactness, that are beyond the reach of the traditional PLL

In this dissertation, several techniques are demonstrated, that improve the design of the digital PLL, in terms of both overall architecture and individual PLL sub-blocks, obtaining excellent performances.

# Contents

| Po | pula  | ir Science ii                              | i |

|----|-------|--------------------------------------------|---|

| Pı | efac  | e i                                        | X |

| A  | ckno  | wledgments                                 | i |

| Li | st of | Abbreviations xii                          | i |

| Li | st of | Figures xvi                                | i |

| Li | st of | Tables xxii                                | i |

| 1  | Inti  | roduction                                  | 1 |

|    | 1.1   | Motivation                                 | 1 |

|    | 1.2   | Research Contribution                      | 2 |

|    | 1.3   | Thesis Outline                             | 4 |

| 2  | Fre   | quency Synthesizer Overview                | 7 |

|    | 2.1   | Introduction                               | 7 |

|    | 2.2   | Frequency Synthesizers in Transceivers     | 8 |

|    |       | 2.2.1 Superheterodyne Transceiver          | 9 |

|    |       | 2.2.2 Homodyne Transceiver                 | 0 |

|    | 2.3   | Frequency Synthesizer Architectures        | 1 |

|    |       | 2.3.1 Direct Analog Frequency Synthesizer  | 1 |

|    |       | 2.3.2 Direct Digital Frequency Synthesizer | 2 |

v

|   |     | 2.3.3 Indirect Frequency Synthesizer                                                                    | . 13 |

|---|-----|---------------------------------------------------------------------------------------------------------|------|

|   |     | 2.3.4 Hybrid Frequency Synthesizer                                                                      | . 15 |

|   | 2.4 | Performance Metrics of The Frequency Synthesizer                                                        | . 15 |

|   |     | 2.4.1 Frequency Tuning Range and Frequency Resolution                                                   | . 16 |

|   |     | 2.4.2 Spectral Purity                                                                                   | . 16 |

|   |     | 2.4.2.1 Phase Noise                                                                                     |      |

|   |     | 2.4.2.2 Spurious Tones                                                                                  |      |

|   |     | 2.4.3 Switching Time                                                                                    |      |

|   |     | 2.4.4 Power Consumption, Size and Portability                                                           | . 22 |

| 3 | DPI | LL Fundamentals                                                                                         | 23   |

|   | 3.1 | DPLL Architectures                                                                                      | . 23 |

|   | 3.2 | TDC-Based DPLL                                                                                          | . 24 |

|   |     | 3.2.1 Discrete and Continuous-Time Models                                                               | . 25 |

|   |     | 3.2.1.1 Digitally Controlled Oscillator                                                                 | . 25 |

|   |     | 3.2.1.2 Time to Digital Converter                                                                       |      |

|   |     | 3.2.1.3 Digital Loop Filter                                                                             |      |

|   |     | 3.2.1.4 MMD and $\Delta\Sigma$ Modulator                                                                |      |

|   |     | 3.2.1.5 Overall Transfer Functions                                                                      |      |

|   |     | 3.2.2 Noise Sources Analysis                                                                            |      |

|   |     | <ul><li>3.2.2.1 Reference Noise Transfer Function</li><li>3.2.2.2 TDC Noise Transfer Function</li></ul> |      |

|   |     | 3.2.2.2 TDC Noise Transfer Function                                                                     |      |

|   |     | 3.2.2.4 $\Delta\Sigma$ Modulator Noise Transfer Function                                                |      |

|   |     | 3.2.3 Phase Noise Performance                                                                           |      |

|   | 3.3 | Bang-Bang-Based DPLL                                                                                    |      |

|   |     | 3.3.1 Discrete and Continuous-Time Models                                                               |      |

|   |     | 3.3.1.1 DTC Control                                                                                     |      |

|   |     | 3.3.1.2 Pre-distorter                                                                                   | . 50 |

|   |     | 3.3.1.3 Loop Bandwidth Regulation                                                                       |      |

|   |     | 3.3.1.4 Frequency Acquisition Controller                                                                | . 55 |

| 4 | Dig | citally Controlled Oscillator                                                                           | 57   |

|   | 4.1 | Oscillator Fundamentals                                                                                 | . 58 |

|   | 4.2 | LC-Tank Oscillator                                                                                      | . 59 |

|   |     | 4.2.1 Principles of LC-Tank Oscillator                                                                  | . 59 |

|   |     | 4.2.2 Cross-Coupled Differential Pair                                                                   | . 60 |

|   | 4.3 | Review of Existing Phase Noise Models                                                                   | . 61 |

|   |     | 4.3.1 Hajimiri aı                     | nd Lee's Phase Noise Model 62                                                    |

|---|-----|---------------------------------------|----------------------------------------------------------------------------------|

|   |     | 4.3.2 Pepe and A                      | Andreani's Phase Noise Model 63                                                  |

|   | 4.4 | Oscillator Perfor                     | mance Parameters 64                                                              |

|   | 4.5 | Frequency Tunir                       | ng Overview                                                                      |

|   |     | 4.5.1 Wide Freq                       | uency Tuning Range Techniques 67                                                 |

|   |     | 4.5.1.1                               | Dual-Core DCO 67                                                                 |

|   |     | 4.5.1.2                               | Transformer-Based DCO 68                                                         |

|   |     | 4.5.1.3                               | Switched Inductors DCO 70                                                        |

|   |     | 4.5.1.4                               | Mode-Switching DCO                                                               |

|   |     | 4.5.2 Fine Tunin                      | g Techniques                                                                     |

|   |     | 4.5.2.1                               | $\Delta\Sigma$ Modulator Dithering 74                                            |

|   |     | 4.5.2.2                               | Capacitive Divider Technique 76                                                  |

|   |     | 4.5.2.3                               | Capacitive Degeneration Method 77                                                |

|   |     | 4.5.2.4                               | MOS Varactors Techniques 78                                                      |

|   | 4.6 | Oscillator Pullin                     | ng                                                                               |

|   |     | 4.6.1 EM Simula                       | ation Setup                                                                      |

|   |     | 4.6.2 EM Simula                       | ation Results                                                                    |

| 5 | TDO | C and DTC                             | 89                                                                               |

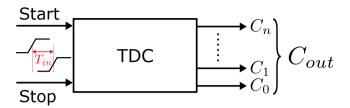

|   | 5.1 | TDC                                   |                                                                                  |

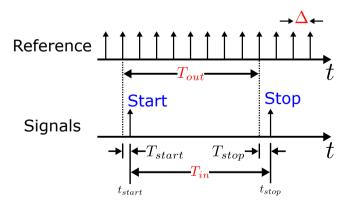

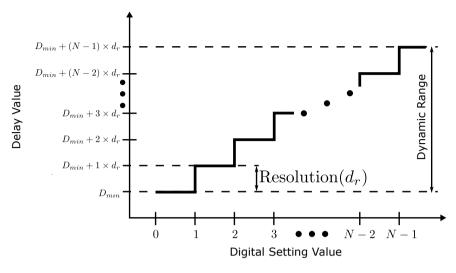

|   |     | 5.1.1 Performan                       | ce Parameters                                                                    |

|   |     | 5.1.1.1                               | Resolution                                                                       |

|   |     | 5.1.1.2                               | Dynamic Range 91                                                                 |

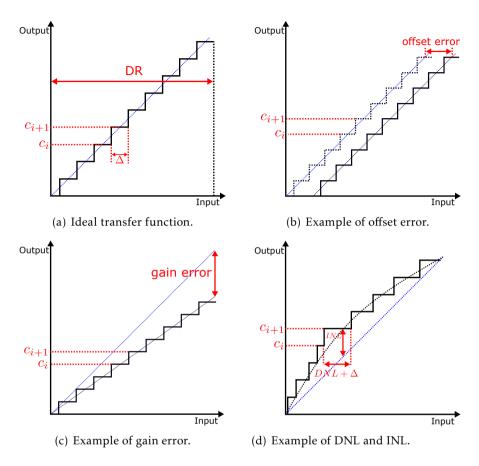

|   |     | 5.1.1.3                               | Linear and Non-Linear Non-Idealities 92                                          |

|   |     | 5.1.1.4                               | Dead Time, Conversion Time and Latency 93                                        |

|   |     | 5.1.2 TDC Archi                       | itectures Review                                                                 |

|   |     | 5.1.2.1                               | Delay-Line TDC 94                                                                |

|   |     | 5.1.2.2                               | Vernier TDC                                                                      |

|   |     | 5.1.2.3                               | GRO-TDC                                                                          |

|   |     | 5.1.2.4                               | 2D Vernier TDC                                                                   |

|   |     | 5.1.2.5                               | 2D GVTDC                                                                         |

|   |     | 5.1.2.6                               | Time-Amplifier-Based TDC 102                                                     |

|   | 5.2 | DTC                                   |                                                                                  |

|   |     | DIC                                   |                                                                                  |

|   |     |                                       | itectures Review                                                                 |

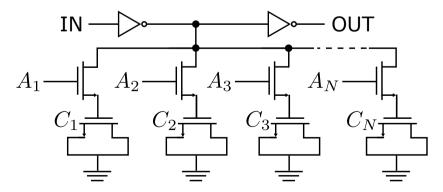

|   |     | 5.2.1 DTC Archi<br>5.2.1.1            | Shunt-Capacitor Inverter-Based DTC 104                                           |

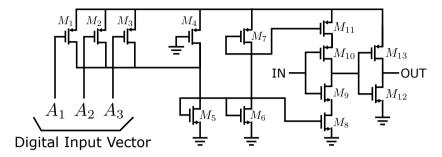

|   |     | 5.2.1 DTC Archi<br>5.2.1.1<br>5.2.1.2 | Shunt-Capacitor Inverter-Based DTC 104<br>Current-Starved Inverter-Based DTC 105 |

|   |     | 5.2.1 DTC Archi<br>5.2.1.1            | Shunt-Capacitor Inverter-Based DTC 104                                           |

| 6  | Exp   | erimental Results 109                                                                               |

|----|-------|-----------------------------------------------------------------------------------------------------|

|    | 6.1   | A 2.8-to-5.8 GHz Harmonic VCO Based on an 8-shaped Inductor in a 28 nm UTBB FD-SOI CMOS Process 109 |

|    |       | 6.1.1 VCO Prototype                                                                                 |

|    |       | 6.1.2 Measurement Results                                                                           |

|    | 6.2   | A Wide Band Fractional-N DPLL with a Noise Shaping 2D TDC                                           |

|    |       | for LTE-A Applications                                                                              |

|    |       | 6.2.1 LMS Based Quantization Noise Cancellation 117                                                 |

|    |       | 6.2.2 Subblocks                                                                                     |

|    |       | 6.2.3 Simulation Results                                                                            |

|    | 6.3   | A 2.8-3.8 GHz Low-Spur DTC-Based DPLL with a Class-D DCO                                            |

|    |       | in 65 nm CMOS                                                                                       |

|    |       | 6.3.1 Circuit Implementation                                                                        |

|    |       | 6.3.1.1 DTC and Fractional Frequency Divider 129                                                    |

|    |       | 6.3.1.2 DTC Linearization                                                                           |

|    |       | 6.3.2 Measurement Results                                                                           |

| 7  | Cor   | aclusions 137                                                                                       |

| Bi | bliog | graphy 141                                                                                          |

### Preface

This thesis summarizes my academic work carried out in the mixed-signal group at the department of Electrical and Information Technology, Lund University, Sweden, from November 2012 to August 2017. In the following, I will describe my contributions to the published papers I have co-authored.

I L. Fanori, A. Mahmoud, T. Mattsson, P. Caputa, S. Ramo, and P. Andreani, "A 2.8-to-5.8 GHz harmonic VCO in a 28 nm UTBB FD-SOI CMOS process," in Radio Frequency Integrated Circuits Symposium (RFIC), 2015 IEEE, 2015, pp. 195-198.

**Contributions.** I helped the first author with circuit simulations and measurements on the designed oscillator.

II A. Mahmoud, L. Fanori, T. Mattsson, P. Caputa, and P. Andreani, "A 2.8-to-5.8 GHz harmonic VCO based on an 8-shaped inductor in a 28 nm UTBB FD-SOI CMOS process," Analog Integrated Circuits and Signal Processing, vol. 88, no. 3, pp. 391-399, 2016.

**Contributions.** I performed all of the analysis and simulations of the magnetic coupling of the 8-shaped inductor. I helped the first author with circuit simulations and measurements on the designed oscillator. I wrote the section about the magnetic coupling, and re-wrote the rest.

III A. Mahmoud, P. Andreani, and P. Lu, "A 65nm CMOS fraction-N digital PLL with shaped in-band phase noise," in Nordic Circuits and Systems Conference (NORCAS): NORCHIP & International Symposium on System-on-Chip (SoC), 2015. IEEE, 2015, pp. 1-4.

**Contributions.** I performed a large part of the PLL modeling, simulation, implementation, and layout design. I wrote most of the manuscript.

IV A. Mahmoud, P. Andreani, and P. Lu, "A wide band fractional-N digital PLL with a noise shaping 2-D time to digital converter for LTE-A applications," Analog Integrated Circuits and Signal Processing, vol. 89, no. 2, pp. 337-345, 2016.

Contributions. I performed a large part of the PLL modeling, simulation, implementation, and layout design. I performed all the analysis and simulation of the  $\Delta\Sigma$  quantization noise cancellation scheme. I wrote the manuscript.

**V** A. Mahmoud, P. Andreani and F. Pepe, "A 2.8-3.8-GHz Low-Spur DTC-Based DPLL With a Class-D DCO in 65-nm CMOS," in IEEE Microwave and Wireless Components Letters, vol. PP, no. 99, pp. 1-3.

**Contribution** I performed most of the modeling, simulation, implementation, and layout design; I took the measurements, and wrote the manuscript.

Valuable help and guidance have been received from my co-authors during different stages of each work. My supervisor' contributions from the idea, design development, simulations up to manuscript production significantly enhanced the quality of work.

## Acknowledgments

As I am approaching the final stage of my graduate career at EIT, I realize I have been blessed by God to collaborate with several people that were very supportive in my research. I believe I would not have been able to accomplish so much without the help from so many.

First and foremost, I would like to express my deepest gratitude to my supervisor Associate Professor Pietro Andreani. His support is always there whenever I need it. His guidance helped me to overcome numerous difficulties encountered during my research.

I also would like to thank my co-supervisors, Dr. Luca Fanori, Dr. Ping Lu and Dr. Federico Pepe. I am greatly indebted to them, and respectful for the encouragements and support they have given me all throughout my graduate studies. I have learnt a great deal from them. Thank you for always having time for me and for all the valuable suggestions and discussions over the years.

I want to thank, too, the many colleagues and friends who have directly or indirectly contributed to my work and have made this experience all themore valuable: Mohammed, Rakesh, Yang, Mojtaba, Dimitar, Farrokh, Breeta, Babak, Oskar, Xiaodong, Siyu, Hemanth, Steffen, Jesús, Muris, Anders, Waqas, Jonas, Mattias, Dejan, and Therese, for the many discussions and the generous help they provided.

I would like to sincerely thank the seniors at the department of EIT. Professor Viktor Öwall, Professor Henrik Sjöland, Associate Professor Markus Törmänen, Associate Professor Joachim Rodrigues, Associate Professor Erik Larsson and Associate Professor Liang Liu. I also thank them for giving me the opportunity to work with many talented researchers.

I would like to thank Göran Jönsson for his great help in the measurement lab, and the people providing various kind of technical support, foremost Andreas Johansson, Erik Jonsson, Stefan Molund and Martin Nilsson. I also ex-

press my gratitude to all the people involved in administrative support, especially Pia Bruhn and Anne Andersson.

Last but not the least, I am deeply indebted to my family. Words cannot express how grateful I am to my parents, my wife, my daughter and my siblings for always been supportive to my work, studies, and research. Although I spent nights and weekends at work, my wife, my better half, always supported me, gave me courage, and made our life full of happiness and love. Finally, I thank all my friends in Sweden and Egypt for their trust and support.

Ahmed Mahmoud

### List of Abbreviations

**ADC** Analog to Digital Converter

**BB** Bang-Bang

**BBPD** Bang-Bang Phase Detector

**BPF** Band Pass Filter

**CAD** Computer-Aided Design

CMOS Complementary Metal Oxide Semiconductor

**CP** Charge Pump

**CSI** Current-Starved Inverter

CT Continuous-Time

**DAC** Digital to Analog Converter

**DAFS** Direct Analog Frequency Synthesizer

**DCO** Digitally Controlled Oscillator

**DDFS** Direct Digital Frequency Synthesizer

**DLF** Digital Loop Filter

DNL Differential Non-LinearityDPLL Digital Phase Locked Loop

**DR** Dynamic Range

**DSP** Digital Signal Processor

**DT** Discrete-Time

**DTC** Digital-to-Time Converter

**EM** Electromagnetic

FAC Frequency Acquisition Controller

FCW Frequency Control Word FDD Frequency Division Duplex

**FGRO** Fast-Delay GRO

FM Frequency Modulation

**FOM** Figure-of-Merit

GRO Gated Ring Oscillator

GVTDC Gated-Vernier TDC

HB High-BandHPF High Pass Filter

IC Integrated Circuit

IF Intermediate Frequency

IIR Infinite Impulse Register

IMD Intermodulation Distortion

INL Integral Non-Linearity

ISF Impulse Sensitivity Function

LB Low-Band

LBR Loop Bandwidth Regulation

LC Inductor-Capacitor

LDO Low-Drop-Output Regulator

LF Loop Filter

**LFSR** Linear Feedback Shift Register

LMS

Least Mean Square

LNA

Low Noise Amplifier

LO

Local Oscillator

LPF

Low Pass Filter

LSB

Least Significant Bit

LTE-A Long Term Evolution-Advanced

**LTV** Linear Time Variant

MASH Multi-stAge noise SHaping

MIM Metal-Insulator-Metal

MMD Multi-Modulus Divider

MOM Metal-Oxide-Metal

MUX Multiplexer

NCO Numerically Controlled Oscillator

NTF Noise Transfer Function

PA Power Amplifier

PD Phase Detector

PFD Phase Frequency Detector

PI Proportional-Integral

PLL Phase Locked Loop

PSD Power Spectral Density

PSS Periodic Steady State

**PVT** Process, Voltage and Temperature

**RF** Radio Frequency

Rx Receiver

**SCI** Shunt-Capacitor Inverter

**SGRO** Slow-Delay GRO

**STF** Signal Transfer Function

**TA** Time Amplifier

TDC Time to Digital Converter TDD Time Division Duplex

TR Tuning Range

Tx Transmitter

**UTBB FD-SOI** Ultra-Thin Body and Buried Oxide Fully Depleted Silicon

on Insulator

VCO Voltage Controlled Oscillator

# List of Figures

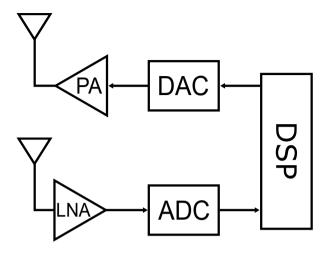

| 2.1  | ideal transceiver architecture envisioned in [1]      | Ö  |

|------|-------------------------------------------------------|----|

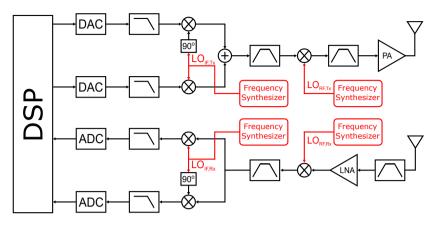

| 2.2  | Superheterodyne transceiver architecture              | 9  |

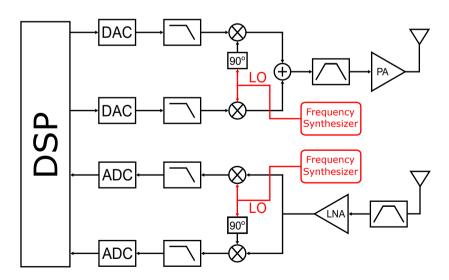

| 2.3  | Homodyne transceiver architecture                     | 10 |

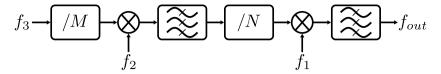

| 2.4  | Direct analog frequency synthesizer [2]               | 11 |

| 2.5  | Direct digital frequency synthesizer [3]              | 12 |

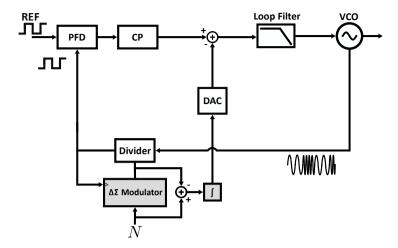

| 2.6  | Fractional-N CP-PLL                                   | 13 |

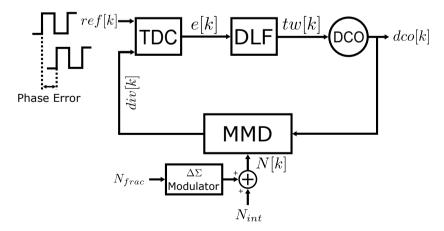

| 2.7  | Fractional-N DPLL                                     | 14 |

| 2.8  | The DDFS-PLL hybrid structure                         | 15 |

| 2.9  | Frequency tuning range and frequency resolution       | 16 |

| 2.10 | Output Spectrum of both an ideal and noisy oscillator | 17 |

| 2.11 | Typical oscillator phase noise                        | 18 |

| 2.12 | Effect of LO phase noise on RF receiver               | 19 |

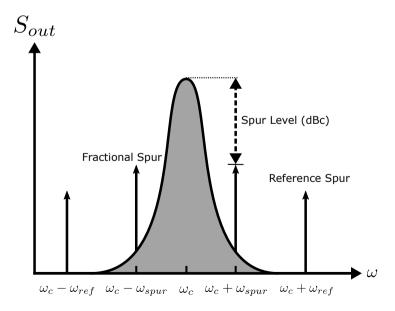

| 2.13 | LO spectrum with spurs                                | 20 |

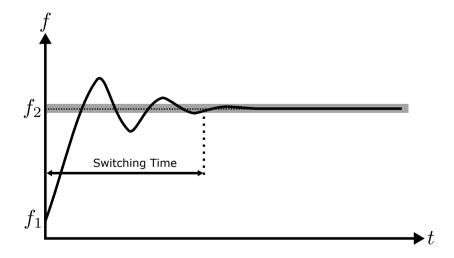

| 2.14 | Settling time example of a frequency synthesizer [3]  | 21 |

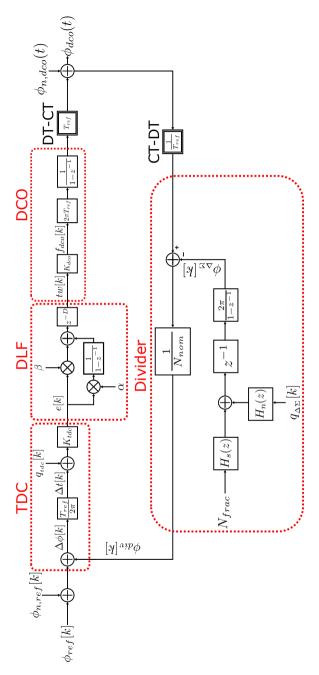

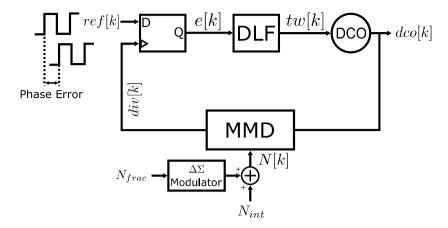

| 3.1  | TDC-based DPLL basic block diagram                    | 24 |

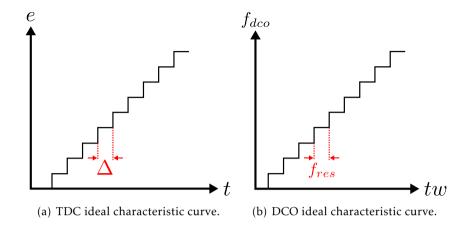

| 3.2  | TDC and DCO ideal characteristic curves               | 25 |

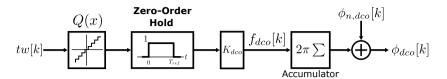

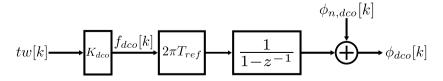

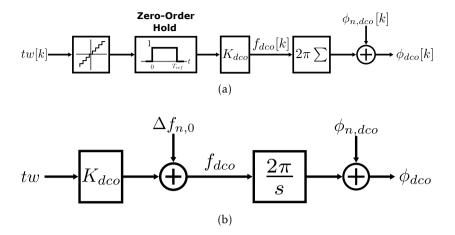

| 3.3  | DCO discrete-time model                               | 26 |

| 3.4  | DCO <i>z</i> -domain simplified model                 | 26 |

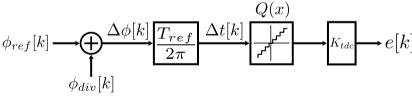

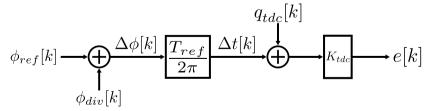

| 3.5  | TDC models                                            | 27 |

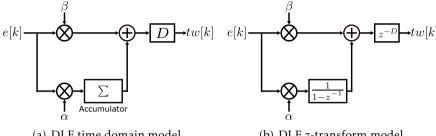

| 3.6   | DLF models                                                                                                                                                                                              | 29  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

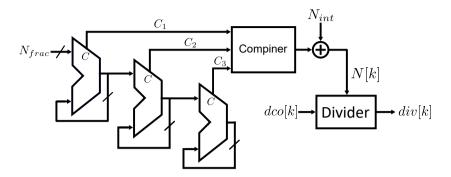

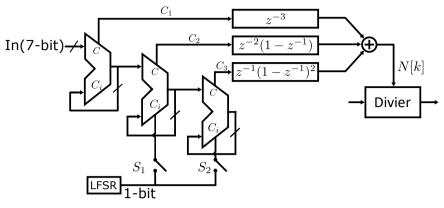

| 3.7   | Digital MASH 1.1.1 $\Delta\Sigma$ modulator                                                                                                                                                             | 30  |

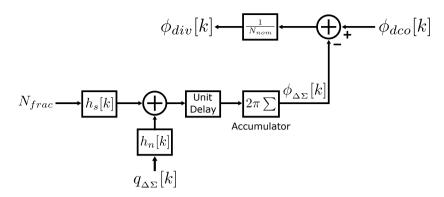

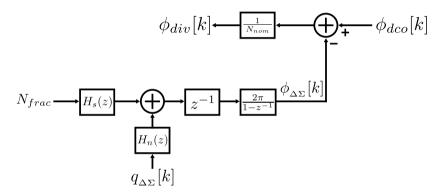

| 3.8   | Divider and $\Delta\Sigma$ modulator time domain model                                                                                                                                                  | 31  |

| 3.9   | Divider and $\Delta\Sigma$ modulator z-domain model                                                                                                                                                     | 31  |

| 3.10  | TDC-based DPLL z-domain model                                                                                                                                                                           | 32  |

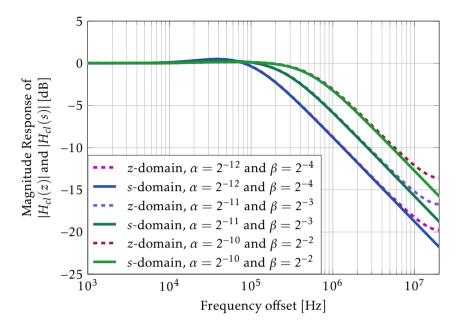

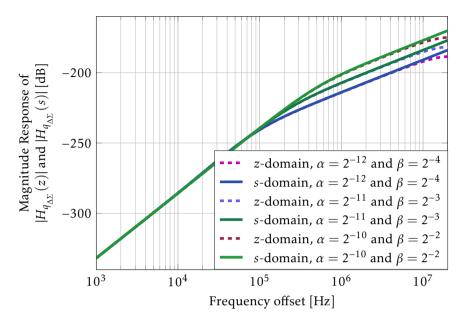

| 3.11  | Matlab simulations showing the magnitude responses of the closed-loop transfer function in z-domain $ H_{cl}(z) $ and also in s-domain $ H_{cl}(s) $ for three different values of $\alpha$ and $\beta$ | 34  |

| 3 1 2 | Matlab simulations showing the magnitude responses of the                                                                                                                                               | 0 1 |

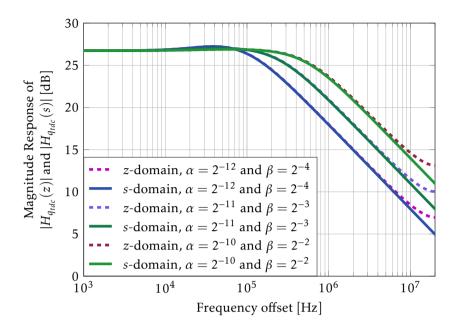

| 0.12  | TDC noise transfer function $ H_{q_{tdc}}(z) $ in z-domain and $ H_{q_{tdc}}(s) $ in s-domain for three different values of $\alpha$ and $\beta$                                                        | 36  |

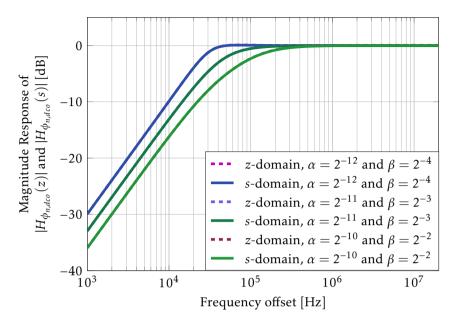

| 3.13  | Matlab simulations showing the magnitude responses of the                                                                                                                                               |     |

|       | DCO noise transfer function $ H_{\phi_{n,dco}}(z) $ in z-domain and $ H_{\phi_{n,dco}}(s) $                                                                                                             |     |

|       | in <i>s</i> -domain for three different values of $\alpha$ and $\beta$                                                                                                                                  | 37  |

| 3.14  | Matlab simulations showing the magnitude responses of the                                                                                                                                               |     |

|       | $\Delta\Sigma$ modulator noise transfer function $ H_{q_{\Delta\Sigma}}(z) $ in z-domain and                                                                                                            |     |

|       | $ H_{q_{\Lambda\Sigma}}(s) $ in s-domain for three different values of $\alpha$ and $\beta$                                                                                                             | 38  |

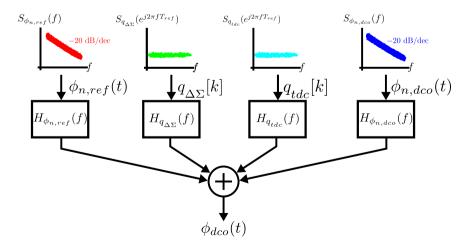

| 3.15  | Phase noise calculation model                                                                                                                                                                           | 39  |

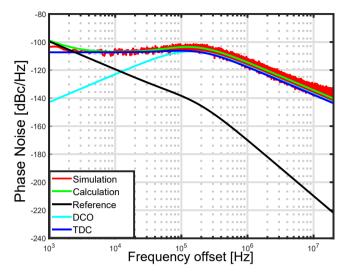

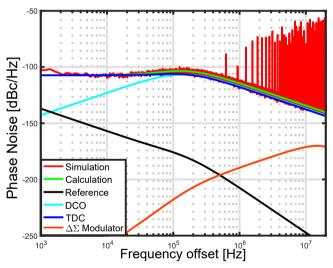

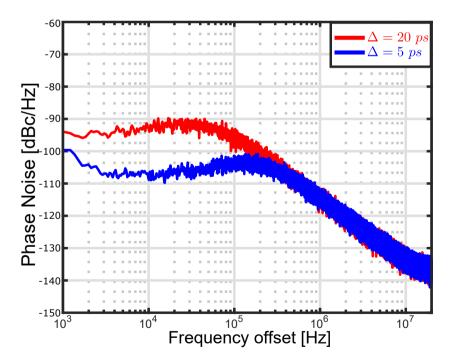

| 3.16  | Simulated TDC-based DPLL phase noise for integer and frac-                                                                                                                                              |     |

|       | tional channels                                                                                                                                                                                         | 41  |

| 3.17  | Phase noise performance for different TDC resolution and band-                                                                                                                                          |     |

|       | widths                                                                                                                                                                                                  | 42  |

| 3.18  | DPLL employing a BBPD                                                                                                                                                                                   | 43  |

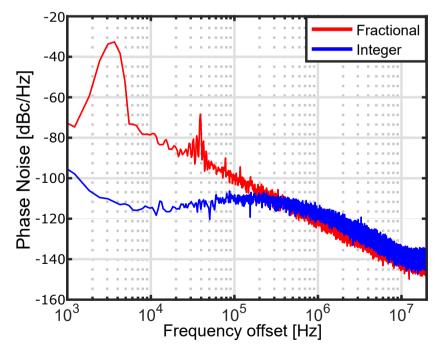

|       | BB-based DPLL z-domain model                                                                                                                                                                            | 44  |

| 3.20  | Matlab simulation of a BB-based DPLL when an integer chan-                                                                                                                                              |     |

|       | nel and a fractional channel are synthesized                                                                                                                                                            | 46  |

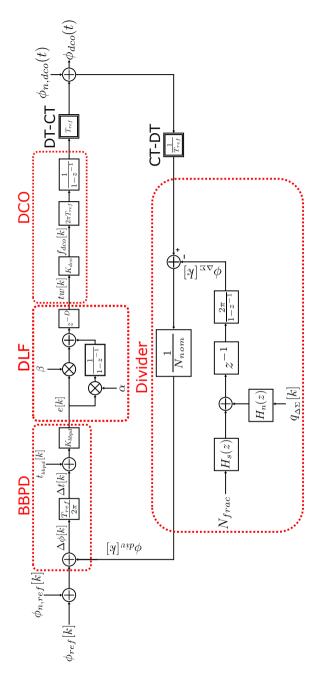

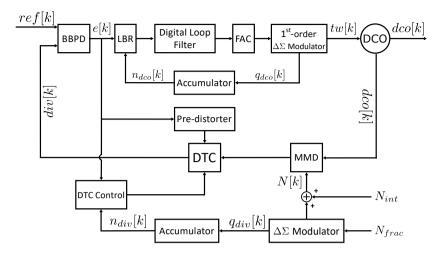

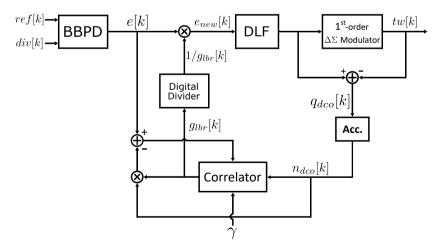

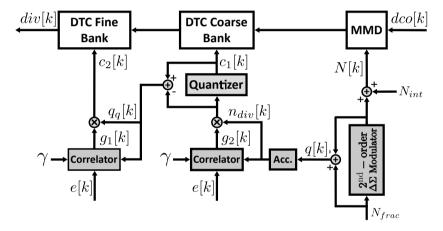

|       | BB-based DPLL complete block diagram                                                                                                                                                                    | 47  |

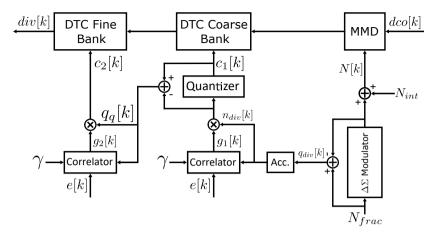

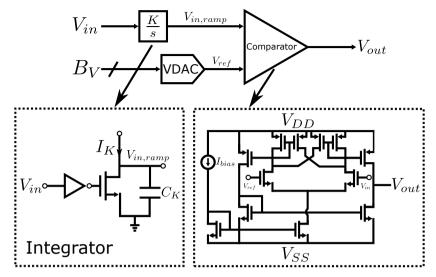

|       | Block schematic view of the DTC control                                                                                                                                                                 | 48  |

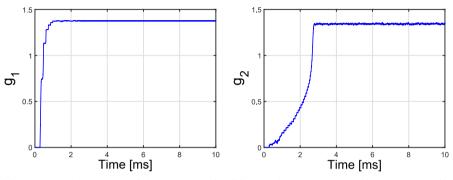

|       | Simulated transients of the LMS coefficients                                                                                                                                                            | 49  |

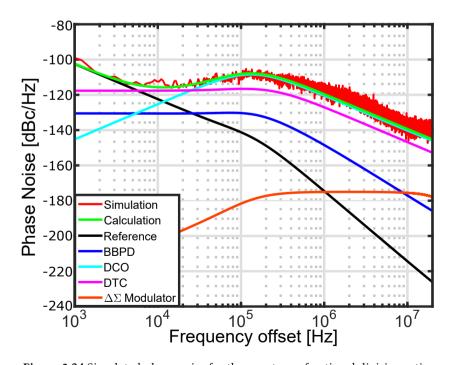

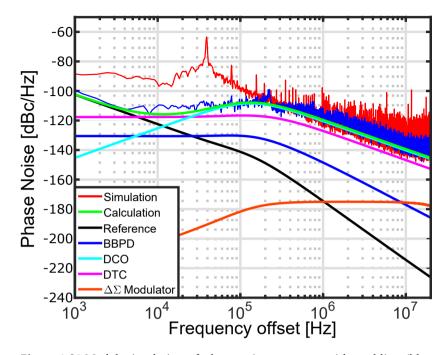

|       | Simulated phase noise for the worst case fractional division ratio.                                                                                                                                     | 49  |

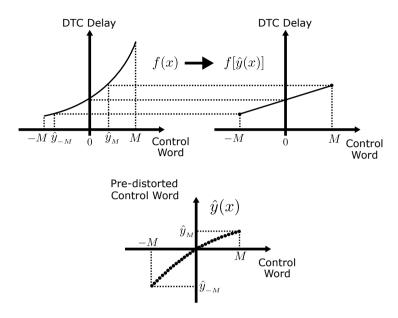

|       | Ideal pre-distortion concept [4]                                                                                                                                                                        | 51  |

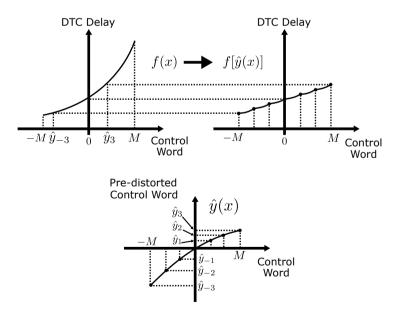

|       | Pre-distortion based piece-wise-linear concept [4]                                                                                                                                                      | 51  |

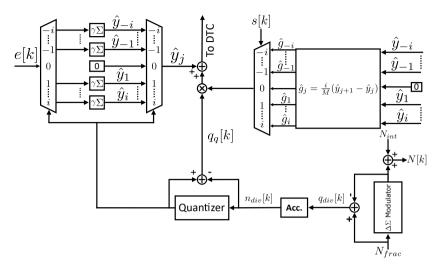

|       | Block schematic view of the pre-distorter [4]                                                                                                                                                           | 52  |

| 3.28  | Matlab simulation of phase noise spectrum with enabling (blue                                                                                                                                           |     |

|       | , , ,                                                                                                                                                                                                   | 53  |

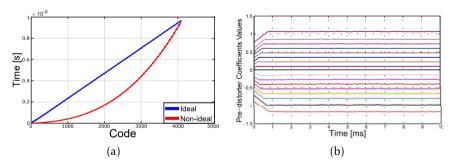

| 3.29  | (a) Ideal (blue line) and non-ideal (red line) DTC characteristic                                                                                                                                       |     |

|       | (b) Simulated transient of the pr-distorter coefficients                                                                                                                                                | 53  |

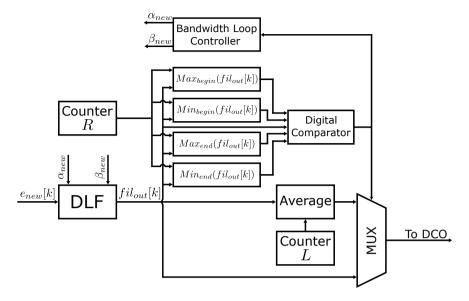

| 3.30  | LBR schematic [5]                                                                                                                                                                                       | 54  |

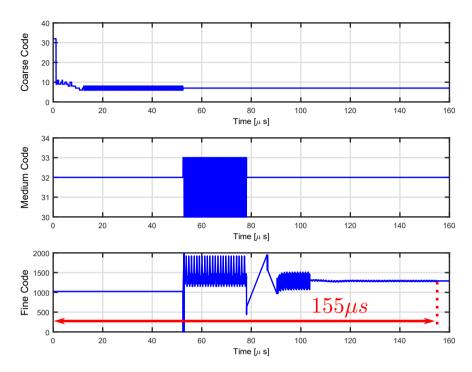

| 3.31  | Proposed FAC scheme                                                                                                                                                                                     | 55  |

| 3.32  | Simulation plots demonstrating the acquisition behavior of three                                                                                                                                        |     |

|       | DCO banks                                                                                                                                                                                               | 56  |

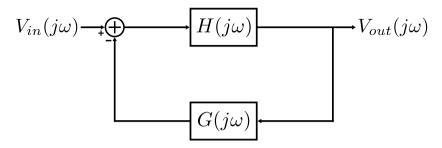

| 4.1  | Feedback network                                                                 | 58 |

|------|----------------------------------------------------------------------------------|----|

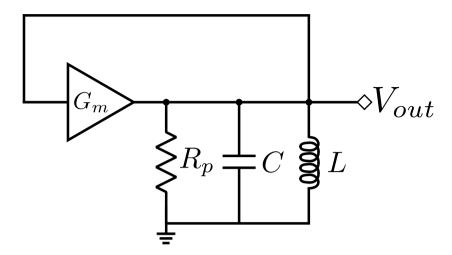

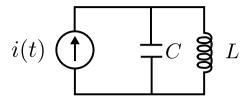

| 4.2  | LC oscillator negative resistance model                                          | 59 |

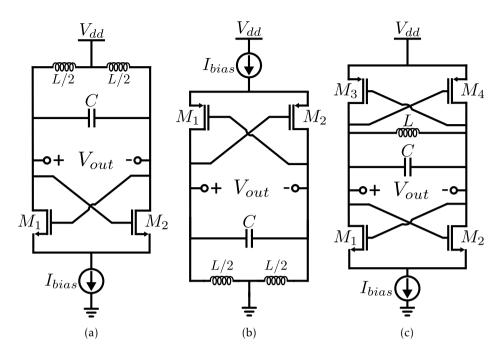

| 4.3  | Simplified circuits schematic of cross-coupled differential pair                 |    |

|      | architectures for a) The NMOS-only architecture b) The PMOS-                     |    |

|      | only architecture and c) The CMOS architecture                                   | 61 |

| 4.4  | Current noise impulse model [6]                                                  | 62 |

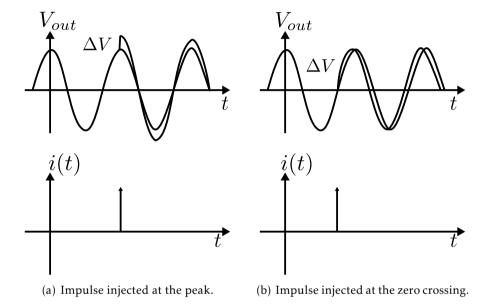

| 4.5  | impulse injected at different times [6]                                          | 62 |

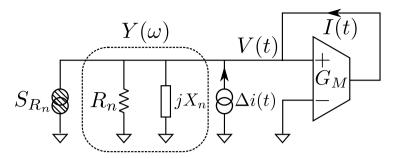

| 4.6  | Basic schematic view of the transconductor-based oscillator [7].                 | 64 |

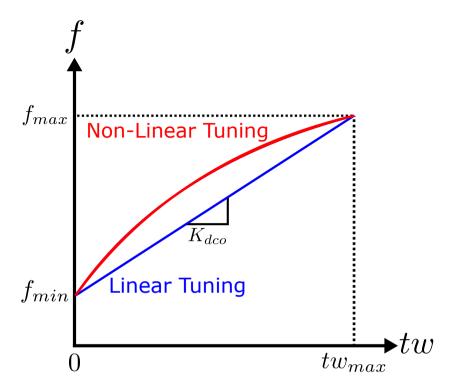

| 4.7  | DCO tuning curves                                                                | 66 |

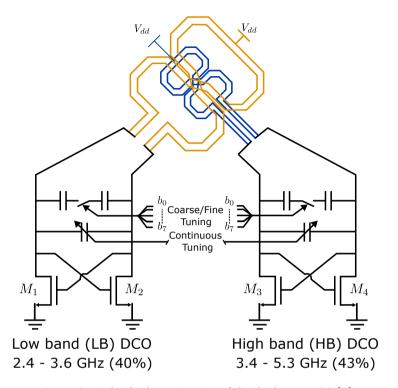

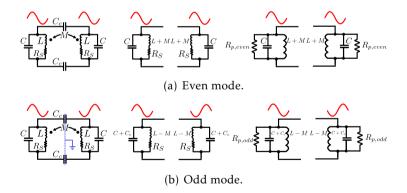

| 4.8  | Hybrid schematic view of the dual-core DCO [8]                                   | 68 |

| 4.9  | The transformer-based DCO architecture proposed in [9]                           | 69 |

| 4.10 | The two resonant modes of the LC resonator [9]                                   | 69 |

| 4.11 | (left) primary circuits; (middle) secondary circuit; (right) trans-              |    |

|      | former implementing the two-step variable inductance [10]                        | 71 |

| 4.12 | When the switch is open, no current is flowing across the sec-                   |    |

|      | ondary circuit [10]                                                              | 71 |

| 4.13 | Circuit schematic of a mode-switching DCO [11]                                   | 72 |

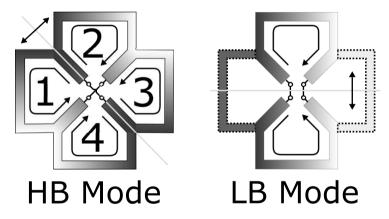

| 4.14 | The two modes of the mode-switching DCO [11]                                     | 72 |

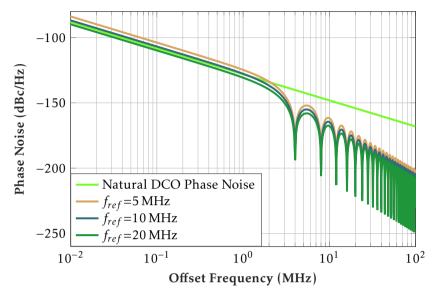

| 4.15 | DCO quantization noise model [12]                                                | 74 |

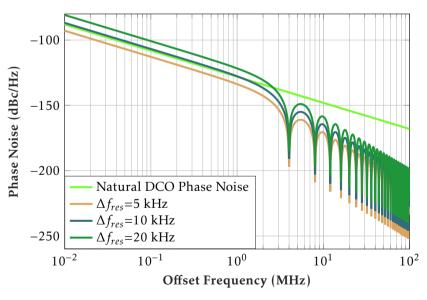

| 4.16 | Matlab simulations showing the effect of changing $f_{ref}$ and $\Delta f_{res}$ |    |

|      | on the DCO quantization-induced phase noise                                      | 75 |

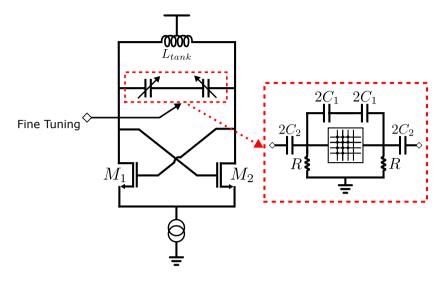

| 4.17 |                                                                                  | 76 |

| 4.18 | Capacitively degenerated DCO scheme [14]                                         | 77 |

| 4.19 | Capacitively degenerated DCO equivalent circuit [14]                             | 77 |

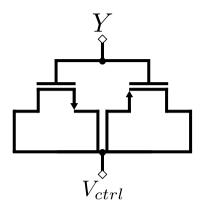

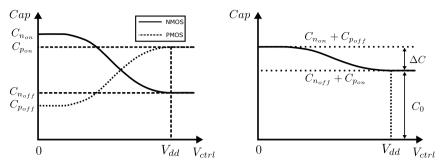

| 4.20 | Simplified model of the varactor composed of NMOS and PMOS                       |    |

|      | pair [15]                                                                        | 78 |

| 4.21 | C-V characteristics [15]                                                         | 79 |

| 4.22 | Simplified model with C-V characteristics [16]                                   | 79 |

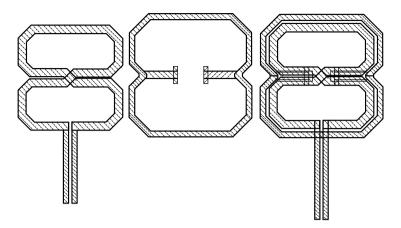

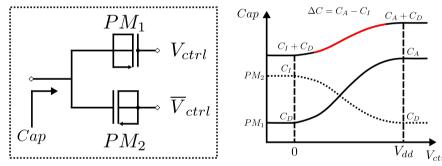

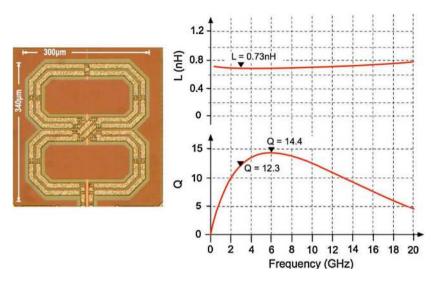

| 4.23 | Top view a) 0.73 nH 8-shaped inductor, b) 3 nH O-shaped in-                      |    |

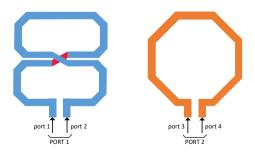

|      | ductor and c) 0.73 nH O-shaped inductor                                          | 81 |

| 4.24 | Ports in ADS momentum simulation                                                 | 81 |

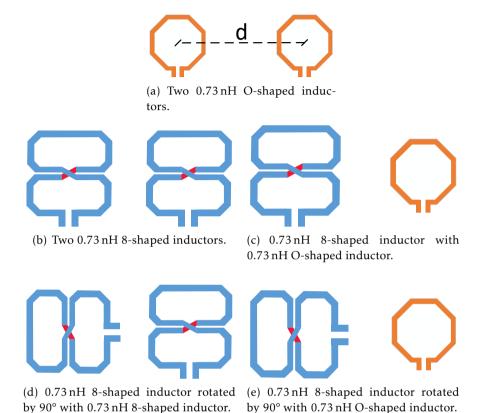

| 4.25 | First configuration                                                              | 82 |

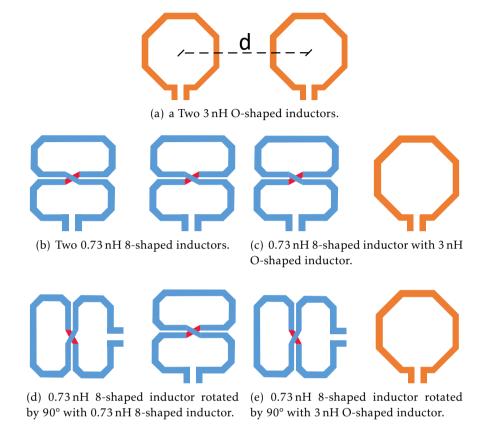

| 4.26 | Second configuration                                                             | 83 |

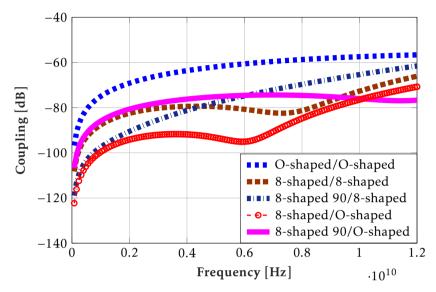

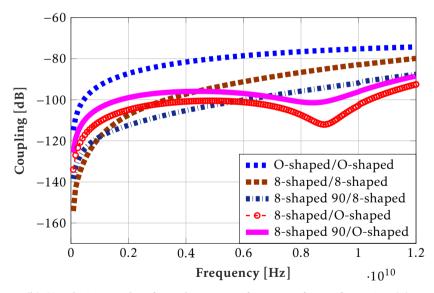

| 4.27 | Simulation results of coupling versus frequency for configura-                   |    |

|      | tion (A) and (B)                                                                 | 85 |

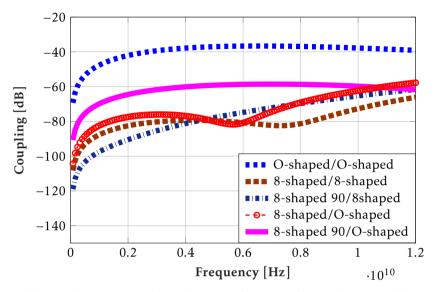

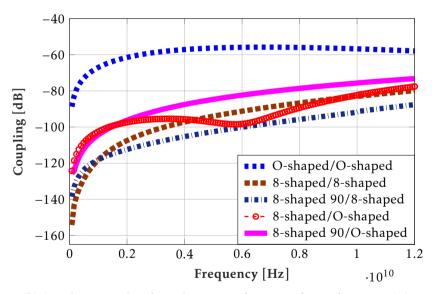

| 4.28 | Simulation results of coupling versus frequency for configura-                   |    |

|      | tion (C) and (D)                                                                 | 86 |

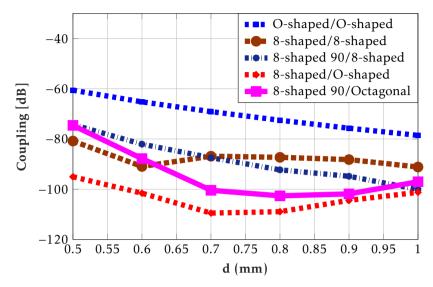

| 4.29 | Simulation results of coupling versus separation distance (d)                    |    |

|      | for configurations (A) and (C). $\dots$                                          | 87 |

|      |                                                                                  |    |

| 5.1  | Basis of time to digital conversion                                              | 90 |

| 5.2  | TDC conceptual idea [17]                                                         | 90 |

| 5.3  | TDC ideal and non-ideal curves with gain error, offset error,           |

|------|-------------------------------------------------------------------------|

|      | DNL and INL examples                                                    |

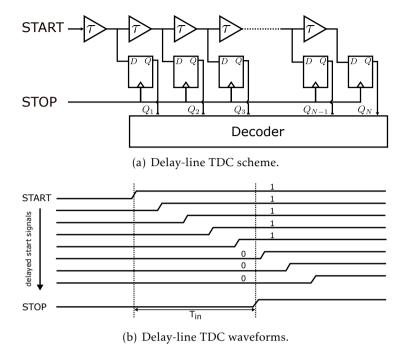

| 5.4  | Delay-line TDC scheme and waveforms 95                                  |

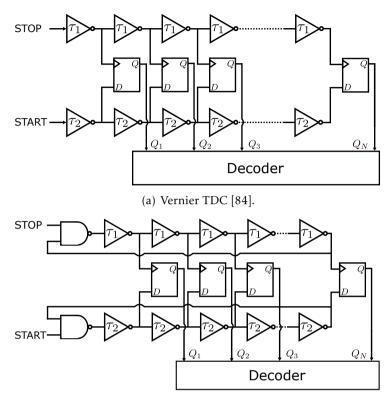

| 5.5  | TDC-based Vernier method                                                |

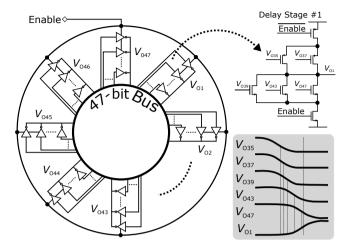

| 5.6  | GRO-TDC scheme and associated signals [18] 97                           |

| 5.7  | Multipath GRO-TDC [19]                                                  |

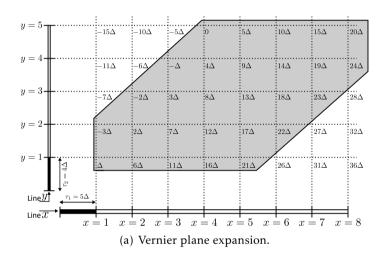

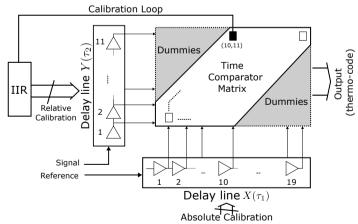

| 5.8  | Vernier plane expansion with 2D Vernier TDC implementation              |

|      | [20]                                                                    |

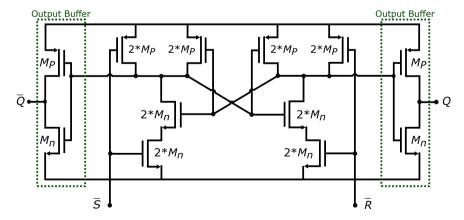

| 5.9  | Time comparator schematic [20]                                          |

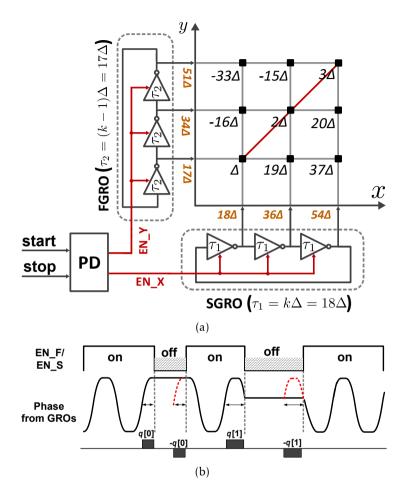

| 5.10 | a) The simplified 2-D GVTDC and b) GRO operation 101                    |

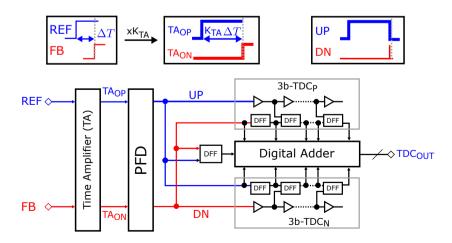

| 5.11 | TA-based TDC [21]102                                                    |

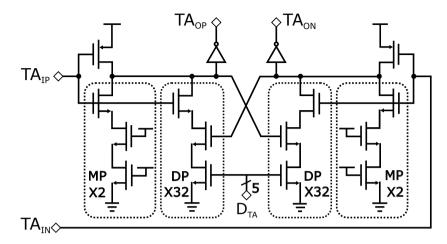

| 5.12 | Schematic of the fully-symmetric TA [21]                                |

| 5.13 | DTC transfer function [22]                                              |

|      | An SCI schematic [23]                                                   |

|      | An example of CSI architecture [24]                                     |

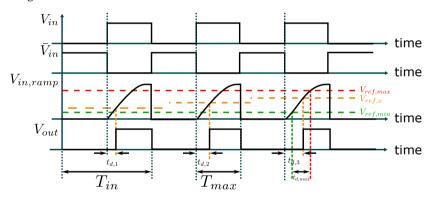

| 5.16 | Voltage-comparator based DTC and associated waveforms [25]. 106         |

| 5.17 |                                                                         |

|      | nals $V_A$ and $V_B$ , where the interpolated phases $(V_1 - V_3)$ have |

|      | the same slope for the part within the two dashed lines [26] 107        |

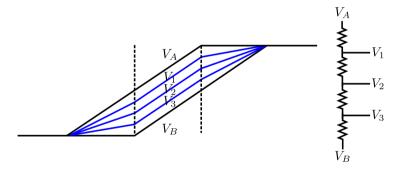

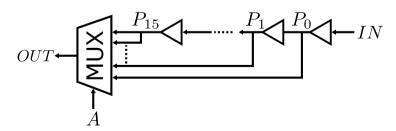

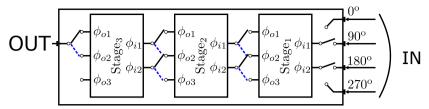

|      | Phase interpolator architecture [27]                                    |

| 5.19 | Block diagram and circuit schematic of the pipelined phase in-          |

|      | terpolator [28]                                                         |

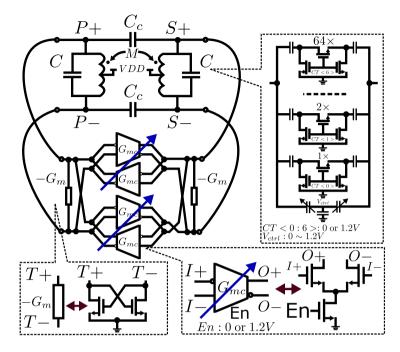

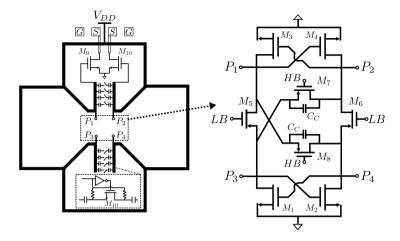

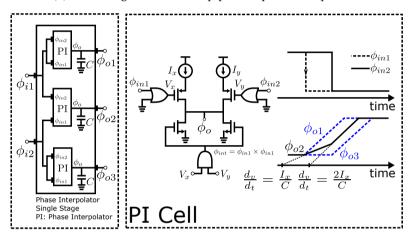

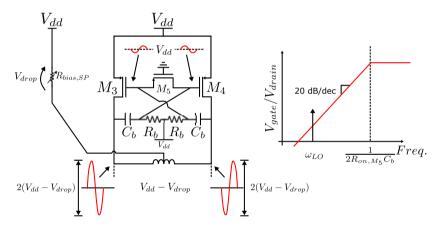

| 6.1  | Simplified schematic of the VCO, whose active core can be con-          |

|      | figured either as a single cross-coupled pair (SP, on the left), or     |

|      | as a complementary cross-coupled pair (CP, on the right) 110            |

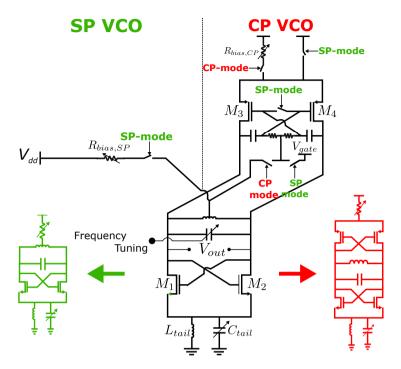

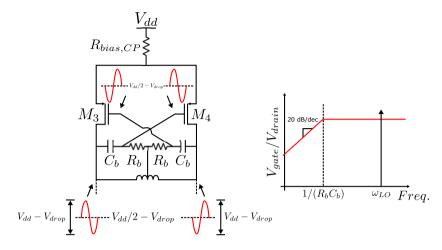

| 6.2  | Bias circuit in CP mode [29]                                            |

| 6.3  | Bias circuit in SP mode [29]                                            |

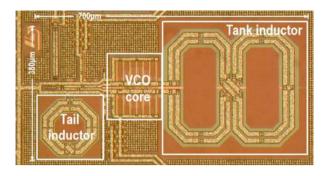

| 6.4  | Die photograph of the VCO                                               |

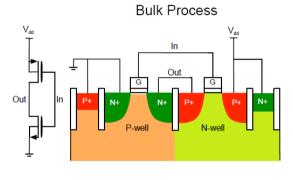

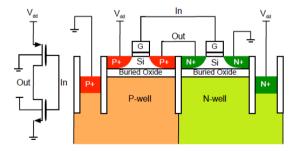

| 6.5  | In the 28 nm UTBB FD-SOI CMOS process used, it is possible              |

|      | to forward-bias the NMOS/PMOS body to obtain low- $V_T$ de-             |

|      | vices. Notice that in this case the well types are flipped, com-        |

|      | pared to a Bulk process or to the normal- $V_T$ devices in the same     |

|      | 28 nm UTBB FD-SOI process, to avoid forward-biasing of the P-           |

|      | well/N-well diode [30]                                                  |

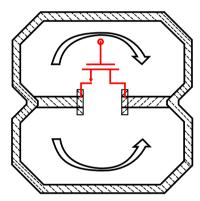

| 6.6  | The 8-shaped inductor, built with metal layers of standard thick-       |

|      | ness                                                                    |

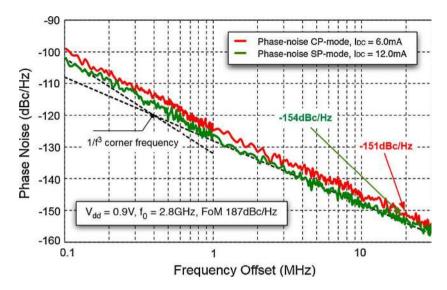

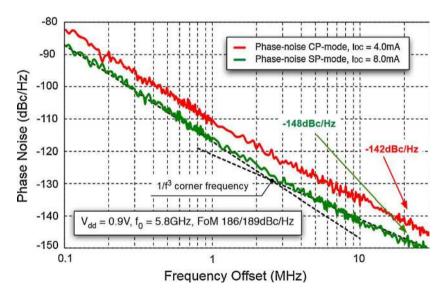

| 6.7  | Phase noise measurements at the lowest oscillation frequency 114        |

| 6.8  | Phase noise measurements at the highest oscillation frequency $114$     |

| 6.9  | Block diagram of the DPLL                                               |

| 6.10 | Conventional fractional-N analog PLL with $\Delta\Sigma$ quantization   |

|      | noise cancellation scheme                                               |

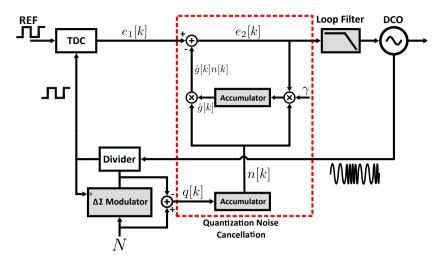

| 5.11 | DPLL with $\Delta\Sigma$ quantization noise cancellation scheme 118                   |

|------|---------------------------------------------------------------------------------------|

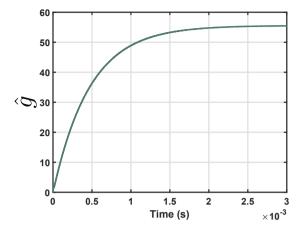

| 5.12 | Simulated LMS coefficient                                                             |

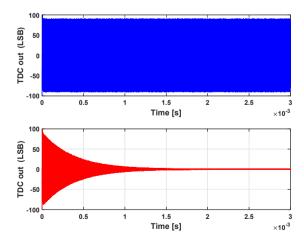

| 5.13 | The output of TDC with and without enabling $\Delta\Sigma$ quantization               |

|      | noise cancellation circuit                                                            |

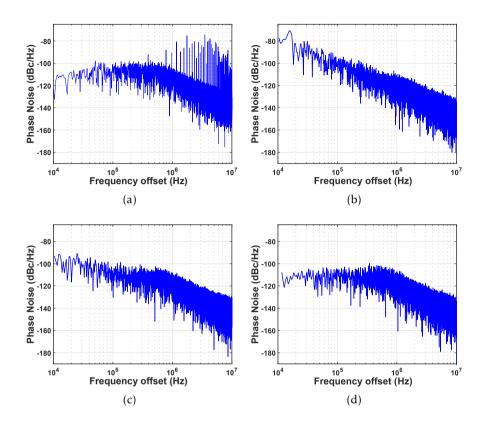

| 5.14 | a) Simulated phase noise of DPLL without enabling $\Delta\Sigma$ quan-                |

|      | tization noise cancellation, b) Simulated phase noise of DPLL                         |

|      | with enabling $\Delta\Sigma$ quantization noise cancellation and $\gamma = 10^{-2}$ , |

|      | c) Simulated phase noise of DPLL with enabling $\Delta\Sigma$ quantiza-               |

|      | tion noise cancellation and $\gamma = 10^{-3}$ , and d) Simulated phase               |

|      | noise of DPLL with enabling $\Delta\Sigma$ quantization noise cancella-               |

|      | tion and $\gamma = 10^{-4}$                                                           |

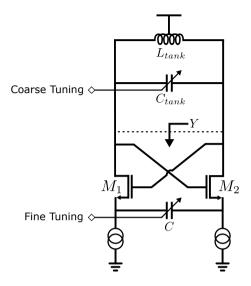

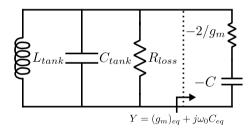

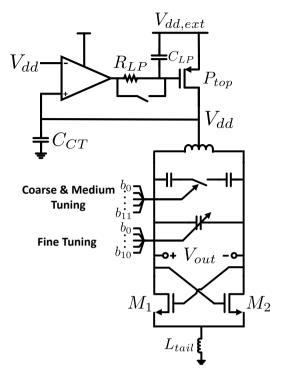

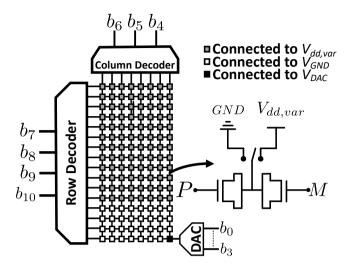

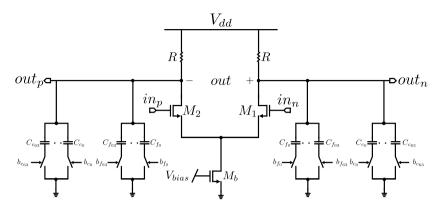

| 5.15 | Schematic view of the class-D DCO                                                     |

|      | Fine tuning bank of the DCO                                                           |

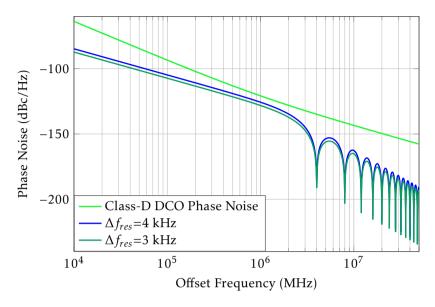

| 5.17 | Matlab simulations showing the phase noise of the class-D DCO                         |

|      | with the DCO quantization-induced phase noise when $\Delta f_{res}$ =4                |

|      | kHz and 3 kHz                                                                         |

| 5.18 | MASH 1-1-1 $\Delta\Sigma$ modulator diagram and simulated PSD 124                     |

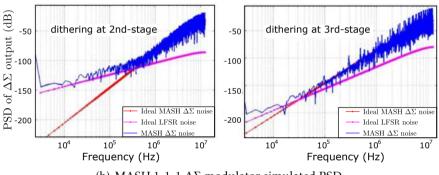

| 5.19 | Multiple-mode frequency divider                                                       |

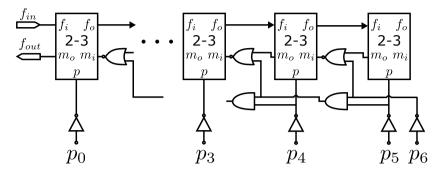

| 5.20 | DLF and IIR details                                                                   |

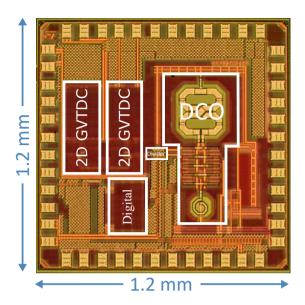

| 5.21 | DPLL chip layout                                                                      |

| 5.22 | Simulated DPLL phase noise at 3.5 GHz with a 50-MHz refer-                            |

|      | ence clock with and without enabling $\Delta\Sigma$ quantization noise                |

|      | cancellation                                                                          |

| 5.23 | Overall DPLL architecture                                                             |

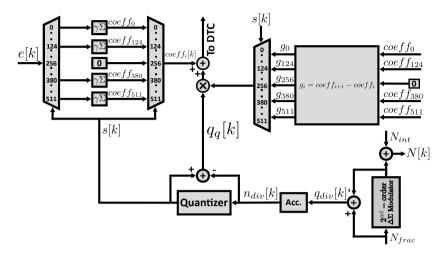

| 5.24 | DTC implementation                                                                    |

| 5.25 | Block schematic view of DTC and fractional divider 130                                |

| 5.26 | Block schematic view of the pre-distorter                                             |

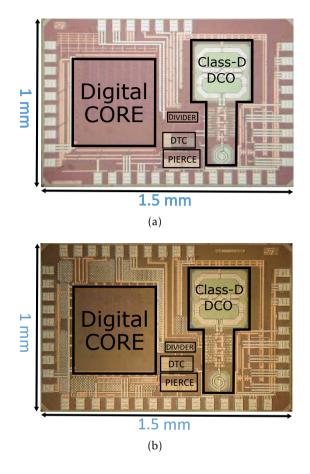

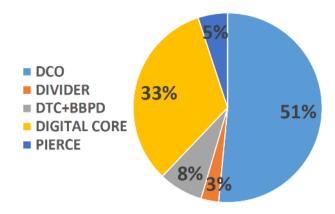

| 5.27 | The fabricated two prototypes die photographs                                         |

| 5.28 | Power consumption in the DPLL                                                         |

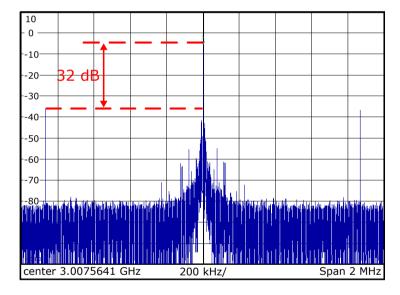

| 5.29 | DPLL spectrum (2-MHz span) for a 3.0-GHz carrier when spur                            |

|      | cancellation is disabled                                                              |

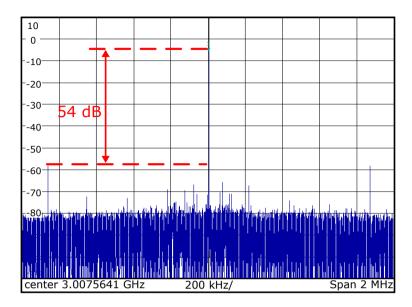

| 5.30 | DPLL spectrum (2-MHz span) for a 3.0-GHz carrier when DTC                             |

|      | pre-distortion is disabled                                                            |

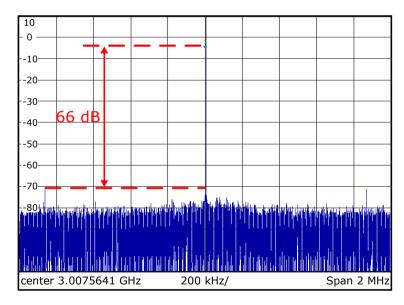

| 5.31 | DPLL spectrum (2-MHz span) for a 3.0-GHz carrier when nom-                            |

|      | inal operation is enabled                                                             |

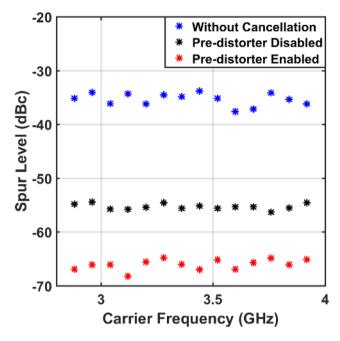

|      | In-band fractional spur level across the DPLL tuning range 135                        |

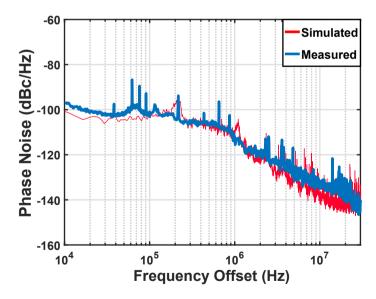

| 5.33 | Phase noise plot at 3.0 GHz                                                           |

# List of Tables

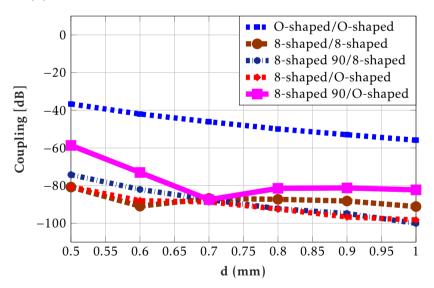

| 4.1 | Coupling comparison of configurations (A), (B), (C) and (D) at 6 GHz |

|-----|----------------------------------------------------------------------|

| 5.1 | Comparison with state of the art VCOs having a tuning range          |

|     | larger than one octave                                               |

| 5.2 | Comparison with state of the art DPLLs                               |

| 5.3 | Performance summary and comparison                                   |

### Introduction

#### 1.1 MOTIVATION

Over the last few decades, wireless communication has become increasingly essential in everyday life. The tremendous growth of wireless systems can be traced back to the prodigious development in semiconductor technology, where the aggressive scaling of Complementary Metal Oxide Semiconductor (CMOS) processes makes it possible to integrate hugely complex systems on a single silicon chip of minuscule dimensions (often much smaller than 1 cm<sup>2</sup>). This unrelenting CMOS scaling has led to numerous innovations in both digital and analog Integrated Circuit (IC) design, which are largely responsible for the unprecedented market growth of wireless communication. However, for an improved design robustness, the digital approach is preferred, while analog IC design is becoming increasingly difficult, as the available voltage headroom is constantly shrinking. Therefore, digital intensive solutions of traditionally analog components are needed. Moreover, a digital intensive approach provides additional benefits in terms of improved reconfigurability and programmability, better testability, lower variability, optimized power consumption and area, higher degree of integration, and straightforward use of automated Computer-Aided Design (CAD) tools. The above reasons are of imperative importance for mobile wireless communication, where especially low cost, small area and low power designs are mandatory.

Traditionally, the Radio Frequency (RF) functions for wireless communication systems have been realized with analog intensive circuitry. Porting such analog functions to the digital domain, however, is not a simple operation. While the functionality of the system must be improved (or, at least, remain the same), novel problems may arise; nevertheless, some digital intensive RF solutions have already been demonstrated. An important and acclaimed exam-

1

2 Introduction

ple is the Digital Phase Locked Loop (DPLL) [31] [32]. The DPLL approach has become very attractive in recent years, as it is capable of drawing much benefit from the downscaling of CMOS processes, which is not the case for the traditional analog Phase Locked Loop (PLL). In a DPLL, analog building blocks are either replaced by purely digital counterparts, such as the Digital Loop Filter (DLF), or by digitally controlled subsystems, such as the Digitally Controlled Oscillator (DCO). These replacements enable the designer to evade major analog design issues, including the non-linearity of the Charge Pump (CP), large passive components in analog Low Pass Filter (LPF) in the PLL loop, current leakage in the LPF capacitor, and the various problems deriving from a low supply voltage, while, on the other side, they bring forth the typical digital IC advantages in terms of high integration level, programmability, and flexibility, as already mentioned.

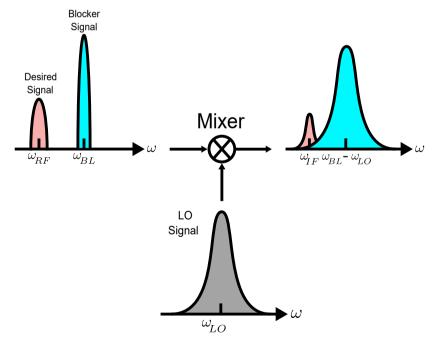

Although several DPLLs have displayed a superb performance [27][33–39], there is still a number of aspects where better techniques and design enhancements are required. Two main issues are phase noise and spurious tones (spurs) in the spectrum of the DPLL output, where a high phase noise may cause reciprocal mixing in the receiver side, which occurs when the noise on the Local Oscillator (LO) (itself derived from the DPLL output) in the radio receiver joins forces with an incoming strong disturbing signal, effectively swamping a much lower desired signal. High spurs, on the other hand, may cause Intermodulation Distortion (IMD). Furthermore, both phase noise and close-in spurs corrupt the signal-to-noise ratio of both received and transmitted signals. A third aspect is that DPLL architectures still require high levels of power consumption and large design areas, which should be both reduced to achieve long operation times and low cost. Finally, DPLLs have, to a large extent, been employed in narrowband wireless systems. With the expected requirements of wideband systems as wireless communication evolves, wideband DPLLs (and, therefore, wideband DCOs) are badly needed.

The goal of this research work has been to find and test techniques for improving different properties of the DPLL at both the architectural and the building-block level.

#### 1.2 RESEARCH CONTRIBUTION

In the course of the research work presented in this thesis, three circuits have been designed in two different CMOS processes, achieving the following results:

- 1. A DCO characterized by a reconfigurable active core with a wide tuning range, targeted for 2.8-5.8 GHz applications. In this work:

- We demonstrate that a 28 nm Ultra-Thin Body and Buried Oxide

1.2. Research Contribution

Fully Depleted Silicon on Insulator (UTBB FD-SOI) CMOS process makes it possible to realize a compact one-octave DCO based on a reconfigurable class-B active core and a single 8-shaped tank inductor, with a very good phase noise and Figure-of-Merit (FOM) performance, even though the UTBB FD-SOI process is optimized for purely low-power digital applications.

- We demonstrate that the UTBB FD-SOI CMOS process is instrumental to achieve a tuning range in excess of one octave at low power consumption

- Compared to ultra wide Tuning Range (TR) DCOs based on transformers or multiple inductors, this DCO is preferred for its comparatively easy and area-efficient design.

- The DCO adopts a re-configurable active core to save power at the lower oscillation frequencies, and to enable a trade-off between power consumption and phase noise at all frequencies.

- Interference caused by the magnetic coupling to and from the DCO inductor is greatly attenuated by resorting to an inductor in the shape of an 8. Simulations of the magnetic coupling between an 8-shaped inductor and a reference inductor show a magnetic coupling reduction as high as 44 dB, depending also on size, orientation, and shape of the interacting inductors.

- The DCO has a FOM of 186–189 dBc/Hz, depending on the oscillation frequency and the configuration of the oscillator core.

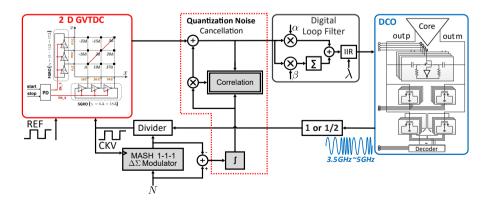

- 2. A DPLL based on a Time to Digital Converter (TDC), targeted for Long Term Evolution-Advanced (LTE-A) applications. The DPLL has a wide tuning range and uses a noise shaping 2D Gated-Vernier TDC (GVTDC) with 5.2 ps of resolution. This contribution presents:

- A wide bandwidth DPLL for LTE-A bands 33–38 that leverages a 2D GVTDC, which greatly improves the DPLL in-band phase noise by both Vernier and noise shaping techniques, while having a full period capture range. The quantization noise shaping of the TDC greatly improves the in-band phase noise. At the same time, the 2D TDC makes the DPLL able to process large phase errors almost without any deterioration on latency time.

- A high FOM class-D DCO with a fine tuning step of ~ 4 kHz, which

pushes the quantization of discrete tuning well below the oscillator

phase noise, is used.

4 Introduction

• A quantization noise cancellation based on a Least Mean Square (LMS) algorithm to cancel the  $\Delta\Sigma$  quantization noise is implemented.

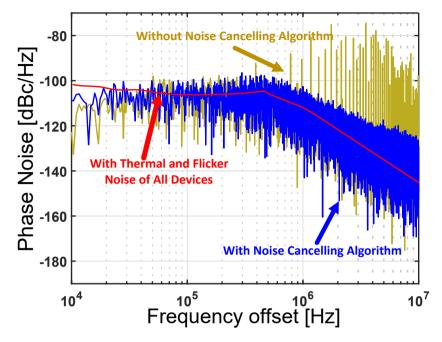

- The DPLL achieves a very good simulated phase noise of -110 dBc/Hz in-band, and of -140 dBc/Hz at 10 MHz offset, with carrier frequency of 3.5 GHz and 1 MHz DPLL bandwidth.

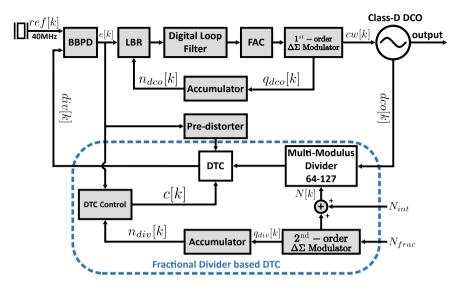

- 3. A wideband Digital-to-Time Converter (DTC) based DPLL operating from 2.8 GHz to 3.8 GHz, with an on-chip 40 MHz reference crystal oscillator is presented. In this work:

- We find the first published measurements on a DPLL employing a class-D DCO.

- The DPLL displays an excellent behavior in terms of in-band fractional spurs, which are consistently below -65 dBc across the tuning range, thanks to a number of digital correction algorithms running in the background.

- The simplified Frequency Acquisition Controller (FAC) proposed is wholly digital, requiring no additional analog blocks (e.g., coarse TDCs and RF counters) used in other DPLL designs. A fast and reliable frequency acquisition (lasting  $160~\mu s$  at most) is achieved, despite the limited capture range of the Bang-Bang Phase Detector (BBPD) used.

- The measured DPLL has a very good in-band phase noise of -102 dBc/Hz at 100 kHz offset.

Simulation and measurement results have been successfully published by the author in three journal articles and two conference papers. He is the first author in four of these publications.

#### 1.3 THESIS OUTLINE

This thesis is organized into seven chapters as follows:

**Chapter 1** presents the motivation and the outline of this work.

**Chapter 2** provides an overview of the general aspects and different architectures for wireless frequency synthesis techniques.

**Chapter 3** introduces basic background concepts for the DPLL architectures employed in this thesis.

1.3. Thesis Outline

**Chapter 4** gives the fundamental design principles of the DCO, focusing on different ways of implementing fine tuning. Digital frequency quantization and oscillator pulling are also analyzed.

- **Chapter 5** focuses on the design principles for TDCs and DTCs, exploring several popular architectures.

- **Chapter 6** discusses the fabricated circuit prototypes, with simulations and experimental results.

Chapter 7 includes a brief conclusion.

# Frequency Synthesizer Overview

#### 2.1 INTRODUCTION

The term frequency synthesizer refers to a category of systems whose objective is to generate a set of stable frequencies. From communication systems to digital circuit applications, from clock and data recovery to modulation and waveform generation, frequency synthesizer is an indispensable item in almost every IC, either wireless or wireline. In general, frequency synthesizers are devices that take one reference frequency  $(f_{ref})$ , and generate a multiple of output frequencies  $(f_{out,min} - f_{out,max})$ . Mostly, a crystal oscillator is employed for the reference frequency, due to its high stability and high spectral purity at a precise frequency.

In wireless communication systems, the frequency synthesizer is commonly serving as an LO source, where it is used as a reference oscillator for frequency translation and channel selection in a variety of up-conversion and down-conversion schemes for different transceiver architectures. Hence, it is one of the most critical modules, as it has a direct critical impact on the performance of the whole transceiver. Therefore, new designs and techniques are usually developed in order to meet the stringent requirements outlined in wireless communication standards in terms of spectral purity, frequency range, etc. along with the stringent specifications of low power consumption and low cost.

This chapter presents a brief discussion of frequency synthesis applications and highlights the high importance of frequency synthesizers for wireless communication systems. Meanwhile, some background into the types and performance metrics of frequency synthesis techniques are introduced, with emphasis on critical performance parameters.

**Figure 2.1** Ideal transceiver architecture envisioned in [1].

#### 2.2 FREQUENCY SYNTHESIZERS IN TRANSCEIVERS

A key device in any wireless communication system is the radio transceiver (amalgamation of Transmitter (Tx) and Receiver (Rx)). It is a building block that is responsible for transmitting and receiving data. Figure 2.1 shows the ideal transceiver concept envisioned in [1]. In this configuration, no frequency conversion is needed, as the Analog to Digital Converter (ADC) and Digital to Analog Converter (DAC) already operate at RF. It is a massively digitized transceiver concept that introduces a very high degree of re-configurability and programmability, since most of the work is accomplished in the digital domain. Therefore, this architecture allows for a maximum degree of flexibility through an increase in software capability. Unfortunately, this architecture is not practical in high frequency applications, as it requires unrealistic requirements for ADC and DAC in terms of very high sampling rate and dynamic range, with higher power consumption and higher cost. Furthermore, it also needs a high speed Digital Signal Processor (DSP) to have the ability to process high sampling rate signals, which comes with larger power consumption and higher cost. Thus, this type of transceiver approach is not suitable for high frequency applications.

To alleviate the previous issues, two well-known transceiver architectures are employed, which typically are classified according to the location of the Intermediate Frequency (IF) involved between the baseband and RF, whether it is a direct-conversion (zero-IF) from the baseband to the RF and vice versa (homodyne transceiver), or it is inserted between the baseband and the RF (superheterodyne transceiver).

Figure 2.2 Superheterodyne transceiver architecture.

#### 2.2.1 SUPERHETERODYNE TRANSCEIVER

Figure 2.2 shows the superheterodyne transceiver architecture. It is characterized by two steps frequency conversion: down-conversion from RF to IF and then to baseband, and the contrary in up-conversion, from baseband to IF then to RF. In the transmitter side, the digital baseband signal is passed through DACs to generate the appropriate analog baseband signals. These signals are then passed through LPFs to reject any high frequency aliasing components caused by the DACs. Thereafter, these signals are mixed up with  $LO_{IF,Tx}$  and up-converted to the IF region, where they are passed through a Band Pass Filter (BPF) to further suppress any unwanted signals. The filtered IF signals are combined together and up-converted to the RF region by  $LO_{RF,Tx}$ , where it is filtered again and then amplified by a Power Amplifier (PA) and fed to the antenna.

Likewise, in the receiver side, the RF signal from the antenna is first filtered by an RF BPF to attenuate any undesired out-of-band blockers. The signal is then amplified by a Low Noise Amplifier (LNA), which amplifies the signal with relatively low noise contribution. The amplified signal is down-converted firstly to IF by  $LO_{RF,Rx}$ , then to baseband by  $LO_{IF,Rx}$ , where it is converted again to the digital domain through ADCs, where additional signal processing is performed. In general, four frequency synthesizers are required: two for the Tx and the other two for the Rx if Frequency Division Duplex (FDD) scheme is adopted, while two frequency synthesizers can be used for both Tx and Rx in case of Time Division Duplex (TDD) scheme.

Superheterodyne transceiver, especially the receiver side, is a very popular architecture in wireless communication systems for its ability to deliver very good performance, and it was the main choice in wireless systems for decades.

Two main advantages single out superheterodyne architectures over other architectures. The first advantage is the low impact of LO leakage, as a result of using two-step frequency conversion. The second one is the high capability of the receiver to suppress undesired signals, which increases the receiver dynamic range, sensitivity and selectivity. However, superheterodyne receivers also exhibit significant drawbacks. One of the biggest cons is the need of high selectivity BPFs to adequately filter out unwanted image and interference signals, which makes these filters hard to be integrated. Discrete components are used instead. Consequently, more discrete components are directly translated to higher cost, higher power consumption, larger area and higher architecture complexity.

#### 2.2.2 HOMODYNE TRANSCEIVER

The homodyne transceiver architecture is shown in Figure 2.3. This architecture is characterized by a one-step frequency translation: either up-conversion directly from baseband to RF on the Tx side, or down-conversion from RF to baseband on the Rx side. Hence, this architecture is also termed as a direct-conversion or a zero-IF transceiver. The homodyne architecture offers a higher degree of integrability, where high cost IF filters are eliminated, since no image problem exists, and then the cost and size of the overall transceiver are consequently reduced. Moreover, it consumes less power than the superheterodyne transceiver, due to only one frequency conversion is needed.

On the other hand, the performance of a homodyne transceiver is limited

Figure 2.3 Homodyne transceiver architecture.

Figure 2.4 Direct analog frequency synthesizer [2].

by two main aspects. Firstly, it requires very high degree of matching between the quadrature paths, as any small mismatch in gain or phase could critically corrupt the performance. Secondly, LO leakage to the mixer has a significant impact and could result in self-mixing problems, which causes a time-varying DC offset at the output of the mixer.

#### 2.3 FREQUENCY SYNTHESIZER ARCHITECTURES

There are many different approaches for implementing a frequency synthesizer [40–42]. Commonly, a frequency synthesizer can be categorized into four main flavors: Direct Analog Frequency Synthesizer (DAFS), Direct Digital Frequency Synthesizer (DDFS), indirect or PLL-based frequency synthesizer, and hybrid frequency synthesizer. The synthesizer performance depends heavily on each particular scheme. Typically, among all the previous schemes, the indirect frequency synthesizer is the most commonly used approach in wireless communication systems because of its high performance, as it has the possibility to achieve high frequency generation, high spectral purity and low power consumption. In the following sub-sections, the above frequency synthesis techniques are explored and their advantages and disadvantages are investigated.

#### 2.3.1 DIRECT ANALOG FREQUENCY SYNTHESIZER

The DAFS approach is shown in Figure 2.4. As indicated by its name, the signal is generated directly employing a frequency multiplication, mixing and division, from a single fixed reference frequency [2]. As explained in the figure, the number of mixing and division stages depends on the target output frequency and the required fine resolution. The generated output frequency can be expressed as

$$f_{out} = f_1 + \frac{f_2}{N} + \frac{f_3}{MN} \tag{2.1}$$

The key advantages of the DAFS approach are the extremely fast switching speed and excellent phase noise performance, as the latter depends mainly on the reference source and can potentially be very low. Unfortunately, serious problems associated with DAFS limit its use in wireless communication systems. The first major disadvantage is the cross coupling between cascaded stages, which degrades spectral purity. Careful layout with perfect isolation between individual components would be needed to alleviate this problem. Also, DAFS is characterized as a hardware intensive topology. Therefore, for stringent specifications in terms of small frequency step and wide coverage, DAFS becomes very expensive and power hungry topology, and ultimately unfeasible.

## 2.3.2 DIRECT DIGITAL FREQUENCY SYNTHESIZER

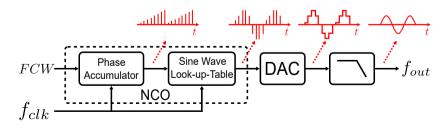

The DDFS approach is very attractive for the reasons of fast frequency generation and very fine frequency resolution. Moreover, it can also be easily integrated, as no external components are needed. Figure 2.5 shows the block diagram of a DDFS. A DDFS utilizes a digital phase accumulator and a sine wave look-up-table to digitally create the desired output waveform in digital domain. Thereafter, a DAC is used to convert the digital waveform from the digital domain to the analog domain. High frequency spurious tones at the DAC output are filtered out by a LPF. As a result of using a lock-up-table, this synthesizer is also known as a table-look-up synthesizer. Furthermore, the combination of digital phase accumulator and sine wave look-up-table is termed Numerically Controlled Oscillator (NCO) [40].

In this approach, the minimum achievable frequency step is determined by the capacity of the digital phase accumulator employed. Therefore, for an L bit accumulator and a certain *Frequency Control Word (FCW)*, the output frequency of the DDFS in terms of the clock frequency  $f_{clk}$  can be calculated as [40]

$$f_{out} = \frac{FCW}{2L} f_{clk} \tag{2.2}$$

Therefore, the range of the output frequency is from  $f_{clk}/2^L$  to  $f_{clk}$ , since FCW can take any integer value between 1 and  $2^L$ .

However, the following major drawbacks limit the use of this topology in

Figure 2.5 Direct digital frequency synthesizer [3].

wireless communication systems, especially for mobile communications. The first reason is the excessive power consumption at high frequencies, as the system has to be clocked with a frequency at least twice the output frequency. In addition, implementing a DAC and a LPF at high frequencies adds a significant amount of power consumption to the total power. Secondly, due to DAC limited resolution and non-linearity issues, the DDFS output spectrum usually suffers from high spurious tones, which are not completely removed by the LPF. These spurious tones degrade the spectral purity performance.

## 2.3.3 INDIRECT FREQUENCY SYNTHESIZER

The indirect frequency synthesizer, also called PLL-based frequency synthesizer, is the most common, popular and widely used approach in communication systems. Basically, a PLL is a control system with negative feedback producing an output frequency with a certain relation to a reference frequency. Depending on the possible ratios between the output frequency and the reference frequency, PLLs are categorized into two groups: integer-N and fractional-N PLLs. Essentially, fractional-N PLLs are a generalized version of integer-N PLLs. In most wireless applications, an integer-N PLL is not capable of meeting the targeted overall performance; hence, a fractional-N PLL is typically employed for frequency synthesis.

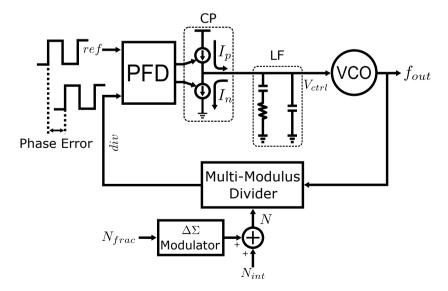

Analog PLL-based frequency synthesizers typically adopt CP architectures. A block diagram of a conventional CP-PLL is depicted in Figure 2.6. The out-

Figure 2.6 Fractional-N CP-PLL.

Figure 2.7 Fractional-N DPLL.

put frequency,  $f_{out}$ , is generated by the Voltage Controlled Oscillator (VCO), while the reference frequency  $f_{ref}$ , is generated by a low-phase-noise crystal oscillator. In the feedback path, the VCO output is divided by a Multi-Modulus Divider (MMD) to produce the frequency-divided signal div. A  $\Delta\Sigma$  modulator is used to dynamically vary the division ratio to achieve an effective fractional division ratio. The Phase Frequency Detector (PFD) detects the difference in phase between the reference signal ref, and the div signal in terms of the time difference between their respective closest rising edges. The PFD, thereafter, generates a series of pulses: either "up" or "down" pulses, with a width proportional to the measured time difference. The CP scales the signal generated from the PFD and pumps a current with a proportional duty cycle either into  $(I_p)$  or out  $(I_n)$  of the Loop Filter (LF). The LF is typically a LPF which converts this current into a tuning voltage for the VCO, while at the same time suppressing noise and glitches produced by the CP non-ideal behavior in order to prevent them from modulating the VCO, causing excessive noise and spurious tones in the VCO output spectrum. The VCO tuning voltage  $V_{ctrl}$  increases or decreases the VCO output frequency. As a result, the VCO steady-state output frequency is equal to

$$f_{out} = (N_{int} + N_{frac})f_{ref} (2.3)$$

where  $N_{int}$  and  $N_{frac}$  are the integer and fractional parts of the division ratio, respectively.

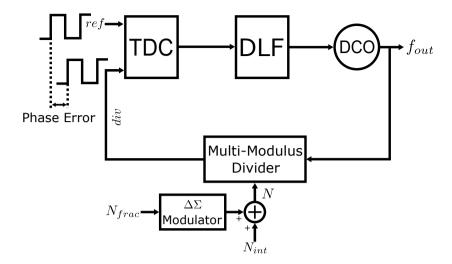

Fractional-N DPLL-based frequency synthesizers often employ a similar architecture as conventional fractional-N analog PLL-based frequency synthe-

sizers. Such architectures can be realized in several variations to meet the specific requirement of different applications, which differ in performance and complexity [27][31][33][36][37][39][43]. In general, however, the architecture of fractional-N analog PLLs are moved to the digital domain by replacing the PFD with a TDC, the analog LF with a DLF, and the VCO with a DCO, as illustrated in Figure 2.7.

## 2.3.4 HYBRID FREQUENCY SYNTHESIZER

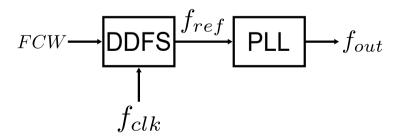

A Hybrid frequency synthesizer is constructed by combining two or more structures together, in order to take advantage of the special features that distinguish each technique and minimize the drawbacks. Typically, it is a combination between DDFS and PLL [41], as shown in Figure 2.8. In the DDFS-PLL hybrid structure, the DDFS generates a narrow-band instantaneously tunable low frequency signal, used as the PLL reference signal. The PLL up-converts that reference signal to the targeted frequency.

The DDFS-PLL hybrid structure takes the advantages of the very fine frequency step and the fast switching time introduced by the DDFS to enhance the tunability of the whole system, which is difficult to achieve using the PLL structure alone.

# 2.4 PERFORMANCE METRICS OF THE FREQUENCY SYNTHESIZER

The frequency synthesizer is a key building block in every transceiver. It needs to provide high quality LO signals with stringent requirements to perform frequency translation, either down-conversion or up-conversion, where the performance of the LO frequency generation system directly affects the performance of the whole transceiver.

In general, the frequency synthesizer is characterized by some main characteristics. Therefore the frequency synthesizers are usually selected and ranked according to the following set of performance metrics.

Figure 2.8 The DDFS-PLL hybrid structure.

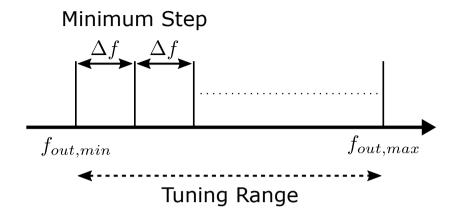

Figure 2.9 Frequency tuning range and frequency resolution.

## 2.4.1 FREQUENCY TUNING RANGE AND FREQUENCY RESOLUTION

The frequency synthesizer should be capable of producing an accurate carrier frequency that can be well tuned within a specified range, to cover all of the frequency bands specified for a given standard. This specified range is termed as a frequency synthesizer tuning range, as shown in Figure 2.9. In order to ease up frequency planning in presence of an unprecedented band proliferation, it is desirable that as many frequencies as possible are synthesized by a single frequency synthesizer. Such tuning is typically determined by the tuning range of its employed oscillator, and by the frequency multiplication ratio.

Besides tuning range, the synthesizer must be capable of producing a carrier frequency with high frequency resolution, or minimum frequency tuning step. Resolution, which is defined as the minimum possible value achieved via tuning, is usually specified according to the channel spacing for a given standard (see Figure 2.9).

#### 2.4.2 SPECTRAL PURITY

Practical frequency synthesizers are not able to deliver ideal LO signals due to devices noise and external interferences. The quality of their output is typically evaluated depending on two critical performance metrics, i.e. phase noise and spurious tones. Therefore, it is crucial to investigate the impact of these on communication systems performance.

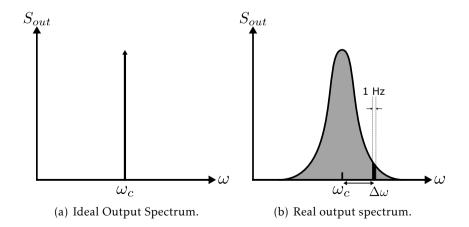

#### 2.4.2.1 PHASE NOISE

An ideal oscillator generates a perfectly periodic output in the time domain, which corresponds to a single tone in the frequency domain at the desired

oscillation frequency  $\omega_c$ . In reality, however, due to noise, the oscillation signal is phase and amplitude modulated by random or periodic fluctuations. The random fluctuations result in phase noise and amplitude noise, and the output spectrum exhibits sidebands close to  $\omega_c$  rather than a single tone, as shown in Figure 2.10. Amplitude noise, on the other hand, is rejected by the oscillator itself close to  $\omega_c$ . The output signal for an ideal and noisy oscillator can be respectively expressed as

$$V_{out,ideal}(t) = A\sin(\omega_c t) \tag{2.4}$$

$$V_{out}(t) = A\sin[\omega_c t + \phi(t)]$$

(2.5)

where A is the amplitude of the signal, while  $\phi(t)$  represents the random phase fluctuation. Supposing that the random phase fluctuation in (2.5) takes the form of  $\phi(t) = \Delta\phi\sin(\Delta\omega t)$ , where  $\Delta\phi$  is the maximum phase deviation, (2.5) can be rewritten as

$$V_{out}(t) = A\sin[\omega_c t + \Delta\phi\sin(\Delta\omega t)]$$

(2.6)

Typically,  $\Delta \phi \ll 1$ , hence the final form of (2.6) becomes

$$V_{out}(t) = A\sin(\omega_c t) + \frac{A\Delta\phi}{2} \{\sin[(\omega_c + \Delta\omega)t] - \sin[(\omega_c - \Delta\omega)t]\}$$

(2.7)

Equation (2.7) shows that the output spectrum of the oscillator is a combination of a strong tone at  $\omega_c$  plus a narrow-band Frequency Modulation (FM)

Figure 2.10 Output Spectrum of both an ideal and noisy oscillator.

signal with a modulation index  $\Delta \phi$ . This FM modulation generates two small tones at  $\omega_c + \Delta \omega$  and  $\omega_c - \Delta \omega$ . Therefore, the output Power Spectral Density (PSD) is

$$S_{out}(\omega) = \frac{A^2}{2} \left[ \delta(\omega - \omega_c) + \frac{1}{2} S_{\phi}(\omega - \omega_c) + \frac{1}{2} S_{\phi}(\omega_c - \omega) \right]$$

(2.8)

where

$$S_{\phi}(\omega) = \frac{\Delta \phi^2}{2} \delta(\omega - \Delta \omega) \tag{2.9}$$

Equation 2.8 illustrates the skirt shape of the oscillator spectrum, where the phase noise spectrum can be seen as a sum of sines.

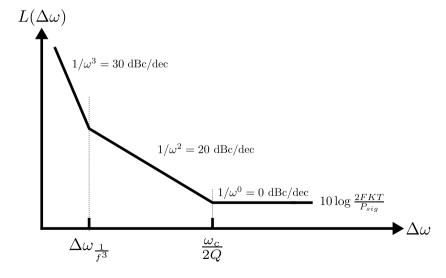

The phase noise is quantified by normalizing the noise power in a unit bandwidth at a certain offset frequency  $\Delta \omega$  from  $\omega_c$  with respect to the total carrier power. It can be expressed as a single sided PSD with units of dBc/Hz, i.e. decibels relative to the carrier per Hertz

$$L(\Delta\omega) = 10\log(\frac{\text{Noise Power in a 1 Hz bandwidth at }\omega_c + \Delta\omega}{\text{Total Carier Power}}) \qquad (2.10)$$