# UCLA UCLA Electronic Theses and Dissertations

### Title

Digitally Enhanced Wireless Transceivers for Multi-mode Reconfigurable Radios

Permalink https://escholarship.org/uc/item/8c3516vp

**Author** Nanda, Rashmi

Publication Date 2012

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# Digitally Enhanced Wireless Transceivers for Multi-mode Reconfigurable Radios

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

## Rashmi Nanda

© Copyright by Rashmi Nanda 2012

# Digitally Enhanced Wireless Transceivers for Multi-mode Reconfigurable Radios

by

#### **Rashmi Nanda**

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2012 Professor Dejan Marković, Chair

Digitally enhanced wireless transceivers are gaining prominence due to their promise of greater integration, flexibility to adapt to varying SNR conditions, performance, and area benefit that comes with CMOS feature size reduction. This thesis discusses the benefits of going digital in a system that has until now been dominated by analog or discrete-time signal processing. Digitally assisted radio transceiver architectures that incorporate a wide range of tuning parameters to control the RF carrier, signal bandwidth, and baseband modulation schemes are presented. These architectures rely on high-speed A/D and D/A conversion close to the antenna in order to maximize the extent of digital signal processing in the radio chain. We examine specific challenges that such a system faces in the context of minimizing noise, maximizing signal bandwidths, and enabling efficient filtering and sample rate conversion. The thesis also presents prototype architectures for a radio receiver and transmitter that employ a range of signal processing techniques to enable high-throughput, power-efficient systems. The dissertation of Rashmi Nanda is approved.

Alan N. Willson Sudhakar Pamarti Milos D. Ercegovac Dejan Marković, Committee Chair

University of California, Los Angeles

2012

I dedicate this dissertation to my husband, Rohit, for his incredible patience and unwavering love and support over the course of my research.

## TABLE OF CONTENTS

| 1 | Intr | oduction                                | 1  |

|---|------|-----------------------------------------|----|

|   | 1.1  | Flexible Radio Receivers                | 4  |

|   | 1.2  | Flexible Radio Transmitters             | 8  |

|   | 1.3  | Thesis Outline                          | 14 |

| 2 | A/D  | Converters for Flexible Receivers       | 15 |

|   | 2.1  | $\Sigma\Delta$ Modulation               | 18 |

|   | 2.2  | ADC Architectures                       | 20 |

|   | 2.3  | ADC Modeling                            | 22 |

|   | 2.4  | Clock Jitter Analysis                   | 28 |

|   | 2.5  | Pre-selection Filter                    | 29 |

| 3 | Digi | tal Front-end for Flexible Receivers    | 32 |

|   | 3.1  | CIC Decimation Filters                  | 32 |

|   | 3.2  | Reconfigurable FIR Filters              | 35 |

|   | 3.3  | Fractional Sample Rate Conversion       | 37 |

|   |      | 3.3.1 Polynomial Interpolation          | 40 |

|   | 3.4  | DFE Architecture                        | 46 |

|   | 3.5  | Simulation Results                      | 47 |

| 4 | Digi | tal Front-end for Flexible Transmitters | 50 |

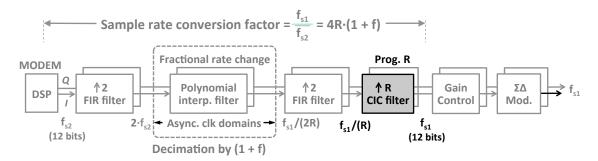

|   | 4.1  | Transmit Digital Front-end              | 52 |

|   |      | 4.1.1 Digital Interpolation             | 53 |

|   |      | 4.1.2 Digital Front-end Architecture    | 55 |

|    |        | 4.1.3 Polynomial Interpolation                | 58  |

|----|--------|-----------------------------------------------|-----|

|    | 4.2    | CIC Interpolation                             | 60  |

|    | 4.3    | $\Sigma\Delta$ Modulation                     | 62  |

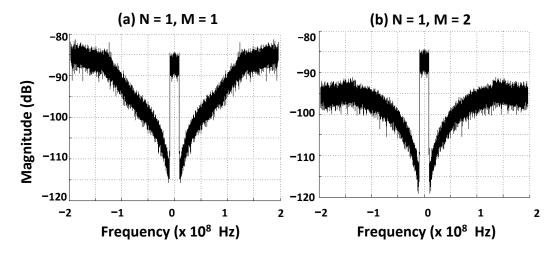

|    |        | 4.3.1 Quantizer Output Width ( <i>M</i> )     | 66  |

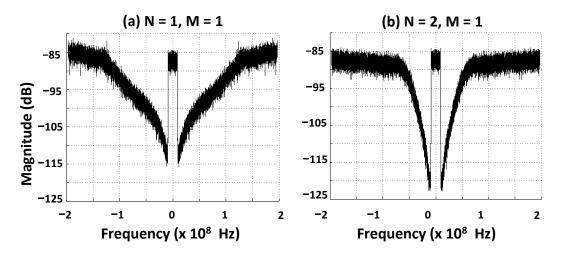

|    |        | 4.3.2 Order of $\Sigma\Delta$ Modulation (N)  | 67  |

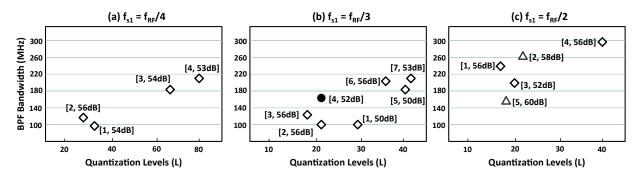

|    |        | 4.3.3 Sample Rate $(f_{s1})$                  | 69  |

|    | 4.4    | RFDAC Architecture                            | 71  |

|    | 4.5    | Proposed Solution                             | 72  |

|    | 4.6    | Simulation Results                            | 76  |

| 5  | Mix    | ing and Data Conversion in Radio Transmitters | 80  |

|    | 5.1    | Dynamic Element Matching (DEM)                | 85  |

|    | 5.2    | Simulation Results                            | 88  |

| 6  | Exp    | erimental Results                             | 91  |

|    | 6.1    | Rx DFE Measurements                           | 92  |

|    | 6.2    | Transmitter Implementation                    | 94  |

|    |        | 6.2.1 Measured Results                        | 95  |

| 7  | Con    | clusion & Future Direction                    | 99  |

|    | 7.1    | Summary of Research Contributions             | 99  |

|    | 7.2    | Future Directions                             | 100 |

| Re | eferen | <b>ces</b>                                    | 103 |

## LIST OF FIGURES

| 1.1  | Multi-mode, multi-band specifications for wireless standards                                                           | 1  |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | (a) Traditional radio receiver front-end (b) The ideal software-defined radio receiver                                 | 2  |

| 1.3  | Conceptual digitally intensive radio receiver terminal.                                                                | 6  |

| 1.4  | Traditional radio transmitter front-end and the ideal software-defined radio Tx                                        | 8  |

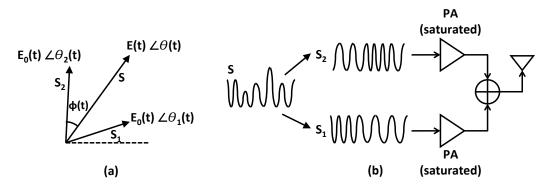

| 1.5  | Outphasing transmitter (a) Defining the signal vectors (b) Power amplifiers                                            | 9  |

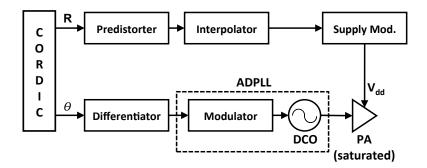

| 1.6  | Polar modulator combines the amplitude, <i>R</i> , and phase, $\theta$ , signals in the PA                             | 10 |

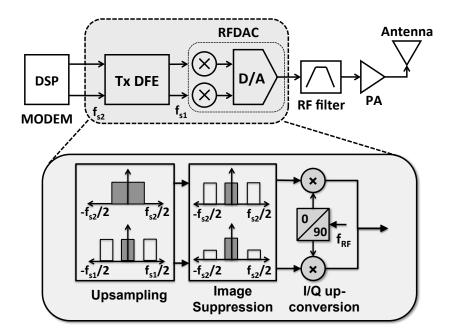

| 1.7  | Basic signal flow in a linear modulator.                                                                               | 12 |

| 2.1  | RF carriers, channel bandwidths, and dynamic range requirements for various radio stan-                                |    |

|      | dards                                                                                                                  | 15 |

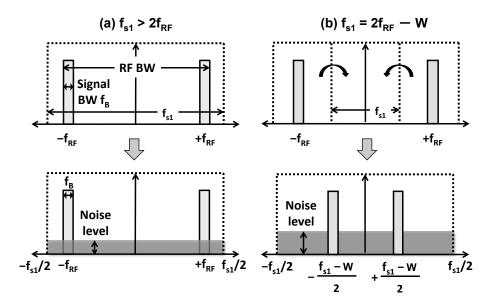

| 2.2  | ADC sampling (a) Nyquist criterion $(f_{s1} > 2f_{RF})$ (b) Undersampling $(f_{s1} = 2f_{RF} - W)$                     | 17 |

| 2.3  | (a) Undersampling at $f_{s1} = 4/3 f_{RF}$ . (b) RF data centered at $\pi/2$                                           | 18 |

| 2.4  | A $2^{nd}$ -order bandpass $\Sigma\Delta$ modulator with 1-bit quantizer                                               | 18 |

| 2.5  | Power spectral density of a 2 <sup>nd</sup> -order bandpass $\Sigma\Delta$ modulator with 1-bit output                 | 19 |

| 2.6  | Comparison of various ADC architectures                                                                                | 20 |

| 2.7  | 4th-order bandpass $\Sigma\Delta$ ADC with 4-bit quantizer. LC resonators are tuned at $f_{RF}.~\ldots~\ldots$         | 22 |

| 2.8  | Simplified model of the bandpass $\Sigma\Delta$ ADC. ZOH is the zero-order-hold function                               | 23 |

| 2.9  | (a) Noise transfer function at $R_W/L = 0$ , $2\pi 10^7$ , and $4\pi 10^7$ . (b) Zoomed-in <i>NTF</i> shows            |    |

|      | notch at f <sub>RF</sub> . (c) Signal transfer Function at $R_W/L = 0$ , $2\pi 10^7$ , and $4\pi 10^7$ . (d) Zoomed-In |    |

|      | STF shows passband around $f_{RF}$ .                                                                                   | 25 |

| 2.10 | Q enhancement of inductor with negative resistance realized using cross-coupled transis-                               |    |

|      | tors $M_1$ and $M_2$ .                                                                                                 | 26 |

| 2.11 | Spectrum of a 2.025GHz RF modulated sinusoid undersampled at 2.7GHz (4/3 $f_{RF}$ ). The                               |    |

|      | signal replica is centered at 0.675GHz                                                                                 | 27 |

| 2.12 SNR variation with input signal amplitude and RF carrier frequency                                     |

|-------------------------------------------------------------------------------------------------------------|

| 2.13 SNR degradation with increasing jitter in the clock                                                    |

| 2.14 Expected attenuation characteristics of the pre-selection filter                                       |

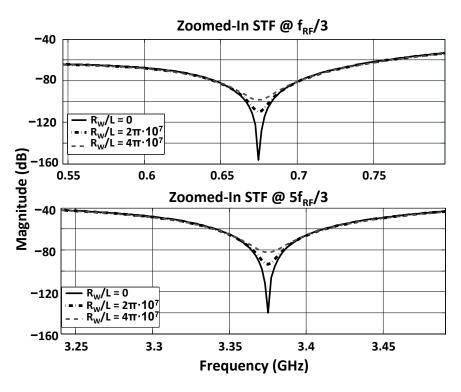

| 2.15 Zoomed-in view of notches in the STF at $f_{RF}/3$ and $5f_{RF}/3$                                     |

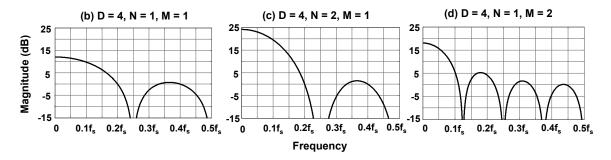

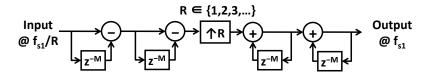

| 3.1 (a) CIC architecture. (b)-(d)Response of the CIC at different values of D, N, and M 33                  |

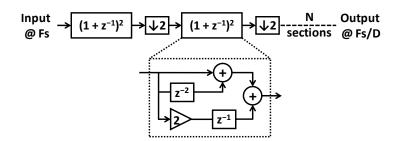

| 3.2 Throughput-optimized feedforward CIC architecture for a $2^{nd}$ -order filter                          |

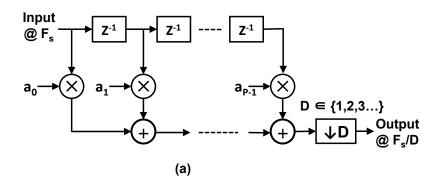

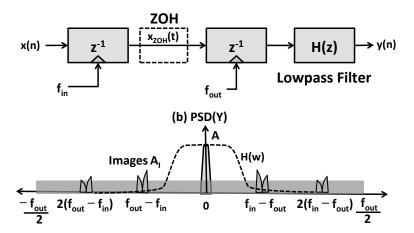

| 3.3 Reconfigurable FIR filter signal-flow-graph                                                             |

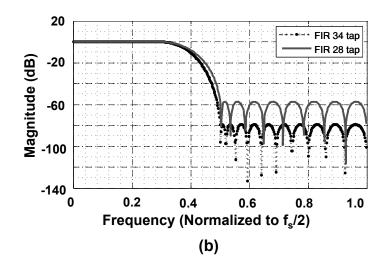

| 3.4 Frequency response of the FIR with variable tap coefficients                                            |

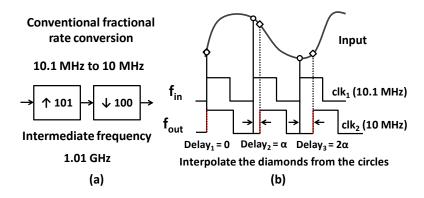

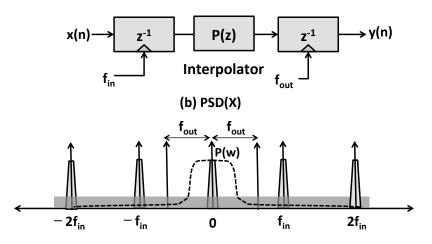

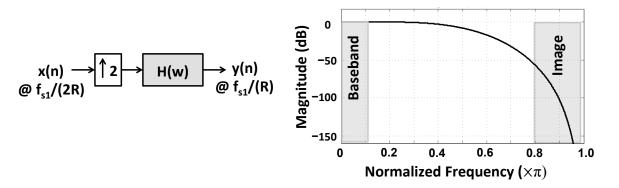

| 3.5 (a) Conventional fractional sample rate conversion (b) Digital Interpolation                            |

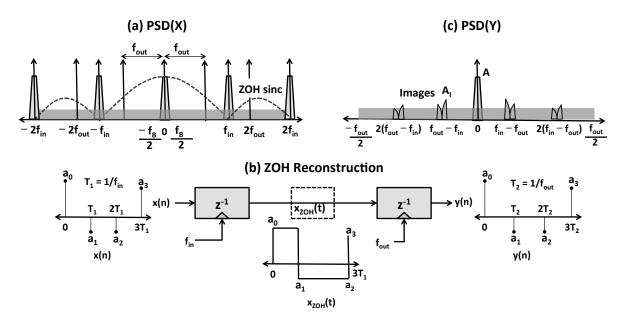

| 3.6 (a) Original baseband spectrum (b) Interpolation with ZOH as reconstruction filter (c)                  |

| Attenuated spectral images after interpolation                                                              |

| 3.7 (a) ZOH Reconstruction followed by lowpass filter (b) Output spectrum                                   |

| 3.8 (a) Interpolation using polynomial interpolator, $P(z)$ , for reconstruction (b) Attenuated             |

| spectral images after interpolation                                                                         |

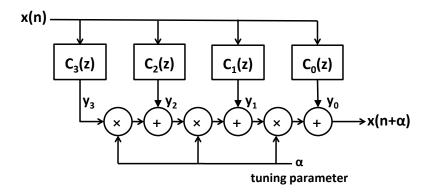

| 3.9 Farrow filter used for third order polynomial interpolation                                             |

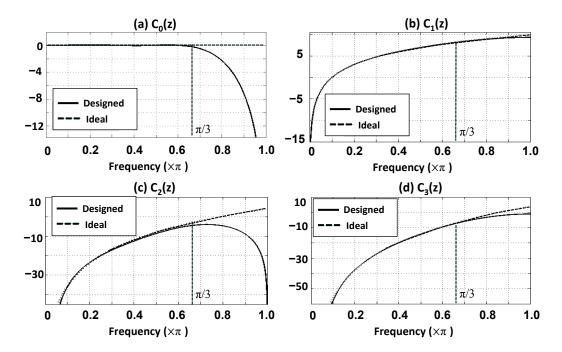

| 3.10 Frequency response of Farrow polynomials. The dashed line shows behavior of ideal all-                 |

| pass and differential functions                                                                             |

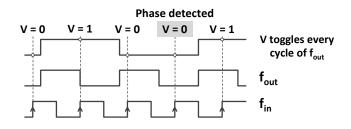

| 3.11 (a) Phase calibration between input and output clocks                                                  |

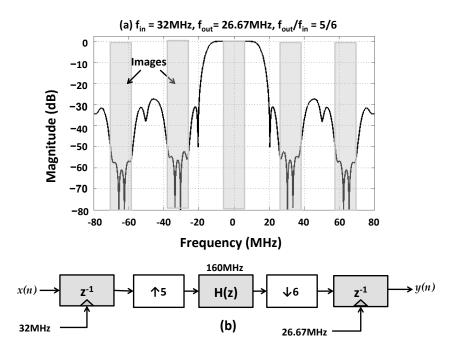

| 3.12 (a) Farrow frequency response at $f_{in} = 32$ MHz and $f_{out} = 26.67$ MHz. (b) Equivalent upsample- |

| filter-downsample model                                                                                     |

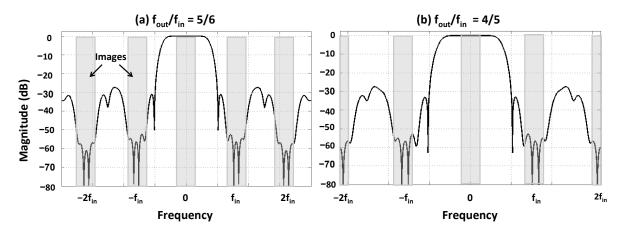

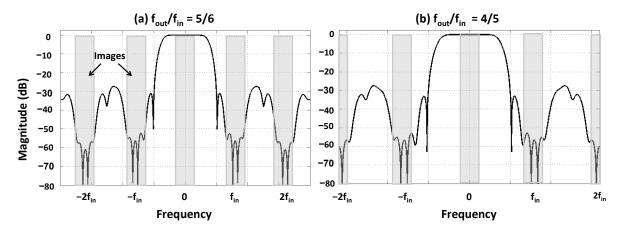

| 3.13 (a) Farrow frequency response at $f_{out}/f_{in}=5/6$ . (b) Response at $f_{out}/f_{in}=4/5$           |

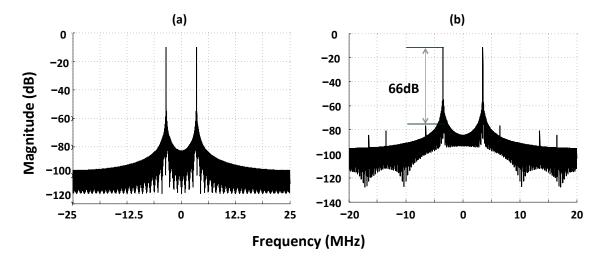

| 3.14 (a) Sinusoidal input to Farrow interpolator. (b) Farrow output after interpolation at rate 4/5. 46     |

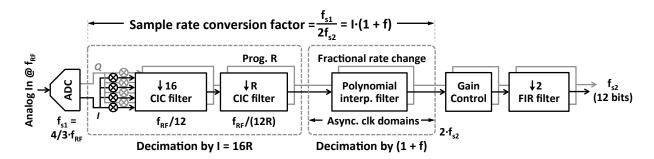

| 3.15 Receiver Digital Front-end Architecture                                                                |

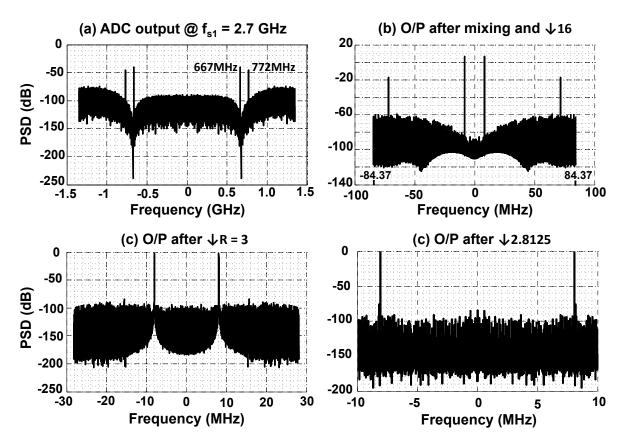

| 3.16 Spectrum of output at different stages of the receiver DFE                                             |

| 4.1 Linear RF modulator with a digital front-end (DFE), $\Sigma\Delta$ modulator, and RFDAC 50              |

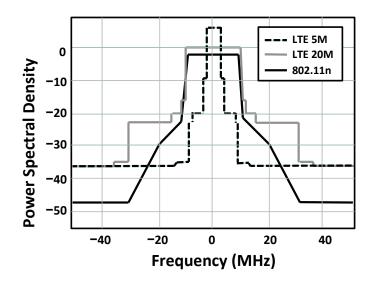

| 4.2  | FCC emission mask for various cellular and WLAN standards                                        | 51 |

|------|--------------------------------------------------------------------------------------------------|----|

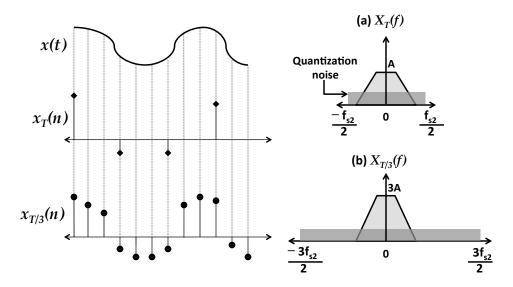

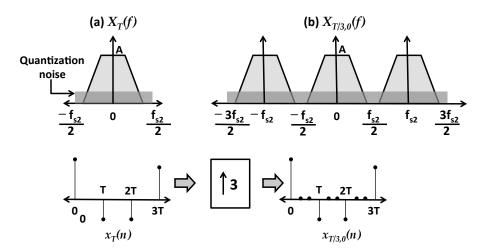

| 4.3  | (a) $X_T(f)$ at sample rate $f_{s_2}$ (b) $X_{T/3}(f)$ at sample rate $3f_{s_2}$ .               | 53 |

| 4.4  | (a) Original signal sampled at $f_{s2}$ (b) Zero-stuffed signal at $3f_{s2}$                     | 54 |

| 4.5  | (a) Zero-stuffed signal at $3f_{s2}$ (b) Filtered signal at $3f_{s2}$ .                          | 55 |

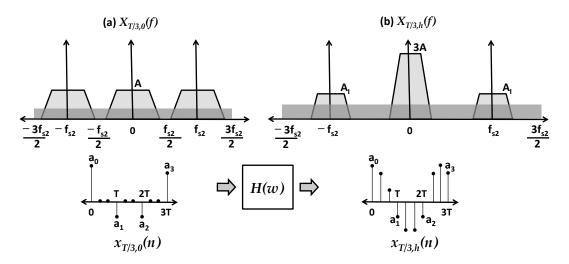

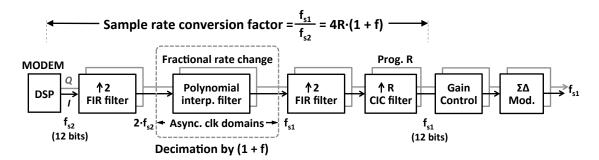

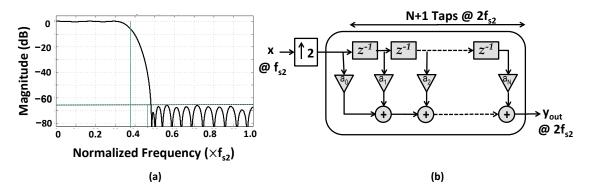

| 4.6  | Linear RF modulator with a digital front-end (DFE), $\Sigma\Delta$ modulator, and RFDAC          | 56 |

| 4.7  | (a) Interpolation by 2 FIR response, (b) conventional FIR                                        | 57 |

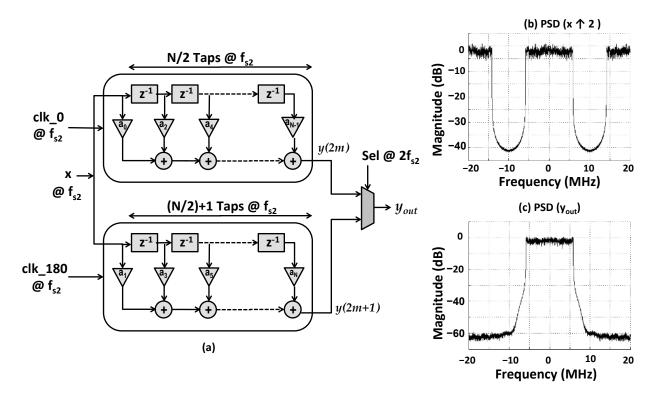

| 4.8  | (a) Polyphase implementation of interpolation-by-2 FIR lowpass filter (b) PSD of zero-           |    |

|      | stuffed input to FIR (c) PSD of interpolated FIR output.                                         | 58 |

| 4.9  | Farrow frequency response at different fractional interpolation ratios                           | 59 |

| 4.10 | Conventional cascade integrated comb (CIC) interpolator.                                         | 59 |

| 4.11 | Linear RF modulator with a digital front-end (DFE)                                               | 60 |

| 4.12 | Conventional cascade integrated comb (CIC) interpolator.                                         | 60 |

| 4.13 | CIC Interpolator frequency response for various values of R, N, and M                            | 61 |

| 4.14 | CIC Interpolator output frequency response for $R = 4$ , $N = 3$ , and $M = 1$                   | 62 |

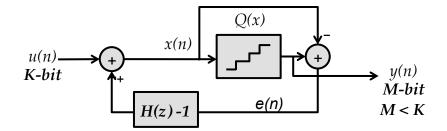

| 4.15 | $1^{st}$ -order $\Sigma\Delta$ modulator with an M-bit quantizer                                 | 63 |

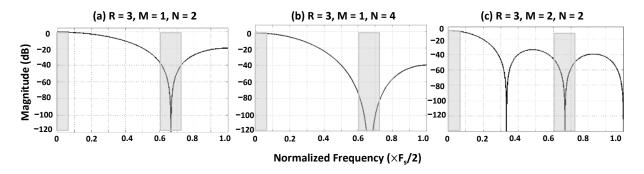

| 4.16 | Spectrum of 1-bit output with 1 <sup>st</sup> -order noise shaping                               | 64 |

| 4.17 | Noise shaping coder topology of a $\Sigma\Delta$ modulator.                                      | 65 |

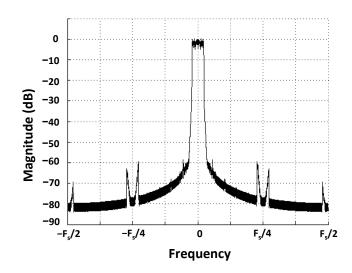

| 4.18 | Effect on noise shaping characteristics with increasing quantizer bits $(M)$                     | 66 |

| 4.19 | Effect on noise shaping characteristics with increasing order of modulation $(N)$                | 67 |

| 4.20 | Noise shaping coder topology of a $\Sigma\Delta$ modulator.                                      | 68 |

| 4.21 | (a) Aliasing of quantization noise with signal after up-conversion to $f_{RF}$ (b) up-conversion |    |

|      | without aliasing.                                                                                | 70 |

| 4.22 | Effect of increasing sample rate on noise shaping characteristics                                | 71 |

| 4.23 | (a) Sinc filtering in RFDAC (b) Sinc filtering in 2-channel time-interleaved RFDAC               | 72 |

| 4.24 | Non recursive realization of the NTF, $H(z)$ , using an FIR                                      | 73 |

| 4.25 | Sigma-delta modulator architectures generated using the iterative flow                                | 75 |

|------|-------------------------------------------------------------------------------------------------------|----|

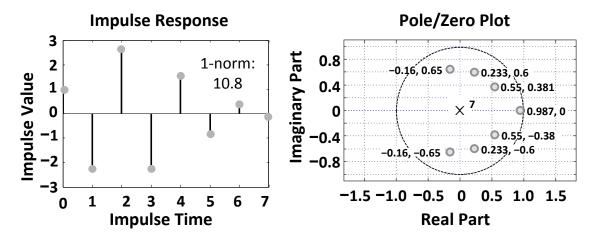

| 4.26 | Impulse response and pole-zero plot of the $7^{th}$ -order minimum phase FIR filter                   | 76 |

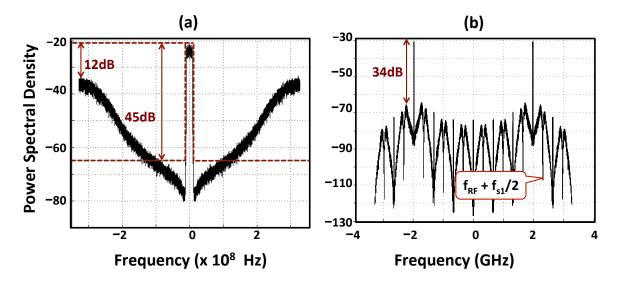

| 4.27 | (a) Noise shaping with 7 <sup>th</sup> -order FIR NTF (b) 2-channel time-interleaved DAC filtering on |    |

|      | up-converted RF signal at $f_{RF} = 2.4$ GHz                                                          | 77 |

| 4.28 | Spectrum of RF modulated signal after 2 <sup>nd</sup> -order bandpass filtering                       | 77 |

| 4.29 | (a) Effect of 2-channel time-interleaved DAC filtering on upconverted RF signal at $f_{RF}$ =         |    |

|      | 1.98GHz. (b) Spectrum of RF modulated signal at $f_{RF}$ =1.98GHz after 3-pole bandpass               |    |

|      | filtering                                                                                             | 78 |

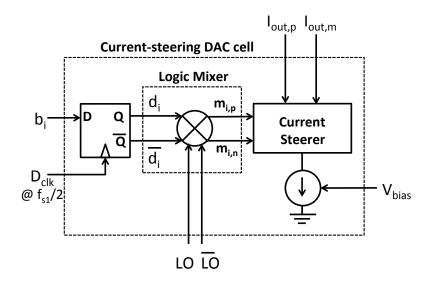

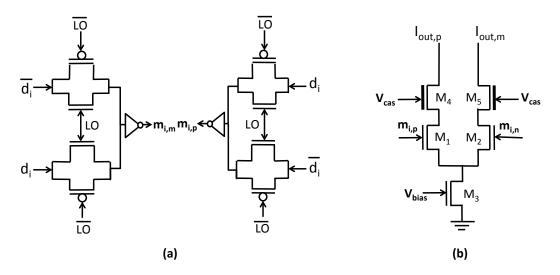

| 5.1  | RFDAC unit cell schematic.                                                                            | 80 |

| 5.2  | (a) Schematic of logic mixer (b) Current steering operation.                                          | 81 |

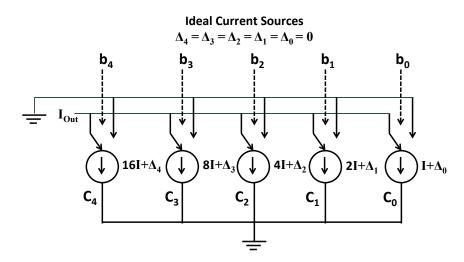

| 5.3  | Binary-weighted DAC topology with unequal weighted current sources                                    | 82 |

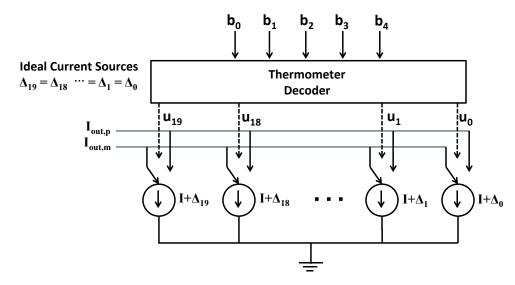

| 5.4  | Unary DAC with equal weighted current sources.                                                        | 83 |

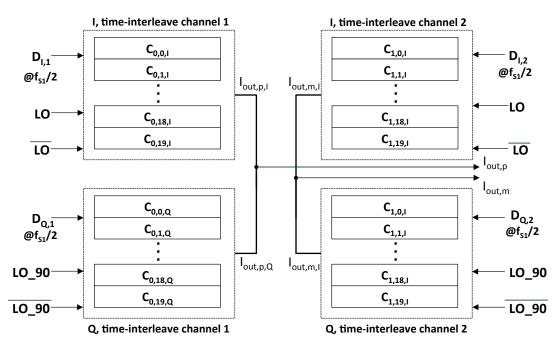

| 5.5  | Time-interleaved RFDAC architecture with I and Q channels                                             | 84 |

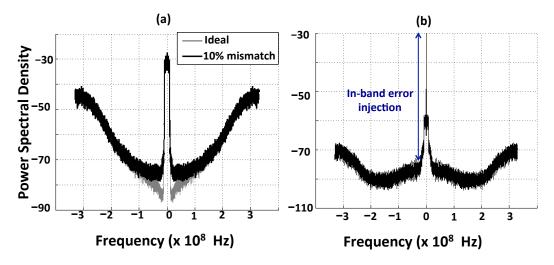

| 5.6  | Effect of mismatches in the unary current sources of the RFDAC                                        | 85 |

| 5.7  | (a) Non-ideal model of the current-steering DAC (b), (c) Table showing ideal and non-ideal            |    |

|      | outputs of the DAC for identical input stimuli                                                        | 86 |

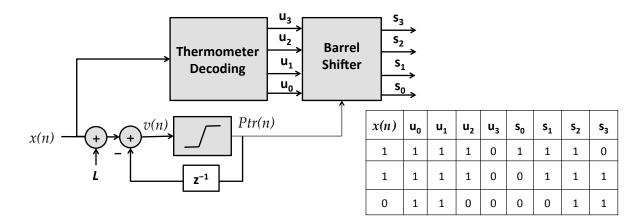

| 5.8  | Data weighted averaging approach for dynamic element matching                                         | 87 |

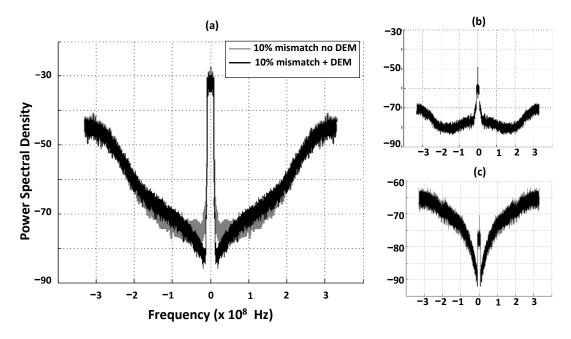

| 5.9  | (a) Effect of dynamic element matching (b) Error spectrum without matching (c) Error                  |    |

|      | spectrum after matching.                                                                              | 88 |

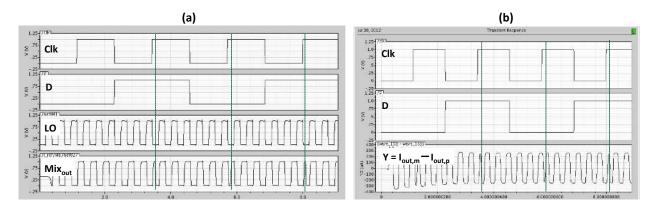

| 5.10 | (a) Simulated waveforms from mixer output (b) Waveforms from current steerer output                   | 89 |

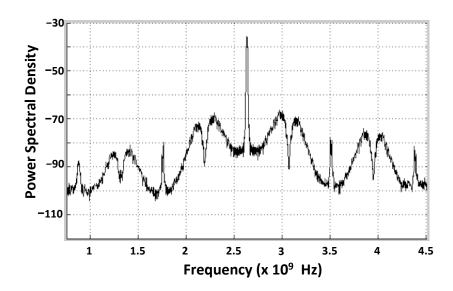

| 5.11 | Spectrum obtained after circuit simulations of the RFDAC                                              | 90 |

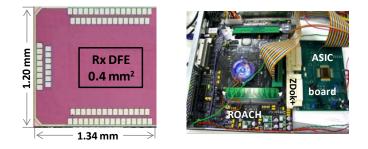

| 6.1  | (a) Rx DFE die photo (b) Measurement setup                                                            | 91 |

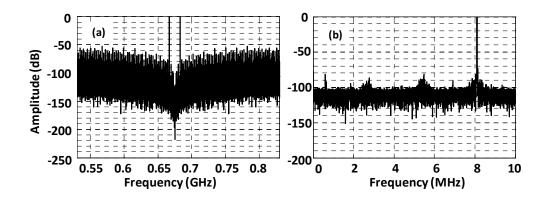

| 6.2  | (a) FFT of 16 MHz bandwidth input modulated at 2.025 GHz after undersampling. (b)                     |    |

|      | FFT of 20 MHz sampled output sinusoid from chip.                                                      | 93 |

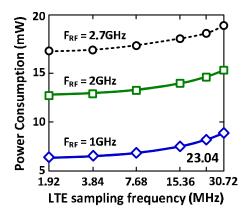

| 6.3 | Power consumption for LTE sampling frequencies. Solid lines: measured, dashed line:     |

|-----|-----------------------------------------------------------------------------------------|

|     | estimated                                                                               |

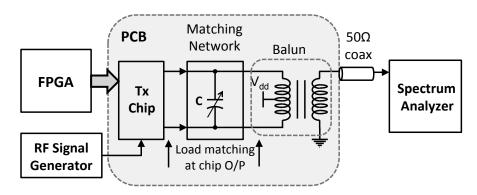

| 6.4 | Setup used for testing the Tx chip                                                      |

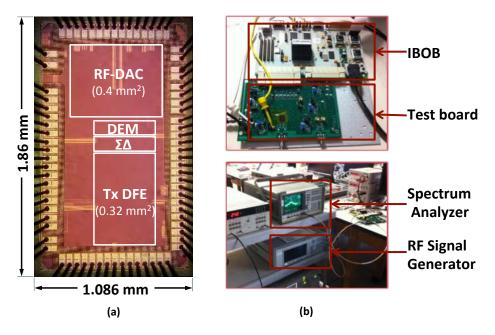

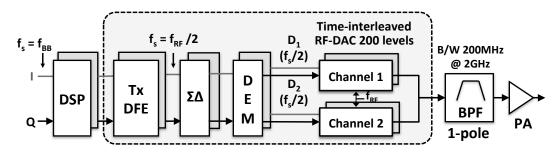

| 6.5 | (a) Tx DFE die photo (b) Measurement setup                                              |

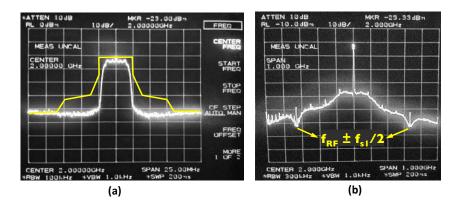

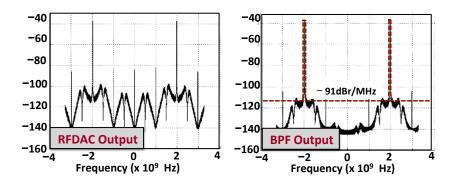

| 6.6 | (a) Close view spectrum of 5MHz bandwidth signal modulated at 2GHz (b) Far out spec-    |

|     | trum spanning 1GHz                                                                      |

| 7.1 | Proposed RF modulator for FDD operation in Rx bands at distance of 30MHz 101            |

| 7.2 | (a) Effect of 2-channel time-interleaved DAC filtering on upconverted RF signal.        |

|     | (b) Spectrum of RF modulated signal after 2 <sup>nd</sup> -order bandpass filtering 101 |

## LIST OF TABLES

| 4.1 | Specifications for multi-standard radio transmitters. |   |   |   |   |   |   |   |   |  |   |   |   | • | <br>52 |

|-----|-------------------------------------------------------|---|---|---|---|---|---|---|---|--|---|---|---|---|--------|

|     |                                                       | - | - | - | - | - | - | - | - |  | - | - | - |   | <br>   |

#### **ACKNOWLEDGMENTS**

This thesis would not have been possible without my advisor, Dejan Marković's, constant support and mentoring. He helped me throughout my time in graduate school and gave me sufficient freedom to work on things that would hold my interest. I am especially grateful for his patience during times when the experimental part of the research was not going ahead as planned. I am also thankful for his guidance and timely discussions, academic and otherwise, which helped me achieve my goals at UCLA. I would also like to thank my committee members, Professor Willson, Professor Ercegovac, and Professor Pamarti for their useful comments during the qualifying examination, which helped define the scope of this work. I also appreciate the funding support provided by the Center for Circuits and Systems Solutions (C2S2) during the course of my graduate study. Also, I would like to thank ST Microelectronics and Samsung Corporation for the infrastructural support they provided.

I want to thank my friends at UCLA for the help they provided during the 6 years of my stay. I appreciate Nitesh Singhal's help during research discussions and his guidance when I was setting up my experiments in the circuits lab. I would also like to thank Abhishek Ghosh who was ready to engage in research discussions at all times. In addition, all the group members in DMgroup were very supportive when I needed their assistance. Cheng-Cheng Wang was extremely helpful during the final phase of chip testing and I will always be grateful for his objective approach when it came to debugging problems in the test setups. Henry Chen taught me the use of all the relevant equipments in the lab and most of the experimental results in this thesis were obtained with his help and knowledge. I am also grateful to Sarah Gibson, Vaibhav Karkare, Chia-Hsiang Yang, Victoria Wang, Richard Dorrance, Vahagn Hokhikyan, Hariprasad Chandrakumar and other members of DMgroup for providing useful insights during the group meetings.

And finally, I have to thank my husband Rohit who was unfailing in his support and encouragement to keep me motivated so I could get closer to completing my degree. I would also like to thank my parents for the support and encouragement they provided, especially during times when I needed it most.

Portions of Chapters III and VI have been reprinted, with permission, from: R. Nanda, H. Chen,

and D. Marković, "A Low-Power Digital Front-end Direct-sampling Receiver for Flexible Radios," *IEEE Asian Solid State Circuits Conference*, November. 2011. Copyright © 2011, IEEE. D. Marković was the PI.

Portions of Chapter III have been reprinted, with permission, from: R. Nanda and D. Marković, "Digitally Intensive Receiver Design: Opportunities and Challenges", *IEEE Design & Test of Computers*, November 2012. Copyright © 2012, IEEE. D. Marković was the PI.

# VITA

| 2002–2006   | Bachelor of Technology (B.Tech.), Electronics and Electrical Com-<br>munication Engineering, Indian Institute of Technology, Kharag-<br>pur, India.                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2006–2008   | Master of Science (M.S.), Electrical Engineering, University of California Los Angeles (UCLA), California.                                                                                                   |

| 09/08–12/08 | Teaching Assistant, Electrical Engineering Department, UCLA,<br>Taught sections of EE 10 (circuit analysis class) under direction<br>of Professor Babak Daneshrad.                                           |

| 04/12-06/12 | Teaching Assistant, Electrical Engineering Department, UCLA.<br>MS Online EE 216B (advanced graduate class on DSP architec-<br>ture design and optimization) under direction of Professor Dejan<br>Marković. |

| 09/06-09/12 | Research Assistant, Electrical Engineering Department, UCLA.                                                                                                                                                 |

#### PUBLICATIONS

- R. Nanda and D. Marković, "ΣΔ Modulators for Low Power Digitally Intensive Radio Transmitters", to appear in the Proceedings of 2012 Asilomar Conference on Signals, Systems, and Computers.

- R. Nanda and D. Marković, "Digitally Intensive Receiver Design: Opportunities and Challenges", IEEE Design & Test of Computers, (Special issue on digitally-assisted wireless systems) November 2012.

- R. Nanda, H. Chen, and D. Marković, "A Low-Power Digital Front-end Direct-sampling Receiver for Flexible Radios," IEEE Asian Solid State Circuits Conference (ASSCC), November 2011.

- R. Nanda and D. Marković, "Energy-efficient Retiming and Scheduling of Datapath Dominant Digital Systems," ASP J. Low Power Electronics, vol. 7, no. 3, pp. 341-349, Aug. 2011.

- Rashmi Nanda, Chia-Hsiang Yang, Dejan Marković, "DSP Architecture Optimization in Matlab/Simulink Environment," in Proc. Int. Symposium on VLSI Circuits (VLSI'08), June 2008, pp. 192-193.

## **CHAPTER 1**

## Introduction

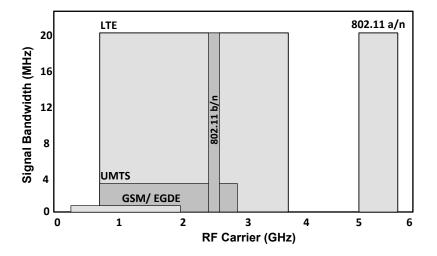

The evolution of CMOS integration is erasing the rigid boundary that used to divide a communication system into two distinct parts, the digital processing core and the RF front-end. While the digital core was tracking Moore's law and benefiting from the speed and performance enhancement provided by CMOS scaling, the RF front-end struggled with issues of low-voltage headroom, poor linearity, and small dynamic range. Adding to these problems was the need to support a wide variety of standards in a single device. Emerging standards such as LTE and WiMAX support data bandwidth up to 20MHz across multiple frequency bands that span several hundred MHz of the RF spectrum. A summary of the RF carriers and signal bandwidths for radio receivers in various wireless standards is shown in Figure 1.1. The multi-mode and multi-band specifications call for RF carriers anywhere between 300MHz to 5.8GHz and signal bandwidths between 200kHz to 20MHz.

The obvious solution was to replicate a conventional front-end multiple times, each realization

Figure 1.1: Multi-mode, multi-band specifications for wireless standards.

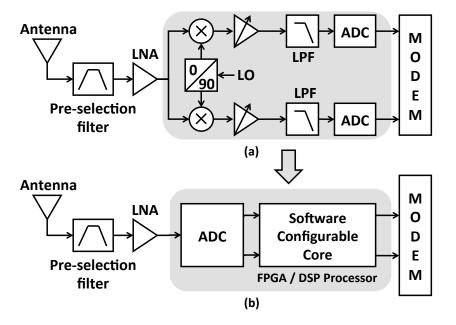

optimized to function in a narrow frequency band. For example, the conventional radio receiver, shown in Figure 1.2(a), will need several realizations of components like LNAs, analog amplifiers, mixers, and lowpass filters when the system has to operate over a wide range of carriers and signal bandwidths. But this solution proves to be costly not only because it occupies a large area, but it also costs significant design effort to build multiple front-ends and optimize them for a given set of specifications.

Eventually the RF community began to envision the holy grail of all RF front-ends, a "softwaredefined radio terminal" capable of being programmed to any radio standard, at any data rate, and any RF carrier [Mit95], [Abi07]. The ideal software-defined radio would be an FPGA-like device programmed externally through a computer interface. On the radio receiver (Rx) side this would mean a highly linear, high-speed ADC digitizing the received RF signal that is processed by the software programmable core. On the transmitter (Tx) side, a high-speed, highly linear DAC interface converts the digital RF data received from the programmable core into analog form suitable for transmission. Components like low-noise amplifiers (LNAs), power amplifiers (PAs), and bandpass filters will remain in the chain, but we get rid of analog components like mixers, amplifiers, and baseband filters that are necessary for signal conditioning in a traditional front-end.

Figure 1.2: (a) Traditional radio receiver front-end (b) The ideal software-defined radio receiver.

The distinction between the two approaches is shown for the radio receiver in the block diagram of Figure 1.2. In Figure 1.2(b), the software radio replaces all the signal conditioning components of the radio receiver in Figure 1.2(a). The RF signal is first digitized by a high-speed ADC, following which it is amplified and filtered by the software-defined core. Parameters like carrier and bandwidth are programmed into the core in order to support multi-mode, multi-band operation.

In addition to solving the problem of multi-mode, multi-standard radio design, software-defined radios become drivers of cognitive radio systems. Cognitive radio refers to the concept of intelligent radios that sense a wide spectrum (e.g. 500MHz) and locate available bandwidth not in use by the primary users of that spectrum [Hay05]. This available bandwidth is then open for transmission or reception by the secondary user employing the cognitive radio. A cognitive radio system has two main components. The first is a spectrum sensing processor that identifies the location and span of the available bandwidth. The second component is a flexible radio transceiver that adjusts its RF carrier and signal bandwidth so as to tune itself to the position of the available band. The software-defined radio terminal is ideally suited to act as this flexible radio transceiver.

Both the receiver and transmitter have distinct challenges associated with their design when it comes to incorporating flexibility and processing signals over a wide bandwidth. First, on the receiver side, a highly linear ADC is needed to support wideband digitization across a spectrum spanning a few GHz. Not only must the ADC digitize the signal of interest, but it must also ensure that any blockers and interference present in the received wideband signal do not degrade the quality of the signal of interest. To achieve this without any narrowband filtering operations before the ADC is tough and demands dynamic range requirements that supersede the maximum dynamic range mandated by the target radio standards. Second, adding to the tough ADC specifications is the challenge of realizing a software-defined processor core that can effectively condition the multi Gs/s ADC output. If the software core is to ideally replicate the traditional radio receiver tasks of mixing, lowpass filtering, and decimation, then we are looking at 10-14 bits of digital signal processing (DSP) starting at a few Gs/s. To put this requirement into perspective, a typical DSP processor from TI can only handle a maximum of 350MHz clock rate [Ins08]. A third challenge is to move towards greater CMOS integration and implement all RF components in scaled technology. This would enable a system-on-chip realization of the entire transceiver chain that includes

the front-end and the baseband modem. In the next section we look at various solutions proposed to enable a fully-flexible integrated radio receiver.

#### **1.1 Flexible Radio Receivers**

Although the dream of a truly software-defined radio receiver has not yet become a reality, several versions of flexible radio receivers, demonstrating varying degrees of success, have been implemented. The original effort [GNS09] was to incorporate flexibility in the RF and analog filters that are part of a traditional analog front-end. The flexible characteristics were realized using a matrix of active and passive components inside the filters. The overall baseband selectivity could be switched between 3<sup>rd</sup>- and 5<sup>th</sup>-order by reconfiguring the filters. This approach was limited due to the fixed set of filter configurations that could be realized from the component matrix. Also, incorporating flexibility in analog components. In addition, the bulky nature of analog filters, the intrinsic non-linearity of the components, low dynamic range, and poor scaling of power with new technology generations make the design process extremely challenging.

A second approach implemented the filtering operation using discrete-time switched-capacitor circuits [MHM05], [SLE08] to alleviate the problems posed by analog components. This class of receivers uses discrete-time analog signal processing to downconvert, downsample, and filter the received signal. The processing occurs on RF data sampled at the carrier Nyquist rate, without analog-to-digital conversion [MS04]. The objective is to sufficiently suppress the out-of-band interferers in the received signal before the signal can be passed onto the ADC for digitization [BMC06], [MCB09]. This approach significantly lowers the dynamic range required by the ADC since the ADC only has to process the signal of interest in a small bandwidth. The frequency response of the switched capacitor filters is varied by tuning their capacitor sizes and sample rates. Overall, the flexibility achieved with discrete-time processing is much wider compared to using fixed set of analog components.

Another interesting use of discrete-time signal processing was made in [RDB08], where the authors used a pre-processing unit that uses discrete-time Fast Fourier Transform (FFT) before

digitization. The idea was to implement filtering of the received signal in the frequency domain by first taking the FFT of the signal, and then selecting the frequency bands of interest from the FFT output. A 4096-point analog FFT with sample rate at 5 Gs/s was used to accommodate RF carriers up to 5GHz. Once the FFT output samples are digitized, they must pass through an inverse FFT operation in the digital domain that brings the samples back to the time domain.

But RF receivers still lacked the capability to scale in performance and area with advanced CMOS technologies. The concept of digitally assisted front-ends has made this scaling possible with the advantage of fine-grain tunability of the components in the receiver chain [HMS05], [HZS08]. Digitally assisted front-ends use DSP components to implement signal-conditioning circuits in the RF receiver chain. In addition to being low cost and low power, digital components are more flexible. Reprogramming the frequency response of digital filters can be done on-the-fly by changing tap coefficients or bypassing cascaded stages.

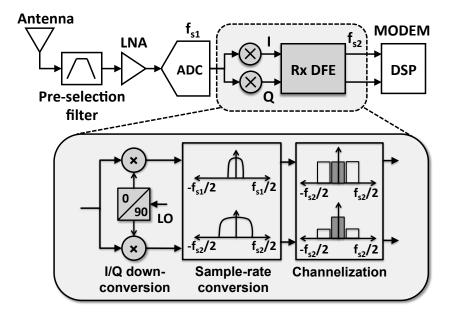

In this work, we adopt an approach similar to the software-defined radio terminal of Figure 1.2, where a high-speed ADC is followed by a processor core, except that instead of using a generic FPGA/DSP processor we use a specialized digital front-end (DFE) expressly suited for performing RF signal-conditioning operations. A conceptual view of this front-end is shown in Figure 1.3. The RF signal received from the antenna is pre-filtered by a wide bandwidth RF filter, amplified, and digitized using a high-speed, high dynamic range ADC. The ADC is optimized to maximize its performance in the bandwidth of interest around the target RF carrier. The digital front-end unit first downconverts the digitized signal by mixing it with the RF carrier. The next task is to downsample the signal from the ADC sample rate of  $f_{s1}$  to the modem sample rate of  $f_{s2}$ . In the downsampling process, the DFE must lowpass filter the signal to minimize noise injection in the baseband, which occurs due to aliasing. Lowpass filtering is also necessary for channel selection, when the unwanted channels in the received signal are attenuated. The DFE must ensure that the combined effect of finite wordlength processing and sample-rate conversion does not degrade the noise figure of the receiver chain to levels below the target specifications of the receiver.

The block diagram in Figure 1.3 shows the ADC directly digitizing the received signal without any significant pre-conditioning. There have been other versions of digitally assisted front-ends where mixing and lowpass filtering is done before digitization. For example, the work in [HMS05]

Figure 1.3: Conceptual digitally intensive radio receiver terminal.

proposed mixing of the RF signal in the analog domain, followed by analog lowpass filters and an ADC operating at a fixed rate of 104 Ms/s. Subsequent signal conditioning like channel selection, additional filtering, and downsampling is done digitally using DSP components that constitute the DFE. This approach lowers the burden on the ADC, which can now operate at lower dynamic range since a significant part of the received signal has been filtered in the analog domain. In essence this is similar to the discrete-time signal processing approach where the switched capacitor filters attenuated the out-of-band content in the received signal before digitization. However, we still face the problem of implementing analog mixers and lowpass filters that do not scale well in power or area. Hence our objective is to move the ADC as close to the antenna as possible, as is shown in Figure 1.3, and enable a direct-sampling receiver.

A direct sampling receiver samples and digitizes the bandpass RF signal at GHz rates and subsequent DSP blocks in the digital front-end, operating at high input sampling frequency, realize the downconversion and filtering. The main advantage of this approach lies in avoiding the use of bulky analog filters and mixers and having a fully reconfigurable front-end that scales in power and area with advancement of technology. The ADC, however, must operate at GHz sample rates with high dynamic range, making it very power hungry. Energy efficiency is therefore critically

important for the ADC. Implementing energy-efficient DFEs is also very challenging given the high throughput requirements of the digital mixer and filters that process the GHz-rate ADC output.

An example of such a conceptual multi-mode radio terminal, fully configurable through parameters in a digital front-end was presented in [HZS08]. This work proposed the use of a 17-bit ADC with 100dB dynamic range to cover standards like EDGE, IS-95, and UMTS between 0-5GHz. Such an ADC, however, is infeasible in present-generation CMOS at power levels ranging around a 100mW that is necessary for portable handset type of applications. With future scaling of CMOS, ADCs are expected to improve in sample rate and operate at reduced power levels and it is likely that such ADCs will become feasible with advancing technology. In present technology, however, a fair compromise is to reduce the range of RF carriers and radio standards such that an ADC with reasonable power consumption can handle the required wideband digitization. The work in [BAM09] presented an example of such an ADC operating up to 2.4GHz RF carrier and 20MHz signal bandwidth with an SNDR (signal to noise plus distortion ratio) of 37dB and a maximum power consumption of 26mW. Although the SNDR and dynamic range for this work was lower than the required 10-12 bits we need for standards like WCDMA and LTE, this work was a good indicator of the kind of ADC architectures needed to digitize narrowband radio signals at high sample rates.

In this thesis we analyze a high-speed direct-sampling receiver (Figure 1.3) and demonstrate the physical implementation of an energy-efficient digital front-end processor. The focus is on the system-level realization of a direct-sampling receiver that includes a pre-selection filter, a highspeed ADC, and a low-power DFE. We model a continuous-time  $\Sigma\Delta$  ADC architecture and show that its SNR performance is ideally suited for implementation in a direct-sampling receiver. We also derive the specifications of the passive bandpass LC filter that will be required before the ADC in order to pre-filter the RF signal before digitization. And finally, we look at the micro-architecture and system design of a digital front-end that can be coupled with the modeled ADC to perform all the signal conditioning operations digitally and handoff data to the baseband MODEM. In the next section we switch gears and discuss the second problem of flexible radio transmitter design.

Figure 1.4: Traditional radio transmitter front-end and the ideal software-defined radio Tx.

### **1.2 Flexible Radio Transmitters**

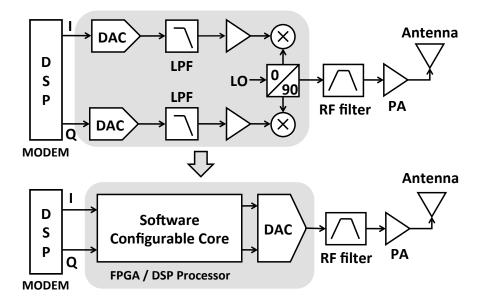

On the transmitter side, the ideal software-defined radio terminal can be visualized as shown in Figure 1.4. The challenge here is to get the baseband signal modulated at the RF carrier without leaking energy beyond the mandated threshold (defined by the strictest radio standard) in the adjacent radio bands. Traditionally, the radio transmitter uses a low-sample rate D/A converter to transform the baseband digital signal, sampled at rate  $f_{s2}$ , to the analog domain. Images of the baseband signal present at multiples of  $f_{s2}$  need to be suppressed after D/A conversion. Analog lowpass filters perform this suppression, following which the signal is mixed with the RF carrier. Additional RF filtering after mixing ensures that the transmitted signal adheres to the spectral emission mask and receive band noise specifications for frequency division duplex (FDD) operations. Finally, the transmitted signal is processed by a power amplifier that increases the output power level (~20dBm), before being passed to the antenna for transmission. Non-linear components in the Tx chain inject noise in the baseband signal that degrades the error vector magnitude (EVM) [MRM04] of the transmitted signal, ultimately leading to a degraded bit error rate [Bre03] on reception. The transmitter must restrict the extent of this noise injection to ensure that the EVM remains below levels required by the target radio standard.

A fully flexible, multi-mode, software-defined radio terminal replaces the analog lowpass filters and mixers, relying on a high-speed, linear DAC to transform the RF modulated waveform to the analog domain. The software-defined core will have to function at high sample rates in order to attenuate the baseband images to power levels lower than the emission mask and upconvert the baseband data to the RF carrier frequency. For a purely digital mixing process, the software core must upsample the baseband data to at least twice the RF carrier frequency, which translates to greater than 4Gs/s for RF carriers higher than 2GHz. FPGA or DSP processors, however, cannot perform this throughput-intensive task in present technology. Hence the best trade-off is to follow the approach we took on the receiver side and design a digital front-end tailored to perform the tasks of a flexible transmit modulator.

In this context, three classes of RF modulators have emerged:

- Outphasing modulators

- Polar modulators

- Linear modulators

The polar and outphasing modulators promise greater efficiency in the power amplifier (PA) stage since they resort to the use of nonlinear PAs that process constant-envelope phase-modulated signals. This is made possible by transforming the original I and Q baseband data to an alternate dimension.

Figure 1.5: Outphasing transmitter (a) Defining the signal vectors (b) Power amplifiers.

The modulator for an outphasing PA [HLA09a] converts any arbitrary modulation, which has amplitude and phase information, into two phase-modulated waveforms. The phase-modulated waveforms, which have constant and equal amplitude but varying phase, when combined together regenerate the amplitude and phase information present in the original signal. As shown in Figure 1.5, the phase modulation is performed on  $\theta$ , and the outphasing angle,  $\phi$ , is responsible for amplitude modulation. The outphasing signals  $S_1$  and  $S_2$  are created by transforming the original signal **S** into two constant-envelope signals with phase ( $\theta + \phi$ ) and ( $\theta - \phi$ ). In the first step, a VCO generates the carrier, whose phase varies with  $\theta$ . This phase-modulated carrier then branches into two paths that delay and advance the phase of the input by  $\phi$ . The two signals are amplified by two independent PAs and combined at the PA outputs. This approach requires precise matching of the signals during their recombination in order to successfully generate the original waveform. A slight gain or phase mismatch between the two paths can result in significant distortion and spectral re-growth in the adjacent bands.

In a polar modulator [SRM03] the I, Q components are transformed to the polar (R,  $\theta$ ) domain and combined in a single output PA, as shown in Figure 1.6. The phase signal,  $\theta$ , is passed to an alldigital PLL (ADPLL) that synthesizes the RF carrier frequency along with the phase modulation, given by the variation of  $\theta$  with time. A constant envelope signal, phase modulated by  $\theta$  is input to a saturated PA. The component R drives a DC-to-DC switching converter, the output of which modulates the PA supply voltage.

In the polar modulator the amplitude signal, R, and the phase signal,  $\theta$ , undergo completely different sets of signal processing steps before being combined in the PA. The recombination of the

Figure 1.6: Polar modulator combines the amplitude, *R*, and phase,  $\theta$ , signals in the PA.

amplitude and phase signals is compromised due to the inherent filtering and different signal processing on each path, resulting in distortion of the final output. The results presented in [KRS08] demonstrate the sensitivity of the polar architecture to the timing alignment of the phase and amplitude paths. It is also challenging to implement a linear, highly efficient, and wideband supply modulator, which is needed for this approach unless we choose to use a pre-driver circuit before the PA to combine the amplitude and phase signal, as was done in [SWR05], [BMK11]. The predriver approach, however, will require a linear power amplifier (PA) that results in loss of output efficiency in the PA stage.

The linear modulator, on the other hand, does not rely on any transformation of the (I, Q) data to an alternate dimension. Hence it does not suffer from the problem of mismatches during the direct combination of the (I, Q) components. The price to pay in this case is the use of a linear PA in the output stage that results in an overall lower efficiency of the transmitter [HLA09a]. But the linear modulator has several benefits to compensate for this loss. In addition to being versatile, linear modulators can support complex modulations like 64-QAM as well as OFDM type of data multiplexing [PZH08]. They are not constrained by the bandwidth limitations of the polar modulator and are therefore an attractive solution for high data rate communication systems.

As mentioned before, the signal processing in a linear transmitter occurs in the Cartesian coordinate system on the I and Q components of the symbols. The attractive trends of speed and power scaling of digital CMOS, coupled with the relative ease of its system integration, has encouraged the digitization of the linear transmitter. Digital signals, however, are rife with quantization noise and also have images of the baseband signal present at multiples of the modem sample rate  $f_{s2}$ . The transmitter must suppress these images and quantization noise in the RF spectrum to ensure that the output signal satisfies emission mask requirements. This requirement sets a maximum limit on the transmitted power levels in frequency bands away from the signal of interest.

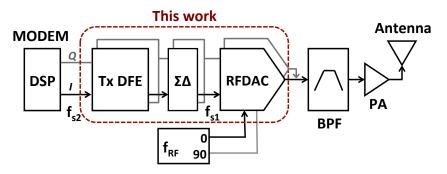

The basic signal processing flow of a digitally intensive linear modulator is shown in Figure 1.7. The (I,Q) components are upsampled, lowpass filtered, and combined in an RFDAC, which is responsible for D/A conversion as well as upconversion of the baseband data to the RF carrier frequency. The baseband signal from the modem at sample rate  $f_{s2}$  is upsampled by the Tx digital front-end (DFE) to a higher sample rate  $f_{s1}$ . In the process it filters the images of the baseband

Figure 1.7: Basic signal flow in a linear modulator.

signal present at multiples of  $f_{s2}$  to ensure that the images do not violate the emission mask. The DFE also performs fractional sample-rate conversion if the frequency  $f_{s1}$  and  $f_{s2}$  are not related by integer factors. The DFE architecture can be designed to include tuning parameters that vary attenuation characteristics, upsampling ratios, signal bandwidths, and extent of quantization noise suppression. The RFDAC following the DFE is a current-steering D/A converter as well as a mixer. The I and Q current signals centered on the RF carrier are combined at the output of the RFDAC.

The wordlength of the digital samples input to the RFDAC and the sample rate  $f_{s1}$  are important factors that determine whether the quantization noise and amplitude level of the images in the RF spectrum are sufficiently low. Noise suppression can be guaranteed if the digital word in the data stream is sufficiently wide, since quantization noise power is inversely proportional to the number of bits. The work in [BMK11] uses a 17-bit RFDAC to ensure that noise suppression is achieved for a 5MHz bandwidth signal without the aid of an on-chip bandpass filter. The work in [ESK07] uses digital signals as wide as 10-bits and sampled at 307.2Ms/s to achieve an acceptable noise level of 56dB in the adjacent band, and image suppression of 44dB at 5MHz signal bandwidth. The low sample rate of 307.2Ms/s is sufficient to ensure 44dB suppression for a 5MHz signal, but the sample rate will have to increase significantly (more than linear) for higher bandwidth

signals. Also, longer wordlengths lead to higher power consumption in the RFDAC. Increasing wordlength also increases the probability of mismatches in the unit current cells used in the D/A converter [AGA04] that ultimately degrades the linearity of the DAC.

A proposed solution to the problem of reducing wordlength in the RFDAC is the use of  $\Sigma\Delta$  modulation [PZH08]. This technique reduces the DAC resolution while shaping the added quantization noise away from the signal of interest. An RF bandpass filter following the RFDAC can filter out the additional out-of-band quantization noise introduced by the  $\Sigma\Delta$  modulator (SDM).  $\Sigma\Delta$  modulation is a promising step towards enabling low-power digital-to-RF signal generation, but conventional modulators [PZH08], [HLA09b] require a high degree of signal oversampling. Oversampling is needed to improve the in-band SNR of the transmitted signal and also to increase the 3 dB bandwidth of the RF bandpass filter, shown after the D/A convertor in Figure 1.7, and enable its on-chip integration. Higher sampling frequency, however, increases the power consumed in the digital blocks, since power consumption is directly proportional to the sample rate.

In [HLA09b] the authors use a sample rate of 4 times the RF carrier ( $f_{s1} = 4Gs/s @ f_{RF} = 1GHz$ ) with a 1-bit  $\Sigma\Delta$  output for a 5MHz QPSK modulated signal. Although this approach results in a 1-bit DAC, it limits the range of RF carriers due to the high oversampling ratio of  $4f_{RF}$ . The work in [PZH08] uses a DFE that upsamples the baseband data to  $2f_{RF}$  ( $f_{s2} = 5.4Gs/s @ f_{RF} = 2.7GHz$ ) before being processed by an SDM and RFDAC. The high DFE output sample rate enables the use of a low  $3^{rd}$ -order  $\Sigma\Delta$  modulator and a low-Q bandpass filter. This approach, however, suffers from high power consumption of close to 100mW in the digital core (DFE + SDM) that is a result of processing digital data at rates of 5.4Gs/s.

In this work we aim to improve the power efficiency of the digital core while also ensuring that a passive integrated BPF can eliminate any spectral noise that violates the emission mask after D/A conversion. This was achieved through co-optimization of the noise transfer function in the  $\Sigma\Delta$  modulator and the bandpass filter response such that we minimize the sample rate,  $f_{s1}$ , as well as the DAC resolution. The  $\Sigma\Delta$  modulator lowers the sampling frequency for a given RF filter bandwidth through the use of an FIR noise shaping filter. This allows the DFE and SDM to operate at a relatively low frequency of  $f_{RF}/3$  ( $f_{s1} = 900$ Ms/s @  $f_{RF} = 2.7$ GHz). We also use a time-interleaved RFDAC architecture that aids in filtering the out of band quantization noise. The

quantization noise introduced by the SDM is suppressed to some extent (~20dB) by the inherent filtering operation of the 2-channel time-interleaved DAC. An integrated RF bandpass filter can then filter out the remaining noise. Consequently, the digital chain functions at a reduced sample rate and switching power without compromising the extent of on-chip integration of the transmitter.

### 1.3 Thesis Outline

This thesis continues with a discussion on the choice of ADC architectures and optimization techniques in Chapter II and is followed by the design of a high-speed energy-efficient DFE processor in Chapter III. We take a detailed look at the digital components in the transmitter chain in Chapter IV. This will include a discussion on the FIR noise shaping employed in the  $\Sigma\Delta$  modulator. Chapter V will talk about the architecture and filtering effects of the time-interleaved RFDAC. This is followed by a description of the prototype test chips for the Rx DFE and the RF transmitter fabricated in 65nm CMOS and their measured results in Chapter VI.

# **CHAPTER 2**

## A/D Converters for Flexible Receivers

A fully reconfigurable direct-sampling radio receiver covering standards like GSM, EDGE, UMTS, WLAN, and LTE will need to cover all the specifications listed in Table 2.1. The specifications demand support for RF carriers between 450MHz-5GHz, channel bandwidths of upto 40MHz, and dynamic range of 90dB, if we look at the strictest requirement of the individual standards. In scenarios where the wideband system has to process several strong radio signals, the dynamic range requirements get worse. According to the work in [HMS05], the digitization process for such a multi-standard radio receiver terminal will require an ADC operating at 10GHz with 17 bits of resolution.

Such an implementation is infeasible in present technologies with acceptable power levels for portable handset type of applications. So we restrict the scope of our work to RF carriers up to 2.7GHz, signal bandwidths of 20MHz, and standards like WiMAX/LTE that require 10-12 bits at

| Standard      | Carrier<br>Frequency<br>(MHz) | Channel Bandwidth   | ADC Dynamic<br>Range (dB) |

|---------------|-------------------------------|---------------------|---------------------------|

| GSM           | 380-1900                      | 200kHz              | 90                        |

| EDGE          | 850-1900                      | 200kHz              | 87                        |

| GPRS          | 850-1900                      | 200kHz              | 84                        |

| CDMA2000      | 450-2100                      | 1.228MHz            | 80                        |

| W-CDMA / UMTS | 728-2690MHz                   | 3.84MHz             | 70                        |

| IEEE802.11a   | 5150-5825                     | 20MHz               | 55                        |

| IEEE802.11b   | 2400-2495                     | 20MHz               | 55                        |

| IEEE802.11n   | 2400/5000                     | 20/40MHz            | 55                        |

| LTE           | 728-3800MHz                   | 1.4/3/5/10/15/20MHz | 76/72/70/70/70/70         |

Figure 2.1: RF carriers, channel bandwidths, and dynamic range requirements for various radio standards.

the MODEM input over a 20MHz wide signal band. For wideband digitization, the actual dynamic range will have to be higher than 12 bits, since we not only have to digitize the signal of interest but also ensure that any strong signals/blockers present in the received signal, which contains several different RF channels, do not distort the signal of interest. Hence the target dynamic range has to be greater than 12 bits with a margin of at least 6-10dB to accommodate such wideband sampling. A  $\Sigma\Delta$  ADC was the preferred choice due to the oversampled nature of the digitization process, and also because of its expected lower power consumption.

System-level decisions regarding the ADC sample rates, number of bits, and order of  $\Sigma\Delta$  modulation go a long way in determining whether the SNR specifications of various radio standards can be achieved at power levels of 50 to 100mW. The ADC sample rate is the most important variable, since it not only determines the operating frequency of the ADC, but also that of the subsequent blocks in the DFE chain. The ADC sample rate has a close relation with the RF mixing process, which is done immediately after digitization.

Mixing is the process of translating the RF modulated data to the baseband. When we sample a continuous-time signal at a finite rate of  $f_{s1}$ , blocks in the analog spectrum spanning a frequency of  $f_{s1}$  fold back in the digital domain to be centered between  $-f_{s1}/2$  and  $+f_{s1}/2$ . An RF signal modulated at carrier  $f_{RF}$  has an RF bandwidth of  $2f_{RF}$ . According to Nyquist criterion, the signal must be sampled at rates above  $2f_{RF}$ . But sampling at twice the Nyquist rate is not mandatory for radio applications, since the signal bandwidth is restricted to only several MHz (20MHz). We can undersample at a rate  $f_{s1} < 2f_{RF}$  and still obtain a replica of the signal.

This process is shown for two combinations of  $f_{RF}$  and  $f_{s1}$  in Figure 2.2. In Figure 2.2(a), the ADC sample rate is greater than  $2f_{RF}$  resulting in the RF data positioned at  $f_{RF}$  before and after digitization. In Figure 2.2(b) we undersample the signal at  $f_{s1} = 2f_{RF} - W$ , which is lower than  $2f_{RF}$ . This results in an image of the original RF data at  $(f_{s1} - W)/2$  after digitization. The noise level, shown in dark grey, rises after undersampling in the second case, since the fixed quantization noise power spreads in a smaller frequency range. In the first case, the digitized RF samples have to be multiplied by the sine and cosine of  $f_{RF}$  during mixing, while in the second case the multiplication is done with the sine and cosine of  $(f_{s1} - W)/2$ . But implementing a digital mixer at the GHz sample rate of  $f_{s1}$  becomes either timing infeasible or very power inefficient for a multi-bit ADC output.

Figure 2.2: ADC sampling (a) Nyquist criterion ( $f_{s1} > 2f_{RF}$ ) (b) Undersampling ( $f_{s1} = 2f_{RF} - W$ ).

In this scenario, the second case of undersampling can be exploited to make the mixing operation trivial after digitization.

A special case is when  $f_{s1} = W = f_{RF}$  and the signal can be translated to the baseband directly after sampling. This seems like an attractive solution, but since there is no distinct mixer following the ADC, we will now need two ADCs, one for the I path and the other for the Q path. Both paths are sampled by clocks that are  $\pi/2$  out of phase to generate the I and Q samples at the baseband. Having two ADCs, however, will result in mismatches between the characteristics of the two converters, leading to I/Q imbalance in the baseband data.

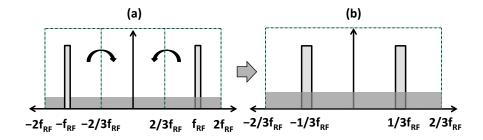

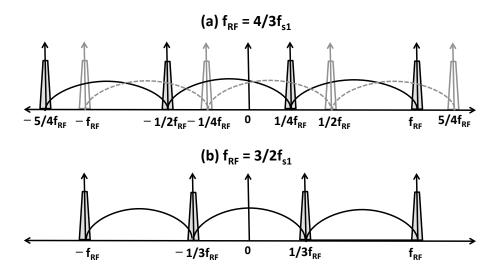

A second solution is when  $f_{s1} = 4/3f_{RF}$  and  $W = 2/3f_{RF}$ , resulting in an image of the signal at  $1/3f_{RF}$ , shown in Figure 2.3. For a sample rate of  $f_{s1} = 4/3f_{RF}$ , the frequency of  $1/3f_{RF}$  corresponds to the  $\pi/2$  position in the digital domain. This implies that the ADC output has to be multiplied with samples of  $sin(\pi/2 \cdot n)$  and  $cos(\pi/2 \cdot n)$ ,  $n \in I$ , during mixing. These functions are repeated sequences of  $\{1, 0, -1, 0\}$  that make the mixing operation trivial. The mixing can then be implemented using just a multiplexer that either selects the input, its compliment, or a zero depending upon a control signal from a counter. This solution only needs a single ADC and hence avoids the problem of I/Q imbalance. The penalty is an increased sample rate of  $4/3f_{RF}$  which is 33% larger than the first case of  $f_{s1} = f_{RF}$ , but the advantage lies in using a single ADC instead of two ADCs that were needed

Figure 2.3: (a) Undersampling at  $f_{s1} = 4/3f_{RF}$ . (b) RF data centered at  $\pi/2$ .

in the first case. Hence we chose a sample rate of  $f_{s1} = 4/3 f_{RF}$  in this work. Before we move on to selecting the ADC topology, it is worthwhile to review the basics of  $\Sigma\Delta$  modulation that will be used extensively throughout this chapter.

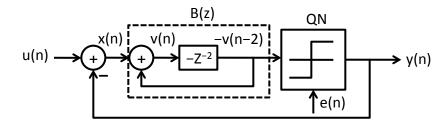

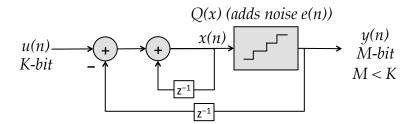

#### **2.1** $\Sigma \Delta$ Modulation

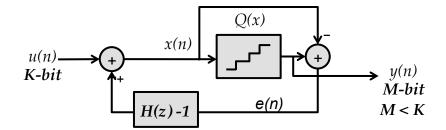

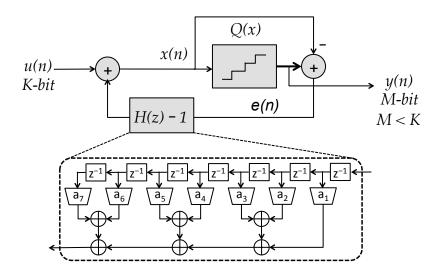

Since the ADC sample rate is  $4/3f_{RF}$  and the RF data is positioned at  $1/3f_{RF}$  (not DC) after digitization, we need a bandpass  $\Sigma\Delta$  modulator. An example of a 2<sup>nd</sup>-order bandpass  $\Sigma\Delta$  modulator is shown in Figure 2.4. The modulator uses a bandpass filter B(z) to shape the quantization noise e(n) introduced by the 1-bit quantizer QN. The quantization occurs on samples of -v(n-2), which is a result of bandpass filtering x(n), the difference between u(n) and y(n). The overall effect is to shape the added quantization noise, e(n), away from the signal of interest, which is the bandpass input signal u(n). The modulator transfer function is derived in equations 2.1-2.6.

Figure 2.4: A 2<sup>nd</sup>-order bandpass  $\Sigma\Delta$  modulator with 1-bit quantizer.

$$x(n) = u(n) - y(n)$$

(2.1)

$$v(n) = x(n) - v(n-2)$$

(2.2)

$$y(n) = -v(n-2) + e(n)$$

(2.3)

$$v(n) = u(n) - e(n)$$

(2.4)

$$y(n) = -u(n-2) + e(n-2) + e(n)$$

(2.5)

$$Y(z) = -z^{-2}U(z) + E(z)(1+z^{-2})$$

(2.6)

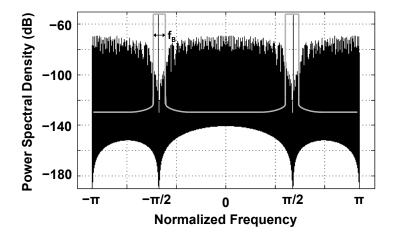

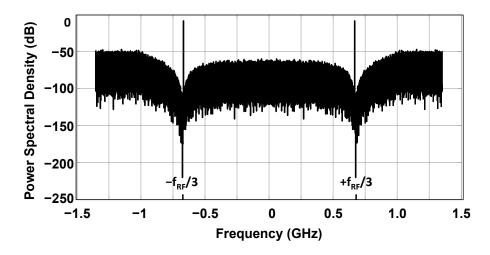

From the z-transform of the output we can see that Y(z) is a combination of the input U(z)and the filtered noise,  $E(z)(1 + z^{-2})$ . The function  $(1 + z^{-2})$  has notches at  $\pi/2$ , a desirable property since the input signal U(z) is centered at  $\pi/2$ . The power spectral density of the  $\Sigma\Delta$ modulator output for a sinusoidal input is shown in Figure 2.5. We can see that the notches at the  $\pm \pi/2$  position shape the quantization noise away from the sinusoid, thus maximizing the SNR in a limited bandwidth around the signal of interest. The excess noise can be filtered away and after decimation we get the spectral content in the bandwidth marked f<sub>B</sub>.

The primary variables that affect the noise performance of the  $\Sigma\Delta$  modulator are the oversampling ratio (f<sub>s1</sub>/2f<sub>B</sub>), the number of output bits, *M*, in the quantizer, and the order of modulation, *N*.

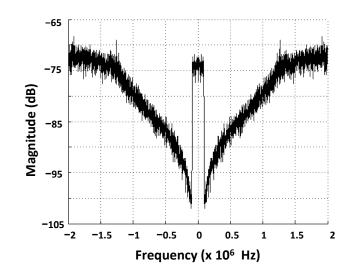

Figure 2.5: Power spectral density of a  $2^{nd}$ -order bandpass  $\Sigma\Delta$  modulator with 1-bit output.

The order of modulation is determined by the order of the noise shaping function. For example, the noise shaping function  $(1 + z^{-2})$  implies second-order modulation. Since we fixed the sample rate of the modulator at 4/3f<sub>RF</sub>, the design variables are now restricted to the order, *N*, and the number of output bits, *M*. A third variable available to us is the choice between a discrete-time modulator and a continuous-time modulator. In a discrete time-modulator the sample and hold operation is performed outside the  $\Sigma\Delta$  loop. The modulator in Figure 2.4 is an example of a discrete-time topology. On the other hand, in a continuous-time modulator the sampling operation is done at the input of the quantizer inside the  $\Sigma\Delta$  loop. We take a look at the trade-offs associated with these design variables in the next section.

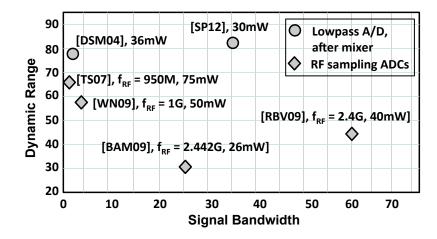

# 2.2 ADC Architectures

Various ADC architectures with varying sample rate, number of output bits, and order of  $\Sigma\Delta$  modulation can be implemented and a summary of published results is presented in the graph in Figure 2.6. We show a comparison between 2 classes of ADC architectures in Figure 2.6. The first, shown by circles, are lowpass ADCs that process baseband signals, and are preceded by a mixer. These represent the A/D converters used in conventional radio chains. The power numbers for references [SP12], [DSM04] are doubled from that of the published results to account for their usage in both I and Q channels. The second class, shown by diamonds, are ADCs that directly digitize

Figure 2.6: Comparison of various ADC architectures.

the RF signal before down conversion and are suitable for use in direct sampling receivers, and all of these use  $\Sigma\Delta$  modulation in one form or another [TS07], [WN09]. It is apparent that the RF sampling ADCs must improve in dynamic range in order to meet the specifications of prevalent radio standards. Realizing a power-efficient, high dynamic range, and high-speed ADC within a limited power budget is one of the biggest bottlenecks a direct sampling receiver must overcome.

Let us now narrow down on potential  $\Sigma\Delta$  ADC architectures for the direct-sampling receiver. A natural choice is the 2<sup>nd</sup>-order 1-bit  $\Sigma\Delta$  modulator, where the feedback loop is stable and the design complexity is low. This topology when implemented for continuous-time ADCs at f<sub>RF</sub> = 2.4GHz, bandwidth of 20MHz, and a sample rate of 3.2GHz only obtains a maximum SNR of 37dB [BAM09]. In order to improve SNR, we can increase the modulation order, *N* and the number of output bits, *M* in the quantizer. One approach is to keep a 1-bit quantizer and only increase the order of modulation. In [RBV09], the authors use a 6<sup>th</sup>-order bandpass 1-bit  $\Sigma\Delta$  modulator, achieving an SNDR of 40dB for a 2.4GHz RF signal and a bandwidth of 60MHz. If the modulation order is increased further for greater SNR performance, we face problems of higher power consumption, large area, and mismatch between the 2<sup>nd</sup>-order resonators that are used in the  $\Sigma\Delta$  loop. Hence, a better choice is to vary both the modulation order and the number of quantizer bits to meet the required resolution of greater than 12 bits.

In order to avoid nonlinearity and mismatch problems in the multi-bit feedback DAC, it is necessary to minimize the number of output bits in the quantizer. With this in mind, we propose a continuous-time 4-bit 4<sup>th</sup>-order bandpass  $\Sigma\Delta$  ADC. This choice of order and resolution can enable the target dynamic range of approximately 80dB in a 20MHz bandwidth. A continuous-time architecture is the preferred choice since it makes high-speed operation of the  $\Sigma\Delta$  loop feasible. The addition of an anti-aliasing filter before the quantizer is also an attractive feature of this ADC. More details on this filtering process will be presented in Section 2.4. In the next section we will look at the ADC modeling, signal and noise transfer functions, SNR variation, and the effect of circuit-level non-idealities on the ADC performance.

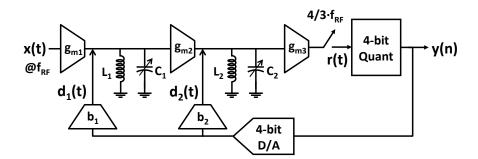

Figure 2.7: 4<sup>th</sup>-order bandpass  $\Sigma\Delta$  ADC with 4-bit quantizer. LC resonators are tuned at f<sub>RF</sub>.

# 2.3 ADC Modeling

The proposed  $\Sigma\Delta$  ADC model is shown in Figure 2.7. The input signal x(t) centered at carrier  $f_{RF}$  is applied to a transconductance amplifier ( $g_{m1}$ ) that converts the voltage waveform to a current signal. The signal is then added to the first feedback current signal,  $d_1(t)$ , from the DAC, after which it passes through a 2<sup>nd</sup>-order LC resonator centered at  $f_{RF}$ . A second transconductance amplifier ( $g_{m2}$ ) is next in the chain, followed by addition of feedback signal,  $d_2(t)$ , from the DAC and another resonator, also centered at  $f_{RF}$ . The continuous-time signal r(t) at the output of the second LC resonator is sampled at 4/3 $f_{RF}$  and passed to the 4-bit quantizer for digitization. The feedback DAC takes the quantized signal as input and generates analog feedback signals  $d_1(t)$  and  $d_2(t)$ . The capacitive component of the LC resonator is tunable to adjust the resonance frequency to variable carrier,  $f_{RF}$ .

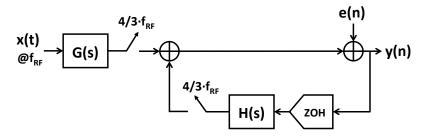

The ADC model can be simplified to the equivalent form shown in Figure 2.8, where the continuous-time input signal x(t) is pre-filtered by G(s) before being sampled at  $4/3f_{RF}$ . The feedback signal from the D/A (modeled as a zero-order-hold / ZOH) is processed by the continuous-time loop filter H(s), following which it is sampled and added to the pre-filtered samples from G(s). The output y(n) is obtained by adding the quantizer error, e(n), to these discrete samples. G(s) is the open-loop transfer function from the input x(t) to the quantizer input r(t) (Figure 2.7). From Figure 2.7, we can see that G(s) is a 4<sup>th</sup>-order continuous-time function given by:

$$G(s) = \frac{k(s + \frac{w_R}{Q})^2}{(s^2 + \frac{w_R}{Q}s + w_R^2)^2}$$

(2.7)

Figure 2.8: Simplified model of the bandpass  $\Sigma\Delta$  ADC. ZOH is the zero-order-hold function.

Here  $w_R$  is the resonance frequency of the LC tank, and Q is the selectivity of the LC resonator. Ideally, the value of Q should be infinite, but non-idealities in the resonator result in finite selectivity. The non-ideality appears in the form of an intrinsic wire resistance,  $R_W$ , which is in series with the inductor. When  $R_W$  is taken into account, the selectivity, Q, of the resonator is given by:

$$Q = \frac{w_R}{w_B} = \frac{w_R}{R_W/L} = \frac{2\pi\sqrt{L}}{R_W\sqrt{C}}$$

(2.8)

Here  $w_B$  is the signal bandwidth of the resonator and is expressed as:

$$w_B = \frac{R_W}{L} \tag{2.9}$$

The resonance frequency,  $w_R$ , in Eq. 2.8 approximately equals  $\frac{1}{\sqrt{LC}}$  under the assumption  $w_B << \frac{1}{\sqrt{LC}}$ . For a fixed implementation of the inductor, the values of  $R_W$  and L remain fixed. In Figure 2.8, H(s) is the open-loop transfer function from the D/A output to the quantizer input. The z-domain equivalent, H(z), of the loop filter transfer function can be computed by discretizing the cascaded functions H(s) and ZOH. The closed-form expression for H(z) is obtained using Eq. 2.10.

$$H(z) = Z\left\{L^{-1}\left\{\frac{1 - e^{-sT}}{s}H(s)\right\}\right\}$$

(2.10)

The function  $Z\{\}$  represents the z-transform and the function  $L^{-1}\{\}$  is the inverse Laplace

transform. The sample period T equals  $3/(4f_{RF})$ . The z-domain noise transfer function, NTF(z), of the ADC can be computed from the loop transfer function H(z) using Eq. 2.11.

$$NTF(z) = \frac{1}{1 - H(z)}$$

(2.11)

The signal transfer function, STF(w), is a combination of the pre-filter G(jw) and the noise transfer function,  $NTF(e^{jwT})$ . It is given by Eq. 2.12, which follows the derivation in [ST04].

$$STF(w) = G(jw)NTF(e^{jwT})$$

(2.12)

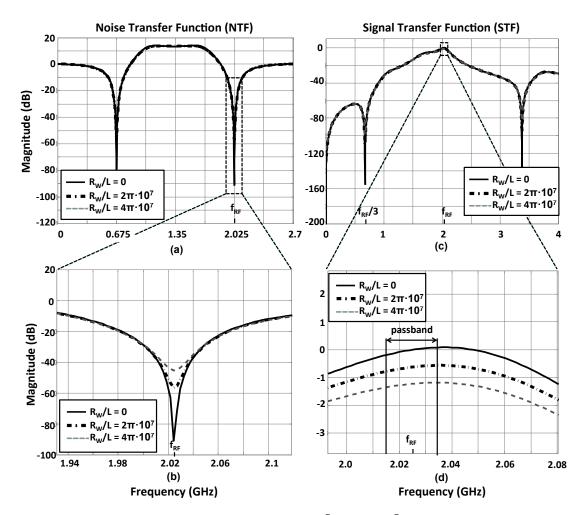

Figure 2.9: (a) Noise transfer function at  $R_W/L = 0$ ,  $2\pi 10^7$ , and  $4\pi 10^7$ . (b) Zoomed-in *NTF* shows notch at f<sub>RF</sub>. (c) Signal transfer Function at  $R_W/L = 0$ ,  $2\pi 10^7$ , and  $4\pi 10^7$ . (d) Zoomed-In *STF* shows passband around f<sub>RF</sub>.

The ratio  $R_W/L$  strongly affects the noise and bandwidth performance of the ADC. This can be observed from the variation of the *STF* and *NTF* as a function of  $R_W/L$ . Figure 2.9 plots the *NTF* at three distinct values of  $R_W/L$ . The chosen values of  $R_W/L$  corresponds to bandwidth, w<sub>B</sub>, increasing in steps of 10MHz, starting from the ideal value of 0 corresponding to infinite Q, and then going to  $2\pi \times 10 \times 10^6$  and  $2\pi \times 20 \times 10^6$ . The transfer function, evaluated at  $f_{RF} = 2.025$ GHz and  $f_{s1} = 2.7$ GHz, has notches at frequencies  $f_{RF}/3$  and  $f_{RF}$ . The solid line shows the ideal *STF* when  $R_W = 0$ . When  $R_W/L$  is increased, the notch is less steep, indicating an increase in noise power. This can be observed from the zoomed-in *NTF* shown in Figure 2.9(b), where the depth of the notch reduces from 90dB to 45dB when  $R_W/L$  is raised from 0 to  $2\pi \times 20 \times 10^6$ . The signal-transfer-function for the continuous time bandpass ADC is shown in Figure 2.9(c). The *STF* has 0dB magnitude around the resonance frequency  $f_{RF} = 2.025$ GHz, and notches around DC,  $f_{RF}/3$ , and  $5/3f_{RF}$ . The notch at DC occurs because the function G(s), in Eq. 2.7, has a zero close to DC. The notches at  $f_{RF}/3$  and  $5/3f_{RF}$  appear because of the *NTF* nulls in these bands, as can be predicted from Eq. 2.12. The variation of the *STF* with increasing  $R_W/L$  is shown in the zoomed-in plot of Figure 2.9(d). It can be seen that the peak of the response reduces with the increase in  $R_W/L$ . The passband range of 20MHz around the RF carrier is nearly flat for all 3 cases. The attenuation at the passband edge w.r.t.  $f_{RF}$  is 0.16dB for  $R_W/L = 0$ , and reduces to 0.1dB for  $R_W/L = 4\pi 10^7$ . The small droop in the passband can be corrected in the digital domain by varying the passband characteristics of the digital FIR filters in the DFE.

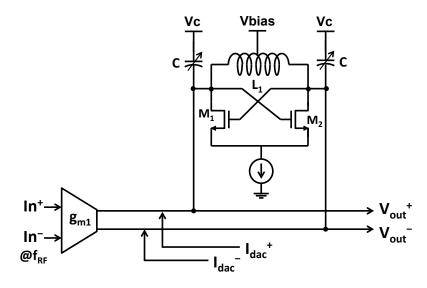

Hence, from the perspective of optimizing the *NTF* and minimizing the noise power, the target is to lower the coil resistance,  $R_W$  as much as possible. In general, it is difficult to minimize the resistance, and in practical realizations of bandpass filters, active *Q*-enhancement techniques are used. A common technique is to use a negative resistance [BAM09] in parallel with the inductor that lowers the intrinsic wire resistance of the inductor. The negative resistance is realized by using a pair of cross-coupled transistors in parallel with the LC tank as shown in Figure 2.10. The cross-coupled pair realizes a resistance of  $-2/g_m$  ( $g_{m1} = g_m = g_m$ ) parallel to the LC circuit,

Figure 2.10: Q enhancement of inductor with negative resistance realized using cross-coupled transistors  $M_1$  and  $M_2$ .

Figure 2.11: Spectrum of a 2.025GHz RF modulated sinusoid undersampled at 2.7GHz (4/3f<sub>RF</sub>). The signal replica is centered at 0.675GHz.

which reduces the effect of the coil resistance  $R_W$ . Here  $g_m$  refers to the transconductance of the transistors.

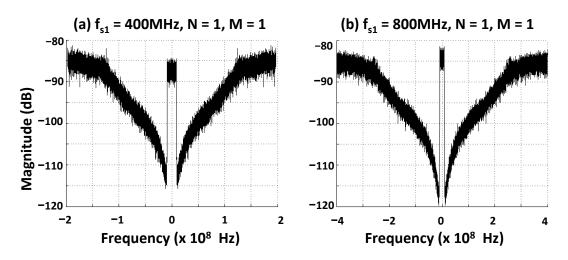

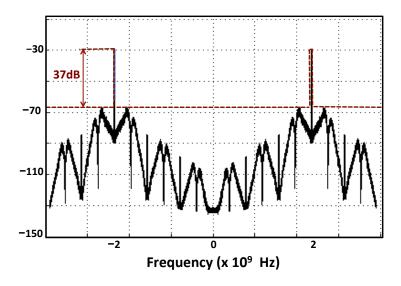

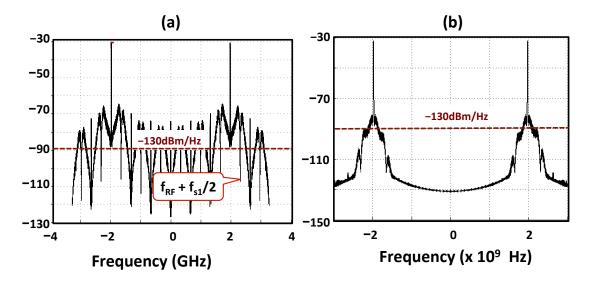

Figure 2.11 shows the power spectral density of an 8MHz sinusoid modulated at  $f_{RF} = 2.025$ GHz and digitized at  $f_{s1} = 2.7$ GHz. The noise spectrum has a notch at  $f_{RF}/3 = 675$  MHz. The  $R_W/L$ ratio for the inductors in the LC resonator sections was chosen to be  $(2\pi) \times 20 \times 10^6$ , since this value results in the ADC meeting the target SNR performance. After undersampling, the signal replica is formed at  $f_{RF}/3 = 675$ MHz. The oversampling ratio for a bandpass  $\Sigma\Delta$  ADC is given by the ratio of half the sampling frequency and the signal bandwidth,  $f_s/(2f_B)$  [NST96]. For a sampling frequency of 2.7GHz and a 20MHz signal bandwidth, the oversampling ratio of the ADC is 67.5. The maximum SNDR was 83.5dB for this example and the dynamic range was 85dB which makes it close to 14-bit resolution, providing sufficient margin for wideband digitization above the mandatory 12-bit resolution.

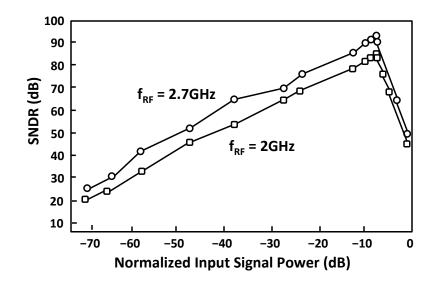

The variation of SNR with input signal amplitude at RF carriers of 2.0GHz and 2.7GHz is shown in Figure 2.12. The LC resonators were tuned to  $f_{RF}$  in each case. As expected, the SNR increases linearly with the input signal amplitude, and when operating close to maximum signal amplitude, the SNR drops due to overloading of the quantizer. For a fixed signal bandwidth, the SNR improves marginally with higher RF carrier frequency due to increase in oversampling ratio. The maximum SNR for the 2.7GHz RF signal ( $f_{s1} = 3.6$ GHz) is around 90dB, which is 6.5dB

Figure 2.12: SNR variation with input signal amplitude and RF carrier frequency.

higher than the 2.0GHz signal. A major factor that limits the achievable SNR in continuous-time ADCs is the jitter in the sampling clock. We analyze the effect of clock jitter in the next section.

### 2.4 Clock Jitter Analysis

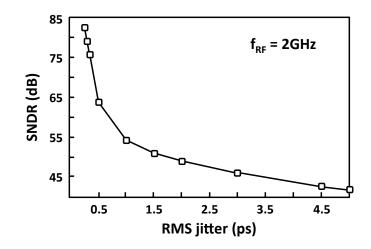

Continuous-time ADC architectures have increased sensitivity to clock jitter. We verified this by adding jitter to our simulation models and computed the SNR under the influence of a jittered clock. The clock jitter was derived from a zero-mean Gaussian distribution with a standard deviation equal to the RMS value of the clock jitter. The variation of SNR with increasing jitter is presented in Figure 2.13 for a 2GHz RF carrier and a 2.66GHz clock ( $4/3 \cdot f_{RF}$ ). The jitter was varied to a maximum of 500fs, which is 1.33% of the clock period, when the SNDR degrades to around 45dB. The results in Figure 2.13 indicate that the system can tolerate about 250-300 fs of jitter. The SNR degradation is sharp if the jitter standard deviation exceeds 300 fs.

This jitter specification can be met by integrating a low-jitter PLL with the receiver [HSP08]. Alternatively, jitter sensitivity of the continuous-time ADC can be reduced by employing a switched capacitor resistive (SCR) feedback DAC [OGM05]. The SCR DAC, however, has an exponentially decreasing feedback pulse that requires a higher peak current compared to conventional switched-

Figure 2.13: SNR degradation with increasing jitter in the clock.

current DACs, resulting in higher power consumption.

Since the undersampling ADC digitizes a limited bandwidth of  $4/3f_{RF}$ , we need a pre-selection filter before the ADC to prevent aliasing of any signal content that aligns with the desired signal after undersampling. In the next section we study the requirements of this pre-filtering operation.

## 2.5 **Pre-selection Filter**

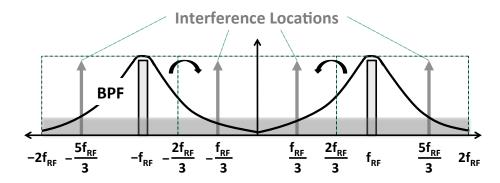

A pre-selection filter is needed before the ADC to prevent aliasing of signals outside the range  $\{2/3f_{RF}, 2f_{RF}\}$ . Undersampling of the RF signal at  $4/3f_{RF}$  will cause all spectral blocks spanning a frequency range of  $4/3f_{RF}$  to fold into the baseband. We are interested in obtaining a replica of the spectral content in the region  $\{2/3f_{RF}, 2f_{RF}\}$ . Any content outside this region needs to be attenuated so that the replica remains uncorrupted after sampling.

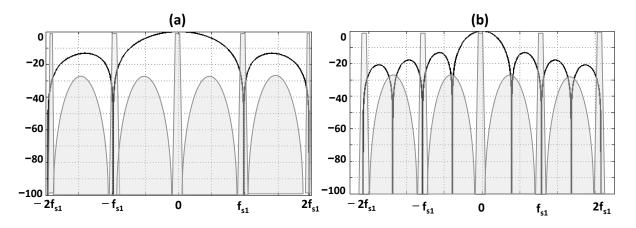

The expected attenuation characteristics of the pre-selection filter are shown in Figure 2.14. The plot shows the interference locations that alias at  $\pm f_{RF}/3$ , where the signal replica of  $f_{RF}$  eventually forms after undersampling. To ensure that the replica is formed without any corruption, the pre-selection filter must attenuate these interferences. The attenuation in the 20MHz band around the interference locations must exceed the linearity requirement at the MODEM input. Therefore the interference must be suppressed by > 72dB (12-bit linearity) with respect to the signal. The

Figure 2.14: Expected attenuation characteristics of the pre-selection filter.

anti-aliasing property of the continuous-time  $\Sigma\Delta$  ADC can be used to suppress the interferers at the aliasing locations of  $f_{RF}/3$  and  $5/3f_{RF}$ . The *STF*, shown in Figure 2.9(c), has notches at these frequencies, and will suppress any interference that can alias with the desired signal centered at  $f_{RF}$  after undersampling. Figure 2.15 shows the zoomed-in plots of the notches at  $f_{RF}/3$  and  $5/3f_{RF}$ for  $f_{RF} = 2.025$ GHz. As expected, the STF notches become less sharp with increasing values of  $R_W/L$ . At  $R_W/L = (4\pi) \times 10^7$ , we get approximately 100dB of attenuation at  $f_{RF}/3 = 675$ MHz, and around 80dB at  $5/3f_{RF} = 3.375$ GHz. At higher RF carriers, more attenuation is expected since the notches become steeper due to higher oversampling ratios. Therefore, a pre-selection filter for anti-aliasing is not necessary in this system.