# Double Flying Capacitor Multicell Converter Based on Modified Phase-Shifted Pulsewidth Modulation

Arash Khoshkbar Sadigh, *Student Member, IEEE*, Seyed Hossein Hosseini, *Member, IEEE*, Mehran Sabahi, and Gevorg B. Gharehpetian, *Senior Member, IEEE*

Abstract-Multilevel converters are very interesting alternatives for medium and high-power applications. The main reason is the increase in the number of output voltage levels and its apparent frequency. This paper presents a new configuration of flying capacitor multicell (FCM) converter. The main advantages of the proposed converter, in comparison with FCM and stacked multicell converters, are doubling the rms and the number of output voltage levels, improving the output voltage frequency spectrum, and canceling the midpoint of dc source. This progress is achieved by adding only two low-frequency switches to the conventional configuration of FCM converter while the number of high-frequency switches and capacitors, voltage ratings of capacitors and switches, and the number of high-frequency switchings during a full cycle are kept constant. This converter is controlled by a modified phase-shifted pulsewidth modulation, therefore, the self-balancing property of the flying capacitor converter is maintained in the proposed converter. The circuit is simulated using power systems computeraided design/electromagnetic transients in DC systems (EMTDC) software and simulation results are presented to validate the effectiveness and advantages of the proposed configuration as well as its control strategy. Additionally, measurements taken from an experimental setup are presented in order to study the practical configuration.

*Index Terms*—Cascaded multicell (CM) converter, flying capacitor multicell (FCM) converter, natural balance, phaseshifted pulsewidth modulation (PSPWM), stacked multicell (SM) converter.

#### I. INTRODUCTION

M ULTILEVEL converters have been continuously developed in recent years due to the necessity of increase in power level of industrial applications, especially high-power applications, such as high-power ac motor drives, active power filters, reactive power compensation, and FACTS devices [1]–[5]. The main reason is the capability of these topologies to handle voltage/power in the range of kilovolts/megawatts due to recent developments in the area of high-power semiconductors [6]–[9].

Multilevel converters include an array of power semiconductors and capacitor voltage sources, which generate output

G. B. Gharehpetian is with the Electrical Engineering Department, Amirkabir University of Technology, Tehran 15914, Iran (e-mail: grptian@aut.ac.ir).

Digital Object Identifier 10.1109/TPEL.2009.2039147

voltage with stepped waveforms. The commutation of the switches permits the addition of the capacitors voltages and generates high voltage at the output, while the power semiconductors must withstand only reduced voltages [8], [10], [11].

The term multilevel starts with the three-level converter introduced by Nabae *et al.* [12]. By increasing the number of levels in the converter, the output voltage has more steps generating a staircase waveform, which has a reduced harmonic distortion [13]. However, a high number of levels increases the control complexity and introduces voltage imbalance problems [10].

The neutral point clamped (NPC) converter, presented in the early 1980s [12], is now a standard topology in industry on its three-level version. However, for a high number of levels, this topology presents some problems, mainly with the clamping diodes and the balance of the dc-link capacitors. An alternative for the NPC converter are the multicell topologies. Different cells and ways to interconnect them generate many topologies, which the most important ones, described in Section II, are the cascaded multicell (CM) and the flying capacitor multicell (FCM) with its subtopology stacked multicell (SM) converters [11], [14].

The FCM converter [15] and [16], and its derivative, the SM converter [17]-[19], have many attractive properties for medium voltage applications, including, in particular, the advantage of transformerless operation and the ability to naturally maintain the flying capacitors voltages at their target operating levels [15], [20]. This important property is called natural balancing and allows the construction of such converters with a large number of voltage levels [21]. Natural self-balancing of the flying capacitors voltages occurs without any feedback control. A necessary self-balancing condition is that the average flying capacitors currents must be zero. As a result, each cell must be controlled with the same duty cycle and a regular phaseshifted progression along the cells. Generally, an output RLC filter (balance booster circuit), tuned to the switching frequency or multiple of that, is suggested to be connected across the load in order to accelerate this self-balancing process in the transient states and to reduce the effect of control signal faults [9], [22].

The FCM converter uses a series connection of "cells" comprising a flying capacitor and its associated complimentary switch pair and produces a switched voltage that is the sum of the individual cell states. The SM converter stacks two FCM converters together with the upper stack switching only when a positive output is required and the lower stack switching only when a negative output is required [21].

The remainder of this paper is organized as follows. Section II provides a brief summary of multicell converter

Manuscript received February 23, 2009; revised August 24, 2009 and November 2, 2009. Current version published June 3, 2010. Recommended for publication by Associate Editor A. Rufer.

A. K. Sadigh, S. H. Hosseini, and M. Sabahi are with the Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz 51664-16471, Iran (e-mail: a.khoshkbar.sadigh@ieee.org; hosseini@tabrizu.ac.ir; sabahi@tabrizu.ac.ir).

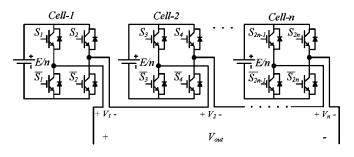

Fig. 1. 2n + 1 level CM converter with maximum output voltage value of E.

circuit topologies, their properties, and output voltages. In Section III, the new configuration based on the FCM converter and its control strategy based on the modified phase-shifted pulsewidth modulation (PSPWM) technique are proposed. The proposed configuration, called double FCM (DFCM) converter, doubles output voltage levels and rms of output voltage in comparison with FCM and SM converters; this progress is achieved by applying only two additional low-frequency switches, which work with low-switching frequency, and generally, are switched twice during a full cycle of the fundamental output voltage.

Simulation and experimental results are presented in Sections IV and V, respectively, for single-phase four-cell-nine-level proposed DFCM converter to validate the effectiveness and advantages of the proposed configuration and its control strategy.

#### II. MULTICELL CONVERTERS

## A. CM Converter

The CM converter, as shown in Fig. 1, was introduced in the early 1990s [23], [24]. This topology is based on the series connection of units known as cells with three-level output voltage. Each cell is a structure based on an isolated voltage source, therefore, a bulky and complex multisecondary input transformer is required when only one dc voltage source is available. Therefore, it causes increase in the cost and size of the converter. As the cells are connected in series, a maximum of 2n + 1 output voltage levels is obtained and the total output voltage, corresponding to the sum of each cell output voltage, is as follows:

$$v_{\rm out} = \sum_{i=1}^{n} v_i \tag{1}$$

where *n* is the number of cells connected in series.

An additional advantage of this topology is that when an internal fault is detected and the faulty cell is identified, it can be easily isolated through an external switch and replaced by a new operative cell without turning OFF the converter. However, while the replacement is done, the maximum output voltage in the faulty leg is reduced to

$$v_f = v_{\rm out} \left( 1 - \frac{f}{n} \right) \tag{2}$$

where *f* is the number of faulty cells.

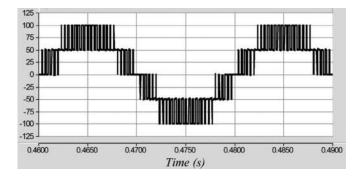

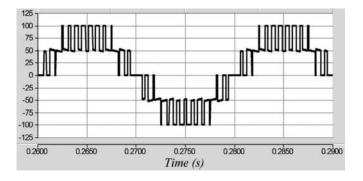

As the four-cell-nine-level CM converter is controlled by PSPWM ( $f_{\text{switching}} = 700 \text{ Hz}$ ) and operated with a modulation

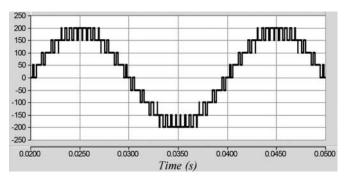

Fig. 2. Output voltage of a four-cell-nine-level CM converter (in volt).

Fig. 3. Output voltage frequency spectrum of a four-cell-nine-level CM converter.

index equal to 0.8 (M = 0.8), the output voltage with total harmonic distortion (THD) of 15% as well as its frequency spectrum are illustrated in Figs. 2 and 3, respectively.

The PSPWM, which is used in CM, FCM, SM, and proposed DFCM converters is a regular PSPWM, where the phase shift between the carriers of each cell is as follows:

$$\varphi = \frac{2\pi}{n} \tag{3}$$

where *n* is number of cells.

# B. FCM Converter

A 2*n*-cell FCM converter, as shown in Fig. 4, is composed of 4*n* switches forming 2*n*-commutation cells controlled with equal duty cycles and phase shifted of  $\pi/n$  and 2n - 1 flying capacitors with the same capacitance. As a result, the electrical stresses on each switch are reduced and more equally distributed as each switch must withstand E/n volts [25]–[27].

The output voltage of 2n-cell FCM converter has 2n + 1 level and its frequency spectrum has the harmonics around the  $(2nkf_{switching})$ th harmonic, where k and  $f_{switching}$  are the integer number and the switching frequency, respectively. All capacitors see similar current waveforms and have the same capacitance to obtain the same voltage ripple, but their dc voltage ratings are different and equal to E/n, 2E/n, ..., (2n - 1)E/n,

Fig. 4. 2n + 1 level FCM converter with maximum output voltage value of E.

Fig. 5. Output voltage of a four-cell-five-level FCM converter (in volt).

therefore, the energy stored in the capacitor *k* is as follows [26]:

$$U_K = \frac{1}{2}C\left(\frac{KE}{n}\right)^2.$$

(4)

Main advantages of a FCM converter over a CM converter are that the FCM converter does not require a complex input transformer and in the case of internal fault of one cell, the maximum output voltage remains constant, but the number of levels decreases to as follows:

$$L_f = L - f \tag{5}$$

where *f* is the number of faulty cells.

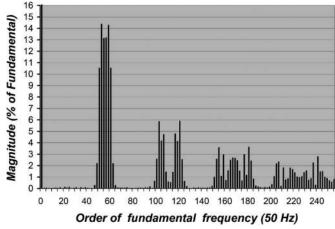

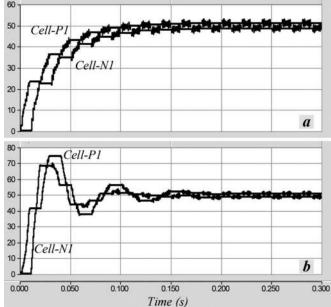

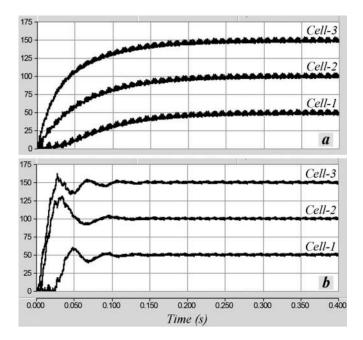

The output voltage of a four-cell-five-level FCM converter with THD of 36%, its frequency spectrum and its internal flying capacitors voltages are shown in Figs. 5–7, respectively, while the converter is controlled by PSPWM ( $f_{switching} = 700$  Hz) and operated with a modulation index equal to 0.8 (M = 0.8). Fig. 7(a) depicts the internal flying capacitors voltages for the case in which the converter load is resistive and no output *RLC* filter is applied. Fig. 7(b) is for the case in which the output load is resistive–inductive, therefore, an output *RLC* filter is needed and applied. This filter, which consists of a resistance, inductance, and a capacitance in series connection, accelerates the self-balancing process and is connected in parallel with the load. The output *RLC* filter is tuned to the switching frequency as follows:

$$\sqrt{LC} = \frac{1}{2\pi f_{\rm SW}} \tag{6}$$

where  $f_{SW}$  is the switching frequency, *L* and *C* are inductance and capacitance of the output *RLC* filter, respectively.

Fig. 6. Output voltage frequency spectrum of a four-cell-five-level FCM converter.

Fig. 7. Internal flying capacitors voltages of a four-cell-five-level FCM converter (in volt). (a) Resistive load without output *RLC* filter. (b) Resistive–inductive load with output *RLC* filter.

# C. SM Converter

An alternative topology based on the FCM converter is the SM converter; this structure uses a  $m \times n$  cells array to increase the number of output voltage levels. A  $2 \times n$  SM converter is shown in Fig. 8. The main advantages of this configuration are that the number of combinations to obtain a desired voltage level is increased (redundancy), and the voltage ratings of capacitors and stored energy in the flying capacitors as well as the semiconductor losses are reduced. However, it requires the same number of capacitors and semiconductors in comparison with the equivalent FCM converter for the same number of output voltage levels [28].

The output voltage of a four-cell-five-level SM converter with THD of 37% and its frequency spectrum as well as its

Fig. 8. 2n + 1 level SM converter with maximum output voltage value of E.

Fig. 9. Output voltage of a four-cell-five-level SM converter (in volt).

Fig. 10. Output voltage frequency spectrum of a four-cell-five-level SM converter.

internal flying capacitors voltages are shown in Figs. 9–11, respectively, while the converter is controlled by PSPWM ( $f_{switching} = 700$  Hz) and operated with a modulation index equal to 0.8 (M = 0.8). Fig. 11(a) depicts the internal flying capacitors voltages for the case in which the converter load is resistive and no output *RLC* filter is applied. Fig. 11(b) is for the case in which the output load is resistive–inductive, therefore, an output *RLC* filter is needed and applied.

Fig. 11. Internal flying capacitors voltages of a four-cell-five-level SM converter (in volt). (a) Resistive load without output *RLC* filter. (b) Resistive-inductive load with output *RLC* filter.

## III. PROPOSED DFCM CONVERTER

#### A. Converter Description

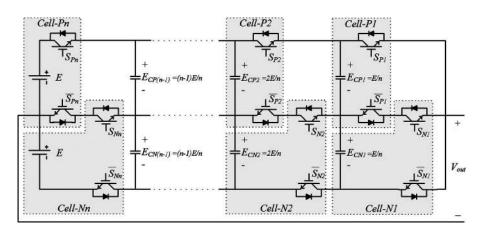

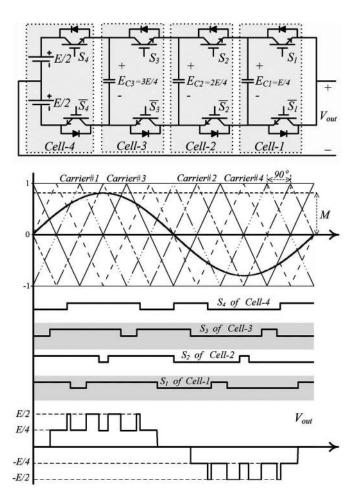

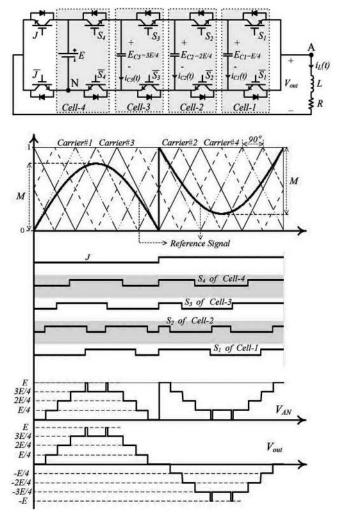

The conventional four-cell-five-level FCM converter, its control strategy based on the PSPWM and the output voltage is shown in Fig. 12. As shown in Fig. 13, two low-frequency switches  $(J, \overline{J})$  are added to the conventional configuration of FCM converter and the new four-cell-nine-level converter, called DFCM converter, is proposed. Two additional switches work with low-switching frequency, and generally, are switched twice during a full cycle of the fundamental output voltage, while the switch J is ON for negative output voltage and the switch  $\overline{J}$  is ON for positive output voltage. The proposed configuration, its control strategy based on the modified PSPWM and its output voltage is shown in Fig. 13 (see Table I for the

Fig. 12. Four-cell-five-level FCM converter's configuration, control strategy, and output voltage.

output voltage levels and switching states of four-cell-nine-level DFCM converter).

In the conventional configuration of FCM converter, as shown in Fig. 12, maximum values of positive and negative peaks of output voltage are only half of the dc source voltage, i.e.,  $\pm E/2$ , while in the proposed DFCM converter, applying the switches J and  $\overline{J}$ , makes it possible to obtain full value of the dc source voltage, i.e.,  $\pm E$  for positive and negative peaks of output voltage. As shown in Fig. 13, this achievement causes to double the rms value of output voltage and the number of output voltage levels. The effect of switch J is a negative shift of the voltage  $V_{AN}$ , equal to -E, in the second half cycle to form the output voltage  $V_{out}$ . As a result, the reference signal must be shifted one positive unit in the second half cycle to offset negative shift of the voltage  $V_{AN}$  made by switch J, as shown in Fig. 13.

The main advantages of the proposed converter, in comparison with FCM and SM converters, are doubling the rms of output voltage and the number of output voltage levels and canceling the midpoint of dc source. This progress is achieved by adding only two low-frequency switches to the conventional configuration of FCM converter, while the number of highfrequency switches and capacitors, voltage ratings of capacitors

Fig. 13. Four-cell-nine-level proposed DFCM converter's configuration, control strategy, and output voltage.

and switches and the number of high-frequency switchings during a full cycle are kept constant. Also, the frequency spectrum of output voltage is improved and its THD is reduced significantly because of doubling the number of output voltage levels.

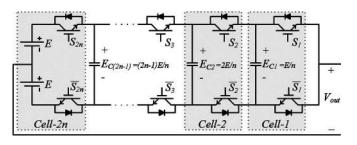

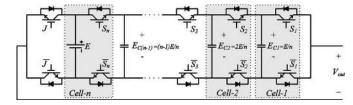

Different types of conventional multicell converters, i.e., CM, FCM, and SM converter, as well as the proposed DFCM converter for producing the identical output voltage with equal number of levels (2n + 1 level) and equal maximum value of output voltage (*E*) are displayed in Figs. 1, 4, 8, and 14, respectively. Also, comparison between the conventional multicell converters and the proposed converter is displayed in Table II for the identical output voltage with equal number of levels (2n + 1 level) and equal maximum value of output voltage is displayed in Table II for the identical output voltage with equal number of levels (2n + 1 level) and equal maximum value of output voltage (*E*).

As shown in Figs. 1, 4, 8, and 14 and Table II, the progress of doubling the rms of output voltage and the number of output voltage levels in the proposed DFCM converter makes it possible to decrease the number of flying capacitors, high-frequency switches and input dc voltage sources by 50% in comparison with FCM and SM converters. Although the number of high-frequency switches is decreased by 50% in the proposed DFCM converter in comparison with CM, FCM, and SM converters,

TABLE I Switching States of Four-Cell-Nine-Level Proposed DFCM Converter

| Output          | State |                                            |   |  |  |

|-----------------|-------|--------------------------------------------|---|--|--|

| Voltage Level   | J     | states                                     |   |  |  |

| +E              | 0     | (1,1,1,1)                                  | 1 |  |  |

| $+\frac{3}{4}E$ | 0     | (1,1,1,0), (1,1,0,1), (1,0,1,1), (0,1,1,1) | 4 |  |  |

| $+\frac{2}{4}E$ | 0     | (1,1,0,0), (1,0,0,1), (0,0,1,1), (0,1,1,0) | 4 |  |  |

| $+\frac{1}{4}E$ | 0     | (1,0,0,0), (0,1,0,0), (0,0,1,0), (0,0,0,1) | 4 |  |  |

| 0               | 0     | (0,0,0,0)                                  | 2 |  |  |

| v               | 1     | (1,1,1,1)                                  | - |  |  |

| $-\frac{1}{4}E$ | 1     | (0,1,1,1), (1,0,1,1), (1,1,0,1), (1,1,1,0) | 4 |  |  |

| $-\frac{2}{4}E$ | 1     | (1,1,0,0), (1,0,0,1), (0,0,1,1), (0,1,1,0) | 4 |  |  |

| $-\frac{3}{4}E$ | 1     | (0,0,0,1), (0,0,1,0), (0,1,0,0), (1,0,0,0) | 4 |  |  |

| -E              | 1     | (0,0,0,0)                                  | 1 |  |  |

Fig. 14. 2n + 1 level proposed DFCM converter with maximum output voltage value of *E*.

the voltage rating of switches is not changed for producing the identical output voltage, as shown in Figs. 1, 4, 8, and 14 and Table II. Also, because of producing the identical output voltage, the load current of equal load is same for all type of mentioned converters. As a result, the power rating of all high-frequency switches is equal in all type of mentioned converters. However, the power rating of two added low-frequency switches is not equal to high-frequency switches.

As shown in Fig. 14, only one dc source (or one dc-link capacitor) is needed for the dc link of the proposed converter in the single-phase applications, such as single-phase active power filter, single-phase motor drive, and/or in three-phase applications in which the each single-phase converter must be controlled separately, such as dynamic voltage restorer or unified power quality conditioner. But, two dc sources (or two dc-link capacitors) are required for the conventional configuration of FCM and SM converters in the mentioned applications, as shown in Figs. 4 and 8.

Because of adding two low-frequency switches  $(J \text{ and } \overline{J})$  to conventional FCM converter, the proposed DFCM converter is combination of H-bridge converter and FCM converter, as shown in Fig. 13. Therefore, the application of the proposed multilevel DFCM converter for three-phase load is like multilevel H-bridge converter while it is mandatory to use three multilevel DFCM converters. As a result, the connection of three separate multilevel DFCM converters must be in one of the following methods.

- Using one dc voltage source (or dc link) jointly for three single-phase proposed DFCM converters and three isolation transformers for each single-phase converter

- Using three isolated dc voltage sources (or three isolated dc links) for each single-phase proposed DFCM converter without isolation transformer.

Moreover, three-phase application of proposed DFCM converter, such as motor drives, FACTS controller, and other must be in one of the aforementioned methods for connection of three separate multilevel DFCM converters.

# B. Instantaneous Model of the Converter in the State-Space Representation

As studied in [3], [7], [25], and [28], the instantaneous model of converter is necessary for estimation of the flying capacitors voltages and active control of the FCM and SM converters. Following, the instantaneous model of the four-cell-nine-level DFCM converter, as shown in Fig. 13, in the state-space representation is obtained

$$\begin{cases} \underline{X'}(t) = A(\underline{S}(t))\underline{X}(t) + B(\underline{S}(t))E\\ Y(t) = C\underline{X}(t) \end{cases}$$

(7)

$$\underline{X}(t) = \begin{bmatrix} V_{C1}(t) & V_{C2}(t) & V_{C3}(t) & i_L(t) \end{bmatrix}^T$$

(8)

$$\begin{bmatrix} 0 & 0 & 0 & \frac{S_2 - S_1}{C_1} \\ & & S_2 - S_2 \end{bmatrix}$$

$$A(\underline{S}(t)) = \begin{bmatrix} 0 & 0 & 0 & \frac{S_3 - S_2}{C_2} \\ 0 & 0 & 0 & \frac{S_4 - S_3}{C_3} \\ \frac{S_1 - S_2}{L} & \frac{S_2 - S_3}{L} & \frac{S_3 - S_4}{L} & \frac{-R}{L} \end{bmatrix}$$

(9)

$$B(\underline{S}(t)) = \begin{bmatrix} 0 & 0 & 0 & \frac{S_4 - J}{L} \end{bmatrix}^T$$

(10)

$$C = \begin{bmatrix} 0 & 0 & 0 & 1 \end{bmatrix} \tag{11}$$

where *E* is the input voltage source,  $\underline{S} = [S_1 \ S_2 \ S_3 \ S_4]$  is the states of switches,  $Y(t) = i_L(t)$  is the measured state and corresponds to the load current, and *R* and *L* are the resistance and inductance of load, respectively. In the aforementioned instantaneous model, the output *RLC* filter is not existent at the output.

## **IV. SIMULATION RESULTS**

Computer simulation is performed to verify the effectiveness and performance of the proposed converter. The

TABLE II COMPARISON BETWEEN THE CONVENTIONAL MULTICELL CONVERTERS AND THE PROPOSED CONVERTER FOR THE SAME OUTPUT VOLTAGE

| Type of multicell<br>converter                | No. of<br>High<br>Frequency<br>Switches | No. of<br>Low<br>Frequency<br>Switches | No.<br>of<br>Cells | No. of<br>Capacitors | No. of<br>DC<br>Sources | Voltage<br>Rating<br>of DC<br>Sources<br>(per unit) |   | Power<br>Rating<br>of<br>High<br>Frequency<br>Switches<br>(per unit) | Voltage<br>Rating<br>of<br>Capacitors<br>(per unit) |

|-----------------------------------------------|-----------------------------------------|----------------------------------------|--------------------|----------------------|-------------------------|-----------------------------------------------------|---|----------------------------------------------------------------------|-----------------------------------------------------|

| Cascade Multicell                             | 4n                                      | 0                                      | n                  | 0                    | n                       | 1                                                   | 1 | 1                                                                    |                                                     |

| Flying Capacitor<br>Multicell                 | 4n                                      | 0                                      | 2n                 | 2n-1                 | 2                       | п                                                   | 1 | 1                                                                    | From 1 to 2n-1                                      |

| Stacked Multicell                             | 4n                                      | 0                                      | 2n                 | 2n-2                 | 2                       | n                                                   | 1 | 1                                                                    | From 1 to n-1                                       |

| Proposed Double Flying<br>Capacitor Multicell | 2n                                      | 2                                      | п                  | n-1                  | 1                       | n                                                   | 1 | 1                                                                    | From 1 to n-1                                       |

TABLE III MAIN PARAMETERS OF SIMULATED CONVENTIONAL AND PROPOSED CONVERTERS

| System Parameters                                                                                 | Values<br>200 V      |  |  |  |

|---------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| DC voltage (E)                                                                                    |                      |  |  |  |

| Internal flying capacitors (C)                                                                    | 1mF                  |  |  |  |

| PSPWM carrier frequency ( <i>f<sub>switching</sub></i> ) used for CM, FCM, SM and DFCM converters | 700 Hz               |  |  |  |

| Fundamental output voltage frequency                                                              | 50 Hz                |  |  |  |

| Resistive load (R <sub>L</sub> )                                                                  | 9 Ω                  |  |  |  |

| Resistive-Inductive load ( $R_L$ ; $L_L$ )                                                        | 20Ω ; 50mH           |  |  |  |

| Output RLC filter tuned to f <sub>SW</sub> (R, L, C)                                              | 1Ω ; 9mH ; 5.74µF    |  |  |  |

| Output RLC filter tuned to $2f_{SW}$ (R, L, C)                                                    | 1Ω ; 2.25mH ; 5.74µF |  |  |  |

| Number of harmonics for THD calculation                                                           | 255                  |  |  |  |

four-cell-nine-level DFCM converter, as shown in Fig. 13, is simulated using the power systems computer aided design /EMTDC software. The main parameters used in the simulations are given in Table III.

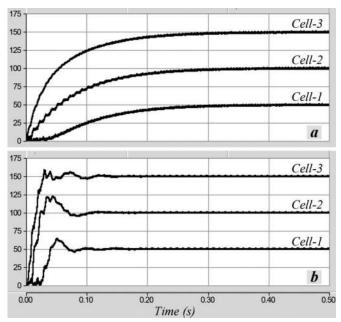

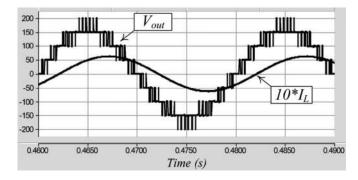

As the four-cell-nine-level DFCM converter is controlled by PSPWM ( $f_{\rm switching} = 700$  Hz) and operated with a modulation index equal to 0.8 (M = 0.8), the output voltage with THD of 15% and load current, as well as the flying capacitors voltages are illustrated in Figs. 15 and 16, respectively. Fig. 16(a) depicts the internal flying capacitors voltages for the case in which the converter load is resistive and no output *RLC* filter is applied. Fig. 16(b) is for the case in which the output load is resistive-

Fig. 15. Four-cell-nine-level DFCM converter output voltage (in volt) and load current (in ampere) with resistive-inductive load.

inductive, therefore, an output *RLC* filter is needed and applied. In comparison with Figs. 5 and 9, Fig. 15 illustrate that in the proposed DFCM converter both the rms of output voltage and the number of output voltage levels are doubled. As shown in Fig. 16, the flying capacitors can reach to their desired voltages, meaning that the self-balancing property of the FCM converter is maintained in the DFCM converter.

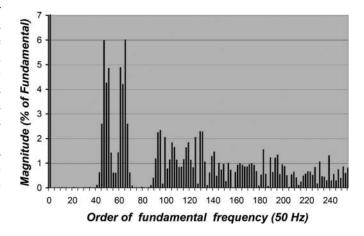

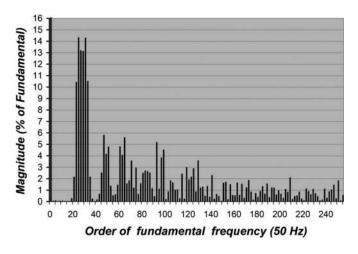

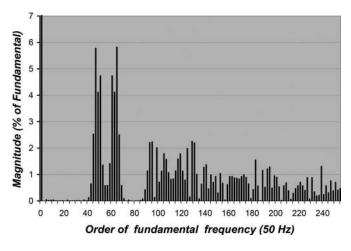

Fig. 17 shows the output voltage frequency spectrum of the four-cell-nine-level DFCM converter. As shown, the output voltage frequency spectrum of the proposed converter is improved in comparison with Figs. 6 and 10.

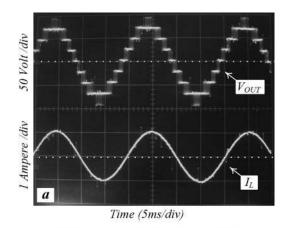

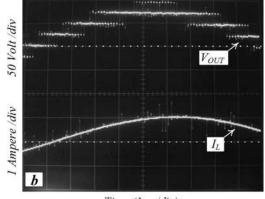

### V. EXPERIMENTAL RESULTS

To test both the validity and the practicality of the proposed configuration, a prototype four-cell-nine-level proposed DFCM converter was built with ten *IRFP460* 500 V 20 A MOSFETs, as shown in Fig. 18. The flying capacitors values are 1 mF, dc voltage is 100 V, switching frequency is 2.1 kHz, modulation index (M) is 0.8 and resistive-inductive (RL) load is

Fig. 16. Internal flying capacitors voltages of a four-cell-nine-level DFCM converter (in volt). (a) Resistive load without output *RLC* filter. (b) Resistive-inductive load with output *RLC* filter.

Fig. 17. Output voltage frequency spectrum of a four-cell-nine-level proposed DFCM converter.

Fig. 18. Hardware implementation of four-cell-nine-level DFCM converter.

Time (1ms/div)

Fig. 19. Experimental results. (a) Four-cell-nine-level DFCM converter output voltage and load current. (b) More detailed of output voltage and load current.

Time (1s/div)

Fig. 20. Experimental results. (a) Voltage of cell-1's flying capacitor  $(V_{C1})$ . (b) Voltage of cell-2's flying capacitor  $(V_{C2})$ . (c) Voltage of cell-3's flying capacitor  $(V_{C3})$ .

75  $\Omega$ –90 mH. As the prototype converter was built for the laboratory test, its maximum output power is 500 W.

The measured output voltage and load current as well as the flying capacitors voltages taken from the prototype system without applying output *RLC* filter (balance booster circuit) are illustrated in Figs. 19 and 20, respectively.

The match between simulation and experimental results confirms the advantages and practicality of the proposed DFCM converter and its modified PSPWM control strategy.

#### VI. CONCLUSION

Multicell converters are very interesting for high-power/highvoltage applications and considerably improve the output voltage frequency spectrum. This paper has proposed a new configuration of the FCM converter called DFCM converter. In comparison with FCM and SM converters, the main advantages of the proposed converter are doubling the rms of output voltage and the number of output voltage levels and canceling the midpoint of dc source. This progress is achieved by adding only two low-frequency switches to the conventional configuration of the FCM converter, while the number of the highfrequency switches and capacitors, voltage ratings of capacitors and switches, and the number of high-frequency switchings during a full cycle are kept constant. Two additional switches work with low-switching frequency and are generally switched twice during a full cycle of the fundamental output voltage. Also, the frequency spectrum of the output voltage is improved and its THD is reduced significantly because of doubling the number of output voltage levels. As a result, the progress of doubling the rms of output voltage and the number of output voltage levels in the proposed DFCM converter makes it possible to decrease the number of flying capacitors, high-frequency switches, and input dc voltage sources by 50% in comparison with CM, FCM, and SM converters. Moreover, the self-balancing property of the FCM and SM converters, and transformerless operation are maintained in the proposed DFCM converter, which its control strategy is based on the modified PSPWM.

Provided a comparison between the conventional configurations of multicell converters and the proposed DFCM converter, and both simulation and experimental results demonstrate the good performance and feasibility of the proposed converter.

The authors believe that the proposed configuration has a good potential for high-power/high-voltage applications, such as high-power ac motor drives, active power filters, reactive power compensation, dynamic voltage restorer, FACTS devices, and power electronic transformers, while the connection of three separate single-phase DFCM converters must be in one of the mentioned methods.

#### References

- P. Lezana, J. Rodríguez, and D. A. Oyarzún, "Cascaded multilevel inverter with regeneration capability and reduced number of switches," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1059–1066, Mar. 2008.

- [2] T. A. Meynard, H. Foch, F. Forest, C. Turpin, F. Richardeau, L. Delmas, G. Gateau, and E. Lefeuvre, "Multicell converters: Derived topologies," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 978–987, Oct. 2002.

- [3] C. Haederli, P. Ladoux, T. Meynard, G. Gateau, and A. M. Lienhardt, "Neutral point control in multi level converters applying novel modulation schemes," in *Proc. IEEE 37th Power Electron. Spec. Conf. (PESC 2006)*, Jun. 18–22, pp. 1–8.

- [4] P. Lezana, G. Ortiz, and J. Rodríguez, "Operation of regenerative cascade multicell converter under fault condition," in *Proc. 11th Workshop Control Model. Power Electron. (COMPEL 2008)*, Aug. 17–20, pp. 1–6.

- [5] Z. Du, L. M. Tolbert, B. Ozpineci, and J. N. Chiasson, "Fundamental frequency switching strategies of a seven-level hybrid cascaded H-bridge multilevel inverter," *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 25– 33, Jan. 2009.

- [6] M. Sabahi, S. H. Hosseini, M. B. B. Sharifian, A. Y. Goharrizi, and G. B. Gharehpetian, "A three-phase dimmable lighting system using a bidirectional power electronic transformer," *IEEE Trans. Power Electron.*, vol. 24, no. 3, pp. 830–837, Mar. 2009.

- [7] G. Gateau, M. Fadel, P. Maussion, R. Bensaid, and T. A. Meynard, "Multicell converters: Active control and observation of flying capacitor voltages," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 998–1008, Oct. 2002.

- [8] A. M. Lienhardt, G. Gateau, and T. A. Meynard, "Zero-steady-state-error input-current controller for regenerative multilevel converters based on single-phase cells," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 733– 740, Apr. 2007.

- [9] C. Turpin, L. Deprez, F. Forest, F. Richardeau, and T. A. Meynard, "A ZVS imbricated cell multilevel inverter with auxiliary resonant commutated poles," *IEEE Trans. Power Electron.*, vol. 17, no. 6, pp. 874–882, Nov. 2002.

- [10] J. Rodríguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [11] B. P. McGrath and D. G. Holmes, "Natural current balancing of multicell current source converters," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1239–1246, May 2008.

- [12] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral point clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [13] E. Babaei, "A Cascade multilevel converter topology with reduced number of switches," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2657–2664, Nov. 2008.

- [14] P. Lezana, J. Rodríguez, R. Aguilera, and C. Silva, "Fault detection on multicell converter based on output voltage frequency analysis," in *Proc. IEEE Ind. Electron. Conf.*, 2006, pp. 1691–1696.

- [15] T. A. Meynard, M. Fadel, and N. Aouda, "Modelling of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 44, no. 3, pp. 356–364, Jun. 1997.

- [16] A. K. Sadigh, S. H. Hosseini, S. M. Barakati, and G. Gharehpetian, "Flying capacitor multicell converter based dynamic voltage restorer," in *Proc.* 41st North Amer. Power Symp. (NAPS 2009), Oct., pp. 1–6.

- [17] G. Gateau, T. A. Meynard, and H. Foch, "Stacked multicell converter (SMC): Properties and design," in *Proc. IEEE PESC Meeting*, 2001, pp. 1583–1588.

- [18] A. K. Sadigh, E. Babaei, S. H. Hosseini, and M. Farasat, "Dynamic voltage restorer based on stacked multicell converter," in *Proc. IEEE Symp. Ind. Electron. Appl. (ISIEA 2009)*, Oct., Malaysia, pp. 1–6.

- [19] A. K. Sadigh, S. H. Hosseini, S. M. Barakati, and G. Gharehpetian, "Stacked multicell converter based DVR with energy minimized compensation strategy," in *Proc. 41st North Amer. Power Symp. (NAPS 2009)*, Oct., pp. 1–6.

- [20] B. P. McGrath and D. G. Holmes, "Analytical modeling of voltage balance dynamics for a flying capacitor multilevel converter," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 543–550, Mar. 2008.

- [21] B. P. McGrath, T. Meynard, G. Gateau, and D. G. Holmes, "Optimal modulation of flying capacitor and stacked multicell converters using a state machine decoder," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 508–516, Mar. 2007.

- [22] C. Feng, J. Liang, and V. G. Agelidis, "Modified phase-shifted PWM control for flying capacitor multilevel converters," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 178–185, Jan. 2007.

- [23] M. Marchesoni, M. Mazzucchelli, and S. Tenconi, "A non conventional power converter for plasma stabilization," *IEEE Trans. Power Electron.*, vol. 5, no. 2, pp. 212–219, Apr. 1990.

- [24] T. Ghiara, M. Marchesoni, L. Puglisi, and G. Sciutto, "A modular approach to converter design for high power AC drives," in *Proc. 4th Eur. Conf. Power Electron. Appl. (EPE 1991)*, Firenze, Italy, Sep., pp. 4-477–4-482.

- [25] S. H. Hosseini, A. K. Sadigh, and A. Sharifi, "Estimation of flying capacitors voltages in multicell converters," in *Proc. 6th Int. ECTI Conf.*, Thailand, May 2009, vol. 1, pp. 110–113.

- [26] T. Meynard, A. M. Lienhardt, G. Gateau, C. Haederli, and P. Barbosa, "Flying capacitor MultiCell converters with reduced stored energy," in *Proc. IEEE Int. Symp. Ind. Electron.*, Canada, Jul. 2006, pp. 914–918.

- [27] A. Shukla, A. Ghosh, and A. Joshi, "Improved multilevel hysteresis current regulation and capacitor voltage balancing schemes for flying capacitor multilevel inverter," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 518– 529, Mar. 2008.

- [28] A. M. Lienhardt, G. Gateau, and T. A. Meynard, "Digital sliding-mode observer implementation using FPGA," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 1865–1875, Aug. 2007.

Mehran Sabahi was born in Tabriz, Iran, in 1968. He received the B.S. degree in electronic engineering from University of Tabriz, Tabriz, the M.S. degree in electrical engineering from Tehran University, Tehran, Iran, and the Ph.D. degree in electrical engineering from University of Tabriz, Tabriz, Iran in 1991, 1994, and 2009, respectively.

In 2004, he joined the Faculty of Electrical and Computer Engineering, University of Tabriz, where he has been an Assistant Professor since 2009. His current research interests include power electronic

converters and power electronic transformers.

**Arash Khoshkbar Sadigh** (S'09) was born in Tabriz, Iran, in 1985. He received the B.S. (Hons.) and M.S. (Hons.) degrees in electrical engineering from the University of Tabriz, Tabriz, in 2007 and 2009, respectively.

He was selected by the University of Tabriz as the best student in 2006. He is author or coauthor of more than 15 journal and conference papers. His current research interests include power electronic circuits, multilevel converters, power quality, dynamic voltage restorer, active power filters, FACTS devices,

and distributed generation.

**Gevorg B. Gharehpetian** (M'00–SM'08) was born in Tehran, Iran, in 1962. He received the B.S. (Hons.) degree from Tabriz University, Tabriz, Iran, in 1987, the M.S. (Hons.) degree from Amirkabir University of Technology (AUT), Tehran, Iran, in 1989, and the Ph.D. degree from Tehran University, Tehran, Iran, in 1996, all in electrical engineering.

From 1997 to 2003, he was an Assistant Professor in AUT, where he was an Associate Professor from 2004 to 2007, and a Professor since 2007. He was also with High Voltage Institute of RWTH Aachen,

Aachen, Germany. He is the author or coauthor of more than 330 journal and conference papers. Since 2004, he has been the Editor-in-Chief of the *Journal of Iranian Association of Electrical and Electronics Engineers* (IAEEE). His current research interests include power system and transformers transients, FACTS devices, distributed generation (DG) and high voltage direct current transmission.

Prof. Gharehpetian is a Senior Member of IAEEE and a member of the central board of IAEEE. From 1993 to 1996, he was recipient of scholarship from German Academic Exchange Service (DAAD). In 2008, he was awarded the National Prize by the ministry of higher education as the Distinguished Professor of Iran. He is a member of Center of Excellence on Power Systems, Iran.

Seyed Hossein Hosseini (M'93) was born in Marand, Iran, in 1953. He received the M.S. degree from the Faculty of Engineering, University of Tabriz, Tabriz, Iran, in 1976, the D.E.A. and Ph.D. degrees from National Polytechnic Institute of Lorraine, Nancy, Lorraine, France, in 1978 and 1981, respectively, all in electrical engineering.

In 1982, he joined as an Assistant Professor in the Department of Electrical Engineering, University of Tabriz, where he was an Associate Professor from 1990 to 1995, and a Professor since 1995. From

September 1990 to September 1991, he was a Visiting Professor at the University of Queensland, Brisbane, Australia. From September 1996 to September 1997, he was a Visiting Professor at the University of Western Ontario, ON, Canada. His current research interests include power electronic converters, matrix converters, active and hybrid filters, application of power electronics in renewable energy systems and electrified railway systems, reactive power control, harmonics and power quality compensation systems, such as static var compensator, unified power quality conditioner, and FACTS devices.