## Drift-diffusion model for single layer transition metal dichalcogenide field-effect transistors

**David Jiménez**

Citation: Applied Physics Letters 101, 243501 (2012); doi: 10.1063/1.4770313

View online: http://dx.doi.org/10.1063/1.4770313

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/101/24?ver=pdfcov

Published by the AIP Publishing

## Re-register for Table of Content Alerts

Create a profile.

Sign up today!

## Drift-diffusion model for single layer transition metal dichalcogenide field-effect transistors

David Jiméneza)

Departament d'Enginyeria Electrònica, Escola d'Enginyeria, Universitat Autònoma de Barcelona, 08193-Bellaterra, Spain

(Received 17 October 2012; accepted 26 November 2012; published online 10 December 2012)

A physics-based model for the surface potential and drain current for monolayer transition metal dichalcogenide (TMD) field-effect transistor is presented. Taking into account the two-dimensional (2D) density-of-states of the atomic layer thick TMD and its impact on the quantum capacitance, a model for the surface potential is presented. Next, considering a drift-diffusion mechanism for the carrier transport along the monolayer TMD, an explicit expression for the drain current has been derived. The model has been benchmarked with a measured prototype transistor. Based on the proposed model, the device design window targeting low-power applications is discussed. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4770313]

A great deal of interest in two-dimensional materials analogues of graphene has appeared among the scientific community since the demonstration of isolated 2D atomic plane crystals from bulk crystals. Dimensionality is key for the definition of material properties and the same chemical compound can exhibit dramatically different properties depending on whether it is arranged in dots (0D), wires (1D), sheets (2D), or bulk (3D) crystal structure. Notably, experimental studies of 2D atomic crystals were lacking until recently because of the difficulty in their identification. Representative of this class are the 2D monolayer of transition metal dichalcogenides (TMDs) with a chemical formula MX<sub>2</sub>, where M stands for a transition metal and X for Se, S, or Te. The potential of this family of layered materials for flexible electronics was proposed by Podzorov et al., who demonstrate an ambipolar WSe2 p-field-effect transistor (FET) with a hole mobility comparable to silicon ( $\sim$ 500 cm<sup>2</sup>/ Vs). The electronic properties of TMDs vary from semiconducting (e.g., WSe<sub>2</sub>) to superconducting (e.g., NbSe<sub>2</sub>). The semiconducting monolayer TMDs, like MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub> are predicted to exhibit a direct gap in the range of  $1-2 \,\mathrm{eV}$ . The wide gap together with a promising ability to scale to short gate lengths because of the optimum electrostatic control of the channel, by virtue of its thinness, make monolayer TMDs very promising for low power switching and optoelectronics applications. The first 2D crystal based FET relying on a semiconducting analogue of graphene was demonstrated using a monolayer MoS2 as the active channel. Low power switching with an  $I_{ON}/I_{OFF} \sim$ 10<sup>8</sup> and subthreshold swing (SS) of 74 mV/decade at room temperature was experimentally measured. More recently, a monolayer p-type WSe<sub>2</sub> FET with an optimum SS  $\sim 60 \, \text{mV/}$ decade and  $I_{ON}/I_{OFF} > 10^6$  was demonstrated.<sup>5</sup>

To boost the development of 2D-material based transistor technology, modeling of the electrical characteristics is essential to cover aspects as device design optimization, projection of performances, and exploration of low-power switching circuits. <sup>6-9</sup> Some models aimed to explore the performance limits of monolayer TMD transistors have been

Let us consider a dual-gate monolayer TMD FET with the cross-section depicted in the inset of Fig. 1. It consists of

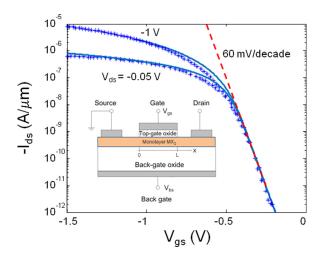

FIG. 1. Transfer characteristics obtained from the analytical model (solid lines) compared with experimental results from Ref. 5 (symbols). Inset: cross section of the dual-gate monolayer TMD transistor.

reported assuming ballistic transport. 10,11 However, the behavior of state-of-the art devices is far from ballistic and a drift-diffusion transport regime seems more appropriate for channel lengths well above the carrier mean free path (see Refs. 12 and 13 as an illustrative example of carrier transport studies, where the case of graphene is discussed). In this context, I propose a model for the current-voltage (I-V) characteristics of monolayer TMD FETs, based on the driftdiffusion theory. As a previous step a surface potential model, accounting for the 2D density-of-states (DOS<sub>2D</sub>) of monolayer TMDs, is proposed. I will consider that carriers are free to move parallel to the TMD sheet. However, their motion is restricted in the perpendicular direction because the strong quantum confinement. The DOS<sub>2D</sub> has a profound impact on the quantum capacitance, which is essentially different from that of a nanowire (1D) or a bulk (3D) material. Analytical expressions are derived for both the surface potential and drain current covering both subthreshold and above threshold operation regions.

a)Electronic mail: david.jimenez@uab.es.

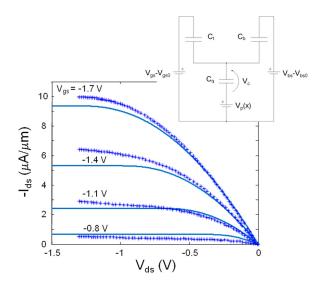

FIG. 2. Output characteristics obtained from the analytical model (solid lines) compared with experimental results from Ref. 5 (symbols). Inset: equivalent capacitive circuit.

one atomic layer thick TMD playing the role of the active channel. The source and drain electrodes contact the monolayer TMD and are assumed to be ohmic. The electrostatic modulation of the carrier concentration in the 2D sheet is achieved via a double-gate stack consisting of top and bottom gate dielectric and the corresponding metal gate. The source is grounded and considered the reference

potential in the device. The electrostatics of this device can be understood using the equivalent capacitive circuit depicted in the inset of Fig. 2. Here,  $C_t$  and  $C_b$  are the top and bottom oxide capacitances and  $C_q$  represents the quantum capacitance of the 2D sheet. The charge density (per unit area) is calculated by integrating the  $DOS_{2D}$  over all the energies and can be expressed as

$$Q_{c} = Q_{p} + Q_{n} = q \int_{-\infty}^{0} DOS_{2D}(E)f(E_{F} - E)dE$$

$$-q \int_{0}^{\infty} DOS_{2D}(E)f(E - E_{F})dE, \tag{1}$$

where  $Q_p$  and  $Q_n$  refer to the positive (holes) and negative (electrons) charge contributions, respectively; f(E) is the Fermi-Dirac function, and  $E_F = qV_c$  is the Fermi level, where the reference level is the semiconductor mid-gap. The parameter  $V_c$  represents the voltage drop across  $C_q$  or surface potential. For the sake of getting a simple model,  $f(E) \sim 1$  for  $E < E_F$  and  $f(E) \sim \exp((E_F - E)/kT)$  for  $E \ge E_F$  have been assumed. Noting that  $DOS_{2D}(E) = D_0 \sum_n H(E - E_n)$ , with  $D_0 = \frac{m^*}{n\hbar^2}$ , where  $m^*$  is the effective mass,  $E_n$  represents the energy of the  $n^{th}$ -subband, H(E) is the Heaviside function, and considering that the ground state (n=0) is the more relevant in determining the carrier density, then Eq. (1) can be written as

$$Q_{p} = -q^{2}D_{0}V_{c} - qD_{0}(E_{0} - kT); \qquad Q_{n} = -qD_{0}kTe^{\frac{qV_{c} - E_{0}}{kT}}, \quad qV_{c} \le -E_{0},$$

$$Q_{p} = qD_{0}kTe^{\frac{-qV_{c} - E_{0}}{kT}}; \qquad Q_{n} = -qD_{0}kTe^{\frac{qV_{c} - E_{0}}{kT}}, \quad q|V_{c}| < E_{0},$$

$$Q_{p} = qD_{0}kTe^{\frac{-qV_{c} - E_{0}}{kT}}; \qquad Q_{n} = -q^{2}D_{0}V_{c} + qD_{0}(E_{0} - kT), \qquad qV_{c} \ge E_{0},$$

$$(2)$$

where  $E_0 = E_g/2$  and  $E_g$  is the band gap of the monolayer TMD. From Eq. (2), the quantum capacitance defined as  $C_q = -dQ_c/dV_c$ , results in

$$C_{q} = C_{q,p} + C_{q,n} = q^{2}D_{0} + q^{2}D_{0}e^{\frac{qV_{c} - E_{0}}{kT}}, \quad qV_{c} \leq -E_{0},$$

$$C_{q} = C_{q,p} + C_{q,n} = q^{2}D_{0}e^{\frac{-qV_{c} - E_{0}}{kT}} + q^{2}D_{0}e^{\frac{qV_{c} - E_{0}}{kT}}, \quad q|V_{c}| < E_{0},$$

$$C_{q} = C_{q,p} + C_{q,n} = q^{2}D_{0}e^{\frac{-qV_{c} - E_{0}}{kT}} + q^{2}D_{0}, \quad qV_{c} \geq E_{0}.$$

$$(3)$$

Under nonequilibrium conditions ( $V_{ds} \neq 0$ ), a single Fermi level cannot be assumed. Instead, two distinct quasi-Fermi levels for computing the electron  $V_n(x)$  and hole  $V_p(x)$  concentrations and currents have to be considered. Here x denotes the transport direction. In this work, I consider the

modeling of unipolar p-FETs. Extension to unipolar n-FETs is straightforward. Coming back to the inset of Fig. 2,  $V_p(x)$  is zero at the source end (x=0) and  $V_{ds}$  at the drain end (x=L). Applying basic circuit laws to the equivalent capacitive network, the following relation can be obtained:

$$V_{c}(x) = \frac{Q_{p}(V_{c})}{C_{t} + C_{b}} + \left(V_{gs} - V_{gs0} - V_{p}(x)\right) \frac{C_{t}}{C_{t} + C_{b}} + \left(V_{bs} - V_{bs0} - V_{p}(x)\right) \frac{C_{b}}{C_{t} + C_{b}}, \tag{4}$$

where  $V_{gs}$ - $V_{gs0}$  and  $V_{bs}$ - $V_{bs0}$  are the top and back gate-source voltage overdrive, respectively. These quantities comprise work-function differences between the gates and the TMD monolayer, eventual charged interface states at the TMD monolayer/oxide interfaces, and intentional or unintentional doping of the TMD monolayer.

To model the drain current of a monolayer TMD p-FET, a drift-diffusion transport is assumed under the form  $I_{ds} = -WQ_p(x)v(x)$ , where W is the gate width, and v(x) the hole drift velocity  $v = \mu F$ , where F is the electric field and  $\mu$  is the hole effective mobility assumed independent of field, carrier density, or temperature. This model applies as long as the channel length is well above the hole mean free path. As

a reference, a mean free path (for electrons) of  $\sim\!20\,\mathrm{nm}$  was estimated in Ref. 10 for MoS<sub>2</sub> monolayers. Applying  $F = -\mathrm{dV_p}(x)/\mathrm{dx}$ , inserting the above expression for v, and integrating the resulting equation over the device length, the drain current becomes  $I_{ds} = \mu \frac{w}{L} \int_0^{V_{ds}} Q_p dV_p$ . In order to get an explicit expression for the drain current, the integral is solved using  $V_c$  as the integration variable consistently expressing  $Q_p$  as a function of  $V_c$ ,

$$I_{ds} = \mu \frac{W}{L} \int_{V_{cr}}^{V_{cd}} Q_p \frac{dV_p}{dV_c} dV_c, \tag{5}$$

where  $V_{cs}$  is obtained from Eq. (4) as  $V_c(V_p=0)$ . Similarly,  $V_{cd}$  is determined as  $V_c(V_p=V_{ds})$ . Moreover, Eq. (4) provides the relation  $\frac{dV_p}{dV_c}=-\left(1+\frac{C_{q,p}}{C_t+C_b}\right)$ , where  $C_{q,p}=-dQ_p/dV_c$ . Inserting this expression into Eq. (5), the following explicit drain current expression can be finally obtained

$$I_{ds} = \mu \frac{W}{L} \{g(V_c)\}_{V_{cs}}^{V_{cd}}$$

$$g(V_c) = \left(1 + \frac{q^2 D_0}{C_t + C_b}\right) \left(\frac{q^2 D_0}{2} V_c^2 + q D_0 (E_0 - kT) V_c\right), \quad q V_c < -E_0,$$

$$g(V_c) = D_0 (kT)^2 \left(e^{\frac{-q V_c - E_0}{kT}} + \frac{q^2 D_0}{C_t + C_b} \frac{1}{2} e^{\frac{-2(q V_c + E_0)}{kT}}\right), \quad q V_c \ge -E_0,$$

(6)

where  $g(V_c)$  takes different forms whether  $qV_c < -E_0$  (above threshold region) or  $qV_c \ge -E_0$  (subthreshold region). To take into account eventual saturation velocity effects, the physical channel length should be replaced by an effective length  $L_{eff} = L + \mu \frac{|V_{ds}|}{v_{sat}}$ , where  $v_{sat}$  is the hole saturation velocity.

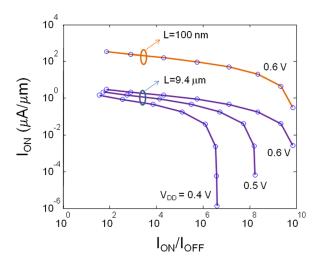

To test the model, I have benchmarked the resulting I-V characteristics with experimental results reported in Ref. 5, which are unipolar p-type FETs with a channel consisting of a monolayer WSe2. The channel was contacted with Pd contacts acting as source and drain electrodes. P-type conduction was experimentally observed and this is presumably due to the small barrier height for hole injection at the Pd-WSe<sub>2</sub> interface. The energy band gap of the monolayer WSe2 is  $E_g \sim 1.68\,eV$  and the valence band effective mass along the transport direction is calculated to be  $m^* = 0.64m_0 (K \rightarrow \Gamma)$ , m<sub>0</sub> being the free electron mass, estimated from the dispersion relations.<sup>3</sup> The device under test has  $L = 9.4 \,\mu\text{m}$ , W = 1  $\mu$ m, top dielectric is ZrO<sub>2</sub> of 17.5 nm and relative permittivity  $\sim$ 12.5, and the bottom dielectric is silicon oxide of  $270 \,\mathrm{nm}$ . The backgate voltage was  $-40 \,\mathrm{V}$ . The flat-band voltages  $V_{gs0}$  and  $V_{bs0}$  were tuned to  $-0.5\,V$  and  $0\,V$ , respectively, to provide an appropriate shift of the transfer characteristics according to the experiment. A constant hole effective mobility of 250 cm<sup>2</sup>/Vs was assumed, consistent with measurements. A source/drain resistance of 300  $\Omega$  provides a good fit with the experiment. Around the threshold voltage ( $\sim -0.5 \,\mathrm{V}$ ), a slight disagreement is observed because the approximation made for the Fermi-Dirac distribution. The resulting I-V transfer and output characteristics are shown in Figs. 1 and 2. In accordance with the experiment, a SS  $\sim 60\,\mathrm{mV/decade}$  at room temperature and  $I_{\mathrm{ON}}$  $I_{\rm Off} \sim 10^6$  is predicted by the model (Fig. 1). Note that no interface trap capacitance (Cit) was needed to be included in the model to match the experiment because the near ideal subthreshold slope suggests that  $C_{it} \ll C_{ox}$ . The output characteristics show saturation-like behavior at high V<sub>ds</sub> (Fig. 2). Saturation velocity effects are not expected to be relevant for this transistor because  $\frac{\mu}{v_{sat}} \sim 2.5\,$  nm/V, giving  $L_{eff} \approx L.$  At low V<sub>ds</sub>, the model nicely reproduces the observed linear behavior, indicative of ohmic metal contacts. The agreement between the proposed model (solid lines) and the experiment (symbols) is pretty good. More accuracy could be expected by adding to the model a field dependent mobility and selfheating effects. Next, by using the model, the tradeoff between I<sub>ON</sub> and I<sub>ON</sub>/I<sub>Off</sub> is calculated (Fig. 3). Ten orders of magnitude between switching states could be achieved, although at the expense of the ION. For the reported transistor, an  $I_{\rm ON}/I_{\rm Off} \sim 10^6$  with  $I_{\rm ON} \sim 1 \,\mu{\rm A}/\mu{\rm m}$  at power supply voltage  $V_{DD} = 0.6 \text{ V}$  could be achieved. Nevertheless, a huge improvement of the I<sub>ON</sub> may be possible via channel length scaling. A simulation of an hypothetical transistor of  $L = 100 \,\mathrm{nm}$  assuming the same hole mobility as the reference transistor gives a factor ×100 of ON-current

FIG. 3. Tradeoff between ON-current and ON-OFF current ratio.

improvement for a fixed I<sub>ON</sub>/I<sub>Off</sub>. Note that short-channel effects (SCEs) have not been included in the model, but due to the extreme immunity of 2D materials to SCE the 100 nm transistor considered here is expected to behave as a well tempered long-channel transistor. For short-channel length devices (sub 100-nm), the calculations should be done by solving the full Poisson's equation in both vertical and lateral dimensions, which is beyond the scope of this work.

In conclusion, a surface potential and drain current model for monolayer TMD transistors has been proposed, taking into account the 2D semiconducting nature of monolayer TMDs. The drain current is formulated assuming a drift-diffusion theory, which seems appropriate for explaining

the experimental results of reported devices till date. These transistors hold promise for low-power switching applications. The proposed model should be valid for other transistors relying on 2D atomic layer thick channels.

I acknowledge the funding of the Ministerio de Ciencia e Innovación under contract FR2009-0020 and TEC2009-09350, and the DURSI of the Generalitat de Catalunya under contract 2009SGR783.

<sup>1</sup>K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V. Morozov, and A. K. Geim, Proc. Natl. Acad. Sci. **102**(30), 10451– 10453 (2005).

<sup>2</sup>V. Podzorov, M. E. Gershenson, C. Kloc, R. Zeis, and E. Bucher, Appl. Phys. Lett. 84(17), 3301–3303 (2004).

<sup>3</sup>W. S. Yun, S. W. Han, S. C. Hong, I. G. Kim, and J. D. Lee, Phys. Rev. B **85**, 033305 (2012).

<sup>4</sup>B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, Nat. Nanotechnol. **6**, 147–150 (2011).

<sup>5</sup>H. Fang, S. Chuang, T. C. Chang, K. Takei, T. Takahashi, and A. Javey, Nano Lett. **12**, 3788–3792 (2012).

<sup>6</sup>S. A. Thiele, J. A. Schaefer, and F. Schwierz, J. Appl. Phys. **107**, 094505 (2010).

<sup>7</sup>S. Thiele and F. Schwierz, J. Appl. Phys. **110**, 034506 (2011).

<sup>8</sup>D. Jiménez and O. Moldovan, IEEE Trans. Electron Devices **58**(11), 4049–4052 (2011).

<sup>9</sup>D. Jiménez, IEEE Trans. Electron Devices **58**(12), 4377–4383 (2011).

<sup>10</sup>Y. Yoon, K. Ganapathi, and S. Salahuddin, Nano Lett. **11**, 3768–3773 (2011)

<sup>11</sup>L. Liu, S. B. Kumar, Y. Ouyang, and J. Guo, IEEE Trans. Electron Devices 58(9), 3042–3047 (2011).

<sup>12</sup>M.-H. Bae, S. Islam, V. E. Dorgan, and E. Pop, ACS Nano 5, 7936–7944 (2011).

<sup>13</sup>M.-H. Bae, Z.-Y. Ong, D. Estrada, and E. Pop, Nano Lett. **10**, 4787–4793 (2010).