# Dual Standard Re-configurable Hardware Interleaver for Turbo Decoding

Rizwan Asghar and Dake liu Department of Electrical Engineering, Linköping University Linkoping, Sweden {rizwan, dake} @ isy.liu.se

Abstract-A very low cost re-configurable hardware interleaver for two standards, 3GPP-WCMDA and 3GPP Long Term Evolution (3GPP-LTE) is presented. The interleaver is a key component of radio communication systems. Using conventional design methods, it consumes a large part of silicon area in the design of turbo encoder and decoder. The presented hardware interleaver address generation architecture, utilizes the algorithmic level hardware simplifications to achieve very low cost solution. After doing the hardware optimizations the proposed architecture consumes only 3.1k gates with a 256x8 bit memory for the fully re-configurable dual standard interleaver address generator. The interleaved address is computed every clock cycle except the case of pruning (if block size is less than the row-column matrix) in 3GPP-WCDMA. In this case one additional clock cycle is consumed for valid address generation.

*Keywords*—Hardware interleaver, WCDMA, LTE, turbo codes, permutation polynomial

# I. INTRODUCTION

OST mobile phones and PC wireless connections have to support multi-mode (multi-standards). We therefore realize the importance of hardware reuse of FEC modules for low silicon costs. Hardware reuse for symbol processing was extensively discussed in [4]. However, hardware reuse of forward error correction (FEC) is seldom discussed. Among FEC modules, interleavers and de-interleavers are silicon consuming because of the silicon cost of the addressing tables. We therefore started the hardware reuse for interleaver address generation in FEC instead of using addressing memory. The newly evolved "3rd Generation Partnership Project (3GPP), Evolved Universal Terrestrial Radio Access (E-UTRA)" or 3GPP-LTE standard [1] is considered to be major step towards 4G systems. 3GPP-LTE uses turbo coding scheme for multiple applications. Wideband CDMA systems in 3G standard [2] also use turbo codes for forward error correction. The turbo codes [3] invented in 1993 captured great importance due to exhibiting near Shannon-limit performance. The superior error correcting performance of turbo codes over convolutional codes is associated with the suitable interleaver design. The primary function of the interleaver is to improve the distance properties of the concatenated coding schemes and to disperse

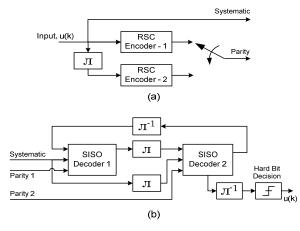

Fig. 1. Structure of Turbo Encoder and Turbo Decoder.

the sequence of bits in a bit stream so as to minimize the effect of burst errors introduced in transmission. Error correcting codes like turbo code can correct errors successfully as long as there are not too many errors in a single code word.

The scheme of turbo code adapted in both 3GPP-WCDMA and 3GPP-LTE is the parallel concatenated code (PCCC) with two 8-state constituent encoders. One turbo code internal interleaver is used in between the two recursive systematic convolutional encoders (RSC) as shown in Fig. 1a, while the turbo decoder as shown in Fig. 1b uses multiple instances of interleaver and de-interleaver to decode the received bits iteratively. The interleavers used in both the standards have different structure. Our research is to merge these two interleavers /de-interleavers structures into one low cost hardware module to demonstrate the way to reuse FEC hardware.

Our method in general is so called hardware multiplexing technique. It starts at analyzing / profiling multi CFG, identify opportunities of hardware multiplexing, and eventually fine tune the micro-architecture, using minimal hardware, and maximally reuse for multi functions.

Some comments on the previous work done for the design for hardware interleavers are provided in Section II. Section III provides the simplifications made for 3G-LTE standard. The detail of WCDMA hardware and its multiplexing with the LTE hardware is discussed in Section IV and V. The controller design and hardware implementation for the address generation of interleaver is described in Sections VI and VII respectively.

#### II. PREVIOUS WORK AND MOTIVATION

The motivation of the research is to explore the general, reconfigurable and low cost hardware interleaver address generator which can support more than one radio communication systems. Looking at the two standards, 3GPP-WCDMA and 3GPP-LTE, the wide range interleaver size, on the fly interleaver size change and requirement of different interleaver patterns for different block sizes has put some challenges to implement the interleaver. Implementing the memory based interleaver needs big memory to meet the whole requirements thus not feasible due to large hardware cost. To minimize the memory usage [5] presents a processor based hardware interleaver address generator which consumes 32k gates and provides the support for two standards i.e. WCMDA and CDMA-2000. The work presented in [6], [7] and [8] consume 30k gates, 4k gates and 2.2k gate + 2Kbit RAM respectively, but they only support hardware interleaver design for WCDMA standard. The hardware interleaver address generation circuits presented in [7] and [8] are really very area efficient solutions, but due to rapid advancement and changes in the radio communication systems there is always a need of flexible, general and multiple standard solutions. It also helps to compete, fast time to market requirements from industry and customer.

All these requirements motivate to explore the flexible and general hardware architecture solution that can accommodate multiple standards.

#### III. 3GPP-LTE SIMPLIFICATIONS AND HARDWARE

Reference to 3GPP-LTE standard the internal interleaver for turbo code is specified by the following quadratic permutation polynomial:

$$\prod(x) = (f_1 \cdot x + f_2 \cdot x^2) \operatorname{mod} K \tag{1}$$

Here  $x = 0, 1, 2 \dots$  (K-1), where K is the interleaver block size. The permutation polynomial mentioned in expression (1) provides deterministic interleaver for different block sizes and appropriate values of f1 and f2. The values of f1 and f2 for different block sizes are mentioned in the 3GPP-LTE standard [1]. The quadratic permutation polynomial interleavers are introduced in [9]. It is claimed in [9], that they are not as good as S-random interleavers, but they achieve average performance of random interleavers. In addition they have very compact representation methodology and also inhibit a structure that allows the easy analysis for its properties.

If we try to implement the permutation polynomial (1) directly, then it seems to be hardware in-efficient due to couple of multiplications and a complex modulo function. Beside this challenge there is a bit growth problem as well appearing in the term  $(f_1 \cdot x + f_2 \cdot x^2)$  with increase in 'x'. To overcome this situation some algorithmic level simplifications proposed in [9] are used. The permutation polynomial (1) can be re-written as follows to be computed in a recursive way.

$$f(x+1) = [f_1^*(x+1) + f_2^*(x+1)^2] \mod K$$

$$f(x+1) = [f(x) + (f_1 + f_2 + 2^* f_2^*x)] \mod K$$

$$f(x+1) = [f(x) + g(x)] \mod K$$

(2)

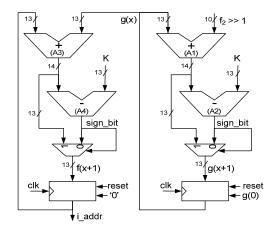

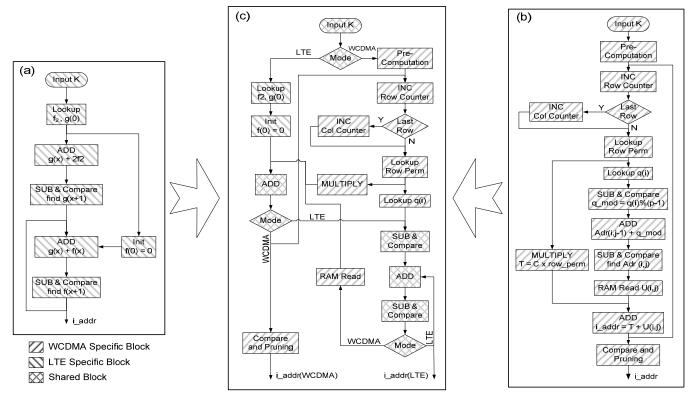

Fig. 2. Hardware required for 3GPP LTE Interleaver Design.

Here g(x) can again be computed recursively by using the following simplifications.

$$g(x+1) = [f1 + f2 + 2*f2*(x+1)] \mod K$$

$$g(x+1) = [g(x) + 2*f2] \mod K$$

(3)

These algebraic simplifications make the computation of quadratic permutation polynomial (1) very much hardware efficient.

From the hardware perspective two terms g(0) and f2 are needed to start computation. Using the values of f1 and f2 given in 3GPP-LTE standard we can find g(0) for all block sizes. The terms g(0) and f2 are placed in a lookup table, which is addressed by block size. Using the simplifications mentioned in equations (2) and (3) the terms f(x+1) and g(x+1) can be computed recursively by just using the adders and comparison. The hardware constructed to compute the interleaved address (i\_addr) is shown in Fig. 2. The computation of interleaving address is done every clock cycle and there is no latency.

## IV. A GLANCE AT INTERLEVER DESIGN FOR 3GPP-WCDMA

The interleaver address generation design for 3GPP-WCDMA has been elaborated in detail in [6], [7] and [8], as they focus on WCDMA. Here, the interleaver design for 3GPP-WCMDA is provided in brief to make continuation and easy understanding of the hardware blocks.

Reference to 3G standard [2], the interleaver algorithm for turbo coding and decoding is, writing the input data row wise in the memory configured as row-column matrix, performing intra-row and inter-row permutations and reading the data column wise. The address generation algorithm for the interleaving is described as below:

## A. 3GPP-WCDMA Interleaver Algorithm

- Find appropriate number of rows 'R', prime no 'p' and primitive root 'v' for particular block size.

- Col Size : C = p 1 if  $(K \le R * (p 1))$  C = p if  $(R * (p - 1) < K \le R * p)$ C = p + 1 if (R \* p < K)

- Construct intra row permutation sequence S(j) by: S(j) = [v \* S(j-1)] mod p; j = 1,2, ..... p-2

Authorized licensed use limited to: Linkoping Universitetsbibliotek. Downloaded on May 16, 2009 at 12:27 from IEEE Xplore. Restrictions apply.

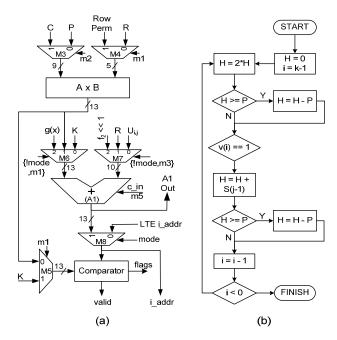

Fig. 3. (a) Hardware Multiplexing of Multiplication, Addition and Compare, (b) Flow Graph for Interleaved Modulo Multiplication Algorithm.

- Find q(i) for i=1,2, ..... R-1, take q(0) = 1, Determine the least prime integer q(i) in the sequence such that g.c.d(q(i),p-1) = 1 and q(i) > 6 and q(i) > q(i-1)

- Apply inter row permutations to q(i) to find r(i)

r(i) = T (q(i));

- Perform the intra row permutations Ui,j; (for i = 0,1,... R-1; j = 0,1, ...,p-2;)

$\begin{array}{ll} If \ (C=p) & : \ Ui, j = S \ [ \ (j * r(i)) \ mod \ (p-1) \ ] \ and \ Ui, (p-1) = 0; \\ If \ (C=p+1) & : \ Ui, j = S \ [ \ (j * r(i)) \ mod \ (p-1) \ ] \ ; \\ and \ Ui, (p-1) = 0; \ Ui, p = p; \ and \ if \ (K = R * C) \\ then \ exchange \ U(R-1,0) \ with \ U(R-1,p) \\ If \ (C=p-1) & : \ Ui, j = S \ [ \ (j * r(i)) \ mod \ (p-1) \ ] - 1 \ ; \end{array}$

- Perform the inter row permutations

- Read the address columns wise

Looking at the interleaver algorithm in 3GPP-WCDMA standard, the computationally intensive functions found are Modulo Computation, Intra-row and Inter-row Permutations, Multipliers, Finding least prime integers, and Computing greatest common divisor. Some of these complex functions are implemented using the support from ROM, while the others are simplified to reduce the hardware usage.

# V. WCDMA PRE-COMPUTATION HARDWARE AND MULTIPLEXING FOR LTE

As different block sizes has different interleaving patterns, thus every time some pre-computation is needed while changing the block size. The only parameter passed to interleaver is the block size (K) and rest of the parameters is computed by the hardware itself. The hardware interleaver parameters for WCDMA computed in the pre-computation phase are number of rows (R), no of columns (C), least prime number sequence (q(i)), inter-row permutation pattern (T(i)), prime number (p) and associated integer (v). Additionally the

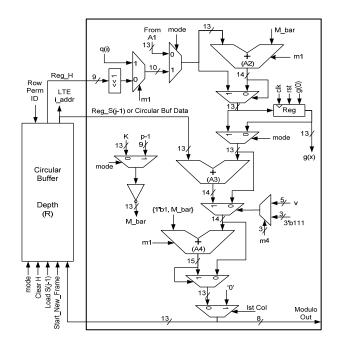

Fig. 4. Hardware for Modulo Computation Block.

intra-row permutation pattern (S(j)) is also computed in the pre-computation phase and placed in a RAM of size 256x8 bit.

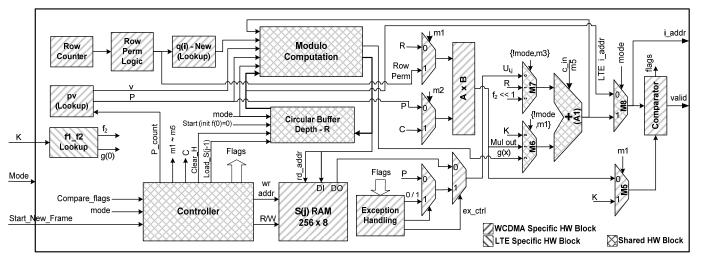

The computation of parameters in pre-computation for 3GPP-WCDMA is discussed in detail in [8]. Some parameters are computed using lookup tables while the others need some close loop or recursive computations. For computation of p and C, the multiplication, addition and comparison are needed. These blocks are shown in Fig. 3a. These blocks are multiplexed to serve in pre-computation phase as well as in run time for 3GPP-WCDMA and 3GPP-LTE. The computation of intra-row permutation pattern also need modulo computation. Here, the modulo function is computed iteratively using the Interleaved Modulo Multiplication Algorithm [11]. The required modulo function is [S(j-1)\*v mod P], so looking at v, which is 5bits, maximum of 5 iterations are needed to compute one modulo multiplication. The algorithm to compute the Interleaved Modulo Multiplications is shown in Fig. 3b. Three adders are needed to compute the S(j) values. The hardware for the computation of S(j) is shown in Fig. 4. Hardware multiplexing is done in such a way that all the hardware is being used in pre-computation phase, run time for 3GPP-WCDMA and run time for 3GPP-LTE. During precomputation phase the ram write address is generated by the controller while in run time it is generated as the Modulo\_Out signal in Fig. 4. The computed S(j) values are placed in a 256\*8bit RAM. The usage of this RAM depends on parameter p and it will be filled up to (p-2) locations starting from zero.

The parameters needed for 3GPP-LTE are only f2 and g(0), which are found using the lookup table as mentioned in section III, so no parameter computation is needed for LTE in the precomputation phase.

#### VI. CONTROLLER DESIGN

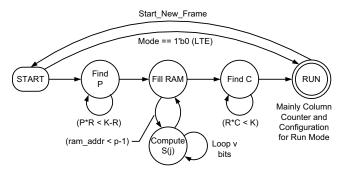

The controller mainly works for the pre-computation phase of 3GPP-WCDMA. It utilizes multiply, add, compare and modulo computation hardware to find all the vital parameters

Fig. 5. Flow Graph for (a) The interleaver address computation in LTE, (b) The interleaver address computation in WDCMA, (c) The interleaver address computation for WCDMA and LTE in combined fashion.

R, C, p, v and S(j). The state diagram of the controller for our design is shown in Fig. 6. For 3GPP-LTE standard the controller only checks the mode and directly jumps into the 'RUN' state. The new frame can always be initiated by just changing the block size parameter K and providing one pulse named 'start\_new\_frame'.

# VII. THE HARDWARE IMPLEMENTAION FOR ADDRESS GENERATION

After completing the pre-computation phase or looking at the input mode (WCDMA / LTE), the controller is set in 'RUN' state and the hardware is configured to perform run time computations for the generation of the interleaved addresses. The computation of least prime number q(i) is handled by computing q mod (p-1) with the help of a look up table and a subtractor. For 3GPP-WCDMA hardware interleaver the final RAM Address is computed mainly using the hardware shown in Fig. 3a. The recursive function used to compute the RAM address and multiply-add function to compute the final interleaved address are as follows:

$$Ram\_Adr(i,j) = [Ram\_Adr(i, j-1) + Q\_mod(i)] \mod (p-1)$$

i addr = (C \* Row Perm ) + U(i,j)

Where U(i,j) is the intra row permutation coming from RAM. The final interleaved address is tagged valid or invalid using the comparator. This is called pruning of the interleaver and is needed for the case when interleaver block size is not exactly equal to R\*C. The exception handling is done by using some flags and a couple of multiplexers.

Fig. 6. Controller for WCDMA and LTE Hardware Interleaver.

For the computation of the interleaver address for 3GPP-LTE systems the same hardware is used after getting the mode input as LTE (1'b0). The controller jumps into 'RUN' state directly and with a small difference of configuration vectors the same hardware is mapped to the hardware shown in Fig. 2 for computation of interleaver address for LTE.

The flow graph for the run time operations in 3GPP-LTE and 3GPP-WCDMA are shown in Fig. 5(a) and 5(b) respectively. Fig. 5(c) shows the flow graph illustrating the sharing of both the standards to achieve the reusable hardware architecture. The complete hardware blocks to compute the interleaved address in a multiplexed way for 3GPP-WCDMA and 3GPP-LTE systems is shown in Fig 7. It can be seen that all the vital computing parts are being shared by the two standards which provides an illustration of the hardware re-use to get the low cost solution for multiple applications.

Fig. 7. Complete Hardware for Combined Interleaver Design.

#### VIII. IMPLEMENTATION RESULTS

The RTL code for the hardware blocks is written in Verilog and the correctness of the design is checked by comparing the results generated by hardware with those generated using MATLAB. The throughput of the address generator is one permutation address per clock cycle, except the case of pruning in WCDMA. In this case the interleaved address is computed at most every two clock cycles.

The design is synthesized after setting constraint as area using 90nm standard CMOS technology. Excluding the 256x8 RAM, the total hardware consumed by the presented design is 3.1 k gates. The presented design provides support for two standards which is not provided in reference designs [6], [7] and [8]. So comparing with the reference designs as shown in Table 1, the design presented here is good in terms of multiple standard support as well as hardware efficiency.

## IX. CONCLUSION

In this paper a very low cost dual standard design for hardware interleaver address generation for 3GPP-WCDMA and 3GPP-LTE turbo decoding is presented. The final results show that it is a small design with the benefit of having two standard supports. Comparing with the conventional methods of using RAM for the interleaver, the silicon cost is about 20 times lower and the power consumption can therefore be much lower. The proposed architecture can act as a re-configurable interleaver accelerator with any kind of processor environment, thus providing performance with flexibility. Our principle goal is to investigate the hardware interleaver for multiple standards. In this regard the proposed architecture is the milestone towards our principle goal of architecture exploration for multiple radio communication standard support and further it can open more opportunities to cover more standards.

# REFERENCES

- "3GPP, Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA); Multiplexing and Channel Coding", Release 8, 3GPP TS 36.212 v8.0.0 (2007-09).

- [2] "3GPP, Technical Specification Group Radio Access Network; Multiplexing and Channel Coding (FDD)", Release 6, 3GPP TS 25.212 v6.0.0 (2003-12).

Standard Sr. No Implementation Size Support ROM 1. >100 Mbit (all patterns) RAM 2. (big off-chip Mem. ~ 80 Kbit required) 3. Design - 1 [5] 2 ~ 32K gates 4. Design - 2 [6] 1 ~ 30K gates 5. 1 Design - 3 [7] ~ 4K gates  $\sim 2.2 \text{K gates} +$ 6. Design - 4 [8] 1 2Kbit RAM  $\sim 3.1 \text{K gates} +$ 7. 2 This Design

TABLE I

HW USAGE COMPARISON FOR DIFFERENT ADDRESSING CIRCUITS

[3] C. Berrou, A. Glavieus, and P. Thitimajshima, "Near Shannon limit error-correcting coding and decoding: Turbo-codes", IEEE ICC'93, May 1993, vol. 2, pp. 1064 – 1070.

2Kbit RAM

- [4] A. Nilsson, E. Tell, and D. Liu, "An 11mm<sup>2</sup>, 70mW fully programmable baseband processor for mobile WiMAX and DVB-T/H in 0.12µm CMOS", accepted to ISSCC, San Francisco, Feb. 2008

- [5] M. Shin and I.-C. Park, "Processor-based turbo interleaver for multiple third-generation wireless standards", IEEE Communication Letters, vol. 7, no. 5, pp. 210 – 212, May 2003.

- [6] P. Ampadu and K. Kornegay, "An efficient hardware interleaver for 3G turbo decoding", Proc. RAWCON'03, pp. 199 – 201, August 2003.

- [7] Z. Wang and Q. Li, "Very low-complexity hardware interleaver for turbo decoding", IEEE Trans. on Circuits and System – II: vol. 54, no. 7, pp. 636 – 640, July 2007.

- [8] R. Asghar and D. Liu, "Very low cost configurable hardware interleaver for 3G turbo decoding", in press ICTTA, Damascus, Syria, April 2008.

- [9] O. Y. Takeshita and D. J. Costello, Jr, "New deterministic interleaver designs for turbo codes", IEEE Trans. for Information Theory, vol. 46, no. 6, pp. 1988–2006, Sep. 2000.

- [10] M. Cheng, M. Nakashima, J. Hamkins, B. Moision and M. Barsoum, "A decoder architecture for high-speed free-space laser communications", Proc. SPIE, Free-Space Laser Comm. Tech. XVII, San Jose, CA, vol. 5712, pp. 174–185, Jan-2005.

- [11] G. R. Blakley, "A Computer Algorithm for Calculating the Product A\*B mod M", IEEE Trans. on Comp, vol.C-32, No.5, pp.497-500, May 1983.