#### **W&M ScholarWorks**

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2004

## Dynamic adaptation to CPU and memory load in scientific applications

Richard Tran Mills College of William & Mary - Arts & Sciences

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons, and the Mathematics Commons

#### **Recommended Citation**

Mills, Richard Tran, "Dynamic adaptation to CPU and memory load in scientific applications" (2004). Dissertations, Theses, and Masters Projects. Paper 1539623457. https://dx.doi.org/doi:10.21220/s2-my1g-nn08

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

# DYNAMIC ADAPTATION TO CPU AND MEMORY LOAD IN SCIENTIFIC APPLICATIONS

A Dissertation

Presented to

The Faculty of the Department of Computer Science

The College of William and Mary in Virginia

In Partial Fulfillment

Of the Requirements for the Degree of

Doctor of Philosophy

by Richard Tran Mills 2004

#### APPROVAL SHEET

This dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Richard Tran Mills

Approved by the committee/November 2004

Andreas Stathopoulos, Chair

Dimitrios Nikolopoulos

Virginia Torczon

Richard Wolski

Department of Computer Science University of California, Santa Barbara

| To my family—especially my mother and father—and the Commodore-64 personal |

|----------------------------------------------------------------------------|

| computer.                                                                  |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

## **Table of Contents**

| A  | ckno            | wledgr          | nents     |                                                   | viii |

|----|-----------------|-----------------|-----------|---------------------------------------------------|------|

| Li | st of           | ' <b>Ta</b> ble | S         |                                                   | x    |

| Li | List of Figures |                 |           |                                                   |      |

| A  | bstra           | ıct             |           |                                                   | xiv  |

| 1  | Inti            | roduct          | ion       |                                                   | 2    |

|    | 1.1             | Contr           | ibutions  |                                                   | . 4  |

|    |                 | 1.1.1           | Dynami    | c load balancing of inner-outer iterative solvers | . 5  |

|    |                 | 1.1.2           | Dynami    | c memory adaptation in scientific applications    | . 5  |

|    | 1.2             | Releva          | ance      |                                                   | . 6  |

|    | 1.3             | Organ           | nization  |                                                   | . 7  |

| 2  | Bac             | kgrou           | nd and r  | related work                                      | 9    |

|    | 2.1             | Load            | balancing |                                                   | . 9  |

|    |                 | 2.1.1           | Pools of  | independent tasks                                 | . 10 |

|    |                 | 2.1.2           | Data pa   | rtitioning                                        | . 12 |

|    |                 |                 | 2.1.2.1   | Geometric partitioning                            | . 13 |

|    |                 |                 | 2.1.2.2   | Topological partitioning                          | . 14 |

|    |                 |                 | 2.1.2.3   | Load balancing adaptive computations              | . 16 |

|   |     | 2.1.3 Load balancing under variable external load          | 8  |

|---|-----|------------------------------------------------------------|----|

|   | 2.2 | Addressing memory shortage                                 | 9  |

|   |     | 2.2.1 Out-of-core algorithms                               | 0  |

|   |     | 2.2.2 Virtual memory system modifications                  | 2  |

|   |     | 2.2.3 Memory-adaptive algorithms                           | 3  |

|   | 2.3 | Application-centric adaptive scheduling                    | 5  |

| 3 | Loa | balancing flexible-phase iterations 2                      | 8  |

|   | 3.1 | Flexible-phase iteration                                   | 9  |

|   | 3.2 | Coarse-grain Jacobi-Davidson implementation                | C  |

|   | 3.3 | Load balancing JDcg                                        | 3  |

|   |     | 3.3.1 Experimental evaluation                              | 4  |

|   | 3.4 | Load balancing a fully multigrain Jacobi-Davidson solver   | 6  |

|   |     | 3.4.1 Benefits of multigrain parallelism                   | 6  |

|   |     | 3.4.2 Load imbalance in the full multigrain case           | 8  |

|   | 3.5 | A load balanced Additive-Schwarz preconditioner for FGMRES | g  |

| 4 | Loa | balancing under memory pressure 4                          | 3  |

|   | 4.1 | Load-balanced JDcg under memory pressure                   | :0 |

|   | 4.2 | Avoiding thrashing from within the algorithm               | .4 |

|   |     | 4.2.1 Choosing the parameters                              | 8  |

|   |     | 4.2.2 Experimental results                                 | 9: |

|   | 4.3 | Limitations of the memory-balancing approach               | 2  |

| 5 | A d | namic memory adaptation framework 5                        | 5  |

|   | 5.1 | A portable framework for memory adaptivity                 | 5  |

|   | 5.2 | Elements of the implementation                             | 7  |

|   | 5.3 | Algorithms for adapting to memory availability             | 8  |

|   |     | 5.3.1 Detecting memory shortage                            | g  |

| 5.3.2 Detecting memory surplus |     |        | ng memory surplus | 63                                                     |     |

|--------------------------------|-----|--------|-------------------|--------------------------------------------------------|-----|

|                                |     |        | 5.3.2.1           | Problems with overly aggressive probing                | 63  |

|                                |     |        | 5.3.2.2           | Balancing performance penalties with a dynamic probing |     |

|                                |     |        |                   | policy                                                 | 64  |

|                                | 5.4 | Furth  | er details        | of the adaptation algorithms                           | 68  |

|                                |     | 5.4.1  | Estimat           | ting the static memory size                            | 69  |

|                                |     | 5.4.2  | Calculat          | ting $R_{pen}$                                         | 70  |

|                                |     |        | 5.4.2.1           | A low frequency probing approach                       | 70  |

|                                |     |        | 5.4.2.2           | Probing with higher frequency                          | 72  |

| 6                              | Des | ign of | MMlib:            | : A memory-malleability library                        | 77  |

|                                | 6.1 | The g  | eneral fra        | amework supported by MMLIB                             | 77  |

|                                | 6.2 | Data   | structures        | s                                                      | 78  |

|                                | 6.3 | Core i | nterface a        | and functionality                                      | 79  |

|                                | 6.4 | Optin  | nizations a       | and additional functionality                           | 80  |

|                                |     | 6.4.1  | Memory            | y access at sub-panel granularity                      | 80  |

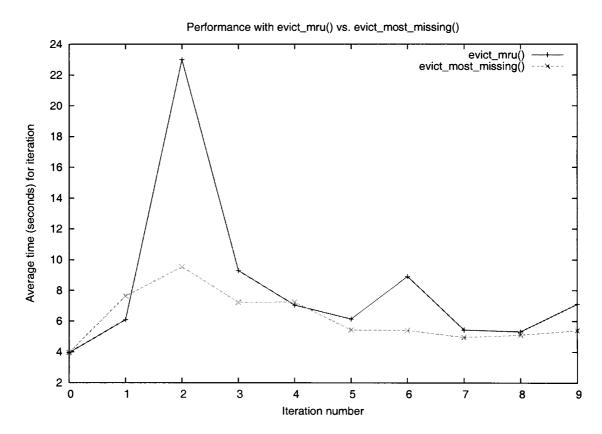

|                                |     | 6.4.2  | Eviction          | n of "most-missing" panels                             | 83  |

| 7                              | Exp | erime  | ntal eval         | luation of memory-adaptation                           | 86  |

|                                | 7.1 | Appli  | cation ker        | rnels                                                  | 86  |

|                                |     | 7.1.1  | Conjuga           | ate Gradient (CG)                                      | 86  |

|                                |     | 7.1.2  | Modified          | d Gram-Schmidt (MGS)                                   | 87  |

|                                |     | 7.1.3  | Monte-C           | Carlo Ising model simulation (ISING)                   | 89  |

|                                | 7.2 | Exper  | imental e         | environments and methodology                           | 91  |

|                                | 7.3 | Choos  | sing the M        | MMLIB parameters                                       | 94  |

|                                |     | 7.3.1  | Panel si          | ize                                                    | 95  |

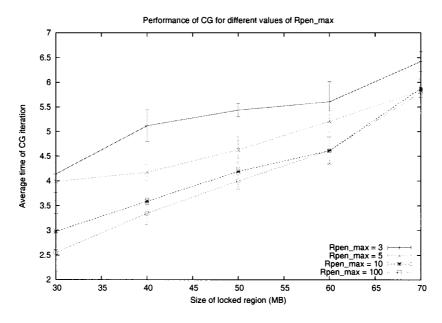

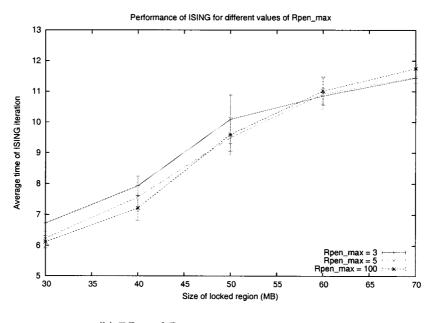

|                                |     | 7.3.2  | $R_{pen\_max}$    | x · · · · · · · · · · · · · · · · · · ·                | 97  |

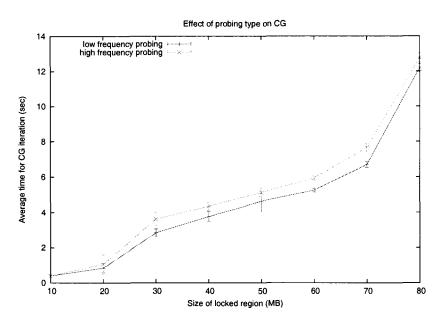

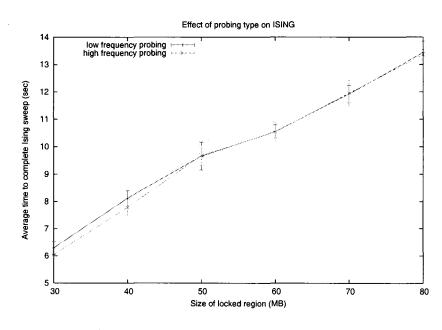

|                                |     | 733    | Choice o          | of probing type                                        | 0.8 |

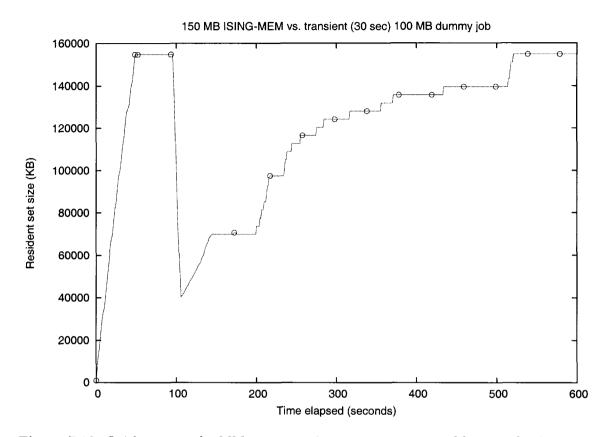

|                  |                    | 7.3.3.1 Static memory pressure                | 98         |

|------------------|--------------------|-----------------------------------------------|------------|

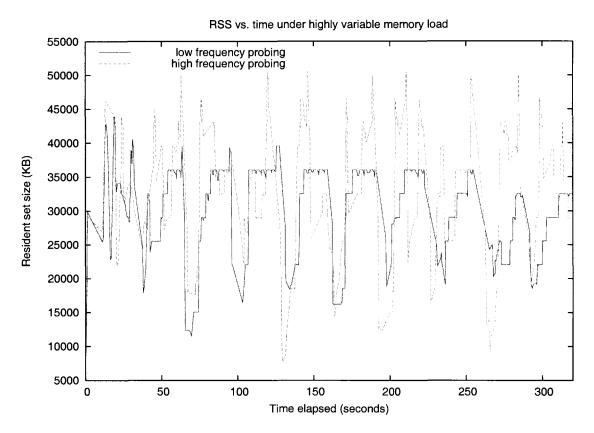

|                  |                    | 7.3.3.2 Highly variable memory pressure       | 100        |

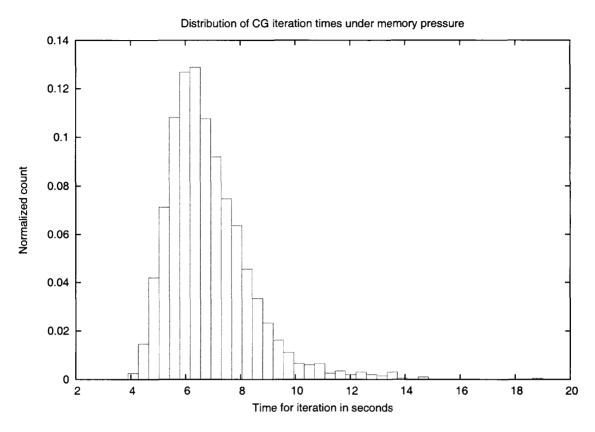

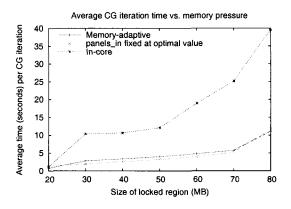

|                  | 7.4                | Graceful degradation of performance           | 102        |

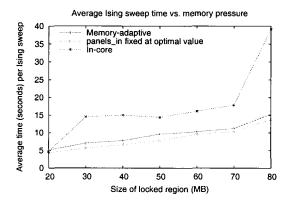

|                  |                    | 7.4.1 Effects of panel write-frequency        | 103        |

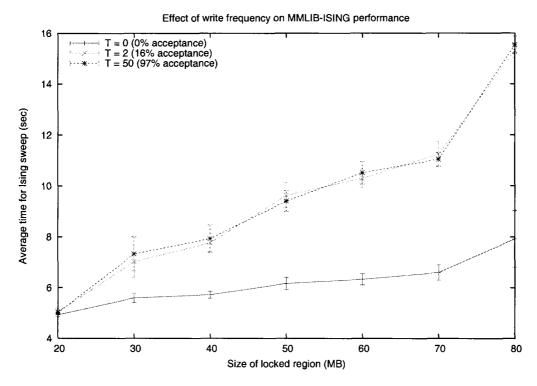

|                  | 7.5                | Quick response to transient memory pressure   | 106        |

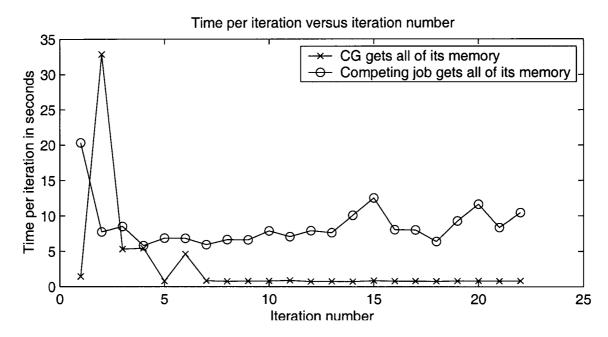

|                  | 7.6                | Adaptive versus adaptive jobs                 | 108        |

|                  | 7.7                | Performance with LRU-friendly access patterns | 110        |

| _                | ~                  | salvaiona and future moule                    | 110        |

| 8                | Con                | clusions and future work                      | 116        |

| 8                | 8.1                | Flexible-phase load balancing                 |            |

| 8                |                    |                                               | 116        |

|                  | 8.1<br>8.2         | Flexible-phase load balancing                 | 116        |

| $\mathbf{A}_{]}$ | 8.1<br>8.2<br>ppen | Flexible-phase load balancing                 | 116<br>117 |

#### ACKNOWLEDGMENTS

This work reflects the influence of a great many people on my life, and I regret that it is not possible to name all of them here; all of them deserve thanks.

I wish to thank all of the members of my dissertation committee for their insightful comments and guidance, which have improved this work tremendously. Foremost among them I thank my advisor, Andreas Stathopoulos, for teaching me a great deal about scientific computing and for taking an active and enthusiastic role in guiding my research. This work reflects a great deal of effort on his part. I thank Dimitris Nikolopoulos for serving as almost a second advisor during the memory-related portions of this work. Robert Voigt deserves special thanks not only for his comments on this work, but also for valuable guidance in my career and professional development. He has always being willing to listen to my problems when I encountered bumps on my road through graduate school. I thank Virginia Torczon for her helpful comments, and for teaching me some of the subtleties of scientific computing when I was the grader for her "Scientific Computing" course. Rich Wolski helped motivate this work with his research on Grid middleware, and deserves special thanks for agreeing to serve on my committee without knowing anything about me.

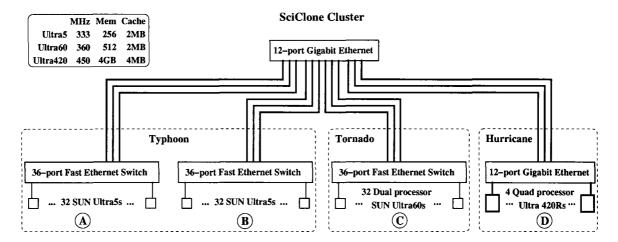

Outside of my committee, other people at William & Mary deserve thanks. Evgenia Smirni taught me me the basics of parallel computing and collaborated on the early stages of the load balancing portion of this work. Xiaodong Zhang impressed upon me the importance of the interplay between algorithms and architecture in his excellent "Advanced Computer Architecture" course. Shiwei Zhang of the Department of Physics exposed me to many areas of computational science—of which I might otherwise have remained ignorant—in his excellent course on computational physics. Tom Crockett kept SciClone up and running and was always ready to resolve technical issues with skill and enthusiasm; additionally, he provided much-needed friendly conversation on the upper floor of Savage House. Jim McCombs provided the Jacobi-Davidson code used in this work, collaborated on the load-balancing work, and was an amicable office mate.

I spent the summer of 2003 working at Los Alamos National Laboratory with Peter Lichtner. Although the work that I did there was unrelated to my dissertation research, the experience was important because it rekindled my enthusiasm for research after several years in graduate school had caused it to wane. I thank Peter for serving as a mentor without parallel during an incredibly intellectually stimulating summer.

I thank Uncle Maury for stimulating my interest in physics in general and computational physics in particular; that led me down the road to becoming a computational scientist.

I thank my wife, Saffron, for her companionship, love, and support though some difficult times as we suffered through our graduate studies together. The years that we have spent in graduate school have been very trying, but thanks to her constant companionship they have also been the best ones of my life.

Lastly, but most importantly, my parents deserve special thanks for all that they have done. Besides being wonderful, loving parents, they impressed the importance of knowledge and learning upon me at a young age, and their gentle encouragement is responsible for all of my academic (and other) success. I thank my mother especially for the countless hours she spent teaching me reading, arithmetic, and so on when I was a young child; I am very fortunate to have had such a patient teacher of these fundamentals. My father deserves credit for teaching me to think rationally and scientifically, and to view the world with curiosity. It is his example that inspired me to pursue a career in the sciences. He has served as my first and closest mentor, answering my endless questions when I was four years old, reading great books to me and my sister, encouraging my ambitious science projects in primary and secondary school, helping me select courses to take as an undergraduate, collaborating with me on my senior thesis work, and helping me through some tough times in graduate school. His influence on my thinking has been inestimable.

This work was supported in part by a Department of Energy Computational Science Graduate Fellowship, provided under grant number DE-FG02-97ER25308 and administered by the wonderful folks at Krell Institute. Some of the work was performed using the Sci-Clone computational cluster at the College of William & Mary, which was enabled by grants from Sun Microsystems, the National Science Foundation, and Virginia's Commonwealth Technology Research Fund.

## List of Tables

| 3.1 | Performance of JDcg with and without load balancing on a system subject    |     |

|-----|----------------------------------------------------------------------------|-----|

|     | to various static external loads                                           | 36  |

| 3.2 | Performance of JDcg with and without load balancing with come-and-go       |     |

|     | dummy jobs on each node                                                    | 37  |

| 3.3 | Performance of the multigrain JD running on different node configurations, |     |

|     | with and without load balancing                                            | 40  |

| 3.4 | Performance of FGMRES when preconditioned with ASM with and without        |     |

|     | load balancing                                                             | 42  |

| 4.1 | Performance of JDcg with and without load balancing with some nodes ex-    |     |

|     | ternally loaded by static, memory intensive dummy jobs                     | 45  |

| 4.2 | Performance of JDcg using the anti-thrashing scheme with a come-and-go     |     |

|     | memory intensive dummy job on one node                                     | 50  |

| 4.3 | Performance of JDcg with the "ideal" anti-thrashing scheme                 | 51  |

| 4.4 | Improvements in execution time of the dummy job because of increased pro-  |     |

|     | cessor throughput due to our anti-thrashing scheme                         | 52  |

| 7 1 | Comparison of the two probing types under highly variable memory pressure  | 103 |

## List of Figures

| 3.1  | The data parallel Jacobi-Davidson algorithm                                  | 32 |

|------|------------------------------------------------------------------------------|----|

| 3.2  | SciClone: The William and Mary heterogeneous cluster of workstations         | 39 |

| 5.1  | Detecting and responding to memory shortage with the naive (and incorrect)   |    |

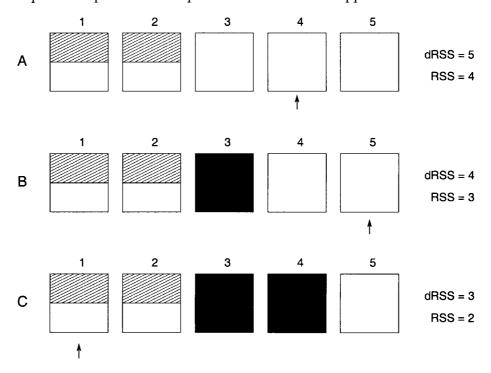

|      | "solution"                                                                   | 60 |

| 5.2  | The algorithm for detecting and responding to memory shortage                | 61 |

| 5.3  | An example of detecting and responding to memory shortage using the algo-    |    |

|      | rithm in Figure 5.2                                                          | 62 |

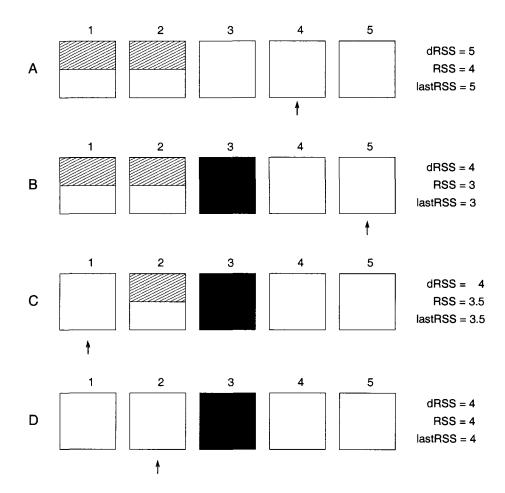

| 5.4  | Graphs depicting the necessity of a dynamic delay parameter in the algorithm |    |

|      | for detecting memory availability                                            | 65 |

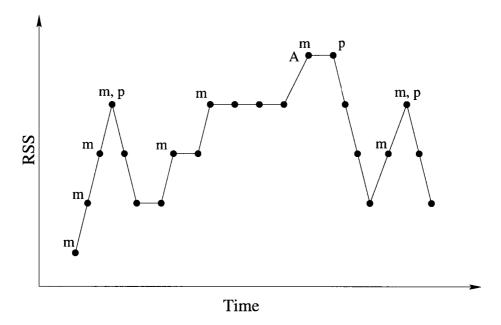

| 5.5  | An example of how peakRSS is determined                                      | 67 |

| 5.6  | The combined algorithm for detecting and adapting to memory shortage or      |    |

|      | surplus                                                                      | 68 |

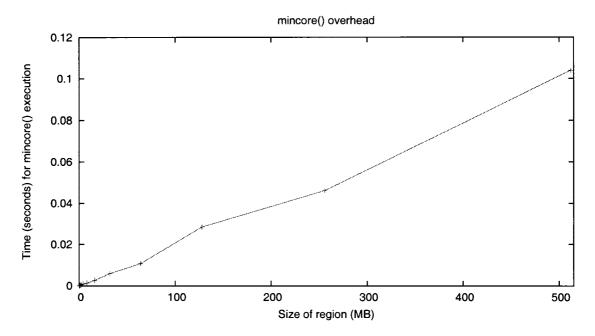

| 5.7  | Overhead as a function of size of the region upon which mincore() is called  | 71 |

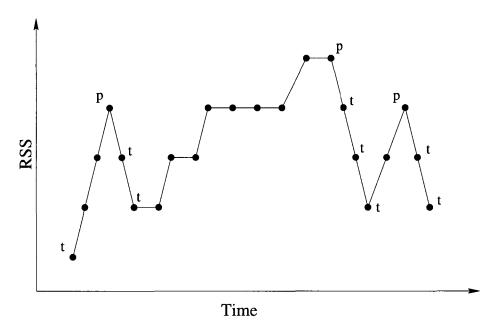

| 5.8  | An example of how troughRSS is determined                                    | 73 |

| 5.9  | The final, complete algorithm for detecting and adapting to memory shortage  |    |

|      | or surplus, using low frequency probing                                      | 75 |

| 5.10 | The final, complete algorithm for detecting and adapting to memory shortage  |    |

|      | or surplus, using high frequency probing                                     | 76 |

| 6.1  | Extended framework modeling the memory access needs of a wide variety of     |    |

|      | scientific applications                                                      | 78 |

| 6.2  | Benefits of using smaller memory transfer units                             | 82  |

|------|-----------------------------------------------------------------------------|-----|

| 6.3  | Benefits of evicting partially swapped out panels                           | 85  |

| 7.1  | Matrix-vector multiplication algorithm for a sparse matrix of dimension N   |     |

|      | consisting of a number of diagonals                                         | 88  |

| 7.2  | The algorithm executed by our MGS test code, which simulates the behavior   |     |

|      | of a GMRES-type solver, generating random vectors of dimension N which      |     |

|      | are added to an orthonormal basis via modified Gram-Schmidt                 | 89  |

| 7.3  | The algorithm for executing a Metropolis sweep through the LxL spin lattice |     |

|      | of the Ising model                                                          | 91  |

| 7.4  | Two different modes in the behavior of the virtual memory system observed   |     |

|      | under the same experimental settings                                        | 93  |

| 7.5  | Relative frequencies of iteration times for memory-adaptive CG running on a |     |

|      | Linux 2.4 machine with 128 MB RAM against a memlock job consuming 70        |     |

|      | MB                                                                          | 94  |

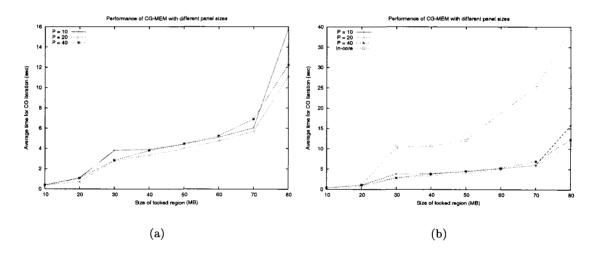

| 7.6  | Effect of panel size on performance of MMLIB-enabled CG                     | 96  |

| 7.7  | Effect of panel size on performance of MMLIB-enabled ISING                  | 97  |

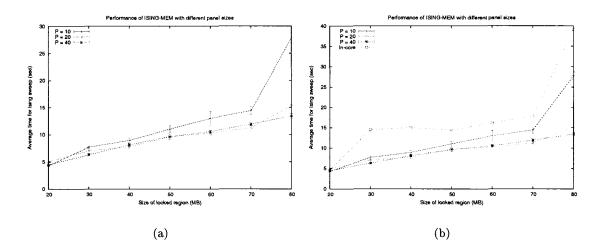

| 7.8  | Effects of $R_{pen\_max}$ on MMLIB performance                              | 99  |

| 7.9  | Comparison of performance using the two methods of calculating $R_{pen}$    | 101 |

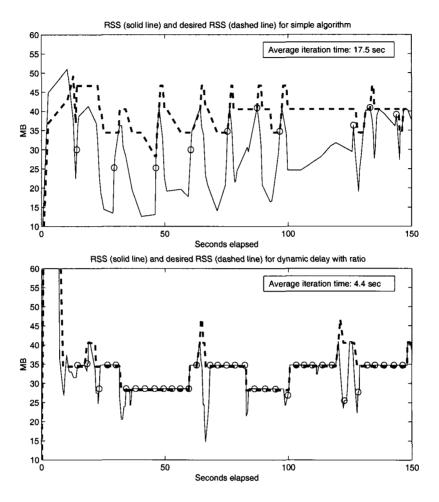

| 7.10 | RSS versus time for the two types of probing in memory adaptive CG under    |     |

|      | highly variable memory load                                                 | 104 |

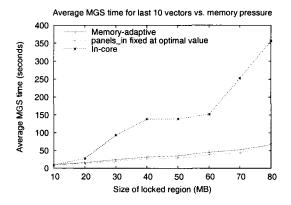

| 7.11 | Performance of the application kernels under constant memory pressure       | 105 |

| 7.12 | Effects of write frequency on MMLIB performance in ISING                    | 107 |

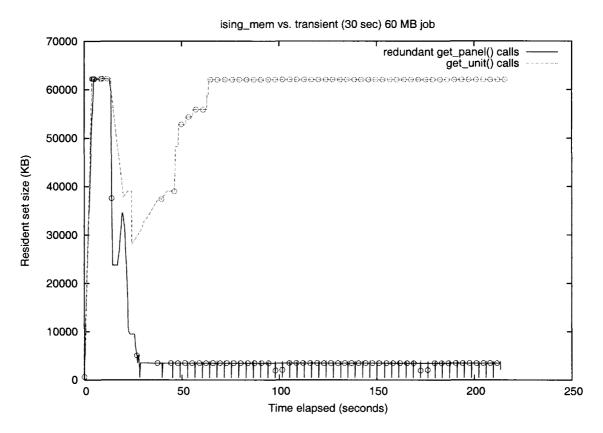

| 7.13 | Quick response by MMLIB to transient memory pressure                        | 108 |

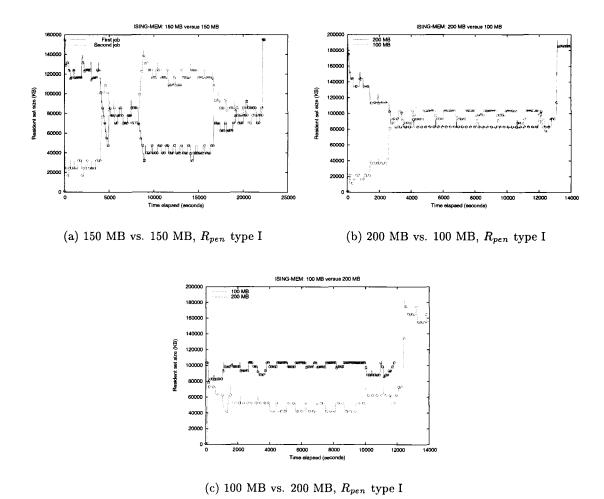

| 7.14 | Profiles of RSS vs. time for two instances of memory adaptive ISING jobs    |     |

|      | running simultaneously, using low frequency probing                         | 111 |

| 7.15 | Profiles of RSS vs. time for two instances of memory adaptive ISING jobs    |     |

|      | running simultaneously, using high frequency probing                        | 112 |

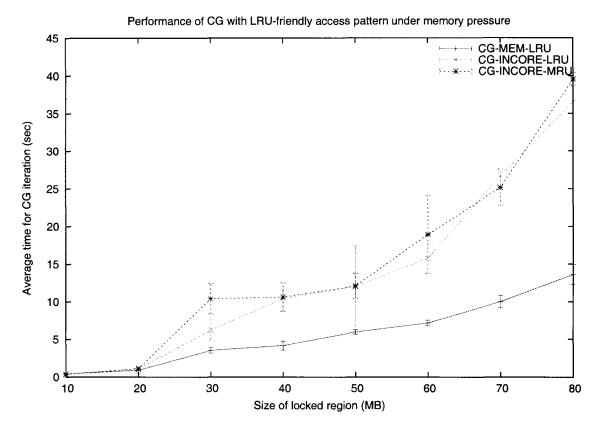

| 7.16 | Performance of in-core and memory adaptive versions of CG-LRU, which uses  |     |

|------|----------------------------------------------------------------------------|-----|

|      | an LRU-friendly access pattern                                             | 114 |

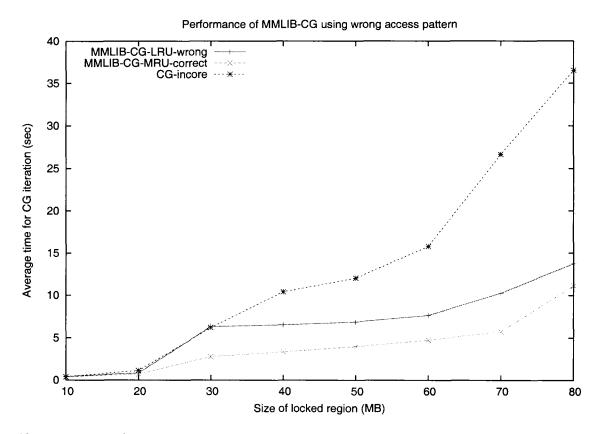

| 7.17 | Performance of memory-adaptive CG versus memory pressure when using        |     |

|      | the wrong panel replacement policy                                         | 115 |

| A.1  | Pseudocode depicting how the LBLIB library can be used to load balance the |     |

|      | .IDcg solver                                                               | 124 |

#### ABSTRACT

As commodity computers and networking technologies have become faster and more affordable, fairly capable machines have become nearly ubiquitous while the effective "distance" between them has decreased as network connectivity and capacity has multiplied. There is considerable interest in developing means to readily access such vast amounts of computing power to solve scientific problems, but the complexity of these modern computing environments pose problems for conventional computer codes designed to run on a static, homogeneous set of resources. One source of problems is the heterogeneity that is naturally present in these settings. More problematic is the competition that arises between programs for shared resources in these semi-autonomous environments. Fluctuations in the availability of CPU, memory, and other resources can cripple application performance. Contention for CPU time between jobs may introduce significant load imbalance in parallel applications. Contention for limited memory resources may cause even more severe performance problems: If the requirements of the processes running on a compute node exceed the amount of memory present, thrashing may increase execution times by an order of magnitude or more.

Our goal is to develop techniques that enable scientific applications to achieve good performance in non-dedicated environments by monitoring system conditions and adapting their behavior accordingly. In this work, we focus on two important shared resources, CPU and memory, and pursue our goal on two distinct but complementary fronts: First, we present some simple algorithmic modifications that can significantly improve load balance in a class of iterative methods that form the computational core of many scientific and engineering applications. Second, we introduce a portable framework for enabling scientific applications to dynamically adapt their memory usage according to current availability of main memory. An application-specific caching policy is used to keep as much of the data set as possible in main memory, while the remainder of the data are accessed in an out-of-core fashion. This allows a graceful degradation of performance as memory becomes scarce.

We have developed modular code libraries to facilitate implementation of our techniques, and have deployed them in a variety of scientific application kernels. Experimental evaluation of their performance indicates that our techniques provide some important classes of scientific applications with robust and low-overhead means for mitigating the effects of fluctuations in CPU and memory availability.

### Chapter 1

## Introduction

The advent of powerful but inexpensive workstations and fast, affordable networking technologies has fundamentally altered the landscape of parallel and distributed computing. Powerful commodity components have led to the emergence of clusters of workstations (COWs) as the primary means of parallel computing at many institutions. On a much grander scale, researchers have been taking steps towards geographically distributed computing, building computational "Grids" that link computing resources between different institutions. Grid environments promise to provide the computational resources necessary for analyzing petabyte-scale data sets and conducting the most computationally demanding of simulations. The impact of these technological developments has been particularly felt in scientific applications, which form a great portion of the high-performance computing workload.

The category of "scientific applications" is large and evolving, and therefore difficult to characterize accurately. We make, however, the following broad observations about scientific applications in parallel and high-performance computing (HPC) environments: First, the applications often work with large quantities of data, because realistic simulation of a problem often requires a large number of degrees of freedom. Second, they tend to follow fairly regular, repetitive data access and communication patterns. Third, they usually have synchronization points at which collective communications occur.

Many modern parallel computing environments possess a degree of complexity that poses problems for conventional scientific applications designed to run on dedicated, uniform resources such as massively-parallel processor (MPP) machines. One source of problems is the heterogeneity that arises naturally in these new settings. For instance, upgrades to a COW may occur in stages, with only specific machines being replaced or added. In other cases, the cluster may simply be a loosely coupled network of personal workstations. In a computational Grid, disparate resources from different institutions may be used in conjunction. Traditional parallel programs attempt to distribute work evenly between all nodes because they target environments in which compute nodes are homogeneous in processing power and memory capacity. When nodes differ considerably in processing speed, such a strategy can result in severe load imbalance as faster processors idle at synchronization points, waiting for their slower brethren to finish. If nodes differ considerably in memory capacity, nodes with higher memory capacities may be underutilized.

Beyond architectural heterogeneity, competition for non-dedicated, shared resources poses even greater challenges. Various economic and practical considerations have made multiprogramming of resources commonplace: In decentralized systems, such as Grid environments or loose networks of personal workstations, space sharing simply may not be a viable option. Owners of smaller COWs may not be willing to sacrifice the time necessary to administer a batch queuing system, or to tolerate the slower turnaround times resulting from waiting in the queue, especially during the development and debugging cycles. In shared memory machines, even when CPUs are space-shared, jobs still compete for memory and I/O resources.

Fluctuations in the availability of CPU, memory, and other resources can cripple application performance. Contention for CPU time between jobs may introduce significant load imbalance in parallel applications. Contention for limited memory resources may cause even more severe performance problems: If the requirements of the processes running on a compute node exceed the amount of memory present, thrashing may increase execution times by an order of magnitude or more.

It is our thesis that the dynamic and unpredictable nature of resource contention in

modern parallel environments necessitates a degree of system awareness and adaptivity that is not present in today's software. Our goal is to develop techniques that allow scientific applications to achieve good performance in non-dedicated environments by monitoring system conditions and adapting their behavior accordingly. In this work, we focus on two important shared resources, CPU and memory, and pursue our goal on two distinct but complementary fronts:

- Application-level dynamic load balancing. We present some simple algorithmic modifications which can significantly improve load balance in a class of iterative methods.

We focus on these methods because they form the computational core of many scientific and engineering applications; improvements to the methods can lead to immediate performance gains in a variety of scientific codes.

- 2. Memory adaptation in scientific and data-intensive codes. We introduce a portable framework for enabling applications to dynamically adapt their memory usage according to current availability of main memory. An application-specific caching policy is used to keep as much of the data set as possible in main memory, while the remainder of the data are accessed in an out-of-core fashion. This allows a graceful degradation of performance as memory becomes scarce.

The combination of system-aware mechanisms for dynamic load balancing and memory adaptation has the potential to change the way computational science is done by enabling efficient use of shared resources that have hitherto been underutilized. We provide some specific tools and techniques for implementing these mechanisms in some specific cases, but our broader goal is to establish an archetype for building system-aware, adaptive applications.

#### 1.1 Contributions

The contributions of this work can be outlined as follows:

#### 1.1.1 Dynamic load balancing of inner-outer iterative solvers

We have studied a novel strategy for dynamic load balancing of a class of inner-outer iterative methods. Our goal has been to enable parallel, iterative, sparse matrix methods—which form the core of many scientific applications—to perform well in heterogeneous and multiprogrammed environments. Our techniques are designed for inner-outer iterative solvers that employ local solvers for the inner iterations, though they are also applicable to other algorithms that possess what we term a *flexible phase* (defined in Chapter 3). We have written a C-library to facilitate use of our load balancing technique, and have used it to implement our scheme in some different solver codes.

We have experimentally demonstrated that our scheme can cope with severe load imbalance under unpredictable external loads in a coarse-grained, block Jacobi-Davidson eigensolver that independently calculates a different correction vector on each processor. This work has been published in [63]. We have also used our load-balancing scheme to enable effective use of a collection of heterogeneous sub-clusters of workstations in a version of the Jacobi-Davidson solver that fully employs the so-called *multigrain* parallelism; see our paper [57]. Finally, we have demonstrated that our method can be used in an additive-Schwarz preconditioned linear system solver to smooth load imbalances due to differences in conditioning of the subdomains, and also to smooth out small load imbalances due to differences in processor speeds.

#### 1.1.2 Dynamic memory adaptation in scientific applications

We have explored a general framework that enables scientific and other data-intensive codes that repetitively access large data sets to dynamically adapt their memory requirements as memory pressure arises. We have developed a modular supporting library, MMLIB, that makes it easy to embed memory-adaptivity in many scientific kernels with little coding effort. The biggest technical hurdle we had to overcome to realize our framework is the lack of information about memory availability provided by operating systems. We have

developed an algorithm that can effectively judge memory availability with minimal reliance on operating system-provided information.

We have used our library to inject memory-adaptivity into three scientific application kernels: a conjugate-gradient linear system solver, a modified Gram-Schmidt orthogonalization routine (surrounded by a GMRES-like wrapper), and a Monte-Carlo Ising model simulation. Though simple, these kernels are representative elements of scientific simulations spanning a diverse range of fields. Experimental evaluation of these memory-adaptive kernels in Linux and Solaris environments has shown that our techniques yield performance several times better than that obtained by relying on the virtual memory system to handle memory pressure. Furthermore, we have demonstrated that these performance gains are not only due to enabling use of application-specific replacement policies, but from avoidance of virtual memory system overheads and antagonism. We have also shown that multiple jobs employing our memory-adaptation techniques can coexist on a node without ill-effects. Our work is presented in [61] and [62].

#### 1.2 Relevance

This work is relevant to both computer scientists and practitioners of computational science. From a computer science perspective, it is significant because it explores adaptation to fluctuating system conditions completely at the application-level; traditionally, adaptation approaches have been more system-oriented. An application-centric approach allows us to exploit knowledge about the application that system software does not possess.

In our work on load balancing parallel computations under unpredictable external loads, we utilize knowledge of the numerics of an important class of iterative methods to dynamically modify the computation—without affecting the end result—to achieve good load balance with very little overhead. This departs from conventional load balancing approaches, which adaptively schedule a computation but do not modify it.

In our work on dynamic adaptation to high levels of memory pressure, we use knowledge

of the memory-access characteristics of an application to manage memory using an appropriate replacement policy and to use units of data transfer suited to the granularity of memory access. Our memory adaptation work is additionally significant because it has explored the interplay of system and application in multiprogrammed systems under extreme levels of memory demand. System and application behavior under such conditions can be extremely unpredictable and has been relatively unexplored; application-specific virtual memory management schemes, for instance, have usually been designed without multiprogramming in mind.

From the perspective of computational science practitioners, this work is relevant because it has the potential to increase their productivity. Many researchers do not have access to dedicated supercomputers or high-end clusters and must meet their computing needs by using either local shared resources such as networks of workstations and small SMPs, or resources shared across a computational grid. The methods we present can enable some important classes of scientific applications to effectively use such resources. These techniques can also improve the productivity of researchers who do have access to dedicated supercomputers by allowing them to run small to moderate-sized jobs on readily available non-dedicated resources, allowing them to conserve their supercomputer allocations and avoid long wait times in compute-center queues.

### 1.3 Organization

The remainder of this document is organized as follows: Chapter 2 relates our work to the current state of knowledge in both load balancing and mechanisms for dealing with memory shortage. Chapter 3 explains our load balancing scheme and presents experimental results demonstrating its effectiveness in balancing CPU load. In chapter 4, we illustrate how the load balancing scheme can be extended to attenuate memory pressure, and we outline the shortcomings of this approach. In chapter 5, we present the essential details of our memory adaptation framework, and in chapter 6 we provide an overview of our software

library, MMLIB, that facilitates use of the framework. In chapter 7 we present experimental evaluations of the memory adaptation strategy as used in three scientific application kernels. Finally, conclusions are presented in chapter 8.

### Chapter 2

## Background and related work

The goal of our work is to allow some classes of scientific applications to perform well in multiprogrammed environments where CPU and memory availability can vary unpredictably. To meet this goal our techniques must maintain good load balance as external CPU loads fluctuate, and adjust memory utilization gracefully as memory availability changes. In this chapter, we present a brief overview of related work in load balancing and mechanisms for addressing memory shortage. Additionally, we describe related work on application-centric adaptive scheduling techniques that dynamically adapt schedules according to resource availability.

### 2.1 Load balancing

Maintaining good load balance is essential to ensure good performance and efficient utilization of processors by a parallel application. Otherwise, CPU cycles will be wasted as lightly loaded processors sit idle waiting for their more heavily loaded brethren to finish. A significant amount of research has focused on the development of methods and software for load balancing within parallel applications, and we outline some of those approaches in this section.

Load balancing is essentially a task-mapping problem, and is thus inextricably linked with the manner in which a computation is decomposed into tasks for parallel execution. The problem is to map a number of tasks onto a set of processors in a way that ensures that

each processor is assigned an amount of work commensurate with its speed. This mapping usually must satisfy other objectives as well, such as limiting the amount of communication required. There are many different strategies for accomplishing these goals, but we can place them into two broad categories based on whether they take a task-oriented or a data-oriented approach to mapping the tasks onto processors. The type of approach that is appropriate is determined by the amount of data required to describe and perform each task, and the cost of moving that data to the appropriate processor. (So the choice between task or data orientation depends on both the properties of the problem to be solved and the properties of the target parallel machine.) If processors can inexpensively obtain the data required to perform a task, a task-oriented approach can be used. Otherwise, a data-oriented approach must be employed because the cost of moving the data for a task is the main limiting factor.

#### 2.1.1 Pools of independent tasks

The task-oriented approach is often known as the pool of tasks paradigm. The problem to be solved is broken into a pool of independent tasks. Processors that need work fetch tasks from the pool, and if additional tasks are generated during the computation, they are placed into the pool. If the size of the tasks is small enough, the pool of tasks approach usually results in excellent load balance. (Tasks that are too large may result in one processor continuing to work while others sit idle because all other tasks have been processed.) In the simplest implementation (master/slave or manager/worker), processors fetch or receive tasks from a single processor that acts as centralized manager of the pool. In addition to being very easy to implement, the master/slave approach maintains global knowledge of the computation state, which facilitates even distribution of tasks and greatly simplifies termination detection. The master/slave approach cannot scale to large numbers of processors, however, because communication with the master becomes a bottleneck.

To improve scalability, a hierarchical approach can be employed, in which workers are

divided into disjoint sets managed by a local sub-master that reports to the central master. If greater scalability is needed, a completely decentralized scheme can be used, making the pool of tasks a distributed data structure. In a decentralized scheme, when a processor runs out of work it sends a potential donor processor a work request. The donor processor to be polled may be chosen in a number of ways: The simplest way is to choose a donor randomly, with all processors having equal probability of being selected. Alternatively, donors can be chosen in a round-robin fashion. The round-robin scheme can employ a global list of processors, or might be restricted to the nearest neighbors of each processor in the network interconnect. Note that if a round-robin scheme is completely decentralized, a donor may receive work requests from multiple processors simultaneously. To prevent this, a hybrid centralized/distributed system may be employed. In such a scheme, the task pool is a distributed data structure, but one processor maintains a global variable that points to the processor to which the next work request should be sent. This improves the distribution of work requests, though contention for access to the global variable somewhat limits scalability. Explanations and analysis of several decentralized pool of tasks schemes and appropriate termination-detection algorithms can be found in [70, 52, 51].

If a computation is decomposed into a large number of small tasks, fetching only one piece of work at a time can result in excessive scheduling overhead. In such situations, an allocation method in which a free processor fetches a chunk of several tasks at a time is usually employed. This reduces scheduling overhead, but care must be taken not to make the chunks too large, because the coarser task granularity may result in increased load imbalance. Kruskal and Weiss [50] used probabilistic analysis to determine an optimal chunk size that balances the trade-offs between very large and very small chunk sizes. Their analysis relies on the assumption of a number of tasks large enough to cancel out variations in the task execution times. Because in practice this assumption often does not hold, other developments in chunk-scheduling employ schemes that start with larger chunk sizes and then gradually decrease the chunk sizes as the computation progresses to prevent

processors from finishing at different times. Such approaches include guided self-scheduling [68], factoring [39], and trapezoidal self-scheduling [85].

The pool of tasks approach can maintain excellent load balance, even in the face of factors such as large variation in the cost of each task, processor heterogeneity, or dynamic variation in external processor load on a time-shared system. Unfortunately, the approach is inapplicable to many scientific problems, since they cannot be broken into independent tasks that can be executed asynchronously. Additionally, the independent tasks often cannot be described with an amount of information that is small enough to prevent excessive communication between master and slave processes.

#### 2.1.2 Data partitioning

If the tasks in a computation cannot be described with a small amount of information, or if dependencies between tasks necessitate frequent inter-processor communication, a data partitioning approach to load balancing should be employed: Rather than thinking in terms of mapping tasks to processors, we map the data objects in the computation (e.g. mesh points or particles) onto processors. Processors then execute those tasks associated with their local data. To load balance a computation, we partition the objects into approximately equal partitions (ensuring load balance) while minimizing the data dependencies between partitions (thus reducing communication costs). If processors vary in speed, the partition associated with a given processor is weighted by its relative speed. What we have called data partitioning is usually referred to as domain partitioning, because it is usually employed to assign portions of a computational domain to processors. Some of the techniques we describe here can be applied to any abstract object that can be modeled as a graph, so we use the more general term "data partitioning".

The partitioning approaches can be grouped into two broad categories: geometric and topological. A geometric approach divides a domain based on the locations of objects in a simulation, and is therefore appropriate for applications such as solid mechanics or particle

simulations, where interactions between computational objects tend to occur between neighbors. A topological method explicitly bases its partitioning on the connectivity of objects in a computation. Typically a computational domain is represented as a graph which is to be equipartitioned in a way that minimizes the edge-cut, which approximates the amount of communication required.

#### 2.1.2.1 Geometric partitioning

The geometric approaches can be classified into two major types: recursive bisection approaches and octree approaches. These categories could also be described respectively as approaches that work with coarse-grained or fine-grained divisions of the geometry. The basic idea of recursive bisection approaches is to cut a domain into two parts such that each part contains an approximately equal number of objects. Each part is then further cut into two smaller parts, and so on, until the required number of partitions have been generated. The simplest such method is Recursive Coordinate Bisection (RCB) [10], also known as Coordinate Nested Dissection (CND). RCB recursively divides the set of objects using a cutting plane orthogonal to the coordinate axis along which the objects are most spread out. The cut is orthogonal to the long axis to reduce the size of the boundaries between subdomains, across which communication will have to occur. RCB is simple, fast, easily parallelizable, and requires little memory, but also tends to produce lower-quality partitionings. A modest improvement is Unbalanced Recursive Bisection (URB) [42], which divides the geometry, rather than the objects, in half. This minimizes the geometric aspect ratio of the partition and thus reduces communication volume, as the amount of information that must be exchanged across boundaries is approximately proportional to their length or area. The effectiveness of both RCB and URB are limited by the somewhat artificial restriction that cuts are always made along coordinate axes. Recursive Inertial Bisection (RIB) [83] eliminates this restriction by calculating the principal axes of inertia of the collection of objects as if they were a collection of particles in a physical system. The domain is then cut by a bisecting plane orthogonal to the principal axis associated with the minimum moment of inertia, which is a naturally "long" direction across which to cut. Geometric bisection methods need not be limited to the use of cutting planes. Based on some interesting theoretical results [34], Gilbert, Miller, and Teng [32] describe a geometric bisection scheme in which circles or spheres are used to bisect domains.

Octree techniques (also known as space-filling curve techniques) for geometric partitioning start with a fine-grained division of the computational domain, and then aggregate these fine-grained pieces into sets that will make up the partitions. The fine-grained division is obtained by recursively dividing a space into a hierarchy of octants. For a 3D domain, the root octant is a cube that encloses the entire domain. This octant is divided into child octants by simultaneously cutting the root octant in half along each axis (forming eight child octants in 3D space). Child octants that contain multiple objects are then recursively divided into sub-octants, and so on, until each object is enclosed by a terminal octant (i.e., one that is not further subdivided). The relationship of octants in the hierarchy is described by a tree data structure known as an *octree*. Octrees are used to represent space in mesh generation, computer graphics, and n-body simulations, among other applications. They also provide a convenient way to partition geometry among processors: By ordering the terminal octants according to their positions along a space-filling curve such as a Peano-Hilbert curve [55], a k-way partitioning can easily be generated by cutting the list into kequal parts [88]. The speed and quality of octree partitioning is roughly equal to that of geometric recursive bisection techniques.

#### 2.1.2.2 Topological partitioning

Geometric partitionings can be calculated very quickly and can be quite effective for computations in which interaction between objects is a function of geometric proximity, such as in n-body or solid mechanics problems. If geometric proximity is a poor indicator of interaction between objects, however, using a more expensive topological method that explicitly

considers the connectivity of the objects can yield far superior partitionings.

One of the simplest topological methods is Levelized Nested Dissection (LND) [31]. LND starts with an initial vertex (a pseudo-peripheral vertex is the best choice), and then visits neighboring vertices in a breadth-first manner. When half of the vertices have been visited, the graph is bisected into the set of vertices that have been visited, and those that have not. This process is applied recursively until the desired number of partitions have been created. The idea behind LND is actually quite similar to geometric bisection methods: distance from the initial vertex is used to cut across a "long" dimension of the graph.

Spectral methods [69, 78] use a very different approach for computing partitionings. The partitioning problem is really a discrete optimization problem: minimize the edge-cut while dividing the graph into k equal parts. This discrete optimization problem is NP-complete, but the problem can be approximated by a continuous optimization problem that is more easily solved. Spectral methods solve the continuous problem by finding some extremal eigenvalue/eigenvector pairs of a matrix derived from the connectivity information of the graph. Spectral methods tend to produce high quality partitions, but solving the eigenproblem can be computationally expensive.

Partition refinement methods refine a sub-optimal partitioning of a graph, and are often used as graph partitioners themselves by applying them to a random partitioning. Kernighan and Lin [48] developed an iterative algorithm (known as the KL algorithm) that improves a graph bisection using a greedy approach to determine pairs of vertices to swap between partitions. Variations of the KL algorithm are used for refinement in several graph partitioning contexts, some of which we discuss below.

Some of the most popular graph partitioning methods being used today are multilevel methods [37, 45]. Multilevel methods form a sequence of increasingly coarse approximations of the original graph by collapsing together selected vertices from finer representations of the graph. The graph is initially partitioned at the coarsest level using a single-level algorithm such as those described above. This partitioning is then propagated back through the finer

approximations, being refined at each level via a KL-type algorithm. Multilevel approaches are very effective for two reasons. First, the initial partitioning can be easily computed for the coarsest graph, because it hides many edges and vertices of the original graph. Second, incremental refinement algorithms can quickly make large changes to the partitioning by working with coarser versions of the graph. Chaco [36], METIS/ParMETIS [43, 44], and JOSTLE [87] are some popular software packages that implement multilevel methods.

#### 2.1.2.3 Load balancing adaptive computations

If external load is not a factor, and if the amount of work per object is known and does not vary during the course of the computation, a static partitioning can be used. The partitioning can be computed as a sequential preprocessing step at the beginning of a simulation, using a package such as METIS or Chaco, or in parallel using a package such as ParMETIS or JOSTLE. In many computations, however, the amount of work assigned to each processor can vary unpredictably, either because the number of objects in a partition can vary, or because the amount of work per object is unknown. For example, if the objects are grid points in an adaptive mesh refinement (AMR) calculation [12, 11], the amount of work for a partition may grow as the mesh is refined. If objects are cells in a particle-in-cell simulation, the amount of work associated with an object varies as particles advect into and out of the cells. Some simulations utilize adaptive physics, in which the physics model used at a mesh point—and thus the work associated with that point—may change as the calculation progresses. In all of these cases, the computational domain must be repartitioned as the computation progresses, because a partitioning that results in good load balance at the beginning of the computation may yield very poor load balance later.

Dynamic repartitioning can be done by simply computing a new global partitioning from scratch. However, this generally incurs an unacceptable amount of costly data migration, because the new partitioning can be very different from the existing one. Instead, the old partitioning should be adjusted in a way that mitigates load imbalance, while also

minimizing the amount of data migration needed to arrive at the new partitioning. Scratch-remap repartitioners [66] attempt to do this by calculating a new partitioning of the graph from scratch, and then permuting the labels of the new partitions so their overlap with the old partitions is maximized.

Scratch-remap approaches result in excellent load balance and low edge-cut, but still involve a relatively high amount of data movement. For this reason, incremental approaches that make a series of small changes to the partitions to restore load balance are usually favored instead. Most of these methods employ a diffusive approach, in which objects move from heavily loaded processors to more lightly loaded neighbors by a diffusion-like process. The number of objects to be moved from a processor is based on the processor workload, while the choice of which objects get moved is usually made using KL-like criteria. In the simplest incarnations [21], a first-order finite difference discretization of the diffusion equation is used to calculate the amount of work that should be moved between processors at each iteration of the method. Because the first-order stencil is compact (only involving nearest neighbors), such methods can be executed locally by a processor. These methods can be slow to converge to a load balanced state, however, so more complex methods use some global information to accelerate convergence to load balance. The method of Hu, Blake, and Emerson [38] (implemented in ParMETIS and JOSTLE) uses information from all processors to perform an implicit solve for the steady-state solution of the diffusion equation, and then migrates data in one step to reach this state of load balance.

Although local methods are usually slower than global methods to achieve load balance, they can be executed asynchronously, whereas global methods cannot. This is a significant advantage for two reasons. First, load balance can be corrected as it arises, without having to wait for the next synchronization. Second, although most scientific applications have natural synchronization points, certain applications [28, Chapter 14] do not, so the use of a global method introduces artificial (and costly) synchronizations.

Parallel partitioning packages such as ParMETIS or JOSTLE provide algorithms for

computing incremental repartitionings, but once the new partitioning is obtained, performing the actual data migration can be a difficult chore for the application programmer. Packages such as Zoltan [22] and PREMA [7, 8] provide tools and frameworks for managing and automatically migrating the objects in adaptive computations. PREMA uses multithreading to support asynchronous load balancing, and thus is particularly suited to very irregular computations.

#### 2.1.3 Load balancing under variable external load

In our discussion so far, we have only considered the load that is internal to an application. In a multiprogrammed environment, however, the total load on a processor can vary unpredictably due to load from processors external to a given application.

Provided that the granularity of the tasks is not too coarse, the pool of tasks paradigm can work well (and automatically) in the presence of external load. Data partitioning approaches, however, face major difficulties in dealing with such loads. External load can conceivably be accounted for by weighting each processor according to its load and then sizing the partitions based on those weights. However, the high cost of repartitioning combined with the dynamic and unpredictable nature of external workloads makes this impractical. If external load conditions stay fairly constant, the cost of repartitioning to reflect that load can be worthwhile. If the decision to repartition proves wrong—that is, if the external workload changes dramatically soon after partitioning—it can be very costly. Because of the difficulties involved in external load prediction, repartitioning is generally not used to cope with external load.

In Chapter 3 we present a load balancing scheme for a very specific but important class of scientific algorithms, inner-outer iterative methods that employ local inner iterations. These algorithms are not amenable to a pool-of-tasks approach, and—for the reasons discussed above—load balancing by dynamic repartitioning is impractical. We present a scheme that provides good load balance for these algorithms in the face of dynamic and unpredictable

load, without any reliance on data migration or performance predictions.

What we call our "load-balancing" scheme differs fundamentally from other load-balancing schemes in the conventional sense of the word. The pool-of-tasks and data partitioning approaches we have described distribute a fixed set of tasks in a balanced way across a set of processors. Our load balancing scheme also distributes tasks in a balanced manner across a set of processors, but the set from which these tasks are drawn is not fixed. That is, the set includes optional tasks: each task (hopefully) helps move the algorithm to its target, but not all tasks must be completed for this target to be reached. The tasks to execute are chosen to maximize load balance and reach the target as quickly (in wall-clock time) as possible: tasks are associated with data on a particular processor, and slower processors execute fewer of the associated tasks. This flexibility in choosing which tasks to execute stems from the intrinsic properties of the inner-outer iterative methods.

#### 2.2 Addressing memory shortage

Jobs in non-dedicated environments contend not only for CPU time, but for memory resources as well. Memory pressure can cause extreme degradation of performance. Its effects are especially pronounced if an affected node is part of a synchronous parallel job, as the immense slowdown experienced by that node can cause incredible load imbalance. In many cases this imbalance cannot be corrected by load balancing techniques that may be in place within the application. For instance, if the job is running on a shared-memory computer, migrating work to other processors on that machine fixes nothing. Even in distributed memory environments, problems remain: The usually excellent load balance provided by a pool-of-tasks scheme may disappear as the slowdown on an affected node increases the granularity of its tasks to excessive levels. If load balancing is performed through domain repartitioning, memory pressure may render the very cost of computing a new partitioning prohibitive! Even when calculating the new partitioning is practical, deciding how to weight each partition is a difficult problem, as operating systems typically provide very little

information about memory usage. For these reasons and others, explicit consideration of memory pressure and its mitigation is needed in non-dedicated environments, in addition to good CPU-load balancing approaches.

In this section we discuss several approaches that have been used to remedy memory pressure in dedicated and non-dedicated environments.

#### 2.2.1 Out-of-core algorithms

Since the earliest days of the computer age, researchers have been faced with problems too large to solve using the main memory of a computer. In response to these problems, many out-of-core algorithms have been developed. An out-of-core algorithm [84, 86, 25, 71] is one that has been designed to provide acceptable performance despite the slow nature of accessing secondary storage. Such an algorithm may be obtained by taking a conventional (in-core) algorithm, implementing it to access large, contiguous blocks of data, and re-scheduling its independent operations in a manner that maximizes the re-use of data that have been brought into main memory. Some out-of-core algorithms go beyond simply rescheduling independent operations, altering conventional algorithms so that their data dependencies are more amenable to data re-use. These alterations may sacrifice some numerical stability or require more CPU operations, but admit much better out-of-core schedules.

Out-of-core algorithms bear many similarities to cache-optimized algorithms, as the goal of both is to maximize use of faster levels of a memory hierarchy by scheduling operations in a manner that provides good spatial and temporal locality. Both types of algorithms benefit from many of the same optimization techniques: Structuring loop nests to eliminate strided accesses is important at all levels of the memory hierarchy. Many dense matrix algorithms are optimized for out-of-core use by structuring them to operate on blocks of a matrix at a time. Such blocking techniques are also used to achieve cache optimality in numerical libraries such as BLAS [53, 24, 23] and LAPACK [2]; they are so important, in fact, that computer vendors make great efforts to precisely tune blocking factors in

their implementations of these libraries, and the ATLAS project [89, 90] provides software to automatically tune these factors. Cache-oblivious algorithms [30, 15], such as the one employed by the popular FFTW library [29], operate using a divide-and-conquer approach that splits a problem into subproblems that fit into the cache; this approach eliminates the need to tune hardware-specific parameters. Although these algorithms have been proposed with cache-optimality in mind, these techniques are also beneficial in out-of-core settings [20].

Despite their similarities, there are important differences in the design of out-of-core versus cache-optimized algorithms. These stem from two fundamental differences between the levels of the memory hierarchy that the two types of algorithms target. First, the main-memory/disk bandwidth ratio is usually much higher than the cache/main-memory bandwidth ratio in a computer system. This means that modifications that increase CPU operations but improve out-of-core performance by reducing disk I/O may perform worse than unmodified versions when executed in-core, despite possibly higher cache efficiency. Second, cache memory usually has limited associativity—that is, blocks brought from main memory cannot be placed anywhere in the cache, but must be placed in a limited number of specific locations in the cache. Many cache-optimization techniques are designed to reduce so-called "conflict" misses that stem from limited cache associativity. Because main-memory is fully associative (i.e., blocks from disk may be placed anywhere), such optimizations do not improve out-of-core performance.

Out-of-core algorithms have been in use for decades to allow computers to solve problems too big for their physical memory. These codes have been designed to operate with a fixed amount of memory, however, and are unsuitable to deal with the transient memory shortages encountered on multiprogrammed systems. An out-of-core code could certainly be used to avoid memory pressure, but the utility of such an approach is dubious: Though the algorithm would work efficiently when memory is scarce and an in-core algorithm would thrash, when memory is plentiful the out-of-core algorithm will not take advantage, continuing to use the slow disk instead of the much faster main memory.

## 2.2.2 Virtual memory system modifications

A virtual memory (VM) system that can transparently handle a high degree of memory pressure is highly desirable, as this could free the application programmer from having to worry about memory shortages. Transparent VM systems fall short, however, because no generic page replacement policy that is appropriate for the memory access patterns of all applications is known. Most systems employ an LRU-like policy. Under such a policy, an application that repeatedly loops through a data set, for example, will incur thrashing even if memory shortage is slight. Recently proposed general-purpose replacement algorithms, such as LRFU [54] and LIRS [40] and the related CLOCK-Pro algorithm [41], eliminate some of the shortcomings of LRU at the expense of introducing some additional complexity. None of these algorithms has yet made its way into a production operating system.

In addition to replacement policy problems, the generic prefetching policy and the fixed page size employed by most VM systems may be inappropriate for the granularity of data access in an application. This is especially true when memory pressure forces pages to be written to swap space, which can be highly fragmented and generally does not support prefetching. The shortcomings of generic VM systems have led many researchers to propose operating system modifications that expose portions of the VM subsystem to applications. The Mach microkernel [1] provided an external pager interface that allowed applications to control the movement of pages between main memory and secondary storage. It did not export control over page replacement policy, however. McNamee and Armstrong [60] extended Mach's external pager interface to allow application programmers to control page replacement. Harty and Cheriton [35] designed and implemented an external page-cache management scheme in the V++ kernel. In their scheme, the VM system provides a cache of physical pages to an application, and it is the responsibility of the application to manage that physical memory. Krueger et al. [49] devised a similar scheme, but gave it a mod-

ular, object-oriented design to allow programmers to use application-defined replacement policies without having to re-implement large portions of the VM system. Cao et al. [18] implemented a system to give applications control over file caching, prefetching and disk scheduling.

Although application-specific virtual memory management schemes are useful in some situations, they suffer some shortcomings. These schemes have generally not been designed with multiprogrammed environments in mind, and assume a fixed amount of physical pages will be available to the process at runtime. Additionally, such schemes are not useful to the typical computer user precisely because they require significant modifications to an operating system kernel. This precludes their use in most computing settings because the operating system does not support such a scheme and cannot be modified to do so. Even if such a system is available to a code developer, writing an application to use such a system incurs severe portability penalties. Memory pressure solutions that do not require OS modification are more desirable to the typical application programmer.

Nikolopoulos [64] developed a runtime system that transparently adapts the memory footprint of running processes as memory availability fluctuates. This solution requires no modification of the operating system and is targeted specifically at multiprogrammed environments. This approach bears many similarities to the memory-adaptation framework we present in Chapter 5, although our framework is even more application-centric: memory adaptation decisions are based solely on measurements local to the application, and we use application-specific replacement policies and units of data transfer.

## 2.2.3 Memory-adaptive algorithms

Not a great deal of literature on memory-adaptive algorithms exists. Most of it comes from the field of database management, in which dealing with huge data sets is commonplace. Pang et al. [67] conducted one of the earliest memory adaptation studies, investigating external sorting. External (viz., out-of-core) sorts are frequently used in database systems to order query results and to perform certain join operations. An external sort is conducted in two phases, a "split" phase and a "merge" phase. In the split phase, an in-core algorithm is used to arrange unsorted data into a set of sorted runs. In the merge phase, the runs are merged into a single sorted run. Pang et al. discussed how the algorithms used for the split phase could adapt to memory shortage by writing out a run of sorted tuples to reduce buffer usage. To respond to a memory increase, more relations should be brought into the buffer for sorting. They also introduced an adaptation strategy for the merge phase, which they termed dynamic splitting: If memory shortage arises during a merge, it should be split into smaller steps that can be performed with the available memory. If there is a memory surplus, then more merges are run at once. Pang et al. did not implement any of their proposed strategies, however, choosing to only utilize simulation in their study. A later study by Zhang and Larson [92] also addressed memory adaptation for external mergesort; it included experimental evaluation of their strategy. Their implementation was designed only to address memory pressure arising from contention between concurrent sorts. Because competing sorts all obtain memory through the same buffer manager, determining the amount of available memory is not a problem. In a general-purpose time-shared system, however, one of the chief difficulties in implementing memory-adaptive algorithms is devising an effective way to determine the amount of available memory.

Barve and Vitter [9] have developed a theoretical framework for proving lower bounds on the resource consumption of memory-adaptive algorithms. Their motivation comes from database management systems, but they also prove bounds for standard matrix-matrix multiplication, fast Fourier transform computation, and LU factorization. Their model assumes that a memory-adaptive algorithm is aware of the amount of memory available to it at all times. Although operating systems do not provide such information, in Chapter 5 we present an algorithm that uses a "gray-box" approach [4] to closely approximate this information with minimal reliance on system-provided information.

## 2.3 Application-centric adaptive scheduling

Schedulers of parallel programs in non-dedicated environments must consider current and future system loads in an attempt to match a job with a set of resources that will meet its requirements. This is a remarkably difficult task, however, and conventional, system-oriented schedulers usually yield poor results in such settings. In response to the limitations of such systems, newer, more application centric approaches have emerged. Though very diverse, these new approaches follow a common thread of interaction between systems and applications to dynamically adapt their schedules according to resource availability.

Polychronopoulos and Nikolopoulos [65] have presented extensions to the kernel scheduler combined with a user-level scheduling module that coordinates the scheduling of communicating threads of parallel jobs and also prevents thrashing by suspending threads at memory-allocation points if memory becomes overcommitted. Such a scheduler could also be used with memory-adaptive applications (such as those presented in Chapter 7) that could modify their memory requirements instead of suspending when an allocation request cannot be met.

Projects such as AppLeS [13, 14] and Active Harmony [46] present complete frameworks for matching applications to appropriate resources and updating application schedules as resource availability changes during execution. AppLeS (Application Level Schedulers) use a completely application-level methodology. An AppLeS-enabled application has its own, specific application-level scheduler that discovers and identifies viable resource sets, determines candidate schedules, selects a schedule that best satisfies the user's performance criteria, and executes the application using that schedule. For long-running applications, the AppLeS agent may refine and re-deploy the schedule as resource availability changes. AppLeS does not provide a custom runtime system; instead, it relies on the existing infrastructure (e.g. Globus [27], NetSolve/GridSolve [3], MPI [79]) for discovering and utilizing compute resources, along with the Network Weather Service [91] to gauge current and predict future resource utilization. Because the AppLeS methodology is entirely application-

driven, it is especially suitable to non-centrally controlled computing environments.

Like AppLeS, Active Harmony matches applications to appropriate resources and reschedules them as resource availability fluctuates. In Active Harmony, however, decisions about application scheduling are made by a centralized resource manager rather than the applications themselves. Centralized decision making is employed in an effort to maximize overall efficiency and throughput. Active Harmony provides a "tuning interface" through which applications export information about possible application configurations. A manager then dynamically tailors the application configuration according to resource availability. For example, a hybrid client-server database that can process queries on either the client or server side could be configured to process queries at the server when there are few clients, but be reconfigured to process queries on client nodes when many clients are using the system.

Systems like AppLeS or Active Harmony can place quite a burden on the user, as often very detailed resource-utilization information must be provided. For instance, Active Harmony requires that the user specify the resource requirements of different options, the granularity at which configuration changes can be performed, the cost of switching between the configurations, and (optionally) a way in which the response time of a given configuration can be calculated. Chang and Karamcheti [19] have developed a resource management framework that eases the burden on the user by providing a virtual execution environment which permits automatic, off-line generation of resource-utilization information.

The adaptive scheduling approaches we have just cited and the techniques for dynamic adaptation to CPU and memory load presented in this dissertation are complementary. Systems such as AppLeS and Active Harmony attempt to identify the "best" schedule for an application, and to refine that schedule as resource availability changes. Our techniques, on the other hand, provide applications with a degree of malleability that enables them to cope with a set of resources that may at times be far from "best" due to fluctuations in resource utilization. Using a system such as AppLeS to select the optimal schedule, and

techniques such as ours to optimize the use of the scheduled resources makes sense. This seems especially true when one considers the overheads involved in re-scheduling onto a different set of resources. Applications that can achieve acceptable performance on less-than-ideal resource sets can reduce the need for re-scheduling and thus avoid some of the associated costs.

## Chapter 3

## Load balancing flexible-phase iterations