Dynamic Supply Noise Measurement Circuit Composed of Standard Cells Suitable for In-Site SoC Power Integrity Verification

#### Y. Ogasahara, M. Hashimoto, and T. Onoye Osaka University, Japan

#### SoC Power Integrity Verification

- Measurement circuit suitable for embedding

- Area

- Layout/routing cost

- Circuit design cost

- Synchronization with clock for digital circuit

|                                       | sample &<br>hold | Improved<br>ring osci.[1] | Proposed<br>circuit |

|---------------------------------------|------------------|---------------------------|---------------------|

| Time/voltage resolution               | $\bigcirc$       | 0                         | 0                   |

| Circuit design cost                   | Х                | 0                         | Ø                   |

| Physical design cost<br>for embedding | $\Delta$         | Ø                         | Ø                   |

| area                                  |                  | 0                         | 0                   |

| synchronization<br>with clock         | 0                | X                         | 0                   |

| [1] T. Sato, et. al, CICC 2006        |                  |                           |                     |

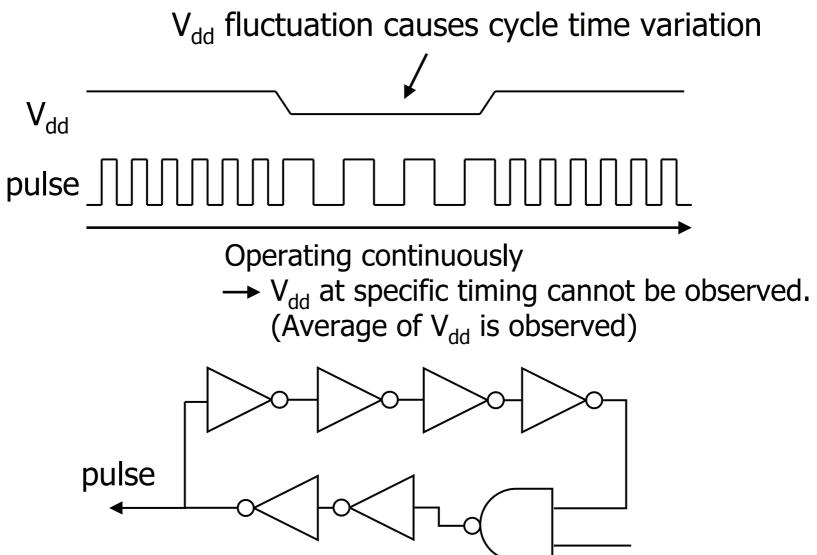

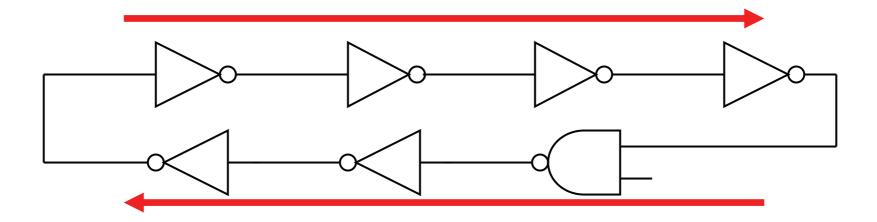

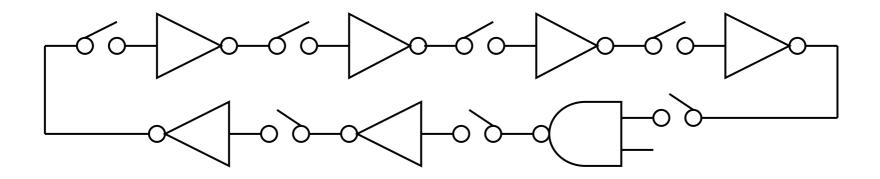

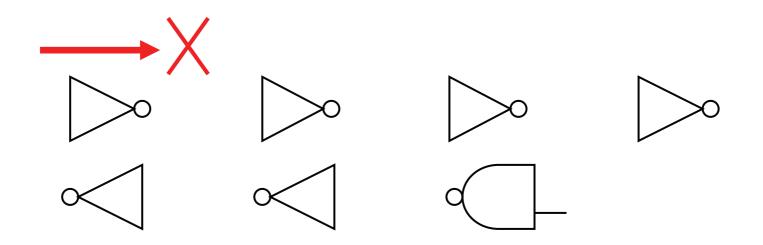

### Ordinary ring oscillator

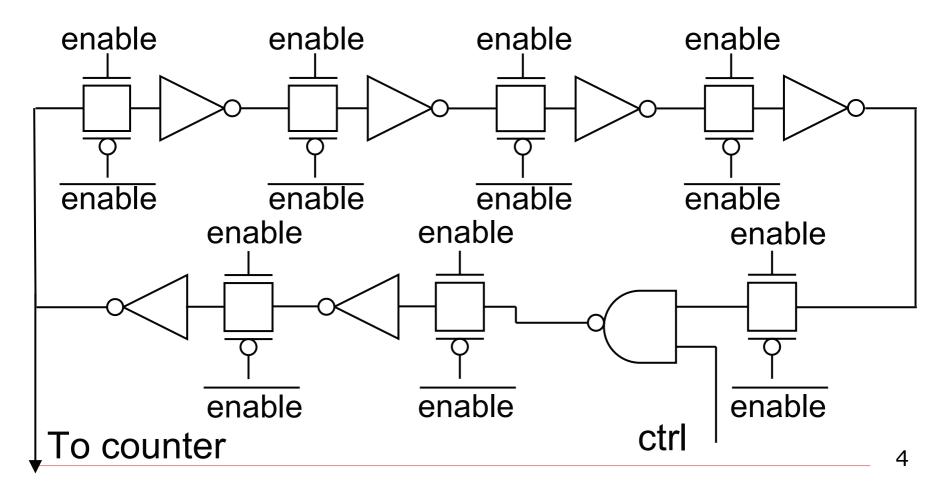

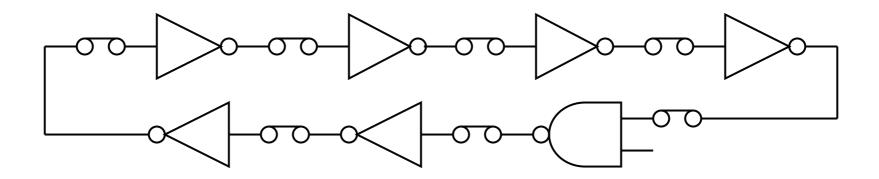

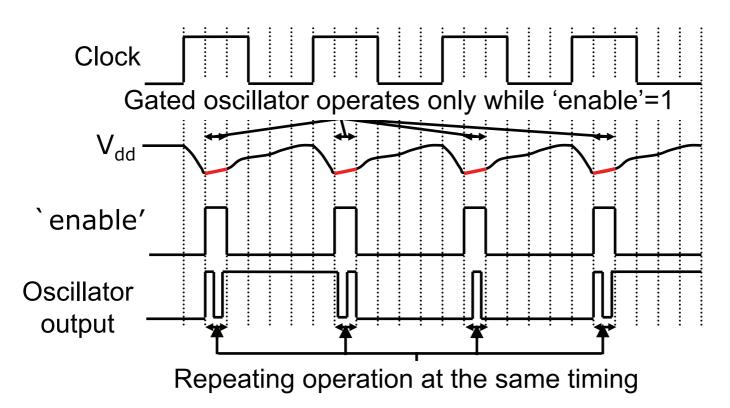

### Operation of gated oscillator

Operating only while `enable'=1 — Capturing V<sub>dd</sub> at specified timing

Accumulating cycle count by repetition

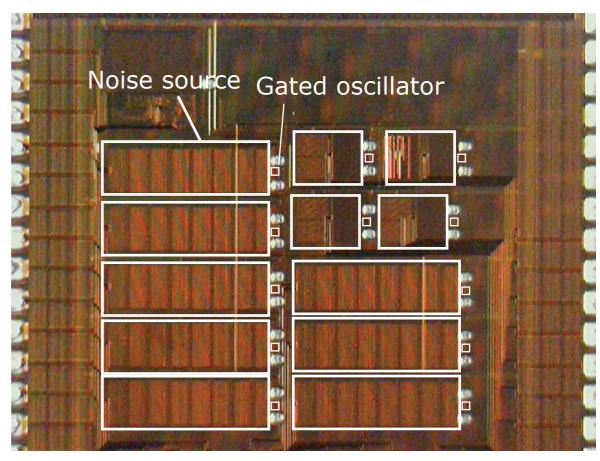

### Micrograph of test chip

Process: 90nm CMOS Supply voltage: 1.0V Area: 1.54 x 1.54mm Num. of gates: 100k

Test structures including noise sources and gated oscillators are implemented.

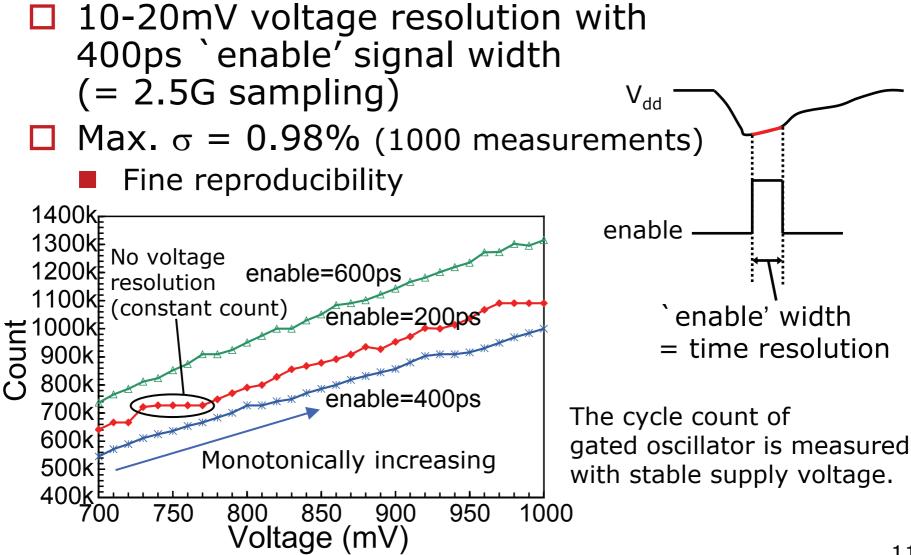

#### Voltage resolution of ``gated oscillator"

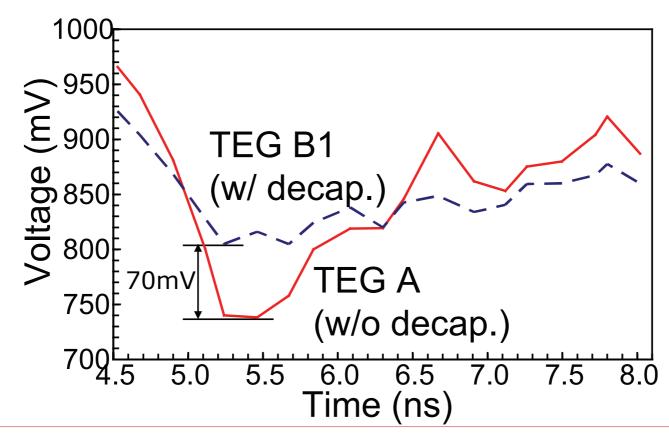

#### Waveform observation

- □ 70mV difference of peak drop was observed.

- Dynamic noise waveform is observed with gated oscillator.

# Features of proposed circuit

- □ Waveform sampling with digital circuit

- Consisting of standard cells

- Dedicated power and bias lines are not needed.

- Circuit design is easy.

- Physical design (place, route) cost is small.

- Size and shape are flexible.

- Small area

- 11.76µm X 15.12µm

(A layout sample in 90nm process)

- □ Synchronization with any external clock

- Application for SoC power integrity verification

# Thank you