#### **PAPER**

## Effect of hysteretic and non-hysteretic negative capacitance on tunnel FETs DC performance

To cite this article: Ali Saeidi et al 2018 Nanotechnology 29 095202

View the <u>article online</u> for updates and enhancements.

### IOP ebooks™

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research.

Start exploring the collection - download the first chapter of every title for free.

https://doi.org/10.1088/1361-6528/aaa590

# Effect of hysteretic and non-hysteretic negative capacitance on tunnel FETs DC performance

Ali Saeidi<sup>1</sup>, Farzan Jazaeri<sup>1</sup>, Igor Stolichnov<sup>1</sup>, Gia V Luong<sup>2</sup>, Qing-Tai Zhao<sup>2</sup>, Siegfried Mantl<sup>2</sup> and Adrian M Ionescu<sup>1</sup>

E-mail: ali.saeidi@epfl.ch

Received 3 December 2017 Accepted for publication 5 January 2018 Published 26 January 2018

#### **Abstract**

This work experimentally demonstrates that the negative capacitance effect can be used to significantly improve the key figures of merit of tunnel field effect transistor (FET) switches. In the proposed approach, a matching condition is fulfilled between a trained-polycrystalline PZT capacitor and the tunnel FET (TFET) gate capacitance fabricated on a strained silicon-nanowire technology. We report a non-hysteretic switch configuration by combining a homojunction TFET and a negative capacitance effect booster, suitable for logic applications, for which the *on*-current is increased by a factor of 100, the transconductance by 2 orders of magnitude, and the low swing region is extended. The operation of a hysteretic negative capacitance TFET, when the matching condition for the negative capacitance is fulfilled only in a limited region of operation, is also reported and discussed. In this late case, a limited improvement in the device performance is observed. Overall, the paper demonstrates the main beneficial effects of negative capacitance on TFETs are the overdrive and transconductance amplification, which exactly address the most limiting performances of current TFETs.

Supplementary material for this article is available online

Keywords: tunnel FET, ferroelectric, negative capacitance, NC-TFET

(Some figures may appear in colour only in the online journal)

#### 1. Introduction

As CMOS technology is continuing its relentless down-scaling, new challenges are encountered to sustain the performance of integrated circuits; among these, the reduction of the threshold voltage and voltage multiply are high priorities of the research community. Among alternative structures, tunnel FETs (TFETs) are the most promising steep-slope switch candidates that are making use of quantum-mechanical band-to-band tunneling (BTBT) [1–3]. The most critical challenge in TFETs is to realize a high *on*-current without compromising the subthreshold swing. The *on*-current of a TFET is the integral of the transmission probability,  $T_{\rm WKB}$ , of the interband tunneling barrier over the source-channel junction [4, 5]. This barrier can be approximated by a

triangular potential [2], so  $T_{\rm WKB}$  can be calculated using the Wentzel-Kramer-Brillouin (WKB) approximation [6]:

$$T_{

m WKB} pprox \exp\Biggl(-rac{4\lambda\sqrt{2m^{\star}}\sqrt{E_{

m g}^3}}{3q\hbar(E_{

m g}+\Delta\Phi)}\Biggr),$$

(1)

where  $m^{\star}$  is the effective mass and  $E_{\rm g}$  is the bandgap. Here,  $\lambda$  is the screening tunneling length that describes the spatial extent of the transition region at the source-channel interface [4]. In a TFET, at a constant drain voltage  $(V_{\rm d})$ , the increase of the gate voltage  $(V_{\rm g})$  modulates the device surface potential, which reduces  $\lambda$  and increases the energetic difference between the conduction band in the source and the valence band in the channel  $(\Delta\Phi)$ . This means that in the first

<sup>&</sup>lt;sup>1</sup> Ecole Polytechnique Federale de Lausanne (EPFL), Lausanne, Switzerland

<sup>&</sup>lt;sup>2</sup> Peter Grunberg Institut 9 (PGI-9), Julich, Germany

approximation, the drain current is a super-exponential function of  $V_{\rm g}$  and a high *on*-current requires a high transparency of the tunneling barrier, thus maximizing  $T_{\rm WKB}$  [7].

Recently, it has been suggested that the integration of a ferroelectric material to the gate stack of conventional field effect transistors (FETs) can provide a feasible solution to step up the gate voltage. The underlying idea consists of exploiting the negative capacitance (NC) region of ferroelectric materials, which is defined as  $C_{\rm FE} = {\rm d}Q/{\rm d}V_{\rm FE}$ , where Q and  $V_{\rm FE}$  refer to the charge density per unit area and the voltage drop over the ferroelectric, respectively [8–10]. It is well established that the use of a ferroelectric negative capacitor in-series with the gate of a field effect transistor could offer an internal voltage amplification [11–13], which is expected to increase the tunneling probability in TFETs [14, 15].

Previous works on NC tunnel FETs have mainly theoretically investigated the performance of these type of devices [14, 16] and there are a few experimental demonstrations [17], major focus being on the achieved low swing value. Here, we explore and demonstrate the double beneficial effect of negative capacitance on both decreasing the subthreshold swing and improving the overdrive. Despite the fact that the used experimental devices are homojunction silicon TFETs with relatively modest performance, the overdrive improvements obtained by connections with ferroelectric capacitors fulfilling the negative capacitance matching are the best reported to date. In addition, we experimentally show that a hysteresis-free behavior of NC-TFETs can be achieved only under a matching condition between the ferroelectric NC and the gate capacitance of the baseline TFET. A non-hysteretic switch configuration using a homojunction silicon-based TFET and an NC booster is also investigated. The improvement of the performance of the non-hysteretic NC-TFET is compared with a hysteretic one, showing a limited gain when the matching condition is not fully satisfied. Overall, the paper demonstrates that the negative capacitance can be indeed employed as an efficient booster of tunneling field effect transistors to simultaneously enhance the overdrive current (which is the main disadvantage of TFETs compared to MOSFETs) and extend the low slope region.

#### 2. Theory

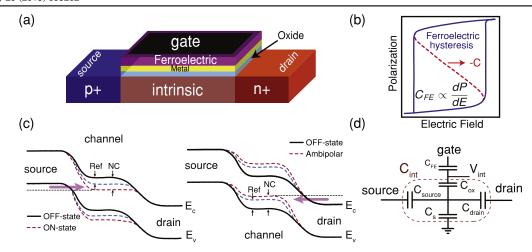

The NC-TFET structure and its operation principle are schematically depicted in figure 1. The gate stack of a conventional TFET is replaced by a series combination of a ferroelectric and a linear dielectric [18]. The use of an intermediate metallic film has the advantage to avoid any non-uniform potential profile along the source-drain direction [10]. The NC region of ferroelectric materials is unstable and exhibits hysteretic jumps in the polarization. However, it can be stabilized if a series capacitance, such the one formed by a conventional oxide and a semiconductor in an MOS structure, is placed in-series with a ferroelectric negative capacitor

(figure 1(b)). The challenges of using BTBT together with the NC in a single device are related to the matched design of capacitances (ferroelectric and in-series stabilizing MOS capacitance) in a regime of operation where a significant boosting of TFET electrical performance can be achieved [12, 19]. In order to have a non-hysteretic NC switch, the total capacitance of the structure looking into the gate needs to be positive in the whole range of operation [18, 20]. Accordingly, the matching condition of the NC-TFET to have a sufficient amplification in the non-hysteretic operation of the device can express as it follows [21, 22]:

$$C_{\text{total}} = (C_{\text{FE}}^{-1} + C_{\text{inf}}^{-1})^{-1} > 0,$$

(2)

$$\beta = \frac{\partial V_{\text{int}}}{\partial V_{\text{g}}} = \frac{C_{\text{FE}}}{C_{\text{FE}} + C_{\text{int}}} \gg 1, \tag{3}$$

where  $\beta$  is the amplification factor due to the differential amplification of NC,  $C_{\rm int}$  and  $C_{\rm total}$  represent the equivalent capacitance of the baseline TFET and NC-TFET, respectively (figure 1(d)). The amplification factor,  $\beta$ , is introduced as the derivative of the internal voltage with respect to the gate voltage and its rather a differential voltage gain [12, 22]. The absolute value of the ferroelectric negative capacitance ( $|C_{\rm FE}|$ ) and  $C_{\rm int}$  need to be relatively close, while the total capacitance of the structure should remain positive in the whole gate voltage range [12]. Using the amplification factor,  $\beta$ , the subthreshold swing (SS) and transconductance ( $g_{\rm m}$ ) of an NC switch can be indicated as

$$SS_{NC} = \left(\frac{\partial log I_{d}}{\partial V_{g}}\right)^{-1} = \frac{\partial V_{int}}{\partial log I_{d}} \times \frac{\partial V_{g}}{\partial V_{int}} = \frac{SS_{ref}}{\beta}, \quad (4)$$

$$g_{\text{m-NC}} = \frac{\partial I_{\text{d}}}{\partial V_{\text{g}}} = \frac{\partial I_{\text{d}}}{\partial V_{\text{int}}} \times \frac{\partial V_{\text{int}}}{\partial V_{\text{g}}} = g_{\text{m-ref}} \times \beta.$$

(5)

In the region where the ferroelectric provides an effective negative capacitance,  $\beta>1$  and the *on*-current will be boosted. Nevertheless, a direct analytical expression that quantitatively links  $\beta$  to the total drain current of the NC-TFET cannot be provided as the tunneling current depends on the surface potential near the tunneling junction in a complex way.

#### 3. Experiments

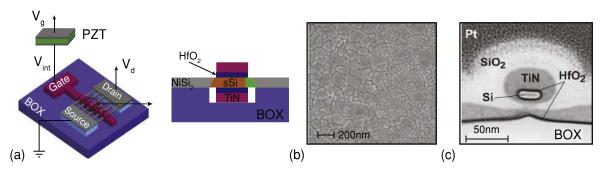

The employed experimental configuration of the NC-TFET in this work is depicted in figure 2(a) where a PZT capacitor is externally connected to the gate of a strained silicon-nanowire (Si-NW) array TFET. Such external electrical connection offers the flexibility of testing tens to hundreds of PZT capacitor values until the best matching, according to equations (2) and (3) is obtained. The employed configuration corresponds to a metal–ferroelectric–metal–insulator–semiconductor structure that is commonly used for the experimental configuration of

**Figure 1.** NC-TFET structure and operation principle. (a) Cross-section schematic of an n-type NC-TFET. (b) P-E characteristic of ferroelectric materials that can be stabilized and provide an effective NC if it placed in-series with a positive capacitor. (c) Band diagram of the NC-TFET which is presented for  $V_g > 0$  (left) and  $V_g < 0$  (right) corresponding to the normal operation and ambipolar behavior of the n-type NC-TFET. The amplified gate voltage reduces the energetic difference between the conduction band in the source and valence band of the channel that results in an enhanced tunneling current. (d) Simplified capacitance model of the NC-TFET where  $C_{\text{source}}$  and  $C_{\text{drain}}$  represent the gate overlapping capacitance with source and drain, respectively. The ferroelectric, oxide, and semiconductor capacitances are expressed as  $C_{\text{FE}}$ ,  $C_{\text{ox}}$ , and  $C_{\text{s}}$ .

**Figure 2.** (a) Experimental configuration of investigated NC-TFETs, where the gate of a Si-NW array TFET is loaded by a PZT capacitor. (b) SEM analysis of the PZT indicating the polycrystalline nature of the film. (c) TEM image of the silicon-nanowire TFET. The nanowire array TFETs have a cross-section of  $6 \times 30 \text{ nm}^2$  and a gate length of 350 nm.

negative capacitance field effect transistors [10]. For this study,  $46 \pm 3$  nm of Pb(Zr<sub>43</sub>,Ti<sub>57</sub>)O<sub>3</sub> (PZT) ferroelectric film has been grown via the chemical solution deposition root on a Pt-coated silicon wafer. The polycrystalline PZT film has a dense columnar grain structure with a grain size of  $200 \pm 100$  nm (figure 2(b)). The fabrication process and the electrical characterization of the PZT thin film are extensively discussed in the supplementary materials, which are available online at stacks.iop.org/NANO/29/095202/mmedia. The nanowire array TFETs have a cross-section of  $6 \times 30$  nm<sup>2</sup> with a gate length of 350 nm (figure 2(c)). The structural data and the fabrication procedure of reference TFETs are also explained in detail in supplementary materials.

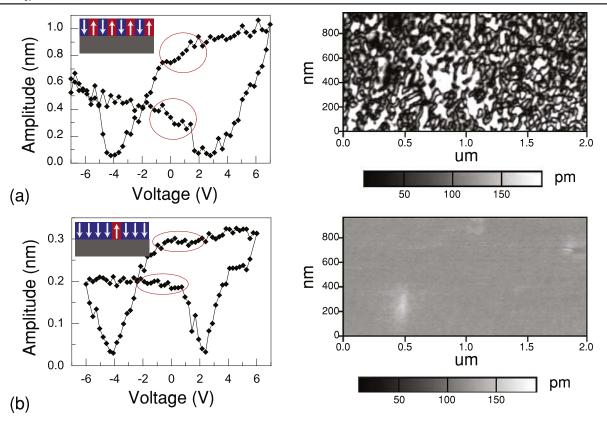

Generally, high-quality epitaxial ferroelectric layers are considered suitable for NC devices as they are more likely to form a mono-domain state characterized by a simple coercive field [23]. This is in contrast with the typical behavior of polycrystalline films, which tend to form complicated polydomain patterns with a broad distribution of nucleation

energies and coercive fields [24–26]. Here, we show that this behavior can be changed dramatically by a repetitive bipolar voltage stress, known as the training procedure of ferroelectric. It should be noted that the training procedure of ferroelectric is different from the well-known wake-up phenomena. The wake-up effect corresponds to the increase of existing remanent polarization after a large number of switching cycles ( $>10^3$ ) [27, 28]. Here, we are raising the point that by applying a limited number of bipolar voltage stress, dipoles can be aligned in the same direction which leads to a mono-domain-like behavior of the polycrystalline ferroelectric. Figure 3 depicts the piezoelectric response measured on a PZT capacitor before (figure 3(a)) and after (figure 3(b)) the training. Piezoelectric loops measured through the top electrode of the PZT capacitor after 20 cycles at  $\pm 7$  V, represent a sharp switching and nearly constant piezoelectric response within the voltage range from -2to 1 V (or from 2 to -1 V). This behavior suggests that the poled polycrystalline ferroelectric layer approaches the

Figure 3. Piezoelectric response of the employed PZT thin film. Results are measured before (a) and after (b) the training procedure of ferroelectric. (a) Illustrates the broad distribution of nucleation energies and coercive fields while (b) represents the mono-domain like behavior of the poled PZT after 20 cycles at  $\pm 7$  V.

mono-domain behavior and does not switch at least at low DC voltages [23]. Note that the piezoelectric loops collected on the as-fabricated capacitors without any training reveal different behavior typical for region-by-region poly-domain switching expected from a polycrystalline film. Consequently, the demonstration of the NC effect using a polycrystalline ferroelectric layer constitutes a significant step towards the integration of NC gates in CMOS technology [23]. In fact, fabrication of epitaxial perovskite layers on silicon is an extremely challenging task, whereas polycrystalline ferroelectrics such as PZT can be integrated, as shown in previous reports [29, 30].

#### 4. Results and discussions

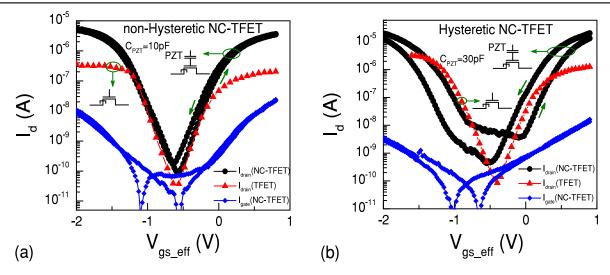

Figure 4 reports experimental transfer characteristics data measured on n-type Si-NW array TFETs with and without connecting a PZT capacitor. The reference homojunction TFETs have  $I_{\rm on} \sim 0.1~\mu{\rm A}$  at  $V_{\rm gs\_eff} = 0.9~{\rm V}$  and  $V_{\rm ds} = 0.5~{\rm V}$  (where  $V_{\rm gs\_eff} = V_{\rm gs} - V_{\rm th}$  and the constant current method at  $I_{\rm d} = 10^{-7}~{\rm A}$  is employed for threshold voltage extraction) with a swing in the order of 100– $150~{\rm mV~dec}^{-1}$  and show ambipolar behavior. The performance of baseline TFETs corresponds to moderate silicon-based tunnel FETs [2, 31, 32]. It should be noted that although TFETs have been

proposed to realize sub-60 mV dec<sup>-1</sup> swing, however, the experimental demonstration of a sub-thermal swing in silicon TFETs is extremely challenging. Besides that, high current values compromise the subthreshold swing [2]. The presented characteristics in figure 4 belong to structures with different reference TFETs which are not totally identical due to the process variation. The gate current of TFETs is very low and negligible compared to the drain current over the whole operation range. A significant double improvement in subthreshold slope and overdrive of the TFET is shown in figure 4(a) when the ferroelectric and the gate capacitances are matched so that a non-hysteretic NC operation is achieved. The  $I_{on}$  is boosted over the whole range of operation, enhanced up to 100 times of its original value at the maximum gate voltage. This is explained by the fact that the NC effect behaves as an efficient electrical booster of the surface potential  $(\psi_s)$  and the body factor (m) of the TFET in the region following the barrier narrowing. This is fundamentally reflected into a body factor reduction less than 1, acting as a performance booster where the on-current of TFETs would otherwise start to have a sloppy dependence on the gate voltage [2, 4]. It should be remarked that the surface potential boosting of NC effect not only increases the tunneling probability but also improves the region over which the tunneling current is integrated. In addition to, considering Landau-Khalatnikov equation, high order terms of the

**Figure 4.** Transfer characteristics of a non-hysteretic and a hysteretic NC-TFET where the negative capacitance matching condition is fulfilled in the entire range of the operation (a) and in a limited range of the gate voltage (b). The reference devices correspond to Si-NW array *n*-type TFETs with a drain voltage of 0.5 V.

ferroelectric charge cannot be neglected at high gate voltages that result in an enhanced negative capacitance effect [33]. The NC effect acts as the TFET performance booster near subthreshold and for the overdrive region. Therefore, the gate voltage can be reduced by 65% maintaining the same level of the output current. Although the reported NC-TFET here do not exhibit a sub-thermal swing like other state of the art heterojunction tunnel FETs [34, 35], the reported experimental characteristics show two remarkable facts: (i) the highest overdrive and transconductance improvements reported today with NC as technology booster, (ii) the extension of the minimum subthreshold region for higher current values [36, 37]. Additionally, our results fully demonstrate that negative capacitance can be used based on an additive strategy with other TFET performance boosters so that improvements are cumulative.

Another device architecture with a different PZT capacitor and TFET, matching the condition of NC only in a limited region (at high gate voltages) is reported in figure 4(b). In this late case, the NC-TFET operation is fully hysteretic and the performance boosting is narrowed down to a reduced region. All measurements have been carried out at the low drain voltage of 0.5 V due to the fact that high values of the drain voltage provide a non-uniform potential profile that will change the negative capacitance condition [22]. Both figures 4(a) and (b) report the recorded gate leakage current in all range of experiments, proving that its level is systematically lower than the  $I_{\rm on}$  and, then, that leakage and charge trapping mechanisms can be neglected in the reported effects. Moreover, this hysteretic leakage presents the typical signature of the ferroelectricity of PZT capacitors. The obtained enhancement in the TFET performance should not be mistaken with the effect of the ferroelectric polarization switching that always occurs with a huge hysteresis. The reported non-hysteretic improvement in the current and conductance can be only achieved in a well-designed negative capacitance transistor.

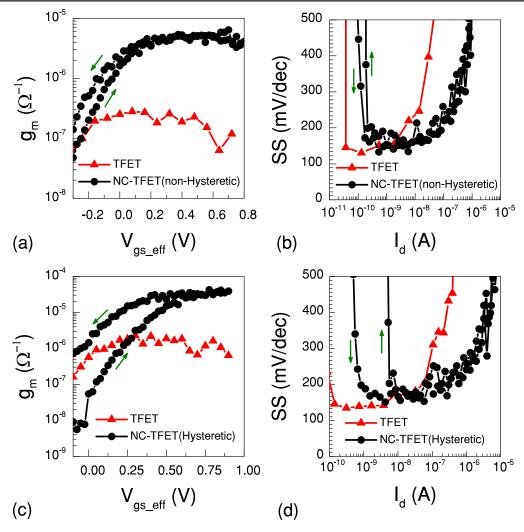

In figure 5, we report the improvement induced by the use of the negative capacitance on TFET transconductance and subthreshold slope, in non-hysteretic and hysteretic modes of operation. Double sweep measurements with a negligible hysteresis for a device that fulfills the analytical condition of the non-hysteretic negative capacitance (corresponds to the presented device in figure 4(a)) are reported in figures 5(a) and (b). In this case, the ferroelectric is stabilized and provides an effective NC in the whole range of the gate voltage which results in an amplification factor above unity  $(\beta > 1)$  in both subthreshold and overdrive regions. Figure 5(a) represents the transconductance boosting by a factor of 10-100 compared to the reference TFET. The largest improvement (higher  $\beta$  value) occurs in the overdrive region due to the surface potential amplification, caused by the NC effect where  $g_{\rm m}$  is increased up to two orders of magnitude. This evidences that the negative capacitance provides a very strong performance boosting effect in TFETs. Figure 5(b) illustrates a smaller, yet clear improvement of the subthreshold swing by the NC effect, in agreement with the recently reported theoretical results [38, 39]. As a consequence of the subthreshold slope and overdrive enhancement, the on-current is boosted over the whole operation range.

Figures 5(c) and (d) summarize the effect of the PZT negative capacitance booster on DC electrical performance of the hysteretic NC-TFET (figure 4(b)) fulfilling the NC matching condition in a limited region. The transconductance is boosted for high gate voltages, reaching a factor of 10 at the maximum gate voltage (figure 5(c)). The subthreshold slope shows no considerable enhancement (figure 5(d)) as the NC matching condition is not fulfilled for low gate voltages. It is remarkable that from variously tested devices, only for the ones that closely verifying the NC stability condition,

**Figure 5.** Experimental performance improvement of non-hysteretic and hysteretic NC-TFETs corresponding to the presented devices in figures 4(a) and (b). The transconductance is boosted up to 100 times of its original value (a) and the low slope region is extended over 2 decades of current (b) in the case of the non-hysteretic NC-TFET. A more limited enhancement is obtained in the transconductance of the hysteretic NC-TFET (c) without any boosting in the subthreshold slope (d).

such a performance boosting is observed. Otherwise, a ferroelectric capacitor out of the range of the stability condition in-series with the gate of a TFET would provide a hysteresis without performance boosting. This type of device could be a proper candidate for hysteretic low power logic or for one transistor (1T) Fe-TFET memory applications [39].

Conclusion

In short, it has been reported that the negative capacitance effect can be efficiently utilized to significantly improve the most limiting performances of tunnel FETs: *on*-current, transconductance, and overdrive. It was demonstrated that by properly designing the ferroelectric gate stack, fulfilling the condition for the non-hysteretic NC-TFET, the conduction performance can be improved by many orders of magnitude and a significant overdrive current can be obtained. This strong effect is explained by the voltage amplification caused

due to the negative capacitance effect. By its insights and reported experiments, this study proposes a new path to the adoption of both homojunction and heterojunction TFETs with an improved performance, while a negative capacitance booster is properly designed and additively integrated into their gate stack.

#### **Acknowledgments**

The authors acknowledge the Swiss National Science Foundation (Grant No. 149495) and, in part, the ERC Advanced Grant Milli-Tech (Grant No. 695459) for providing financial support for this work.

#### **ORCID iDs**

Ali Saeidi https://orcid.org/0000-0003-1637-3269

Adrian M Ionescu https://orcid.org/0000-0003-0265-5281

#### References

- [1] Takagi S, Iisawa T, Tezuka T, Numata T, Nakaharai S, Hirashita N, Moriyama Y, Usuda K, Toyoda E and Dissanayake S 2008 Carrier-transport-enhanced channel CMOS for improved power consumption and performance IEEE Trans. Electron Devices 55 21–39

- [2] Ionescu A M and Riel H 2011 Tunnel field-effect transistors as energy-efficient electronic switches *Nature* 479 329–37

- [3] Choi W Y, Park B-G, Lee J D and Liu T-J K 2007 Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec *IEEE Electron Device Lett.* 28 743–5

- [4] Wu C, Huang R, Huang Q, Wang C, Wang J and Wang Y 2014 An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs *IEEE Trans*. *Electron Devices* 61 2690–6

- [5] Dash S and Mishra G P 2016 An extensive electrostatic analysis of dual material gate all around tunnel FET (DMGAA-TFET) Adv. Nat. Sci.: Nanosci. Nanotechnol. 7 025012

- [6] Knoch J, Mantl S and Appenzeller J 2007 Impact of the dimensionality on the performance of tunneling FETs: bulk versus one-dimensional devices *Solid-State Electron*. 51 572–8

- [7] Zhang Q, Zhao W and Seabaugh A 2006 Low-subthresholdswing tunnel transistors *IEEE Electron Device Lett.* 27 297–300

- [8] Salahuddin S and Datta S 2008 Use of negative capacitance to provide voltage amplification for low power nanoscale devices *Nano Lett.* 8 405–10

- [9] Salvatore G A, Bouvet D and Ionescu A M 2008 Demonstration of subthrehold swing smaller than 60 mV/ decade in Fe-FET with P(VDF-TrFE)/SiO<sub>2</sub> gate stack *IEEE Int. Electron Devices Meeting* pp 1–4

- [10] Rusu A, Salvatore G A, Jimenez D and Ionescu A M 2010 Metal-ferroelectric-metal-oxide-semiconductor field effect transistor with sub-60 mV/decade subthreshold swing and internal voltage amplification *IEEE Int. Electron Devices Meeting* pp 16–3

- [11] Appleby D J R, Ponon N K, Kwa K S K, Zou B, Petrov P K, Wang T, Alford N M and ONeill A 2014 Experimental observation of negative capacitance in ferroelectrics at room temperature *Nano Lett.* 14 3864–8

- [12] Khan A I, Yeung C W, Hu C and Salahuddin S 2011 Ferroelectric negative capacitance MOSFET: Capacitance tuning and antiferroelectric operation *IEEE Int. Electron Devices Meeting* pp 11–3

- [13] Ricinschi D, Harnagea C, Papusoi C, Mitoseriu L, Tura V and Okuyama M 1998 Analysis of ferroelectric switching in finite media as a Landau-type phase transition J. Phys.: Condens. Matter 10 477

- [14] Kobayashi M, Jang K, Ueyama N and Hiramoto T 2017 Negative capacitance for boosting tunnel FET performance IEEE Trans. Nanotechnol. 16 253–8

- [15] Saeidi A, Jazaeri F, Bellando F, Stolichnov I, Luong G V, Zhao Q-T, Mantl S, Enz C C and Ionescu A M 2017 Negative capacitance as performance booster for tunnel FETs and MOSFETs: an experimental study *IEEE Electron Device Lett.* 38 1485–8

- [16] Kobayashi M, Jang K, Ueyama N and Hiramoto T 2016 Negative capacitance as a performance booster for tunnel FET 2016 IEEE Silicon Nanoelectronics Workshop (SNW) (Piscataway, NJ: IEEE) pp 150-1

- [17] Ionescu A M *et al* 2010 The hysteretic ferroelectric tunnel FET *IEEE Trans. Electron Devices* **57** 3518–24

- [18] Saeidi A, Jazaeri F, Stolichnov I and Ionescu A M 2016 Double-gate negative-capacitance MOSFET With PZT gate-stack on ultra thin body SOI: an experimentally calibrated simulation study of device performance *IEEE Trans*. Electron Devices 63 4678–84

- [19] Cano A and Jimenez D 2010 Multidomain ferroelectricity as a limiting factor for voltage amplification in ferroelectric fieldeffect transistors Appl. Phys. Lett. 97 133509

- [20] Saeidi A, Jazaeri F, Bellando F, Stolichnov I, Enz C C and Ionescu A M 2017 Negative capacitance field effect transistors; capacitance matching and non-hysteretic operation 2017 47th European Solid-State Device Research Conf. (ESSDERC) (Piscataway, NJ: IEEE) pp 78–81

- [21] Jimenez D, Miranda E and Godoy A 2010 Analytic model for the surface potential and drain current in negative capacitance field-effect transistors *IEEE Trans. Electron Devices* 57 2405–9

- [22] Rusu A, Saeidi A and Ionescu A M 2016 Condition for the negative capacitance effect in metal-ferroelectric-insulatorsemiconductor devices *Nanotechnology* 27 115201

- [23] Zubko P, Wojdeł J C, Hadjimichael M, Fernandez-Pena S, Sené A, Luk'yanchuk I, Triscone J-M and Íñiguez J 2016 Negative capacitance in multidomain ferroelectric superlattices *Nature* 6 524–8

- [24] Nakamura T, Nakao Y, Kamisawa A and Takasu H 1994 Preparation of Pb(Zr,Ti)O<sub>3</sub> thin films on electrodes including IrO<sub>2</sub> Appl. Phys. Lett. 65 1522–4

- [25] Kidoh H, Ogawa T, Morimoto A and Shimizu T 1991 Ferroelectric properties of lead–zirconate–titanate films prepared by laser ablation Appl. Phys. Lett. 58 2910–2

- [26] Kim D-J, Maria J-P, Kingon A I and Streiffer S K 2003 Evaluation of intrinsic and extrinsic contributions to the piezoelectric properties of Pb(Zr<sub>1-x</sub>T<sub>x</sub>)O<sub>3</sub> thin films as a function of composition *J. Appl. Phys.* 93 5568–75

- [27] Shur V Y, Baturin I S, Shishkin E I and Belousova M V 2003 New approach to analysis of the switching current data in ferroelectric thin films *Ferroelectrics* 291 27–35

- [28] Zhou D, Xu J, Li Q, Guan Y, Cao F, Dong X, Müller J, Schenk T and Schröder U 2013 Wake-up effects in Si-doped hafnium oxide ferroelectric thin films Appl. Phys. Lett. 103 192904

- [29] Dasgupta S, Rajashekhar A, Majumdar K, Agrawal N, Razavieh A, Trolier-Mckinstry S and Datta S 2015 Sub-kT/q switching in strong inversion in PbZr<sub>0.52</sub>Ti<sub>0.48</sub>O<sub>3</sub> gated negative capacitance FETs *IEEE J. Exploratory Solid-State Comput. Devices Circuits* 1 43–8

- [30] Park J H, Jang G S, Kim H Y, Seok K H, Chae H J, Lee S K and Joo S K 2016 Sub-kT/q subthreshold-slope using negative capacitance in low-temperature polycrystalline-silicon thinfilm transistor Sci. Rep. 6 24734

- [31] Boucart K and Ionescu A M 2006 Double gate tunnel FET with ultrathin silicon body and high-k gate dielectric ESSDERC 2006. Proc. 36th European Solid-State Device Research Conf. 2006 (Piscataway, NJ: IEEE) pp 383–6

- [32] Villalon A, Le Royer C, Casse M, Cooper D, Hartmann J-M, Allain F, Tabone C, Andrieu F and Cristoloveanu S 2013 Experimental investigation of the tunneling injection boosters for enhanced I<sub>ON</sub> ETSOI tunnel FET IEEE Trans. Electron Devices 60 4079–84

- [33] Jiang C, Liang R and Xu J 2017 Investigation of negative capacitance gate-all-around tunnel fets combining numerical simulation and analytical modeling *IEEE Trans*. *Nanotechnol.* 16 58–67

- [34] Mohata D K, Bijesh R, Saripalli V, Mayer T and Datta S 2011 Self-aligned gate nanopillar In0.53Ga 0.47As vertical tunnel transistor 2011 69th Annual Device Research Conf. (DRC) (Piscataway, NJ: IEEE) pp 203–4

- [35] Gandhi R, Chen Z, Singh N, Banerjee K and Lee S 2011 CMOS-compatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs with <50 mV/decade subthreshold swing *IEEE Electron Device Lett.* 32 1504–6

- [36] Narimani K, Glass S, Rieger T, Bernardy P, von den Driesch N, Mantl S and Zhao Q T 2017 Silicon tunnel FET with average subthreshold slope of 55 mv/dec at low drain currents 2017 Joint Int. EUROSOI Workshop and Int. Conf. on Ultimate Integration on Silicon (EUROSOI-ULIS) (Piscataway, NJ: IEEE) pp 75–8

- [37] Asra R, Shrivastava M, VRM Murali K, Pandey R K, Gossner H and Rao V R 2011 A tunnel FET for  $V_{dd}$  scaling below 0.6 V with a CMOS-comparable performance *IEEE Trans. Electron Devices* **58** 1855–63

- [38] Jain A and Alam M A 2014 Stability constraints define the minimum subthreshold swing of a negative capacitance field-effect transistor *IEEE Trans. Electron Devices* 61 2235–42

- [39] Saeidi A, Biswas A and Ionescu A M 2016 Modeling and simulation of low power ferroelectric non-volatile memory tunnel field effect transistors using silicon-doped hafnium oxide as gate dielectric *Solid-State Electron*. 124 16–23