# Effect of Physical Stress on the Degradation of Thin SiO<sub>2</sub> Films Under Electrical Stress

Tien-Chun Yang and Krishna C. Saraswat, Fellow, IEEE

Abstract—In this work, we demonstrate that for ultrathin MOS gate oxides, the reliability is closely related to the SiO2/Si interfacial physical stress for constant current gate injection  $(V_q^{-})$  in the Fowler-Nordheim tunneling regime. A physical stress-enhanced bond-breaking model is proposed to explain this. The oxide breakdown mechanism is very closely related to the Si-Si bond formation from the breakage of Si-O-Si bond, and that is influenced by the physical stress in the film. The interfacial stress is generated due to the volume expansion from Si to SiO2 during the thermal oxidation, and it is a strong function of growth conditions, such as temperature, growth rate, and growth ambient. Higher temperatures, lower oxidation rates, and higher steam concentrations allow faster stress relaxation through viscous flow. Reduced disorder at the interface results in better reliability. Fourier transform infrared spectroscopy (FTIR) technique has been used to characterize stress in thin oxide films grown by both furnace and rapid thermal process (RTP). In conjunction with the Gibbs free energy theory, this model successfully predicts the trends of time-to-breakdown  $(t_{bd})$  as a function of oxide thickness and growth conditions. The trends of predicted  $t_{bd}$  values agree well with the experiment data from the electrical measurement.

Index Terms—Bond breaking, FTIR, oxide breakdown, oxide reliability, physical stress,  $Q_{bd}$ , steam concentration,  $t_{bd}$ , ultrathin.

#### I. INTRODUCTION

T HAS been generally believed in the past that the intrinsic oxide properties, such as, breakdown strength, charge to breakdown ( $Q_{bd}$ ), etc. improve as the thickness is reduced [1], [2]. The reason was attributed to the fact that for thinner oxides rather than Fowler–Nordheim tunneling, direct tunneling dominates involving less energetic electrons or holes causing lesser damage [1], [3]. Recently, it has been observed that the  $t_{bd}$  is lower under gate injection compared to substrate injection [4], [5], and this reduction is stronger for thinner oxides [6]–[10]. Many models have been proposed to explain the degradation and breakdown of thin oxides, for example, E model [11], 1/E model [12], anode hole injection [3], H-release [13], physical bond breaking [1], high field related oxide wearout [14], trap generation, critical electron trap density [15], and interface roughness [4]. These models try to relate electrical

Manuscript received October 6, 1998; revised July 27, 1999. This work was supported by the Defense Advanced Research Projects Agency. In addition, this work made use of National Nanofabrication Users Network facilities at Stanford University, Stanford, CA, supported by the National Science Foundation. The review of this paper was arranged by Editor C. Y. Yang.

T. C. Yang was with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA. He is currently with Advanced Micro Devices, Sunnyvale, CA 94088.

K. C. Saraswat is with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: saraswat@cis.stanford.edu). Publisher Item Identifier S 0018-9383(00)02714-3.

stress to dielectric degradation through some phenomenon in it. Most of these studies involve extensive stress conditions and measurements, however, limited attention has been paid to growth conditions which could alter the dielectric properties of the oxides. Therefore, each of these models can explain its own electrical measurement data, but cannot explain the dependence of dielectric degradation to the growth conditions of oxides. In addition, they cannot explain the following two phenomena for gate injection of electrons: 1) the  $t_{bd}$  decreases as the oxide thickness is reduced in the Fowler–Nordheim regime; 2)  $t_{bd}$  for gate injection is always lower than that of substrate injection.

Han *et al.* have proposed that the physical stress in oxide could be a factor to cause polarity difference of  $t_{bd}$  [7]. Miura *et al.* demonstrated that the oxide breakdown failure rate decreases monotonically as internal stress in the MOS gate electrodes is reduced [16]. Eriguchi *et al.*have determined the strained layer near SiO<sub>2</sub>/Si interface to be approximately 1 nm [10] and verified that the increased compressive strain decreases  $t_{bd}$ .

In this work, we propose that enhanced bond breaking due to physical stress resulting from thermal oxidation of Si plays an important role in the reliability of gate oxides. By investigating the effect of growth conditions on the physical stress and reliability of thin MOS gate oxides, we can explain the thickness and stress polarity dependence. The degradation is always more for those growth conditions, which result in higher physical stress in SiO<sub>2</sub>. Higher temperatures and slower oxidation rates allow stress relaxation through viscous flow. Steam oxidation results in lower stress as compared to dry O<sub>2</sub> oxidation. Reduced stress at the interface always results in better reliability.

#### II. GENERAL BACKGROUND

Most crystalline polymorphs of SiO<sub>2</sub> consist of ordered networks of corner-sharing SiO<sub>4</sub> tetrahedra, with the topology of the network differing from structure to structure. In the amorphous SiO<sub>2</sub>, the basic structural unit is the SiO<sub>4</sub> tetrahedron with each Si atom surrounded by four O atoms [17]. The angle of O–Si–O bonds is fixed at 109.5 °. However, the Si–O–Si angle is rather flexible; and being twofold coordinated [18]. Each O atom bridges two neighboring SiO<sub>4</sub> tetrahedrons. The bond is relatively easy to bend, stretch, or rotate. And the Si-O-Si bonds are capable of accommodating large lattice distortion [18]. For this reason, the Si-O-Si bond is of special interest, and it has been used as a basic bonding unit of SiO2 to characterize its properties [19]. The Si-O-Si bond angle changes with oxide density [20]. At the normal density of 2.2 g/cm<sup>3</sup>, the bond angle distribution has a single peak at 144° and the full width at half maximum of this peak is 26°. With an increase in the density, the

peak in the bond angle distribution broadens and shifts continuously to lower angles: at 2.64 and 2.94 g/cm<sup>3</sup>, this peak shifts to 139 and 137°, respectively [20].

The bond strength of the Si–O–Si bonds mentioned in the previous paragraph is severely weakened when the bond angle deviates from the mean value of 144°. Generally, bond angles greater than 180° or less than 120° are rarely observed and an oxygen vacancy also known as E' centers, tends to occur [21]. It is this molecular defect in intrinsic SiO<sub>2</sub> films that is thought to dominate time-dependent dielectric breakdown [21].

Several models have been developed by different researchers to explain the oxide degradation and breakdown [1], [3], [4], [11]–[15]. The common essence is summarized here. If the electric field is sufficiently high, Fowler-Nordheim tunneling of electrons occurs and electrons are injected into the conduction band of the oxide. They gain energy from the electric field and lose it through lattice scattering. Some of these electrons lose all of the excess energy and get trapped in the oxide if traps are present in it. Many electrons continue to conduct in the conduction band. At the anode, they fall into the conduction band of Si and in the process lose the excess energy. The energy gained by the electrons when they reach the anode can be as high as 3–9 eV [13]. The loss of the excess energy can cause damage through several ways. The high energy imparted by the electron can break bonds between Si and O at the interface. The dangling bonds give rise to traps in the oxide bandgap [1]. The energy released by the electrons can release hydrogen at the interface, which may have been incorporated during the processing. H release leaves a dangling bond giving rise to traps [22]. If the energy released by the electrons is sufficiently high, it can cause impact ionization at the interface generating more hot electrons and hot holes. Hot holes can then be injected in the valance band of SiO<sub>2</sub> via Fowler–Nordheim tunneling. Similar to the case of electrons the holes also cause further damage through trap creation and trapping [3]. Another model states that the high electric field itself may polarize the bonds and ultimately break them under a combination of electrical stress and thermal energy imparted to them [14]. All of these models agree that the damage is caused by bond breaking. If large number of bonds is broken, the damage is excessive and a damage cluster is created in a local region. If several damage clusters are formed and a continuous path is created from anode to cathode oxide breakdown occurs [1], [15].

## III. EXPERIMENT

LOCOS isolated MOS capacitors made on lightly doped nand p-type (100)-oriented Si substrates with gate oxides grown either in a furnace or an RTP system were used in this study. N+ poly-Si gates of 250 nm thickness *in situ* doped with phosphorus were deposited by LPCVD. Since the incorporation of hydrogen in oxides plays an important role in oxide breakdown [13], some of the devices went through low temperature forming gas anneal at 400 °C and others didn't. However, there were no significant  $t_{bd}$  differences between them. This indicates that there was enough hydrogen incorporated into the oxides during the fabrication passivating the SiO<sub>2</sub>/Si interface. Furnace oxides were grown in dry  $O_2$ , whereas RTP oxides were grown in dry as well as wet  $O_2$ . For the furnace processing, the oxides of 4–10 nm thickness were grown at 800 °C or 1000 °C in 30% or 70% dry oxygen, diluted with Ar, at a total pressure of 1atm. The difference between 30% and 70% grown oxides is the oxidation time, allowing the determination of the effect of oxidation times on oxide reliability.

For the RTP, the oxides of 4–10 nm thickness were grown at  $800-1000\,^{\circ}\text{C}$  in dry, 2% wet or 50% wet oxygen, at a total pressure of 1 atm. In the wet oxidations, both steam and  $O_2$  oxidize at the same time. The percentage of wet oxygen is calculated as the ratio of the partial pressure of steam to the total pressure of steam and  $O_2$  during the oxidation process. The higher the percentage of steam is, the more its contribution to the oxidation is. Such controlled growth of thin  $SiO_2$  films in wet  $O_2$  at higher temperatures would be difficult to perform in a furnace.

The oxidation times and the resulting oxide thickness are shown for different ambients and temperatures for both furnace and RTP oxides in Tables I and II, respectively.

The charge to breakdown,  $Q_{bd}$ , was measured under constant current stress on  $100~\mu\mathrm{m} \times 100~\mu\mathrm{m}$  capacitors with both positive and negative gate polarities. Time-to-breakdown,  $t_{bd}$ , for various oxides was determined from cumulative plots. The  $t_{bd}$  data were sampled uniformly all over the wafers. Note that the  $t_{bd}$  measurements were done under illumination on  $\mathrm{n}^+$  poly-Si gate MOSCAP's with  $\mathrm{n}^-$  substrates to keep the devices from deep depletion.

To characterize the interfacial stress, FTIR technique was used. From the absorption spectrum, we can get information on interfacial stress from the positions of absorption frequency peaks of Si–O–Si bonds in SiO<sub>2</sub>. Higher stress is associated with a denser oxide film, smaller Si–O–Si bond angle and lower peak [17], [23], [24]. For FTIR measurements, a duplicate set of wafers with blanket films of thin oxide was grown concurrently with the gate oxides of LOCOS isolated MOS capacitors.

# IV. TIME DEPENDENT DIELECTRIC BREAKDOWN (TDDB) MEASUREMENT RESULTS

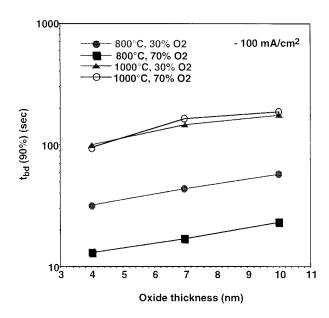

Fig. 1 shows a  $t_{bd}$  of furnace grown oxides as a function of their thickness at a gate injection  $(V_g^-)$  of  $100~\rm mA/cm^2$ . The  $t_{bd}$  values were chosen from 90% value of cumulative plots to obtain the intrinsic properties of oxides. TDDB measurements on  $10~\mu \rm m \times 10~\mu m$  size devices were also done. The  $90\%~t_{bd}$  values were very close to those of  $100~\mu \rm m \times 100~\mu m$  devices although the slopes of the cumulative plots were higher. All the data reported here were collected on devices of the same area of  $100~\mu \rm m \times 100~\mu m$ . Degraeve et~al. have shown that  $Q_{bd}$  increases as the area decreases, however, the fact that  $Q_{bd}$  decreases as the oxide thickness is reduced is still observed for smaller as well as larger devices [15]. From Fig. 1, the following trends can be observed.

- 1)  $t_{bd}$  reduces as the SiO<sub>2</sub> thickness reduces.

- 2)  $t_{bd}$  is higher for oxides grown at the higher oxidation temperature (1000 °C).

- 3) At the low temperature (800 °C),  $t_{bd}$  reduces as the SiO<sub>2</sub> growth rate is increased (or oxidation time is decreased),

| Dry O2 concentration | 800°C            | 1000°C           |

|----------------------|------------------|------------------|

|                      | time - thickness | time - thickness |

| 30%                  | 50 min - 39Å     | 1.1 min - 41Å    |

| 30%                  | 155 min - 61Å    | 5 min - 66Å      |

| 30%                  | 350 min - 92Å    | 11.5 min - 94Å   |

| 70%                  | 24 min - 37Å     | 0.5 min - 41Å    |

| 70%                  | 97 min - 68Å     | 2.7 min - 70Å    |

| 70%                  | 180 min - 95Å    | 5.5 min - 93Å    |

TABLE I

OXIDATION CONDITIONS OF FURNACE

OXIDES

TABLE II

OXIDATION CONDITONS OF RTP OXIDES

| oxidation conditions | time -thickness |

|----------------------|-----------------|

| 800°C, dry           | 630sec - 43Å    |

| 900°C, dry           | 85 sec - 43Å    |

| 1000°C, dry          | 17 sec - 46Å    |

| 800°C, 2% wet        | 580 sec - 44Å   |

| 900°C, 2% wet        | 68 sec - 42Å    |

| 950°C, 2% wet        | 28 sec - 44Å    |

| 1000°C, 2% wet       | 10 sec - 43Å    |

| 1000°C, 2% wet       | 114 sec 106Å    |

| 800°C, 50% wet       | 264 sec - 49Å   |

| 1000°C, 50% wet      | 5 sec - 42Å     |

| ·                    |                 |

as in the case of 70%  $O_2$ . However, at 1000 °C, the  $t_{bd}$  values are about the same for different growth rates.

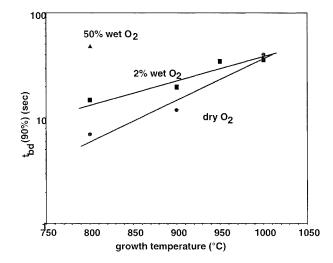

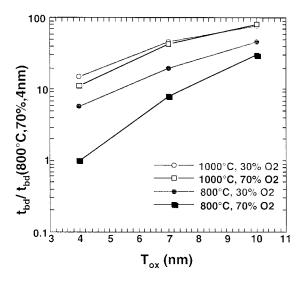

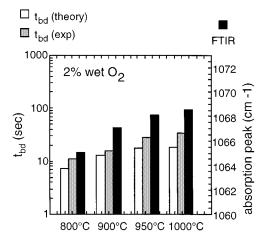

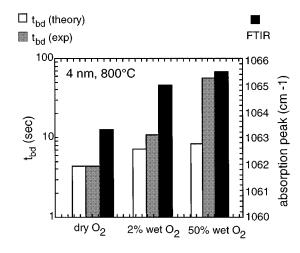

Fig. 2 shows  $t_{bd}$  of 4 nm dry, 2% wet, and 50% wet oxides grown in an RTP system as a function of oxidation temperature. Following trends can be observed.

- 1) For both dry and wet oxides,  $t_{bd}$  is higher for oxides grown at higher temperatures.

- 2) At low temperatures (800 °C),  $t_{bd}$  increases as the steam concentration is increased, as in the case of 2% and 50% wet oxides. As the temperature is increased the difference becomes less. At 1000 °C, there is no difference. At 50% steam concentration, use of higher temperatures was not feasible as the time of growth was too short to be practical.

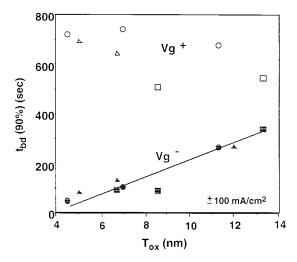

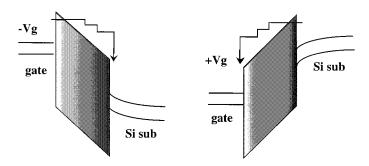

Fig. 3 shows  $t_{bd}$  as a function of oxide thickness for both gate injection  $(Vg^-)$  and substrate injection  $(Vg^+)$  for devices from different runs with slight process variations. All the oxides were thermally grown at 800 °C in a furnace. It can be seen that, for gate injection, the  $t_{bd}$  increases with the gate oxide thickness. On the other hand, for substrate injections, there are no significant trends.  $t_{bd}$  shows only a slight increase for thinner oxides. In general,  $t_{bd}$  for substrate injection is higher than that for gate injection.

### V. STRESS MEASUREMENT TECHNIQUE AND RESULTS

All the trends of furnace and RTP oxides in the previous section can be explained by examining the role of physical stress at the SiO<sub>2</sub>/Si interface. During the thermal growth of SiO<sub>2</sub>, there is a 128% volume expansion from Si to SiO<sub>2</sub> [25], and therefore

Fig. 1.  $t_{bd}$  (90% values from cumulative plots) for various oxides for constant current gate injection  $(Vg^-)$  at a current density of 100 mA/cm<sup>2</sup>.

Fig. 2.  $t_{bd}$  (90% values from cumulative plots) of 4 nm oxides for gate injection at a current density of 100 mA/cm<sup>2</sup>. The RTP oxides were thermally grown in dry, 2% wet and 50% wet  $O_2$  at different temperatures.

Fig. 3.  $t_{bd}$  of 800 °C oxides for constant current gate injection (Vg-) and substrate injection (Vg+) at a current density of 100 mA/cm<sup>2</sup>.

the SiO<sub>2</sub> film is compressed. The newly formed SiO<sub>2</sub> pushes the previously grown SiO<sub>2</sub> upwards. This growth results in a compressive stress in the oxide close to the Si/SiO<sub>2</sub> interface. The interfacial stress decreases as we move farther from the interface. It has been shown that the stress in the SiO<sub>2</sub> thin film at the Si/SiO<sub>2</sub> interface,  $\sigma_i$  (SiO<sub>2</sub>), is very large,  $\cong$ 500 MPa, and there can be very large stress gradients,  $\cong$  2 × 10<sup>8</sup> MPa/cm, in the SiO<sub>2</sub> films in the immediate vicinity of the Si/SiO<sub>2</sub> interface [26]. It has also been demonstrated through XPS measurements that there is a measurable gradient in bond strain in SiO<sub>2</sub> at the SiO<sub>2</sub>/Si interface [27]. The strained layer was determined to be about 1 nm for dry, RTP and pyrogenic oxides by XPS [10].

Aside from the intrinsic (growth) stress,  $\sigma_i$ , originating from the molar volume change when converting Si to SiO<sub>2</sub>, there is also a thermal expansion stress,  $\sigma_{th}$ , arising from the thermal contraction mismatch which results upon cool-down from oxidation to room temperature. Usually the total residual stress,  $\sigma_i + \sigma_{th}$ , exists in the film when the electrical and optical measurements are done. However, the difference in the thermal stress is very small for 800 °C and 1000 °C grown oxides, i.e.,  $\cong$ 200 MPa and 230 MPa for 800 °C and 1000 °C oxides, respectively [28]. For the intrinsic stress, the difference can be quite large; for 800 °C grown oxides, the intrinsic stress is about 300 MPa [28], however at 1000 °C oxides are grown in an almost stress-free condition [29].

To prove that oxide film stress varies with processing conditions, FTIR measurements were done on oxides grown under different conditions. From the FTIR absorption spectrum, one can determine the angle of Si–O–Si bonds and therefore the stress in the oxide film [17], [23]. This absorption is associated with the different vibrational energy state transition of Si–O–Si molecular structure [30]. The absorption peak frequency tells us the angle of Si–O–Si bonds and therefore is an indicative of the associated stress. The absorption peak varies when the stress in the oxides is different [23], [24]. When the compressive stress becomes larger, the Si–O–Si bond angle becomes smaller, and therefore the absorption peak frequency is lower.

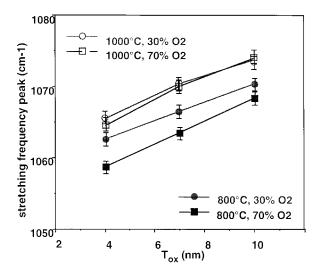

The measured FTIR results of different furnace oxides grown in dry  $O_2$  are summarized in Fig. 4. The error of the measured absorption peaks was within  $\pm 1~\rm cm^{-1}$ . An increasing trend of peak stretching frequency as a function of oxide thickness is observed. Lower temperature (800 °C) and faster growth rate give lower peak stretching frequency. The overall trends are similar to those observed earlier in Fig. 1 for  $t_{bd}$ . Therefore, there is a strong correlation between the absorption peak and  $t_{bd}$ .

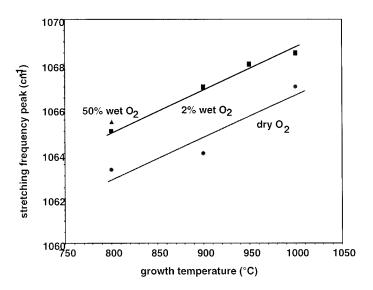

Fig. 5 shows the stretching peak frequencies of 4 nm thick RTP oxides grown in dry, 2% wet, and 50% wet oxygen at different temperatures. Although not the same, the overall trends agree well with the  $t_{bd}$  trends shown in Fig. 2. The stretching peak frequencies of oxides grown at 800 °C increase as the steam concentration is increased. The frequency increases as the growth temperature increases. However, at 1000 °C, the stretching peak frequency of 2% wet oxide is higher than that of dry oxide but their  $t_{bd}$  are about the same. This tells us that the interface stress is a good indicator, but not the only factor in determining oxide reliability.

Higher absorption peak frequency implies lower stress in the oxides. Therefore it implies that the oxide with lower stress has

Fig. 4. Absorption peak frequencies as a function of oxide thickness by FTIR measurement. The oxides were grown at different temperatures and dilute concentrations in furnace.

Fig. 5. Stretching peak frequencies of 4 nm dry, 2% wet, and 50% wet oxides grown at different temperatures by RTP.

higher  $t_{bd}$ . Higher growth temperature and higher steam concentration seem to reduce the stress. Furthermore, the decrease in frequency with the decrease in oxide thickness indicates the existence of stress gradient at the Si–SiO<sub>2</sub> interface as FTIR averages the measurement across the thickness.

#### VI. PHYSICAL STRESS-ENHANCED BOND BREAKING MODEL

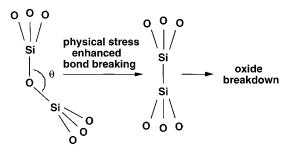

We propose a physical stress-enhanced bond-breaking model for thin SiO<sub>2</sub> degradation in the Fowler–Nordheim regime. The oxide breakdown is a two-step process as shown in Fig. 6. McPherson *et al.*have shown the electric field effect on the decomposition of the Si–Si bonds, the second step of the breakdown process [31]. In this work we have focused on the first step. In the discussion below we focus only on the Si–O–Si bonds, however, our methodology can also be applied to other bonds like Si–H. We demonstrate that the first step is strongly dependent on the physical stress in the thin oxide

films. Enhanced stress strains the bonds making it easier to break. As we mentioned in earlier sections, if the stress in oxides is different, the bond angles of Si–O–Si will be different, which is 144  $^{\circ}$  at a stress free state. As the stress increases, the bond angle decreases. The bonding energy increases and therefore the bond will be weaker and easier to break by the electrons tunneling due to the electrical stress. Hence, the  $t_{bd}$  will be lower.

The free energy approach to time-dependent dielectric breakdown mechanism is used in our model [32]. For any chemical reaction to take place, the reactants (stable state) must overcome a potential difference to form the products (breakdown state). The driving force for this is the free energy difference between the stable state and the bond breakdown state. However, the reaction rate k at which the breakdown progresses depends on the free energy difference  $\Delta G^*$  which separates the stable state from the activated state that leads to rapid breakdown.

Assuming the time-dependent dielectric breakdown is an activated process obeying standard chemical reaction rate theory [33], [34], the reaction rate constant should hold true by the following equation:

$$k \propto \exp\left(\frac{\Delta G^*}{KT}\right)$$

. (1)

The total time for this process to take place,  $t_{bd}$  in the case, should be inversely proportional to the reaction rate constant as described in the following equation.

$$t_{bd} \propto \frac{1}{k} \propto \exp\left(\frac{\Delta G^*}{KT}\right).$$

(2)

The Gibbs free energy difference can be written as

$$\Delta G^* = \Delta H^* - T\Delta S^* \tag{3}$$

where  $\Delta H^*$  is the change in the enthalpy and  $\Delta S^*$  is the change in the entropy. Usually the entropy S is very small for solids compared to the enthalpy change, so (3) can be simplified to

$$\Delta G^* = \Delta H^*. \tag{4}$$

One can see from (2) and (4) that the  $t_{bd}$  value depends on the enthalpy change. Since enthalpy is the formation heat, therefore,  $t_{bd}$  is dependent on the bonding energy of the Si–O–Si bonds, which is a function of the bond angles  $\theta$ .

To determine the bonding energy as a function of  $\theta$ , the molecular mechanics approach described by Allinger is used [35]. We begin with a potential surface describing a molecule, and approximate this surface near the energy minimum using a Taylor's series expansion. The Taylor's series, if expressed in terms of internal coordinates, leads to an infinite power series, which describes bond bending. Then, we can have the following familiar expression:

$$E(\theta) = E(\theta_0) + \frac{K_{\theta}}{2} (\theta - \theta_0)^2 + \frac{K_{\theta}'}{3!} (\theta - \theta_0)^3 + \frac{K_{\theta}''}{4!} (\theta - \theta_0)^4 \cdots$$

(5)

Fig. 6. Proposed physical stress-enhanced bond breaking mechanism. For the oxide breakdown to occur, the Si–O–Si bonds in SiO<sub>2</sub> break and are replaced by the Si–Si bonds, and this process is strongly dependent on the physical stress in the thin oxide films.

where  $\theta_0 = 144^{\circ}$  and  $K_{\theta}$  values are the force constants for bending. The linear term is zero because the expansion is at the energy minima.

If the amount of bond bending is not large, we can neglect the higher order terms and (5) can be simplified to

$$E(\theta) = E(\theta_0) + \frac{K_\theta}{2} (\theta - \theta_0)^2. \tag{6}$$

The energy form of (6) is like a harmonic oscillator. Thus, the force constant  $K_{\theta}$  can be determined to be 20.5 eV [37] by the measured oscillating frequencies (bending, stretching, and rocking) of thick SiO<sub>2</sub> as shown by Harrison [36]. Therefore, from (2), (4), and (6), for two oxides under the same electric field, the following equation is obtained:

$$\frac{t_{bd2}}{t_{bd1}} = \exp\left(\frac{\Delta G_2^* - \Delta G_1^*}{KT}\right)$$

$$= \exp\left(\frac{\frac{K_\theta}{2} (\theta_1 - \theta_0)^2 - \frac{K_\theta}{2} (\theta_2 - \theta_0)^2}{KT}\right) \quad (7)$$

where  $\theta_0$  is 144°,  $\theta_1$  and  $\theta_2$  can be calculated from the measured FTIR absorption peaks through the following equation [19]:

$$\nu_p = \nu_0 \sin \frac{\theta}{2} \tag{8}$$

where  $\nu_p$  is the peak of the absorption frequency and  $\nu_o$  is 1134 cm<sup>-1</sup>.

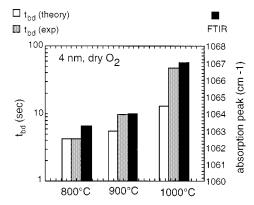

Based on (7) and (8) and the FTIR absorption peak data (Figs. 4 and 5) of various oxides, the relative  $t_{bd}$  values can be predicted. For furnace grown oxides, the predicted  $t_{bd}$  values are plotted in Fig. 7. Note that all the  $t_{bd}$  values have been normalized to the  $t_{bd}$  of 800 °C, 70% 4 nm oxide. It can be observed that the  $t_{bd}$  trends agree well with the experiment data shown in Fig. 1. Similar results are obtained for the RTP oxides. Figs. 8–10 summarize theoretical  $t_{bd}$ , measured  $t_{bd}$ and the FTIR absorption peaks for oxides of 4 nm thickness grown in dry and wet  $O_2$  at 800, 900, 950, and 1000 °C. The theoretical  $t_{bd}$  value of the 800 °C, 4 nm dry oxide (the one with the lowest  $t_{bd}$ ) is set to 4.25 s (its experimental value). All the other theoretical  $t_{bd}$  values are normalized to this value using (7). It can be observed that the trends of the theoretical  $t_{bd}$  agree very well with that of the experimental  $t_{bd}$  and the FTIR measurements. The slight  $t_{bd}$  difference between the experimental and theoretical values can come from the

following reasons. First, we have assumed in our calculations that the stress in the film is uniform during the bond breaking process that causes the formation of a conducting path from the substrate to the gate electrode. In reality, the stress decreases as one moves away from the substrate interface. Second, only the breakage of the Si–O bonds is considered, not other bonds, for example the Si–H bond, which has been observed to be related to the oxide breakdown [13]. Third, other oxide breakdown mechanisms are not taken into account, e.g., anode hole injection [3] and high field oxide wearout [14].

#### VII. DISCUSSIONS

Although constant current stress (CCS) was used throughout the TDDB measurement in this work, the results should be very close to those of constant voltage stress (CVS);  $Q_{bd}$  values have been shown to depend on the gate work function [38], the stress polarity in dual-gate CMOSFET's [39], and the testing methodology [40]. In general, they depend on the electric field in oxide  $E_{ox}$  and the stressing current density  $J_{ox}$ . At a fixed  $J_{ox}$ , higher  $E_{ox}$  gives lower  $Q_{bd}$ , and same  $E_{ox}$  gives same  $Q_{bd}$  [41]. For a given capacitor, the relation of  $J_{ox}$  and  $E_{ox}$  is one to one. In our case,  $J_{ox}$  is fixed and the tunneling barrier height is the same (3.1 eV for n+ poly-Si gates). Therefore,  $E_{ox}$  is the same. Constant current stress in our case is therefore very close to constant voltage stress. The only differences is that under constant current stress, the total voltage drop across the MOS capacitors changes slightly during the measurement due to electron and hole trapping in the oxides, while for the constant voltage stress, the injecting current changes. To the first order, the changes are relatively small compared to the average voltage for constant current stress or the average current for constant voltage stress and therefore they are negligible. Table III shows the initial voltage  $(V_{init})$  drops across the MOS capacitors under constant current stress at a current density of  $-100 \text{ mA/cm}^2$  for various furnace oxides with information given in Table I. These values are very close to their average voltages before the oxides break down in our measurements (within 5%). In addition, one can observe that the corresponding voltage drops acrossthe capacitors of about the same oxide thickness grown by different conditions are very close. Therefore, results of constant current stress in this work should be very close to constant voltage stress.

Many researchers have shown that there is a strong correlation between the interfacial stress and  $t_{bd}$ . Han  $et\ al$ . have proposed that the structural transition layer at the  $\mathrm{SiO}_2/\mathrm{Si}$  interface is related to  $Q_{bd}$  [7]. Eriguchi  $et\ al$ . have determined that the increase of the built-in compressive strain would decrease  $t_{bd}$  [10]. Bhat  $et\ al$ . have shown the correlation between  $Q_{bd}$  and stress in deposited oxides [42], [43]. Lee  $et\ al$ . have shown a correlation between stress and oxide soft-breakdown [44]. In this section we discuss how stress affects  $t_{bd}$  in more detail.

As we have mentioned earlier, several oxide damage mechanisms have been proposed, and basically, they all agree well with this model as all of them rely on trap creation through some kind of physical damage. The stressed region is more vulnerable to high energy electrons tunneling through the oxide and causing damage at the anode, consistent with anode being the

primary damage site [1], [5], [13]. Since the strained layer occupies a larger fraction in a thinner oxide than thicker one, its  $t_{bd}$  is lower. This is consistent with the observations that there is a measurable gradient in bond strain at the interface [27] and most of the stress occurs within a 1-nm-thick strained-layer near the SiO<sub>2</sub>/Si interface [10]. This can explain the increase in  $t_{bd}$  as a function of oxide thickness for gate injection.

During oxide growth, the viscous flow of SiO<sub>2</sub> can occur. If there was no viscous relaxation, we would expect a constant value of stress across the thickness of the films. That is not the case. There is a nonhomogeneous thermal history aspect to all thermally grown SiO<sub>2</sub> films; in a thick oxide film, the topmost increment of oxide was formed first and was being annealed while the underlying oxide was being formed. The increment of oxide nearest the interface has spent very little time at the growth temperature and is therefore expected to show the least amount of relaxation [24]. It is apparent that the stress generated at the growth interface relaxes as we move away from the interface. Therefore, the viscous flow can partially relieve the physical stress in the oxide film. When the temperature is below 950 °C, this process takes place at a very slow rate. However, it is noticeably faster when the temperature is higher than 950 °C [45]. This is because the time required for viscous flow is reduced significantly if the temperature is above 950 °C. Therefore the oxides grown at higher temperatures have lower stress with an accompanying decrease in the oxide density [17], [46]. The stress relaxation time for oxide density can be expressed as in the following equation [47], [48]:

$$\tau(T) = \tau_o \exp(E_a/kT) \tag{9}$$

where  $\tau_o=2\times 10^{-20}c$  s and  $E_a=5.1$  eV. The relaxation times at different temperatures based on this equation are summarized in Table IV.

At 1000 °C, the relaxation time of 3 s is so small compared to the oxidation times (see Table I) that no matter whether the oxides were grown in 30% or 70%  $O_2$ , the stress was almost all relieved through  $SiO_2$  viscous flow. Hence, no significant  $t_{bd}$  differences can be observed for oxides grown at 1000 °C. At 800 °C the relaxation time of 4.76 h is much larger than the oxidation time. Therefore, there is little viscous flow resulting in higher stress. Since the interfacial bonds of 1000 °C oxides have less stress than 800 °C, they are more difficult to break. Therefore, 1000 °C grown oxides have higher  $t_{bd}$  as shown in Fig. 1. Similar trend of  $t_{bd}$  versus temperature can be seen in Fig. 2 for RTP oxides. Note that in Fig. 2, the  $t_{bd}$  of the 2% wet 950 °C oxides is very close to that of the 1000 °C oxides, because for both temperatures the relaxation times are smaller than the oxidation times.

At 800 °C, however, since the viscous flow of  $SiO_2$  is not significant, different growth times will affect  $t_{bd}$  results if they are smaller than or comparable to the relaxation time, which is the case for our furnace grown oxides as shown in Table I. As one can see in Fig. 1, longer time growth (30%  $O_2$ ) gives higher  $t_{bd}$ . This is because if the oxidation time is longer, the relaxation of Si–O–Si bonds at the  $Si/SiO_2$  interface through viscous flow will be more. Therefore, it will result in lower stress and higher  $t_{bd}$ .

Fig. 7. Theoretical prediction of relative  $t_{bd}$  values of furnace dry oxides normalized to 800 °C, 70% O<sub>2</sub>, 4 nm oxide. The measured FTIR absorption peaks of various oxides were used in this calculation.

Fig. 8. Theoretical  $t_{bd}$ , experimental  $t_{bd}$  (90% value) and the FTIR absorption peaks of 4 nm oxides. The RTP oxides were thermally grown in dry  $O_2$  at different temperatures. All the calculated  $t_{bd}$  values have been normalized to the  $t_{bd}$  of 800  $^{\circ}$ C, 4 nm dry oxide.

Fig. 9. Theoretical  $t_{bd}$ , experimental  $t_{bd}$  (90% value) and the FTIR absorption peaks of 4 nm oxides. The RTP oxides were thermally grown in 2% wet  $O_2$  at different temperatures. All the calculated  $t_{bd}$  values have been normalized to the  $t_{bd}$  of 800 °C, 4 nm dry oxide.

Another interesting result as shown in Fig. 2 is that at 800 °C, more steam during the oxidation gives higher  $t_{bd}$ . Eriguchi *et al.*

Fig. 10. Theoretical  $t_{bd}$ , experimental  $t_{bd}$  (90% value) and the FTIR absorption peaks of 4 nm oxides. The RTP oxides were thermally grown at 800 °C at different steam concentrations. All the calculated  $t_{bd}$  values have been normalized to the  $t_{bd}$  of 800 °C, 4 nm dry oxide.

TABLE III INITIAL VOLTAGE DROPS ACROSS THE FURNACE GROWN OXIDES UNDER CONSTANT CURRENT STRESS AT A CURRENT DENSITY OF -100~mA/cm2

| Dry O2 concentration | 800°C   | 1000°C  |

|----------------------|---------|---------|

|                      | Vinit   | Vinit   |

| 30%                  | -4.9 V  | -4.9 V  |

| 30%                  | -7 V    | -7 V    |

| 30%                  | -12.6 V | -11.5 V |

| 70%                  | -4.8 V  | -4.9 V  |

| 70%                  | -7. 2 V | - 7.4 V |

| 70%                  | -12.4 V | -11.8 V |

TABLE IV RELAXATION TIME VERSUS TEMPERATURE

| T      | τ(T)       |

|--------|------------|

| 800°C  | 4.76 hours |

| 850°C  | 25 min     |

| 900°C  | 160 sec    |

| 950°C  | 20 sec     |

| 1000°C | 3 sec      |

have found similar trend [10]. By investigating the oxide etch rates in dilute HF, they showed that the interface stress in oxides grown in dry  $O_2$  is higher than those grown in pyrogenic steam. We attribute this to the fact that the viscosity of OH-containing  $SiO_2$  is about two orders of magnitude less than that of dry  $SiO_2$  [49]. An oxide with a lower viscosity results in a lower film stress and therefore a higher  $t_{bd}$ .

Now let us look at the case of substrate injection. The slightly decreasing trend and the higher  $t_{bd}$  for substrate injection in Fig. 3 can be explained using Fig. 11. For gate injection, the primary damage occurs at the substrate/oxide interface [1], [5], [13]. Kao *et al.* showed [45] that the stress is highest at the substrate/oxide interface and reduces continuously as we move away from the interface as shown schematically by

varying shade in Fig. 11. For substrate injection, stress has much less effect on the primary damage as it occurs at the poly-Si gate/oxide interface. Oxide breakdown occurs when a conducting path forms between the poly-Si gate and the substrate. A conducting path consists of many damage clusters caused by the electrical stress [15]. In a damage cluster there are many traps due to broken bonds, and it becomes conductive due to the traps [1], [15]. The oxide damage initiates primarily at the anode. After a damage cluster is formed the stress voltage drops across the remaining oxide which is now thinner at that spot increasing the electric field in that region. Hence, the generation of the damage clusters in the remaining thickness is accelerated. This concept is similar to the effective oxide thinning proposed by Lee [50]. The total time to breakdown is therefore dominated by the time to initially break the bonds and form a damage cluster in the oxide. From Fig. 11 it is clear that the stress is highest at the SiO<sub>2</sub>/substrate interface and therefore for a given electric field it is easier to break bonds at this interface. It will take shorter time to create initial damage for gate injection than for substrate injection. Accordingly the  $t_{bd}$  for gate injection is lower than that for substrate injection.

Surface roughness has been shown to influence the  $t_{bd}$  of the gate oxides [4]. The surface roughness model can explain the  $t_{bd}$  dependence on the injection polarity as well, but it cannot explain the  $t_{bd}$  dependence on oxide growth conditions because the rough poly-Si/oxide interface is the same for all growth conditions. Furthermore, it cannot explain why the  $t_{bd}$  reduces as the oxide thickness is reduced for constant current gate injection.

In our model, we assumed that the Si–O–Si bond is broken and replaced by the Si–Si bond during an oxide breakdown. This Si–Si bond is very weak and it can be either an electron trap or a hole trap [51]. If it traps an electron, it becomes an electron trap [52], [53]. Degraeve *et al.* have demonstrated that oxide breakdown occurs as soon as a critical density of neutral electron traps in the oxide is reached [15]. If it traps a hole, it becomes an E' center. It is consistent with the observation of E' centers in oxides during a breakdown process. It has been reported that the Si–Si bond in SiO<sub>2</sub> is the precursor of an E' center [54]. As to the missing oxygen atom after the formation of the Si–Si bond, the following process was proposed because it is not easy for the oxygen atoms to dissociate out of oxides [54], [55]:

$$2(\equiv Si - O - Si \equiv) \leftrightarrow \equiv Si - Si \equiv + \equiv Si - O - O - Si \equiv$$

.

These observations have serious implications for future scaling of MOS devices and fabrication technology, especially for EEPROM's. The fact that  $Q_{bd}$  decreases with decreasing oxide thickness will become a more serious problem when EEPROM's are doing erase-operations. The strained layer will play a more important role in oxide reliability and lifetime in the devices of newer generation. Controlling the strained layer and reducing the stress properly will be extremely important for future ultrathin gate oxides in the sub-100 nm ULSI technology. Besides, higher growth temperatures may be needed to improve reliability, which may go against the thermal budget

Fig. 11. Energy band diagrams of a MOS capacitor under gate injection  $(Vg^-)$  and substrate injection  $(Vg^+)$ . The darker shade depicts higher stress at the oxide/substrate interface.

limitations. Rapid thermal processing may become the logical choice to keep thermal budget low.

#### VIII. CONCLUSIONS

We have demonstrated that in MOS devices the reliability of the thin gate oxides for constant current gate injection  $(V_q^-)$  in the Fowler-Nordheim tunneling regime is closely related to the SiO<sub>2</sub>/Si interfacial physical stress. This is consistent with anode being the primary damage site. A physical stress-enhanced bond-breaking model is proposed. The oxide breakdown mechanism is very closely related to the Si-Si bond formation from the breakage of Si-O-Si bond, and that depends on the physical stress in the film. The interfacial stress comes from the volume expansion from Si to SiO2 during the thermal oxidation, and it is a strong function of growth conditions, such as temperature and growth rate. Higher temperatures and slower oxidation rates allow stress relaxation through viscous flow. Reduced disorder at the interface results in better reliability. In addition, the degradation of SiO<sub>2</sub> is enhanced as the thickness is reduced in the Fowler-Nordheim tunneling regime. In conjunction with the Gibbs free energy theory, this model successfully predicts the trends of time-to-breakdown  $(t_{bd})$  as a function of oxide thickness and growth conditions. The trends of predicted  $t_{bd}$ values agree well with the electrical  $t_{bd}$  and the stress data.

The process techniques, which enable slower growth rate and higher growth temperature, are desirable. These observations have serious implications for future scaling of MOS devices and fabrication technology. Higher growth temperatures may be needed to improve reliability, which may go against the thermal budget limitations. Rapid thermal processing may become the logical choice to keep thermal budget low.

#### ACKNOWLEDGMENT

The authors would like to thank H. Luo for help in FTIR measurements, R, Sharangpani and AG Associates for help in growing RTP oxides, J. W. McPherson for useful discussions of the bond breaking process, and M. Prisbe and G. Sarmiento for help in fabrication support.

#### REFERENCES

P. P. Apte and K. C. Saraswat, "Correlation of trap generation to charge to breakdown (Q<sub>bd</sub>): A physical damage model of dielectric breakdown," *IEEE Trans. Electron Devices*, vol. 41, pp. 1595–1602, Sept. 1994.

- [2] K. Ohmi, K. Nakamura, T. Futatsuki, and T. Ohmi, "Hydrogen-radical-balanced steam oxidation for growing ultra-thin high-reliability gate oxide films," in *IEEE, Symp.VLSI Technology Dig. Tech. Papers*, June 1994, pp. 109–110.

- [3] K. F. Schuegraf and C. Hu, "Hole injection SiO<sub>2</sub> breakdown model for very low voltage lifetime extrapolation," *IEEE Trans. Electron Devices*, vol. 41, pp. 761–767, May 1994.

- [4] S. S. Gong, M. E. Burnham, N. D. Theodore, and D. K. Schroder, "Evaluation of Q<sub>bd</sub> for electrons tunneling from the Si/SiO<sub>2</sub> interface compared to electron tunneling from the poly-Si/SiO<sub>2</sub> interface," *IEEE Trans. Electron Devices*, vol. 40, pp. 1251–1257, July 1993.

- [5] P. P. Apte and K. C. Saraswat, "SiO<sub>2</sub> degradation with charge injection polarity," *IEEE Electron Device Lett.*, vol. 12, pp. 512–514, Nov. 1993.

- [6] T. C. Yang, N. Bhat, and K. C. Saraswat, "Effect of interface stress on reliability of gate oxide," *Silicon Nitride and Silicon Dioxide Thin Insulating Films*, pp. 34–45, 1997.

- [7] L. K. Han *et al.*, "Polarity dependence of dielectric breakdown in scaled SiO<sub>2</sub>," in *IEEE IEDM Tech. Dig.*, 1994, pp. 617–620.

- [8] H. Yamada, "Reliability of ultimate ultrathin silicon oxide films produced by the continuous ultradry process," *J. Vac. Sci. Technol.*, vol. B14, pp. 757–762, Mar./Apr. 1996.

- [9] M. Depas et al., "Critical processes for ultrathin gate oxide integrity," The Physics and Chemistry of SiO<sub>2</sub> and Si/SiO<sub>2</sub> Interface—3, pp. 352–366, 1996.

- [10] K. Eriguchi, Y. Harada, and M. Niwa, "Influence of 1 nm-thick structural "strained-layer" near SiO<sub>2</sub>/Si interface on sub-4 nm-thick gate oxide reliability," in *IEEE IEDM Tech. Dig.*, 1998, pp. 175–178.

- [11] D. L. Crook, "Method of determining reliability screens for time dependent dielectric breakdown," in *Proc. IEEE Int. Reliability Physics Symp.*, 1979, pp. 1–7.

- [12] I.-C. Chen, S. E. Holland, and C. Hu, "Electrical breakdown in thin gate and tunneling oxides," *Trans. Electron Devices*, vol. ED-32, pp. 413–421, Feb. 1985.

- [13] D. J. DiMaria, E. Cartier, and D. Arnold, "Impact ionization, trap creation, degradation, and breakdown in silicon dioxide films on silicon," J. Appl. Phys., vol. 73, pp. 3367–3384, Apr. 1993.

- [14] D. J. Dumin et al., "High field related thin oxide wearout and breakdown," *IEEE Trans. Electron Devices*, vol. 42, pp. 760–772, Apr. 1995.

- [15] R. Degraeve et al., "New insights in the relation between electron trap generation and the statistical properties of oxide breakdown," *IEEE Trans. Electron Devices*, vol. 45, pp. 904–911, Apr. 1998.

- [16] H. Miura, S. Ikeda, and N. Suzuki, "Effect of mechanical stress on reliability of gate-oxide film in MOS transistors," in *IEDM Tech. Dig.*, 1996, pp. 743–746.

- [17] G. Lucovsky, M. J. Manitini, J. K. Srivastava, and E. A. Irene, "Low-temperature growth of silicon dioxide films: A study of chemical bonding by ellipsometry and infrared spectroscopy," *J. Vac. Sci. Technol. B*, vol. 5, no. 2, pp. 530–537, Mar./Apr. 1987.

- [18] J. K. Rudra and W. B. Fowler, "Oxygen vacancy and the E'<sub>1</sub> center in crystalline SiO<sub>2</sub>," *Phys. Rev. B*, vol. 35, no. 15, pp. 8223–8230, May 1987.

- [19] C. H. Bjorkman, J. T. Fitch, and G. Lucovsky, "Stress gradients in SiO2 thin films prepared by thermal oxidation and subjected to rapid thermal annealing," in *Proc. Materials Research Soc. Symp.*, vol. 146, Apr. 1989, pp. 197–202.

- [20] W. Jin, R. K. Kalia, and P. Vashishta, "Structural transformation in densified silica glass: A molecular-dynamics study," *Phys. Rev. B*, vol. 50, pp. 118–131, July 1994.

- [21] J. W. McPherson, V. K. Reddy, and H. C. Mogul, "Field-enhanced Si–Si bond-breakage mechanism for time-dependent dielectric breakdown in thin-film SiO<sub>2</sub> dielectrics," *Appl. Phys. Lett.*, vol. 71, pp. 1101–1103, Aug. 1997.

- [22] D. J. DiMaria, D. Arnold, and E. Cartier, "Degradation and breakdown of silicon dioxide films on silicon," *Appl. Phys. Lett.*, vol. 61, no. 19, pp. 2329–2331, Nov. 1992.

- [23] J. T. Fitch, C. H. Bjorkman, and G. Lucovsky, "Intrinsic stress and stress gradients at the SiO<sub>2</sub>/Si interface in structures prepared by thermal oxidation of Si and subjected to rapid thermal annealing," *J. Vac. Sci. Technol. B*, vol. 7, pp. 775–781, July/Aug. 1989.

- [24] J. T. Fitch, C. H. Bjorkman, J. J. Sumakeris, and G. Lucovsky, "The effect of intrinsic in-plane stress on the local atomic structure of thermally grown SiO<sub>2</sub>," in *Mat. Res. Soc. Symp. Proc.*, vol. 130, 1989, pp. 289–294.

- [25] B. J. Mrstik, A. G. Revesz, M. Ancona, and H. L. Hughes, "Structural and strain-related effects during growth of SiO<sub>2</sub> films on silicon," *J. Electrochem. Soc. A*, vol. 134, pp. 2020–2007, Aug. 1987.

- [26] C. H. Bjorkman, J. T. Fitch, and G. Lucovsky, "Correlation between midgap interface state density and thickness-averaged oxide stress and strain at the Si/SiO<sub>2</sub> interfaces formed by thermal oxidation of Si," *Appl. Phys. Lett.*, vol. 56, pp. 1983–1985, May 1990.

- [27] F. J. Grunthaner, P. J. Grunthaner, and J. Maserjian, "Radiation-induced defects in SiO<sub>2</sub> as determined with XPS," *IEEE Trans. Nucl. Sci.*, vol. NS-29, pp. 1462–1466, Dec. 1982.

- [28] E. Kobeda and E. A. Irene, "In situ stress measurements during thermal oxidation of silicon," J. Vac. Sci. Technol. B, vol. 7, pp. 163–166, Mar./Apr. 1989.

- [29] E. P. EerNisse, "Stress in thermal SiO<sub>2</sub> during growth," Appl. Phys. Lett., vol. 35, pp. 8–10, July 1979.

- [30] C. Martinet and R. A. B. Devine, "Analysis of the vibrational mode spectra of amorphous SiO<sub>2</sub> films," J. Appl. Phys., vol. 77, pp. 4343–4348, May 1995.

- [31] J. W. McPherson and H. C. Mogul, "Disturbed bonding states in SiO2 thin-films and their impact on time-dependent dielectric breakdown," in *IEEE Proc. Int. Reliability Physics Symp.*, 1998, pp. 47–56.

- [32] J. W. McPherson, "Stress dependent activation energy," in *IEEE Proc. Int. Reliability Physics Symp.*, 1986, pp. 12–18.

- [33] S. Glasstone, K. Laidler, and H. Eyring, The Theory of Rate Processes. New York: McGraw-Hill, 1941.

- [34] H. Eyring, D. Henderson, B. Stover, and E. Eyring, Statistical Mechanics and Dynamics. New York: Wiley, 1964.

- [35] N. L. Allinger, X. Zhou, and J. Bergsma, "Molecular mechanics parameters," J. Molec. Struct., vol. 312, pp. 69–83, Aug. 1994.

- [36] T.-C. Yang, "Role of physical stress and electric field on the reliability of ultrathin MOS gate oxides," Ph.D. dissertation, Stanford Univ., Stanford, CA, Mar. 1999.

- [37] W. A. Harrison, Electronic Structure and the Properties of Solids. New York: Dover, 1989.

- [38] D. J. DiMaria, "Dependence on gate work function of oxide charging, defect generation, and hole currents in metal-oxide-semiconductor structures," J. Appl. Phys., vol. 81, pp. 3220–3226, Apr. 1997.

- [39] Y. Shi, T. P. Ma, S. Prasad, and S. Dhanda, "Polarity-dependent tunneling current and oxide breakdown in dual-gate CMOSFET's," *IEEE Electron Dev. Lett*, vol. 19, pp. 391–393, Oct. 1998.

- [40] T. Nigam, R. Degraeve, G. Groeseneken, M. M. Heyns, and H. E. Maes, "Constant current charge-to-breakdown: Still a valid tool to study the reliability of MOS structures?," in *Int. Reliability Physics Symp.*, 1998, pp. 62–69.

- [41] T. C. Yang, P. Sachdev, and K. C. Saraswat, "Dependence of Fermi level positions at gate and substrate on the reliability of ultrathin MOS gate oxides," *IEEE Trans. Electron Devices*, vol. 46, pp. 1457–1463, July 1999.

- [42] N. Bhat and K. C. Saraswat, "Characterization of border trap generation in rapid thermally annealed oxides deposited using silane chemistry," J. Appl. Phys., vol. 84, p. 2722, Sept. 1998.

- [43] N. Bhat, A. Wang, and K. C. Saraswat, "Rapid thermal anneal of gate oxides for low thermal budget TFTs," *IEEE Trans. Electron Devices*, vol. 46, pp. 63–69, Jan. 1999.

- [44] S. H. Lee, P. Sachdev, T. C. Yang, J. C. Bravman, and K. C. Saraswat, "Effect of interface stress on the quasibreakdown of ultrathin oxide," in Proc. Joint Int. Meeting Electrochem. Soc., Honolulu, HI, Oct. 17–22, 1999

- [45] D.-B. Kao, J. P. McVittie, W. D. Nix, and K. C. Saraswat, "Two-dimensional thermal oxidation of silicon. II: Modeling stress effects in wet oxides," *IEEE Trans. Electron Devices*, vol. 35, pp. 25–37, Jan. 1988.

- [46] E. Hasegawa, A. Ishitani, K. Akimoto, M. Tsukiji, and N. Ohta, "SiO<sub>2</sub>/Si interface structures and reliability characteristics," *J. Electrochem. Soc.*, vol. 142, no. 1, pp. 273–282, Jan. 1995.

- [47] K. Taniguchi, M. Tanaka, and C. Hamaguchi, "Density relaxation of silicon dioxide on (100) silicon during thermal annealing," *J. Appl. Phys.*, vol. 67, pp. 2195–2198, Mar. 1990.

- [48] G. Lupke et al., "Thermally induced stress relaxation of silicon dioxide on vicinal Si(111) studied with surface nonlinear-optical techniques," in Proc. Conf. Nonlinear Optics: Materials, Fundamentals and Applications, Waikoloa, HI, USA, July 25–29, 1994, pp. 89–91.

- [49] B. J. Mrstik, A. G. Revesz, M. Ancona, and H. L. Hughes, "Structural and strain-related effects during growth of SiO<sub>2</sub> films on silicon," *J. Electrochem. Soc.*, vol. 134, pp. 2020–2027, Aug. 1987.

- [50] J. C. Lee, I. C. Chen, and C. Hu, "Modeling and characterization of gate oxide reliability," *IEEE Trans. Electron Devices*, vol. 35, pp. 2268–2278, Dec. 1988.

- [51] A. Reisman and C. K. Williams, "SiO<sub>2</sub> gate insulator defects, spatial distributions, densities, types, and sizes," *J. Electron. Mater.*, vol. 24, pp. 2015–2023, Dec. 1995.

- [52] E. Harari, "Dielectric breakdown in electrically stressed thin films of thermal SiO<sub>2</sub>," J. Appl Phys., vol. 49, pp. 2478–2489, Apr. 1978.

- [53] G. Auriel, J. Oualid, and D. Vuillaume, "Electron traps created in gate oxides by Fowler–Nordheim injections," *Microelectron. Reliab.*, vol. 38, pp. 227–231, 1998.

- [54] J. Robertson, "Intrinsic defects and hydroxyl groups in a-SiO<sub>2</sub>," J. Phys. C Solid State Phys., vol. 17, pp. L221–L225, Mar. 1984.

- [55] M. Kimura, "Oxide breakdown mechanism and quantum physical chemistry for time-dependent dielectric breakdown," in *IEEE Proc. Int. Reliability Physics Symp.*, 1997, pp. 190–200.

**Tien-Chun Yang** (S'93) received the B.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, R.O.C., in 1998, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1995 and 1998, respectively. His Ph.D. dissertation work was in the reliability of ultrathin MOS gate oxides.

In 1998, he joined Advanced Micro Devices, Sunnyvale, CA, where he is currently working on the device design and the development of thin gate dielectrics of flash memory technology. His research

interests include oxide reliability, device physics, and process technology. He has authored or co-authored about 15 technical papers.

Dr. Yang is a member of the American Vacuum Society and the Materials Research Society.

Krishna C. Saraswat (M'70–SM'85–F'89) received the B.E. degree in electronics and telecommunications in 1968 from Birla Institute of Technology and Science, Pilani, India, and the M.S. and Ph.D degrees in electrical engineering in 1969 and 1974, respectively, from Stanford University, Stanford, CA.

From 1969 to 1970, he worked on microwave transitors at Texas Instruments, Dallas, TX, and since 1971, he has been with Stanford University, where presently he is a Professor of electrical engineering and Associate Director of the NSF/SRC Engineering

Research Center for Environmentally Benign Semiconductor Manufacturing. From 1996 to 1997, he was the Director of the Integrated Circuits Laboratory at Stanford. He is working on a variety of problems related to new and innovative materials, device structures, and process technology of silicon devices and integrated circuits. Special areas of interest are thin-film MOS transitors on insulator for 3-D multilayer IC's and flat panel displays, thin-film technology for VLSI interconnections and contacts, process and equipment modeling, ultrathin MOS gate dielectrics, rapid thermal processing, IC process design automation, and development of tools and methodology for simulation and control of a manufacturing line. His group has developed several simulators for process, equipment and factory process, equipment and factory performance simulations, such as SPEEDIE for etch and deposition simulation, SCOPE for IC factory performance simulations, and a thermal simulator for RTP equipment design. Currently, he is also involved in the development of BEST (beck-end simulation tool), an interconnect process simulator. He has authored or co-authored more than 300 technical papers.

Prof. Saraswat was co-editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES from 1988 to 1990. He is a member of the Electrochemical Society, the Materials Research Society, and the Society for Information Display.