### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Effects of mechanical stress on the performance of metal-oxide-semiconductor transistors

Yang, Peizhen

2012

Yang, P. (2012). Effects of mechanical stress on the performance of metal-oxide-semiconductor transistors. Doctoral thesis, Nanyang Technological University, Singapore.

### https://hdl.handle.net/10356/50306

https://doi.org/10.32657/10356/50306

Downloaded on 24 Aug 2022 21:10:27 SGT

## EFFECTS OF MECHANICAL STRESS ON THE PERFORMANCE OF METAL-OXIDE-SEMICONDUCTOR TRANSISTORS

# YANG PEIZHEN SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING

2012

## EFFECTS OF MECHANICAL STRESS ON THE PERFORMANCE OF METAL-OXIDE-SEMICONDUCTOR TRANSISTORS

YANG PEIZHEN

School of Electrical and Electronic Engineering

A thesis submitted to the Nanyang Technological University in fulfillment of the requirement for the degree of Doctor of Philosophy

2012

### ACKNOWLEDGEMENT

First and foremost, I would like to thank my thesis advisor, Assoc Prof Lau Wai Shing for his guidance, encouragement, and continuous support throughout my research. I am also indebted to Assoc Prof Chen Tupei for his assistance in the final stage of my postgraduate studies.

I would like to acknowledge the staff of GLOBALFOUNDRIES SINGAPORE Pte Ltd for providing the wafers for this project. In particular, I would like to thank the engineers and managers whom I have personally worked with: Siah Soh Yun, Lai Seow Wei, Patrick Lo, Tang Yee Ling, Lim Eng Hua, Eng Chee Wee, Vincent Ho, Loh Cheng Hou, Lim Boon Kiat, Toh Liew Feng, Liu Yang, Jacob Wang and See Kwang Seng.

My sincere gratitude goes to Asst Prof Sridhar Idapalapati and Mr Leo Cheng Seng from the School of Mechanical and Aerospace Engineering (MAE) for their assistance in the design and calibration of the four point rod bending fixture. My fellow coursemate, Teo Zhiqiang Andy was a great help with the construction and calibration of the four point rod bending fixture. I would like to specifically thank Mr Lim Meng Keong from the School of Materials Science and Engineering (MSE) for his assistance in the wafer dicing, which is essential for my four point rod bending experiments.

My research at NTU would not be possible without the funding from GLOBALFOUNDRIES SINGAPORE Pte Ltd and Singapore Economic Development Board (EDB). The weekly meeting has provided a unique opportunity to exchange ideas and receive timely comments and advice. Last, but not the least, my parents receive my deepest gratitude and love for their dedication and many years of support. My siblings, Sheryl and Zhiren were a continuous source of love and I wish them success in their endeavors and happiness throughout their life. I am also indebted to my husband, Justin for his extraordinary patience, understanding and love during the past few years.

### ABSTRACT

Stress engineering is widely used in the microelectronics industry to improve the oncurrent  $(I_{on})$  performance of the metal-oxide-semiconductor (MOS) transistors through the strain-induced mobility enhancement. However, there are still debates regarding the relevance of the low-field mobility in the saturation drain current of the nanoscale MOS transistors. Based on velocity saturation model, the high-field velocity is independent of the low-field mobility. In the other words, velocity saturation model predicts that mobility enhancement techniques will not improve  $I_{on}$  of the nanoscale MOS transistors. Ballistic transport model considers an ideal situation where the channel carriers do not experience any scattering when they transit from the source to the drain. Since mobility is a concept that involves channel scattering, ballistic transport regards mobility as irrelevant in the nanoscale MOS transistors. In quasi-ballistic transport model, channel carriers will undergo a number of channel scatterings before reaching the drain. Hence, quasi-ballistic transport model is able to account for the strain-induced  $I_{on}$  improvement in nanoscale MOS transistors. However, the saturation drain current equation of a transistor in the quasi-ballistic model comprises parameters that are not properly defined. Furthermore, some researchers managed to use velocity saturation model to fit the saturation current of the nanoscale MOS transistor. By improvising Lundstrom's 1997 theory on the quasiballistic transport and unifying the merits of existing transport models, we arrive at a simplified saturation drain current equation for nanoscale MOS transistors.

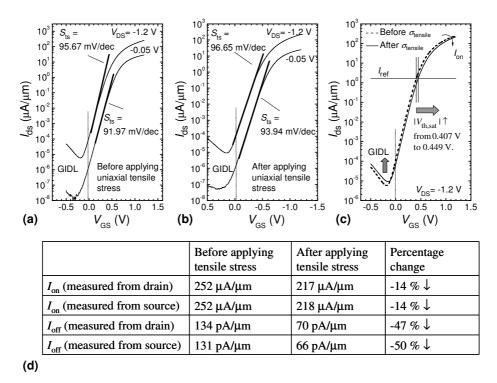

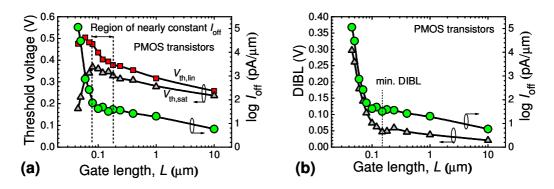

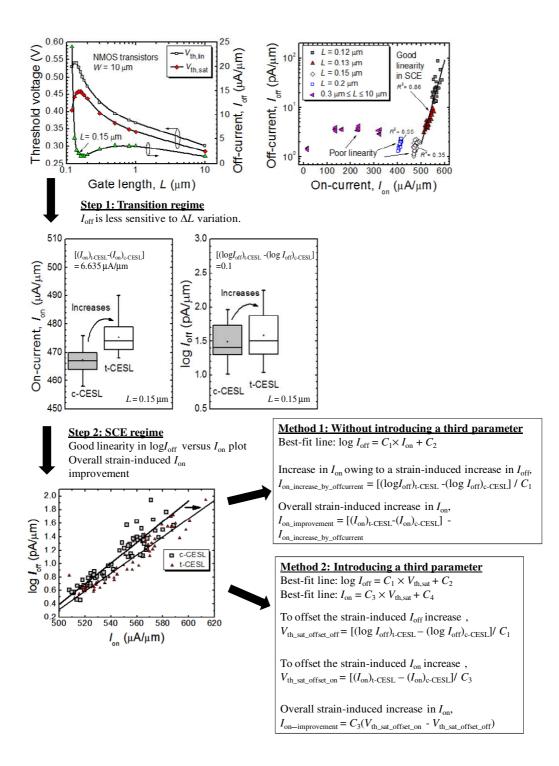

Most research in stress engineering focus on the strain-induced  $I_{on}$  improvement, but disregard the effects of the mechanical stress on the off-current ( $I_{off}$ ). Using externally applied mechanical stress, we can isolate the effects of process variations from the straininduced effects from the strain-induced effects on  $I_{off}$ . We studied the physics behind the strain-induced increase in the subthreshold  $I_{off}$  and found that the strain-induced change in the quantum mechanical confinement decreases the subthreshold swing ( $S_{ts}$ ) of NMOS transistor but increases  $S_{ts}$  of p-channel MOS (PMOS) transistor. It is well-known that uniaxial tensile stress leads to electron mobility enhancement and a reduction in the threshold voltage of NMOS transistor. Since our experimental results show that uniaxial tensile stress can increase the subthreshold  $I_{off}$  of NMOS transistor, the effects of straininduced reduction in threshold voltage and the strain-induced mobility enhancement will dominate over the strain-induced improvement in the subthreshold swing. To extend the study to the process-induced stress, we need to reduce the effects of process variation on  $I_{off}$ . In order to reduce the effects of wafer-to-wafer variation on  $I_{off}$ , we intentionally use consecutive wafers with different amount of process-induced stress. In addition, we also identify NMOS transistors whose  $I_{off}$  is less sensitive to the die-to-die variation. Our experimental results show that CESL-induced tensile stress can increase both  $I_{on}$  and the subthreshold I<sub>off</sub> of NMOS transistors. In fact, we observed that CESL-induced tensile stress has led to a bigger percentage increase in  $\log I_{off}$  as compared to  $I_{on}$  in NMOS transistor. This makes us wonder if stress engineering can lead to an overall  $I_{on}$ improvement. The most straightforward approach to ascertain the overall strain-induced  $I_{on}$ improvement is to determine the strain-induced increase in  $\log I_{off}$ , and then obtain the corresponding increase in  $I_{on}$  from the log $I_{off}$  versus  $I_{on}$  plot characteristics plot. However, this approach does not explain why there is an overall strain-induced improvement in  $I_{on}$ when stress engineering actually leads to a bigger percentage increase in  $\log I_{off}$  compared to that of  $I_{on}$ . Hence, we introduce a third parameter ( $V_{th,sat}$  or DIBL) in the log $I_{off}$  versus  $I_{on}$ characteristics. We found that the subthreshold  $I_{off}$  is more sensitive to the change in  $V_{th,sat}$ as compared to  $I_{on}$  and thus the strain-induced increase in  $I_{off}$  can be removed by a slight change in  $V_{\text{th,sat}}$  without much effect on  $I_{\text{on}}$ . This leads to an overall improvement straininduced improvement in Ion even though stress engineering actually leads to a bigger percentage increase in  $\log I_{off}$  compared to that of  $I_{on}$ . Similar analysis can be applied by introducing DIBL as the third parameter in the  $\log I_{off}$  versus  $I_{on}$  characteristics.

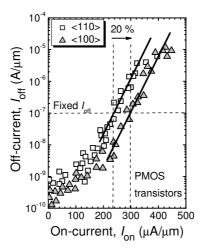

Apart from the conventional <110> channel orientation on (100) surface-oriented silicon wafer, transistors can also be fabricated on 45° rotated (100) surface-oriented wafer with <100> channel orientation. We have evaluated the impact of the change in channel orientation together with mechanical stress on the performance of NMOS transistors and PMOS transistors. We found that NMOS transistors are not improved by switching from the conventional <110> channel orientation to <100> channel orientation but they can be improved by tensile stress. PMOS transistors are improved by switching from the conventional <110> channel orientation to <100> channel orientation but PMOS transistors with <100> channel orientation to <100> channel orientation but PMOS transistors with <100> channel orientation to <100> channel orientation but PMOS transistors with <100> channel orientation to <100> channel orientation but PMOS transistors with <100> channel orientation are not sensitive to mechanical stress.

### CONTENTS

| ACKNOWLEDGEMENT i |         |                                                                         |     |

|-------------------|---------|-------------------------------------------------------------------------|-----|

| ABSTRACT ii       |         |                                                                         |     |

| LI                | ST OF I | FIGURES                                                                 | vi  |

| LI                | ST OF 1 | ГАBLES                                                                  | xiv |

| 1.                |         | luction                                                                 |     |

| 1.                | 1.1     | Background                                                              |     |

|                   | 1.1     | Roles of carrier mobility in drain current transport                    |     |

|                   | 1.2     | Mobility enhancement techniques                                         |     |

|                   | 1.5     | Organization of the Thesis                                              |     |

| 2.                |         | ture review on Stress Engineering                                       |     |

| 2.                |         |                                                                         |     |

|                   | 2.1     | Methods to introduce channel stress                                     |     |

|                   | 2.1.1   | Substrate-induced stress                                                | 8   |

|                   | 2.1.2   | Process-induced stress                                                  | 9   |

|                   | 2.1.3   | Externally applied mechanical stress                                    | 15  |

|                   | 2.2     | Strain-induced mobility enhancement                                     | 18  |

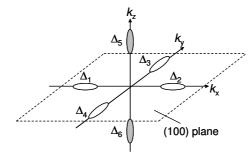

|                   | 2.2.1   | First Brillouin zone                                                    | 18  |

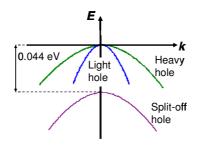

|                   | 2.2.2   | <i>E-k</i> diagram of unstrained bulk silicon                           | 20  |

|                   | 2.2.3   | Relationship between the effective mass and the <i>E-k</i> diagram      | 23  |

|                   | 2.2.4   | Effects of mechanical stress on the conduction band minimum             | 24  |

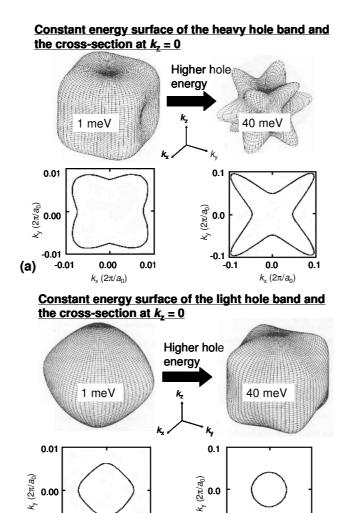

|                   | 2.2.5   | Effects of mechanical stress on the valence band maximum                | 27  |

|                   | 2.2.6   | Low-field mobility: Drude model                                         | 30  |

|                   | 2.3     | Usage of Piezoresistance coefficients                                   | 32  |

| 3.                | Drain   | current transport in nanoscale MOS transistors                          | 36  |

|                   | 3.1     | Velocity saturation model                                               |     |

|                   | 3.2     | Ballistic transport model                                               |     |

|                   | 3.3     | Quasi-ballistic transport                                               | 48  |

|                   | 3.4     | Semi-empirical model                                                    | 51  |

|                   | 3.5     | Results and Discussion                                                  | 53  |

|                   | 3.5.1   | Temperature dependency of the drain current                             | 53  |

|                   | 3.5.2   | Saturation drain current equation                                       | 56  |

|                   | 3.5.3   | Physics behind the apparent velocity saturation                         | 67  |

| 4.                | Effect  | ts of mechanical stress on the electrical parameters of MOS transistors | 68  |

| 4.1                  | On-current ( <i>I</i> <sub>on</sub> )                                                           | 68  |  |

|----------------------|-------------------------------------------------------------------------------------------------|-----|--|

| 4.2                  | Threshold voltage                                                                               | 69  |  |

| 4.2.                 | Strain-induced effects on silicon bandgap                                                       |     |  |

| 4.2.2                | 2 Equations for strain-induced change in the threshold voltage                                  | 71  |  |

| 4.3                  | Gate leakage current                                                                            | 72  |  |

| 4.4                  | Gate-induced-drain leakage (GIDL) current                                                       | 74  |  |

| 4.5                  | Gate oxide thickness                                                                            | 75  |  |

| 4.5.                 | Poisson's ratio                                                                                 | 75  |  |

| 4.5.                 | 2 Quantum confinement                                                                           | 76  |  |

| 4.6                  | Subthreshold off-current $(I_{off})$                                                            | 80  |  |

| 4.7                  | Results and Discussion                                                                          | 83  |  |

| 4.7.                 | Physics behind the linearity in the log $I_{\text{off}}$ versus $I_{\text{on}}$ characteristics |     |  |

| 4.7.2                | 2 Four-point bending measurement                                                                |     |  |

| 4.7.                 | 3 Tensile stressed contact etch stop layer (CESL)                                               |     |  |

| 5. Impa              | ct of the change in channel orientation on performance                                          | 103 |  |

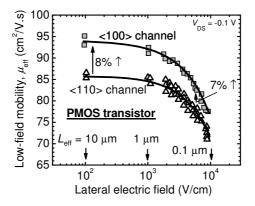

| 5.1                  | Impact of channel orientation on hole mobility                                                  | 104 |  |

| 5.2                  | Limited studies on the impact of channel orientation on electron mobility                       | 105 |  |

| 5.3                  | Experimental evidence of an increase in $L_{\rm eff}$ by channel orientation                    | 108 |  |

| 5.4                  | Mechanism behind the increase in $L_{\rm eff}$ by channel orientation                           | 109 |  |

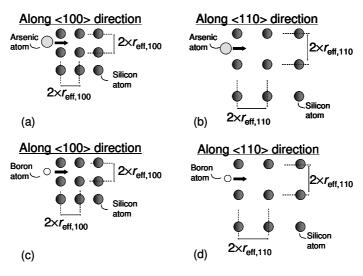

| 5.4.                 | I Impact of channel orientation on diffusion                                                    | 109 |  |

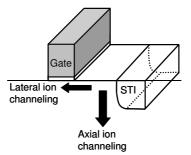

| 5.4.2                | 2 Impact of channel orientation on ion channeling                                               | 111 |  |

| 5.5                  | Results and Discussion                                                                          | 114 |  |

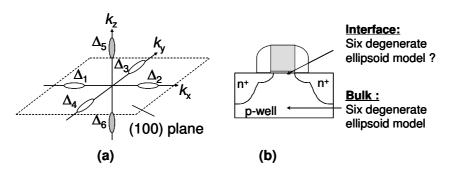

| 5.5.                 | Validity of the six degenerate ellipsoid model                                                  | 114 |  |

| 5.5.2                | 2 Mechanism behind the increase in $L_{\text{eff}}$ of <100> transistors                        | 118 |  |

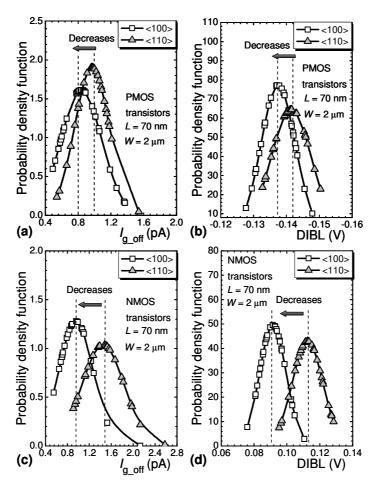

| 5.5.                 | Effects of channel orientation on $I_{on}$ and $I_{off}$ of MOS transistors                     | 121 |  |

| 6. Conc              | lusions and Recommendation                                                                      | 125 |  |

| 6.1                  | Main contributions of the thesis                                                                | 125 |  |

| 6.2                  | Recommendations of future work                                                                  | 126 |  |

| List of publications |                                                                                                 |     |  |

| Appendix             | : Effects of surface-orientation on electron mobility and hole mobility                         | 131 |  |

| Bibliogra            | phy                                                                                             | 134 |  |

### LIST OF FIGURES

| Figure 1-1 Moore's Law: CPU transistor count has increased by two times and feature size has                |

|-------------------------------------------------------------------------------------------------------------|

| decreased by 0.7 times in every two years [1.1]1                                                            |

| Figure 1-2 Excessive gate-oxide leakage occurs with further scaling of the conventional silicon             |

| oxynitride gate dielectric [1.2]                                                                            |

| Figure 1-3 Total chip dynamic and static power dissipation trends based on the International                |

| Technology Roadmap for Semiconductor (ITRS) [1.3]                                                           |

| Figure 1-4 Experimental correlation between low-field mobility ( $\mu_{eff}$ ) and the high-field carrier   |

| velocity (v <sub>eff</sub> ) for the nanoscale NMOS transistors [1.29]                                      |

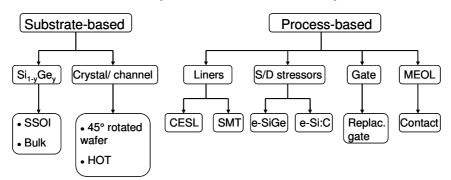

| Figure 1-5 Flow chart of the main mobility enhancement techniques [1.30]                                    |

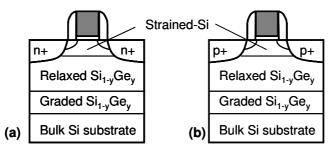

| Figure 2-1 Cross-section of (a) NMOS transistor, (b) PMOS transistor fabricated on the strained-Si          |

| on relaxed Si <sub>1-x</sub> Ge <sub>y</sub> virtual substrate                                              |

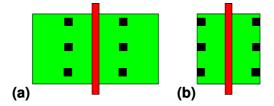

| Figure 2-2 Schematics of (a) the ordinary S/D contacts and (b) the borderless S/D contacts                  |

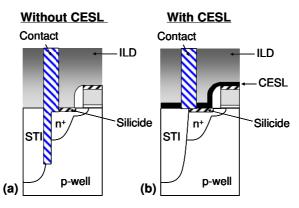

| Figure 2-3 The importance of CESL to prevent the electrical shorting between $n^+$ S/D and p-well           |

| when there is a mask misalignment: (a) Without CESL, (b) With CESL11                                        |

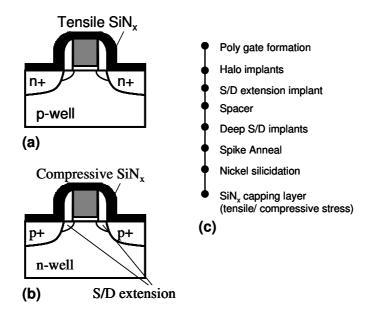

| Figure 2-4 Process flow of CESL as a mechanical stressor                                                    |

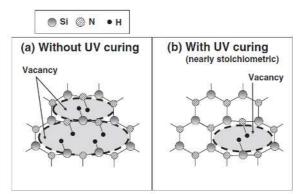

| Figure 2-5 Structural model for local bonding arrangement in PECVD SiN <sub>x</sub> film for (a) Without UV |

| curing, (b) With UV curing [2.14]11                                                                         |

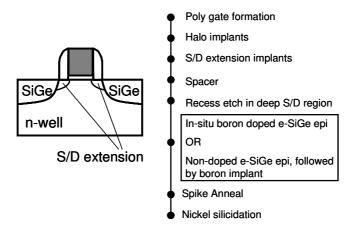

| Figure 2-6 Process flow of Si <sub>1-y</sub> Ge <sub>y</sub> S/D stressor for PMOS transistor               |

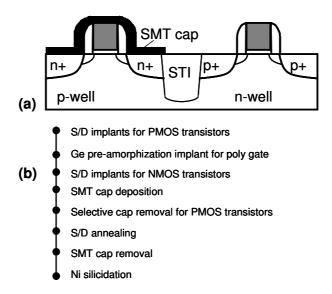

| Figure 2-7 Process flow of Stress Memorization Technique (SMT)14                                            |

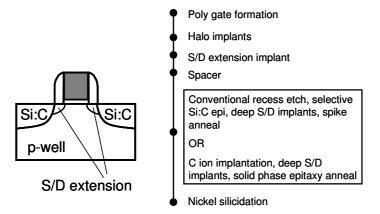

| Figure 2-8 Process flow of e-Si:C S/D as a mechanical stressor15                                            |

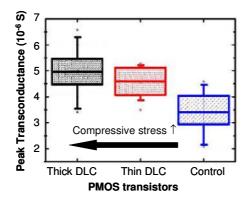

| Figure 2-9 The use of statistics to compare the hole mobility enhancement by the Diamond-like               |

| Carbon (DLC) liner [2.37]16                                                                                 |

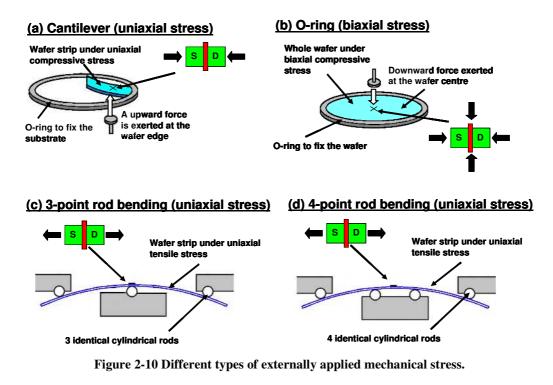

| Figure 2-10 Different types of externally applied mechanical stress17                                       |

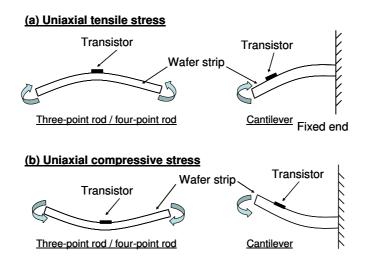

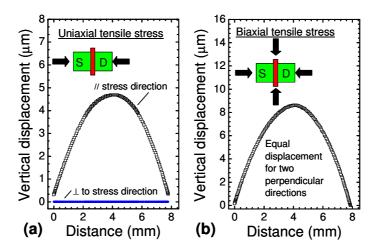

| Figure 2-11 Schematics of the curvature of the rectangular wafer strips under: (a) uniaxial tensile         |

| stress and (b) uniaxial compressive stress. Note that the transistor is on the top surface of the wafer     |

| strip17                                                                                                     |

| Figure 2-12 Differences between uniaxial tensile stress and biaxial tensile tensile in terms of wafer       |

| displacement from equilibrium position [2.43]                                                               |

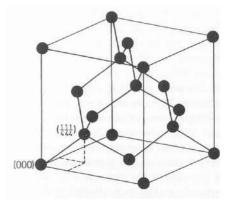

| Figure 2-13 Schematics of a diamond crystal structure [2.47]                                                |

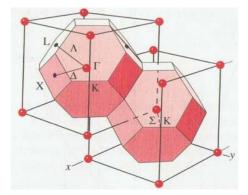

| Figure 2-14 Reciprocal lattice of a face-centred cubic lattice with its first Brillouin zone [2.48]19       |

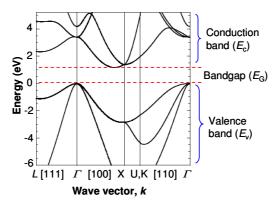

| Figure 2-15 Schematics of energy band diagram of silicon [2.61]21                                           |

| Figure 2-16 Schematics of the conduction band valleys of silicon21                                          |

| Figure 2-17 Schematics of valence band maximum of silicon [2.62]21                                          |

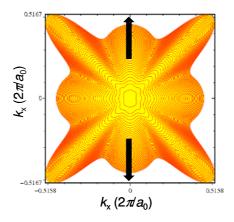

| Figure 2-18 Constant energy surface and cross section of valence band maximum at $k_z = 0$ plane            |

| [2.63]                                                                                                      |

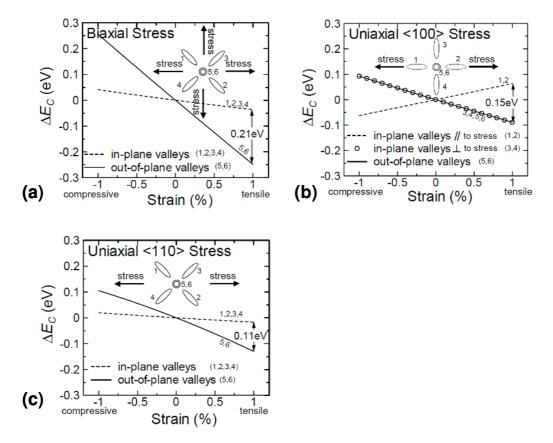

| Figure 2-19 Splitting of the conduction band edge ( $\Delta E_c$ ) as a function of (a) biaxial stress, (b)                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| uniaxial $<100>$ stress, (c) uniaxial $<110>$ stress [1.14]                                                                                    |

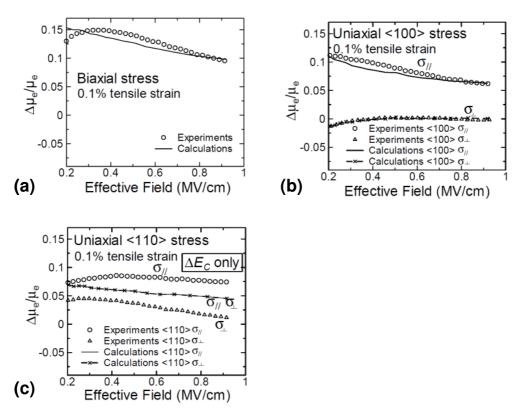

| Figure 2-20 Electron mobility enhancement $(\Delta \mu_e / \Delta \mu_e)$ as a function of the vertical electric field                         |

| under (a) biaxial stress, (b) uniaxial <100> stress, (c) uniaxial <110> stress [1.14]                                                          |

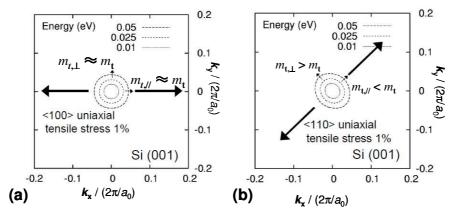

| Figure 2-21 Energy contours of the out-of-plane conduction band valleys ( $\Delta_5$ , $\Delta_6$ ) on (100) silicon                           |

| plane under (a) uniaxial <100> tensile stress, (b) uniaxial <110> tensile stress [1.14]26                                                      |

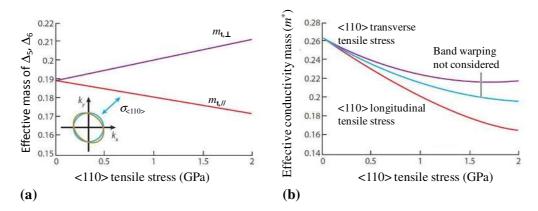

| Figure 2-22 The effects of <110> uniaxial tensile stress on: (a) the longitudinal effective mass $(m_{t,l})$                                   |

| and the transverse effective mass $(m_{t,\perp})$ of the out-of-plane conduction valleys, (b) the effective                                    |

| conductivity mass ( <i>m</i> <sup>*</sup> ) [2.66]27                                                                                           |

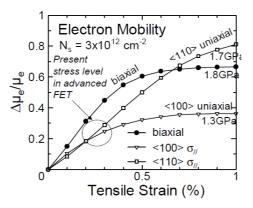

| Figure 2-23 Electron mobility enhancement as a function of mechanical stress [1.14]27                                                          |

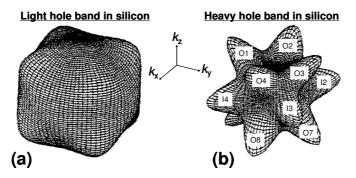

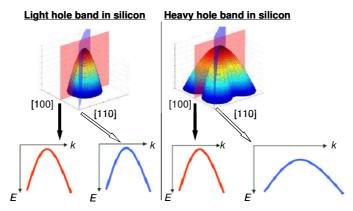

| Figure 2-24 Constant energy contours of (a) the light hole band and (b) heavy hole band at $\Gamma$ for                                        |

| unstressed bulk silicon [1.15, 2.63]. $k_x$ , $k_y$ and $k_z$ are the wave vectors along x, y and z directions28                               |

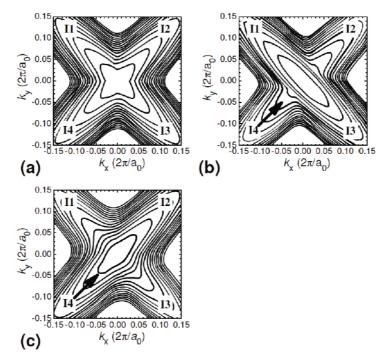

| Figure 2-25 Constant energy contours separated by 25 meV for the lowest hole energy band of                                                    |

| (100) bulk silicon at $\Gamma$ under (a) the unstressed condition, (b) the uniaxial compressive stress along                                   |

| <110> direction, and (c) the uniaxial tensile stress along <110> direction [1.15]29                                                            |

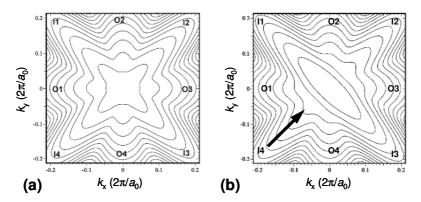

| Figure 2-26 Constant energy contours of the lowest hole energy band at $\Gamma$ of silicon inversion layer                                     |

| in (100) plane with vertical confinement field of 1 MV/cm under (a) the unstrained condition, (b)                                              |

| the uniaxial compressive stress along <110> channel direction (as indicated by the arrow) [1.15]29                                             |

| Figure 2-27 Phonon dispersion spectrum of silicon along the (100) direction of the first Brillouin (                                           |

| $\Gamma \rightarrow \Delta \rightarrow X$ ). The <i>f</i> and <i>g</i> phonons participate in the intervalley scattering of electrons [2.71]31 |

| Figure 2-28 First Heavy-hole subband equivalent energy lines of (100) surface-oriented silicon                                                 |

| under uniaxial <100> tensile stress of 1.5 GPa (Courtesy of Dr Pham from BST, TU Braunschweig,                                                 |

| Germany, Ref. [2.44])                                                                                                                          |

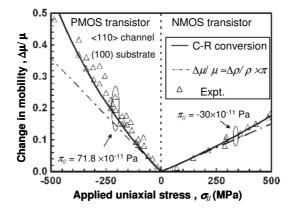

| Figure 2-29 Non-linearity of piezoresistance coefficient at higher uniaxial stress [2.85]. C-R                                                 |

| conversion model is represented by eqn. (2.16). $\Delta \mu / \mu \approx \Delta \rho / \rho \times \pi$ refers to the piezoresistance         |

| model, which is given by eqn. (2.13)                                                                                                           |

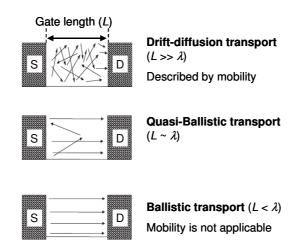

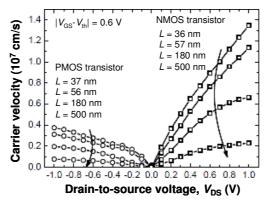

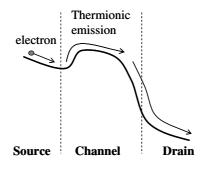

| Figure 3-1 Classification of carrier transport in MOS transistors [1.21]                                                                       |

| Figure 3-2 Time-of-flight measurement suggests that the low-field mobility ( $\mu_{eff}$ ) is independent of                                   |

| carrier velocity at high lateral electric field [1.9]                                                                                          |

| Figure 3-3 Electron velocity overshoot has been observed at room temperature in bulk NMOS                                                      |

| transistor with gate length ( $L$ ) of 32 nm [1.19]                                                                                            |

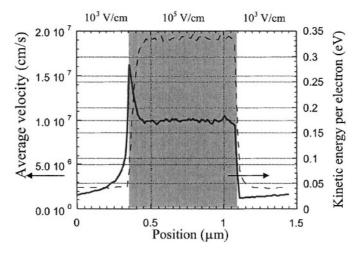

| Figure 3-4 The average velocity versus position for electrons injected into a short slab of silicon                                            |

| with a high electric field [3.4]. Dotted line refers to the average velocity of electrons. Solid line                                          |

| refers to the kinetic energy of the electrons                                                                                                  |

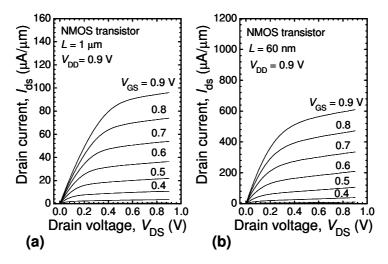

| Figure 3-5 Equal spacing in the $I_{ds}$ versus $V_{DS}$ characteristics at high $V_{DS}$ is observed in (a) long-                             |

| channel NMOS transistor, (b) short-channel NMOS transistor                                                                                     |

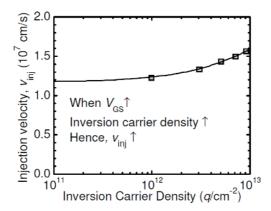

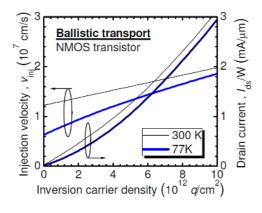

| Figure 3-6 Injection velocity $(v_{inj})$ as a function of the inversion carrier density [1.21]40                                              |

| Figure 3-7 Temperature dependency of the injection velocity $(v_{inj})$ and the saturation drain current                      |

|-------------------------------------------------------------------------------------------------------------------------------|

| of the nanoscale NMOS transistors [1.20]41                                                                                    |

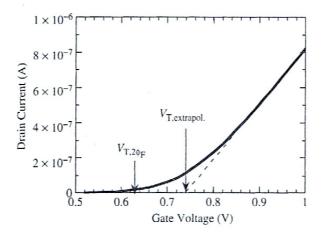

| Figure 3-8 Illustration of $V_{T, 2\phi F}$ and $V_{T, extrapol}$ in the $I_{ds}$ versus $V_{GS}$ characteristics[3.14]       |

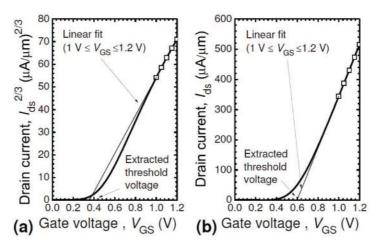

| Figure 3-9 As opposed to Natori's 1994 theory on ballistic transport, the saturation $I_{ds}$ of the                          |

| nanoscale NMOS transistor ( $L = 60$ nm) does not follow a ( $V_{GS} - V_{th,sat}$ ) <sup>3/2</sup> relationship. The symbols |

| indicate the data points that are used for the linear extrapolation. The thicker lines indicate the                           |

| experimental values of <i>I</i> <sub>ds</sub> 42                                                                              |

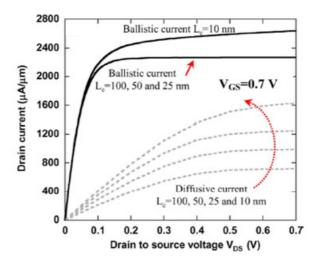

| Figure 3-10 Simulation results of the drain current as a function of the drain-to-source voltage ( $V_{DS}$ )                 |

| for a double-gate NMOS transistor with several channel lengths [3.15]. Solid line for ballistic                               |

| transport and dashed line for classical diffusive transport43                                                                 |

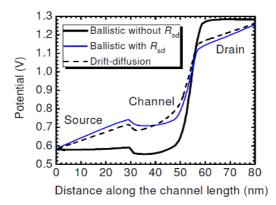

| Figure 3-11 Impact of the S/D series resistance $(R_{sd})$ on the potential profile along the channel of                      |

| NMOS transistor [3.15]43                                                                                                      |

| Figure 3-12 Impact of the S/D series resistance ( $R_{sd}$ ) on the $I_{ds}$ versus $V_{DS}$ characteristics of a NMOS        |

| transistor [3.15]44                                                                                                           |

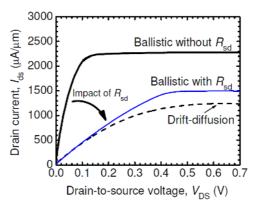

| Figure 3-13 Mean free path ( $\lambda$ ) as a function of $L_{\rm eff}$ for NMOS transistor [3.18]. Constant gate             |

| overdrive of 1.1 V is used. The drain bias is 10 mV46                                                                         |

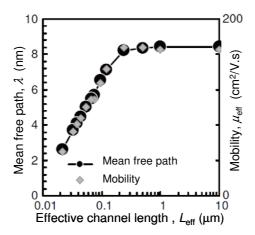

| Figure 3-14 Mobility degradation with $L_{\rm eff}$ is observed in NMOS transistors without halo implants                     |

| [3.20]                                                                                                                        |

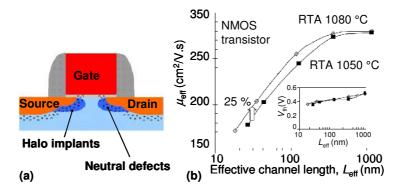

| Figure 3-15(a) Schematics of neutral defects near S/D regions , (b) Neutral defects recovery by                               |

| increasing the rapid thermal anneal (RTA) temperature [3.20]47                                                                |

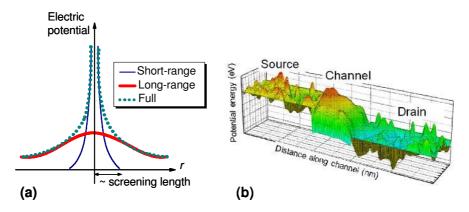

| Figure 3-16 Role of long-range Coulomb scattering in nanoscale MOS transistor: (a) Region of                                  |

| influence, (b) Potential fluctuations in the S/D regions [3.22]. Note that $r$ is the distance between the                    |

| channel carrier and the scattering ion47                                                                                      |

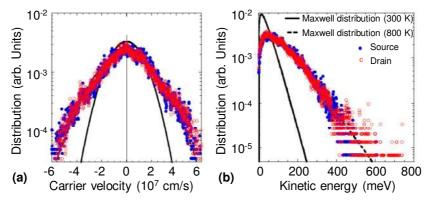

| Figure 3-17 The effective electron temperature in the S/D regions is at 800 K rather than the                                 |

| ambient temperature of 300 K: (a) the carrier velocity distribution, (b) the kinetic energy                                   |

| distribution at location close to the source and drain contacts [3.22]47                                                      |

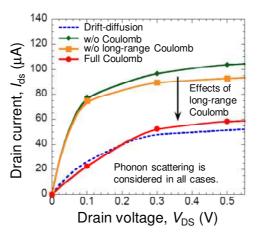

| Figure 3-18 Effects of the long-range Coulomb scattering on the $I_{ds}$ versus $V_{DS}$ characteristics of a                 |

| nanoscale NMOS transistor [3.22]                                                                                              |

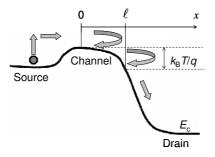

| Figure 3-19 Definition of the critical length ( $\ell$ ) for NMOS transistor [1.25]                                           |

| Figure 3-20 The average electric field, $\varepsilon(0^+)$ is a function of (a) $V_{GS}$ and (b) $V_{DS}$ [1.25]49            |

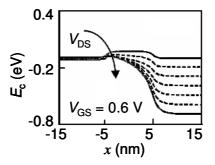

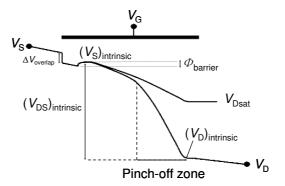

| Figure 3-21 Schematics of the potential profile along the channel length of a NMOS transistor under                           |

| quasi-ballistic transport [3.26]. $\Delta V_{\text{overlap}}$ is the drop in potential in the source series resistance and    |

| the accumulation region under the source-to-gate overlap. $(V_s)_{intrinsic}$ and $(V_D)_{intrinsic}$ are the intrinsic       |

| source bias and the intrinsic drain bias, respectively. $\varPhi_{\text{barrier}}$ is the potential barrier at the source-    |

| channel                                                                                                                       |

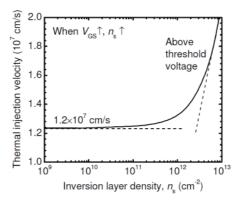

| Figure 3-22 The thermal injection velocity ( $\tilde{v}_T$ ) versus the inversion layer density ( $n_s$ ) [1.25]. For                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{\rm GS}$ below threshold voltage, $\tilde{v}_{\rm T} \approx 1.2 \times 10^{-7}$ cm/s. For $V_{\rm GS}$ above threshold voltage, the channel                       |

| carriers become degenerate and $\tilde{v}_{\rm T}$ increases                                                                                                           |

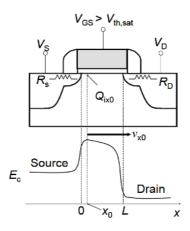

| Figure 3-23 Illustration of the virtual source point $(x_0)$ in the NMOS transistor. $Q_{ixo}$ and $v_{xo}$ are                                                        |

| defined at the top of the conduction band profile along the channel direction. [1.28]                                                                                  |

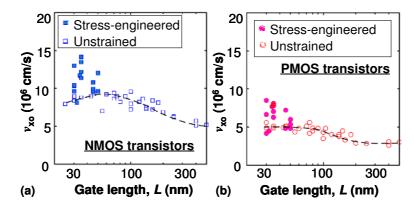

| Figure 3-24 Extracted virtual source velocity ( $v_{xo}$ ) as a function of the gate length for (a) NMOS                                                               |

| transistors, (b) PMOS transistors that are fabricated on (100) Si wafer with <110> channel                                                                             |

| orientation [1.27]. Stress engineering can increase $v_{xo}$ to beyond $v_{sat}$                                                                                       |

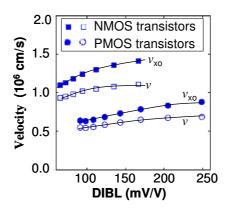

| Figure 3-25 Extracted virtual source velocity ( $v_{xo}$ ) and effective carrier velocity ( $v$ ) versus DIBL for                                                      |

| the nanoscale NMOS transistors and PMOS transistors [1.27]                                                                                                             |

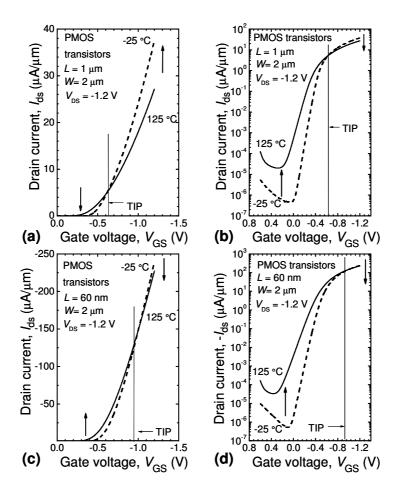

| Figure 3-26 Temperature independent point (TIP) of the long-channel PMOS transistor with                                                                               |

| nominal gate length of 1 $\mu$ m (a, b), and the short-channel PMOS transistor with nominal gate length                                                                |

| of 60 nm (c,d). V <sub>DD</sub> is -1.2                                                                                                                                |

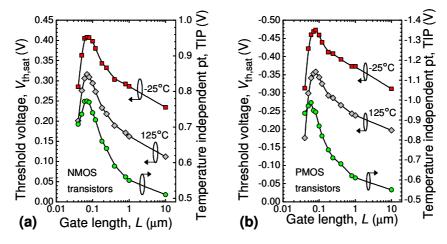

| Figure 3-27 Gate length dependency of temperature independent point (TIP) for (a) NMOS                                                                                 |

| transistor, (b) PMOS transistor. $V_{DD}$ is 1.2 V                                                                                                                     |

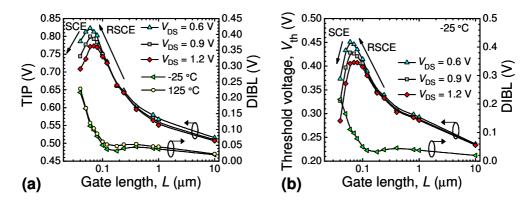

| Figure 3-28 NMOS transistors (fabricated by 65 nm CMOS technology) in the SCE regime: (a) TIP                                                                          |

| decreases with increasing $V_{\text{DS}}$ , (b) $V_{\text{th}}$ decreases with increasing $V_{\text{DS}}$ . Note that DIBL = $V_{\text{th,lin}} - V_{\text{th,sat}}$ . |

|                                                                                                                                                                        |

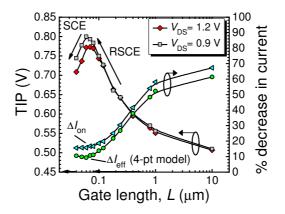

| Figure 3-29 Temperature sensitivity in $I_{on}$ and $I_{eff}$ of NMOS transistors as a function of L                                                                   |

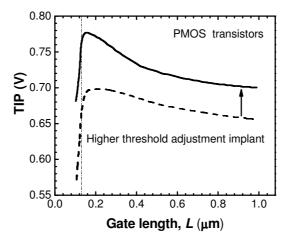

| Figure 3-30 Simulation shows that threshold adjustment implant can increase TIP [3.34]56                                                                               |

| Figure 3-31 Effects of $R_{sd}$ on $E_c$ of a NMOS transistor in saturation operation                                                                                  |

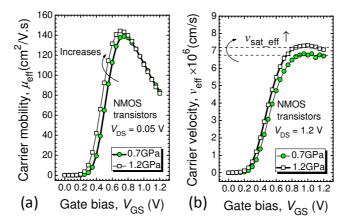

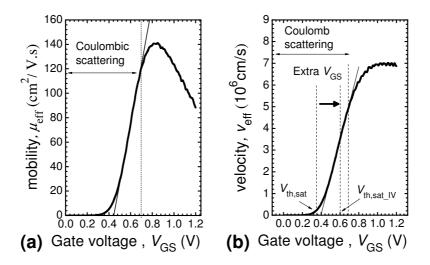

| Figure 3-32 Effects of CESL-induced tensile stress on: (a) $\mu_{eff}$ versus $V_{GS}$ characteristics, (b) $v_{eff}$                                                  |

| versus $V_{GS}$ characteristics of a NMOS transistor with nominal gate length of 60 nm. The drain bias                                                                 |

| is 1.2 V                                                                                                                                                               |

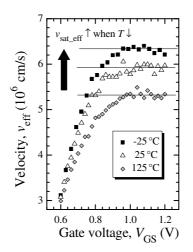

| Figure 3-33 Effects of temperature on $v_{sat_{eff}}$ and $v_{eff}$ of a NMOS transistor with nominal gate length                                                      |

| of 60 nm. Note that $v_{\text{sat}_{eff}}$ refers to the average value of $v_{eff}$ when $V_{GS}$ is close to $V_{DD}$ 60                                              |

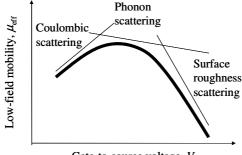

| Figure 3-34 Effects of the scattering mechanism on the $\mu_{eff}$ versus $V_{GS}$ characteristics                                                                     |

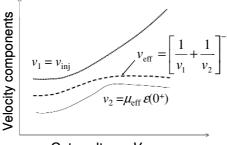

| Figure 3-35 Schematic diagram showing the relationship of $v_1$ , $v_2$ and $v_{eff}$ with $V_{GS}$                                                                    |

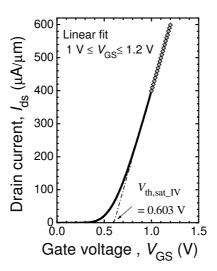

| Figure 3-36 Extraction of $V_{\text{th,sat_IV}}$ from the saturation $I_{\text{ds}}$ versus $V_{\text{GS}}$ characteristics                                            |

| Figure 3-37 $V_{\text{th,sat_IV}}$ includes a component to overcome the Coulombic scattering by "screening":                                                           |

| (a) $\mu_{\rm eff}$ versus $V_{\rm GS}$ characteristics, (b) $v_{\rm eff}$ versus $V_{\rm GS}$ characteristics of a NMOS transistor with a                             |

| nominal gate length of 60 nm                                                                                                                                           |

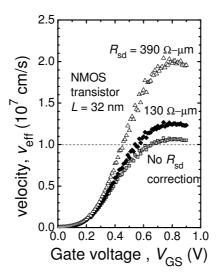

| Figure 3-38 Effects of $R_{sd}$ correction on $v_{sat_{eff}}$ of a nanoscale NMOS transistor at room temperature.                                                      |

|                                                                                                                                                                        |

|                                                                                                                                                                        |

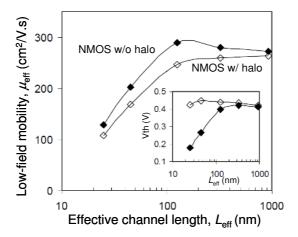

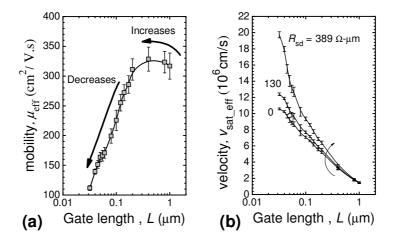

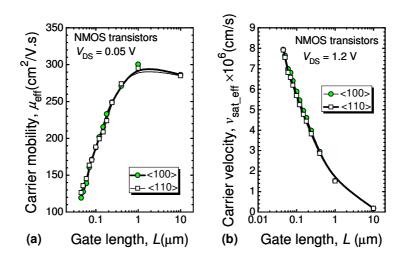

| Figure 3-39 Effects of transistor scaling on (a) the $\mu_{\rm eff}$ versus L characteristics and (b) the $v_{\rm sat_eff}$                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| versus L characteristics of NMOS transistors. $R_{sd} = 0 \Omega$ -µm refers to the case where the S/D series                                                    |

| resistance correction is not performed                                                                                                                           |

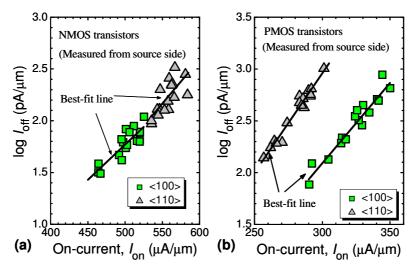

| Figure 4-1 The use of the log $I_{off}$ versus $I_{on}$ plot of NMOS transistors to assess the amount of $I_{on}$                                                |

| improvement by stress engineering [1.42]                                                                                                                         |

| Figure 4-2 Validity of the linearity assumption in the log $I_{off}$ versus $I_{on}$ plot for NMOS transistor                                                    |

| [1.39]                                                                                                                                                           |

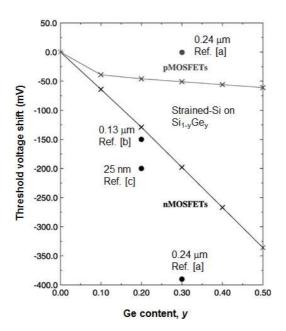

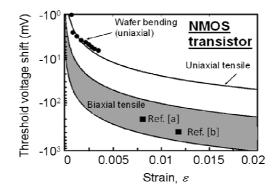

| Figure 4-3 Biaxial tensile stress leads to negative threshold voltage shifts in<110> MOS transistors                                                             |

| on (100) Si [4.1]                                                                                                                                                |

| Figure 4-4 Uniaxial tensile stress and biaxial tensile stress lead to negative threshold voltage shift in                                                        |

| <110> NMOS transistors on (100) Si [4.2]70                                                                                                                       |

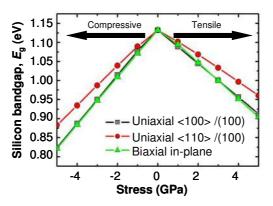

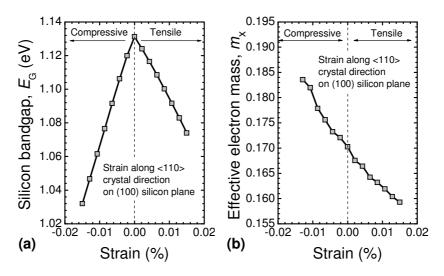

| Figure 4-5 Effects of mechanical stress on the silicon bandgap of (100) Si[4.4]70                                                                                |

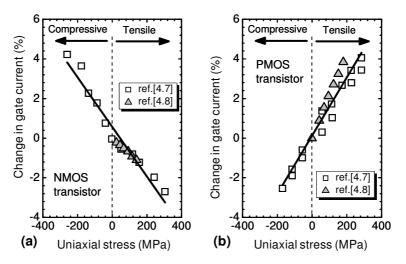

| Figure 4-6 The effects of uniaxial stress on gate tunneling current of <110> MOS transistors on                                                                  |

| (100) Si surface[4.7,4.8]73                                                                                                                                      |

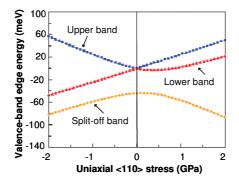

| Figure 4-7 Valence band edge energy as a function of the uniaxial <110> stress [2.86]                                                                            |

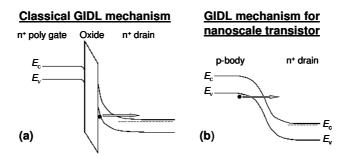

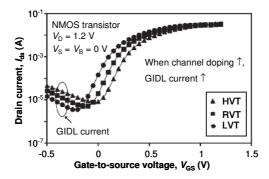

| Figure 4-8 (a) Classical GIDL mechanism, (b) New GIDL mechanism[4.9]74                                                                                           |

| Figure 4-9 Effects of threshold adjustment implant on the GIDL current of a nanoscale NMOS                                                                       |

| transistor ( $L = 40 \text{ nm}$ )[4.9]. HVT: High dose, RVT: Regular dose, LVT: Low dose74                                                                      |

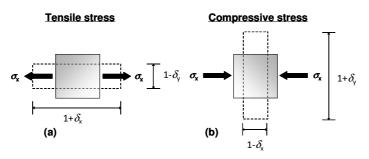

| Figure 4-10 Effects of Poisson's ratio under (a) tensile stress, (b) compressive stress [4.11]75                                                                 |

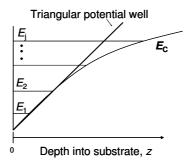

| Figure 4-11 Triangular potential well approximation77                                                                                                            |

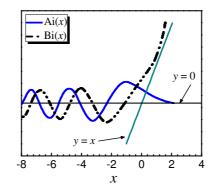

| Figure 4-12 Graphical representation of Airy functions, Ai( <i>x</i> ) and Bi( <i>x</i> ) [4.19]78                                                               |

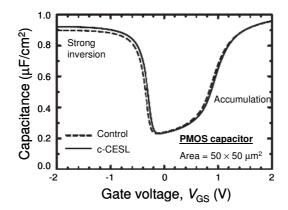

| Figure 4-13 Effects of compressive stress on the C-V characteristics of PMOS capacitor [4.25]79                                                                  |

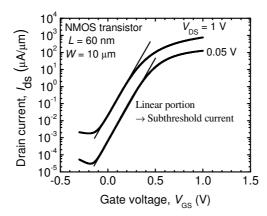

| Figure 4-14 Subthreshold current is taken to be the linear portion of log $I_{\rm ds}$ versus $V_{\rm GS}$                                                       |

| characteristics of NMOS transistor                                                                                                                               |

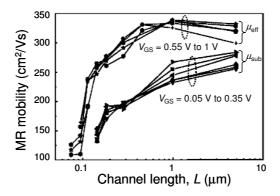

| Figure 4-15 Magnetoresistance (MR) mobility measurements show that there is a correlation                                                                        |

| between $\mu_{sub}$ and $\mu_{eff}$ [4.29]81                                                                                                                     |

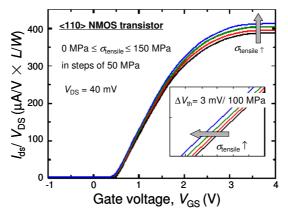

| Figure 4-16 Effects of externally applied tensile stress on the $I_{ds}$ versus $V_{GS}$ characteristics of a                                                    |

| relatively long NMOS transistor with 4 nm conventional gate dielectric [4.30]. Inset shows the                                                                   |

| threshold voltage shift in the subthreshold regime                                                                                                               |

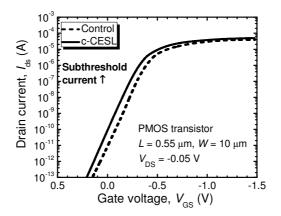

| Figure 4-17 Effects of CESL-induced compressive stress on the subthreshold current of <110>                                                                      |

| PMOS transistor with $L = 0.55 \mu\text{m}$ and $W = 10 \mu\text{m}$ [4.25]81                                                                                    |

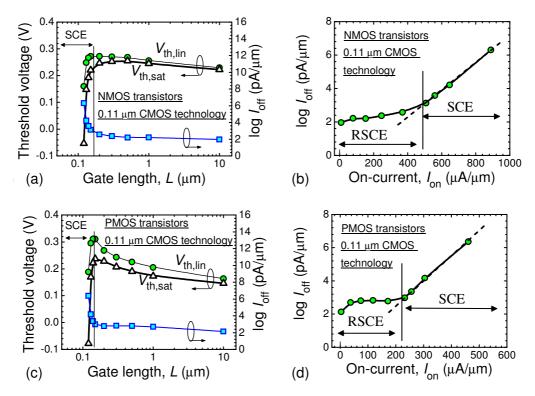

| Figure 4-18 Linearity of $\log I_{off}$ versus $I_{on}$ plot is valid for the short channel effect (SCE) regime of                                               |

| transistors fabricated by 0.11 $\mu m$ CMOS technology. (a) & (b) refer to NMOS transistors. (c) & (d)                                                           |

| refer to PMOS transistors                                                                                                                                        |

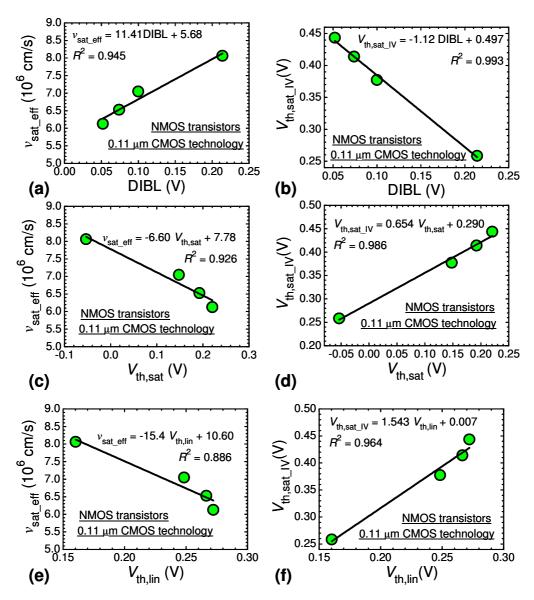

| Figure 4-19 For NMOS transistors in the SCE regime: (a) $v_{sat_{eff}}$ has a good linearity with DIBL, (b)                                                      |

| $V_{\text{th,sat_IV}}$ has a good linearity with DIBL, (c) $v_{\text{sat_eff}}$ has a good linearity with $V_{\text{th,sat}}$ , (d) $V_{\text{th,sat_IV}}$ has a |

| good linearity with $V_{\text{th,sat}}$ , (e) $v_{\text{sat}_{eff}}$ has a good linearity with $V_{\text{th,lin}}$ , (f) $V_{\text{th,sat}_{IV}}$ has a good linearity    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| with V <sub>th,lin</sub>                                                                                                                                                  |

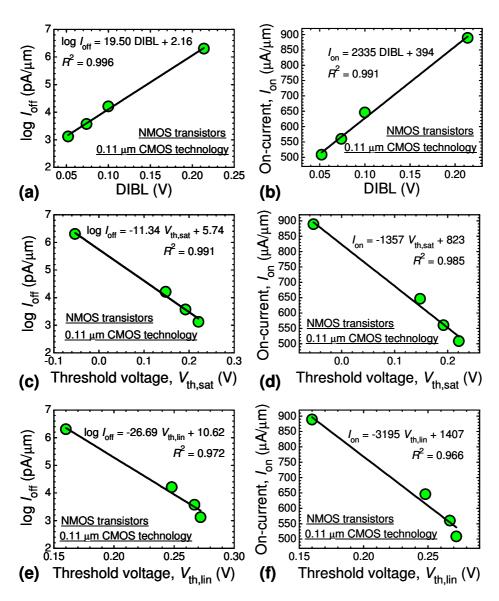

| Figure 4-20 Third parameter in the log $I_{off}$ versus $I_{on}$ characteristics of NMOS transistors in SCE                                                               |

| regime: (a) and (b) show that DIBL has a linear relationship with log $I_{off}$ and $I_{on}$ . (c) and (d) show                                                           |

| that $V_{\text{th,sat}}$ has a linear relationship with log $I_{\text{off}}$ and $I_{\text{on}}$ . (e) and (f) show that $V_{\text{th,lin}}$ has a linear                 |

| relationship with log $I_{\text{off}}$ and $I_{\text{on}}$                                                                                                                |

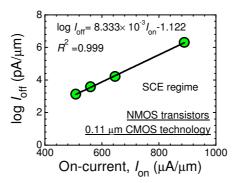

| Figure 4-21 Best-fit line of the log $I_{off}$ versus $I_{on}$ plot of NMOS transistors in the SCE regime87                                                               |

| Figure 4-22 Linearity of log $I_{off}$ versus $I_{on}$ characteristics of NMOS transistors in SCE regime (65                                                              |

| nm CMOS technology)                                                                                                                                                       |

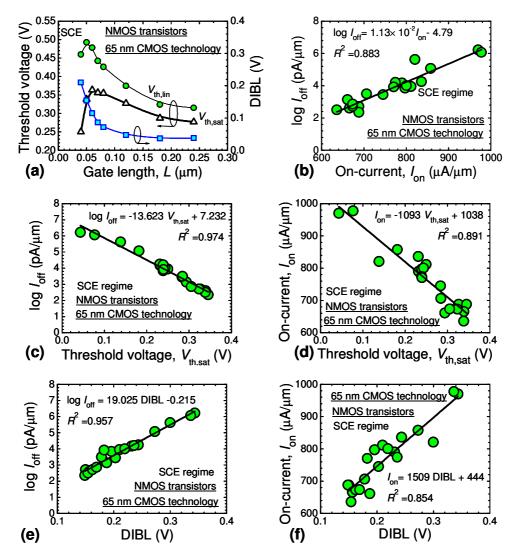

| Figure 4-23 Linearity of the log $I_{off}$ versus $I_{on}$ characteristics may not be valid for PMOS transistors                                                          |

| that are fabricated by 45 nm CMOS technology: (a) Anomalous increase in the threshold voltage,                                                                            |

| (b) Kink in the $I_{ds_on}$ versus L characteristics, (c) Kink in the $I_{ds_off}$ versus L characteristics, (d) Poor                                                     |

| linearity in SCE regime                                                                                                                                                   |

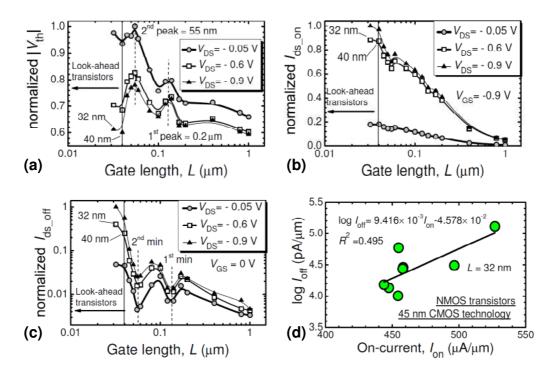

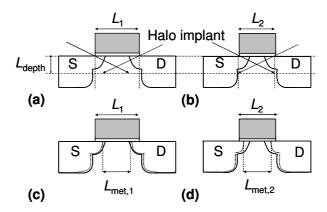

| Figure 4-24 Mechanism responsible for the poor linearity in log $I_{off}$ versus $I_{on}$ plot of PMOS                                                                    |

| transistors fabricated by 40nm CMOS technology. (a) & (c) refer to the case for the onset of the                                                                          |

| cross-over of halo implants. (b) & (d) refer to the case for the cross over of halo implants                                                                              |

| Figure 4-25 The effects of uniaxial stress on (a) the silicon bandgap and (b) the effective electron                                                                      |

| mass along the channel direction ( <i>m</i> <sub>x</sub> )91                                                                                                              |

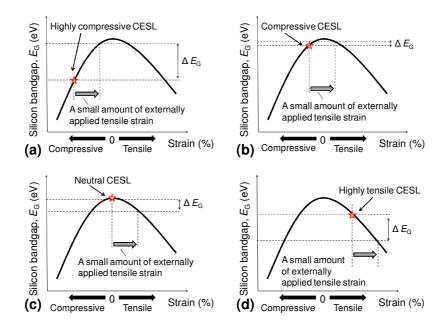

| Figure 4-26 Effects of a "mechanical stress bias" in MOS transistor on the sensitivity of the silicon                                                                     |

| bandgap to a small amount of externally applied tensile stress: (a) highly compressively stressed                                                                         |

| CESL, (b) low compressive stressed CESL, (c) highly tensile stressed CESL                                                                                                 |

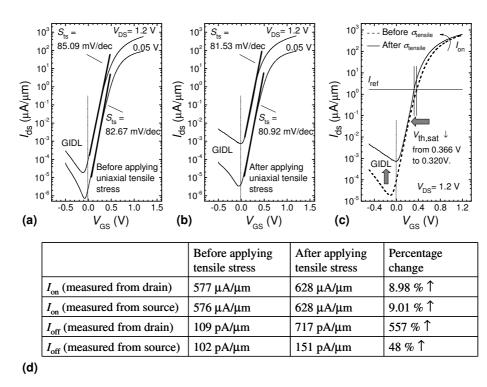

| Figure 4-27 Effects of the externally applied uniaxial tensile stress on <110> channel NMOS                                                                               |

| transistor fabricated on (100) Si substrate with 0.7 GPa tensile stressed CESL92                                                                                          |

| Figure 4-28 Effects of the externally applied uniaxial tensile stress on <110> channel PMOS                                                                               |

| transistor on (100) Si substrate with 0.7 GPa tensile stressed CESL                                                                                                       |

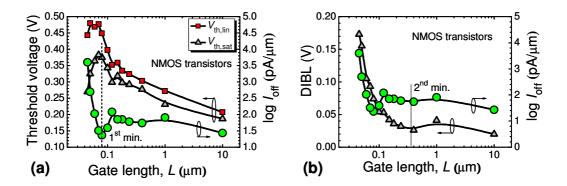

| Figure 4-29 Region of nearly constant $I_{\text{off}}$ for NMOS transistors fabricated by 65 nm CMOS                                                                      |

| technology: (a) Maximum V <sub>th,sat</sub> , (b) Minimum DIBL95                                                                                                          |

| Figure 4-30 Region of nearly constant $I_{off}$ for PMOS transistors fabricated by 65 nm CMOS                                                                             |

| technology: (a) Maximum V <sub>th,sat</sub> , (b) Minimum DIBL                                                                                                            |

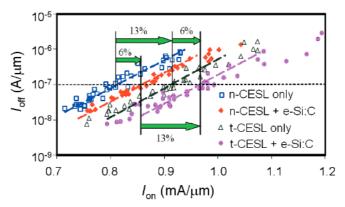

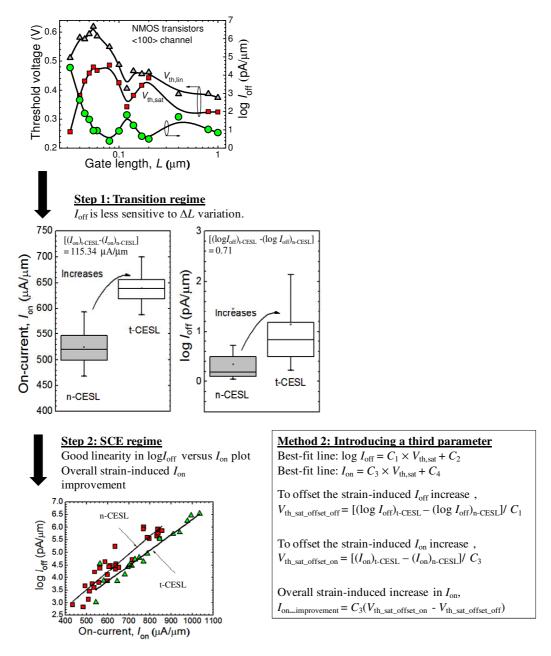

| Figure 4-31 Overall strain-induced I <sub>on</sub> improvement in <110> NMOS transistors                                                                                  |

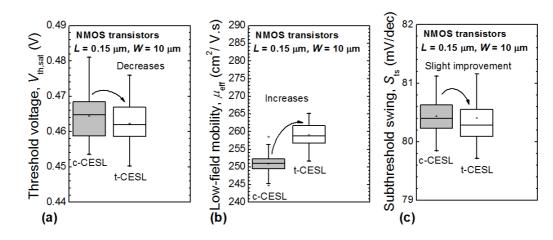

| Figure 4-32 The effects of CESL-induced tensile stress on: (a) $V_{\text{th,sat}}$ , (b) $\mu_{\text{eff}}$ , (c) $S_{\text{ts}}$ of NMOS                                 |

| transistors in the transition between SCE regime and RSCE regime                                                                                                          |

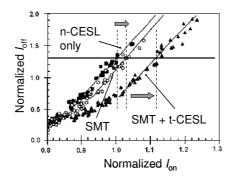

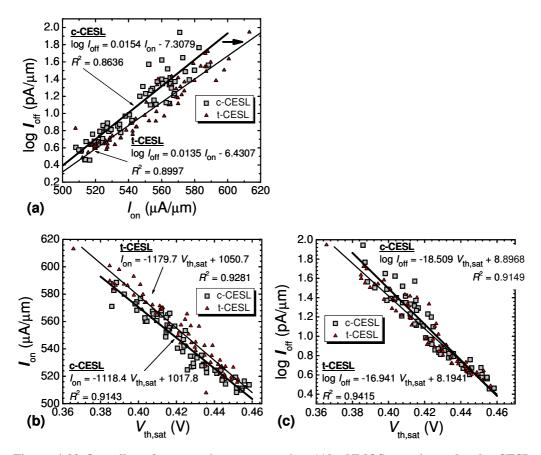

| Figure 4-33 Overall performance improvement in <110> NMOS transistors by the CESL-induced                                                                                 |

| tensile stress: (a) log $I_{\text{off}}$ versus $I_{\text{on}}$ characteristics, (b) $I_{\text{on}}$ versus $V_{\text{th,sat}}$ characteristics, (c) log $I_{\text{off}}$ |

| versus $V_{\text{th,sat}}$ characteristics                                                                                                                                |

| Figure 4-34 Overall strain-induced <i>I</i> <sub>on</sub> improvement in <100> NMOS transistors                                                                           |

|                                                                                                                                                                           |

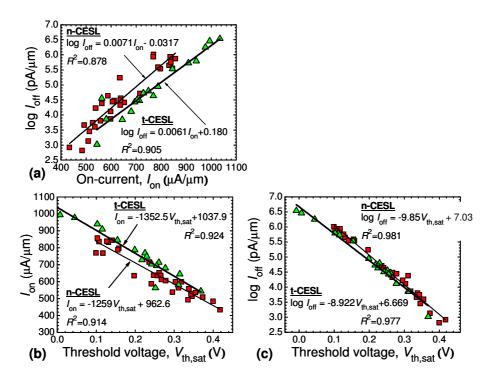

| Figure 4-35 Overall performance improvement in <100> NMOS transistors by CESL-induced                                                |

|--------------------------------------------------------------------------------------------------------------------------------------|

| tensile stress: (a) the log $I_{off}$ versus $I_{on}$ characteristics, (b) the $I_{on}$ versus $V_{th,sat}$ characteristics, and (c) |

| the log $I_{\text{off}}$ versus $V_{\text{th,sat}}$ characteristics                                                                  |

| Figure 5-1 Switching in channel orientation increases hole mobility[1.32]                                                            |

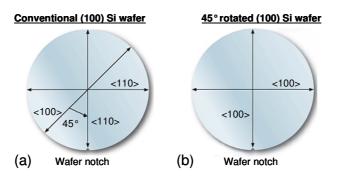

| Figure 5-2 Schematics of the (a) conventional (100)Si, (b) 45° rotated (100)Si103                                                    |

| Figure 5-3 Effects of channel orientation on the effective hole mass of (100)Si[1.34]104                                             |

| Figure 5-4 Effects of channel orientation increases I <sub>on</sub> of PMOS transistors on (100)Si [1.33]104                         |

| Figure 5-5 Calculations of the effective conductivity electron mass $(m^*)$ : (a) 45° rotated (100)Si, (b)                           |

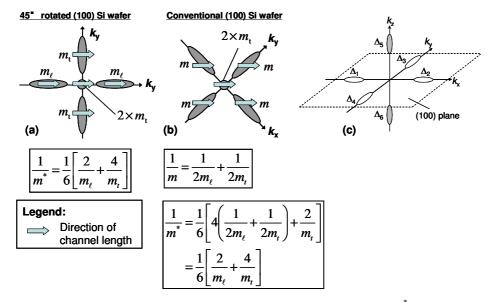

| conventional (100) Si [1.34], (c) conduction band valleys on (100)Si plane105                                                        |

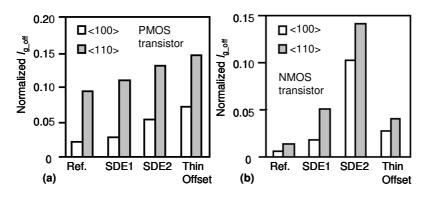

| Figure 5-6 The effects of channel orientation on $I_{g_{off}}$ of: (a) PMOS transistors, (b) NMOS                                    |

| transistors on (100) Si [1.33]. S/D extension implant dose: Ref = Thin Offset = SDE1 < SDE2.                                         |

| Thickness of the gate offset spacer: Ref = SDE1 = SDE2 > Thin Offset109                                                              |

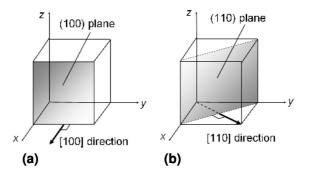

| Figure 5-7 For cubic crystal structure such as silicon, (a) [100] direction is perpendicular to (100)                                |

| plane, (b) [110] direction is perpendicular to (110) plane [5.15]110                                                                 |

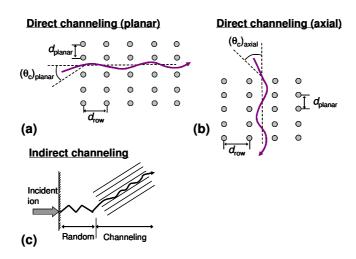

| Figure 5-8 Various types of ion channeling : (a) planar channeling, (b) axial channeling, (c) indirect                               |

| channeling [5.18]                                                                                                                    |

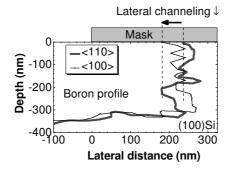

| Figure 5-9 Monte Carlo simulation of the two-dimensional implanted boron distribution into (100)                                     |

| Si at a mask edge [5.19]111                                                                                                          |

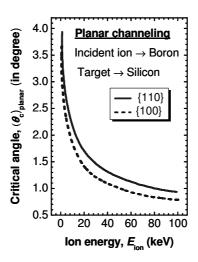

| Figure 5-10 Critical angle for planar channeling along {110} plane and {100} plane as a function of                                  |

| the incident ion energy [5.22]113                                                                                                    |

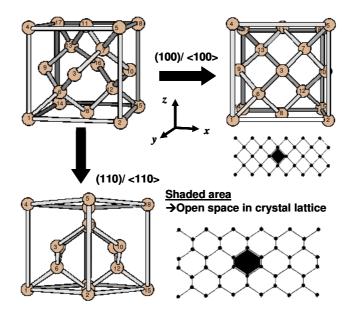

| Figure 5-11 Arrangements of the silicon atoms in (100) Si and (110) Si that are viewed along the                                     |

| direction normal to the plane [5.20, 5.21]113                                                                                        |

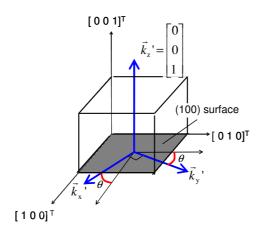

| Figure 5-12 $\Re_{E \leftarrow D}$ of (100) Si for a generalized channel orientation                                                 |

| Figure 5-13 (a) Schematics of the six conduction band valleys of (100) Si, (b) Validity of the six                                   |

| degenerate ellipsoid model for the conduction band energy minimum of silicon at the interface                                        |

| between SiO <sub>2</sub> /Si interface                                                                                               |

| Figure 5-14-Difference between lateral ion channeling and axial channeling119                                                        |

| Figure 5-15 Evidence of the increase in $L_{\rm eff}$ of <100> MOS transistors on (100) Si after a change in                         |

| the channel orientation. Note that $DIBL = V_{th,lin} - V_{th,sat}$                                                                  |

| Figure 5-16 The ease of lateral ion channeling for arsenic and boron along <100> direction and                                       |

| <110> direction of (100)Si                                                                                                           |

| Figure 5-17 Effects of the change in channel orientation on the log $I_{off}$ versus $I_{on}$ plot of NMOS                           |

| transistors (b) PMOS transistors on (100)Si. ( $L = 60 \text{ nm}$ , $W = 1 \mu \text{m}$ )                                          |

| Figure 5-18 Effects of the change in the channel orientation on $\mu_{eff}$ and $v_{sat_eff}$ of NMOS transistors                    |

| on (100) Si                                                                                                                          |

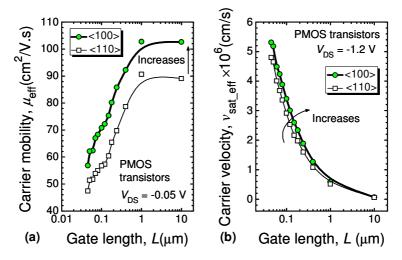

| Figure 5-19 Effects of the change in the channel orientation on $\mu_{eff}$ and $v_{sat_{eff}}$ of PMOS transistors                  |

| on (100) Si                                                                                                                          |

|                                                                                                                                      |

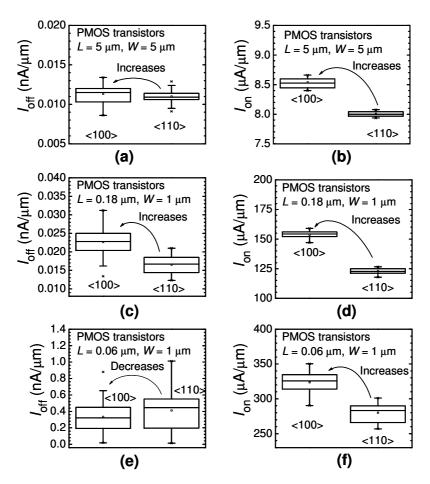

| Figure 5-20 Effects of switching from the conventional <110> channel orientation to <100> channel                 |

|-------------------------------------------------------------------------------------------------------------------|

| orientation on the I <sub>on</sub> and I <sub>off</sub> of NMOS transistors on (100)Si                            |

| Figure 5-21 Effects of switching from the conventional <110> channel orientation to <100> channel                 |

| orientation on the I <sub>on</sub> and I <sub>off</sub> of PMOS transistors on (100)Si124                         |

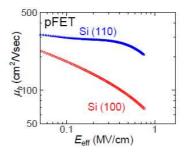

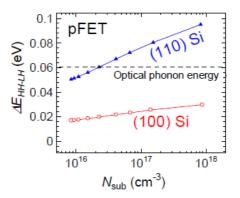

| Figure A-1 Higher hole mobility ( $\mu_h$ ) as a function of the effective vertical field ( $E_{eff}$ ) for <110> |

| PMOS transistors fabricated on (100)Si and (110)Si[A.1]132                                                        |

| Figure A-2 Energy split ( $\Delta E_{\text{HH-LH}}$ ) in PMOS transistors on (100)Si and (110)Si [A.1]132         |

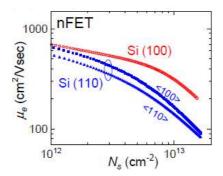

| Figure A-3 Electron mobility ( $\mu_e$ ) as a function of the surface carrier concentration ( $N_s$ ) for NMOS    |

| transistors on (100)Si and (110)Si [A.1]132                                                                       |

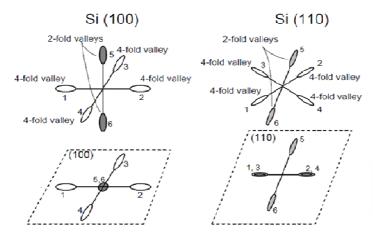

| Figure A-4 Conduction band valleys on (100) plane and (110) plane [A.1]133                                        |

### LIST OF TABLES

| Table 2-1 Components of the piezoresistive tensor of bulk silicon (units: 10 <sup>-11</sup> Pa <sup>-1</sup> ) [2.74]                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-2 Device-level piezoresistance coefficients of the MOS transistors fabricated on (100)                                              |

| surface-oriented silicon wafer (units: 10 <sup>-11</sup> Pa <sup>-1</sup> )                                                                 |

| Table 3-1 Merits and limitations of various drain current transport theories for the nanoscale MOS                                          |

| transistors                                                                                                                                 |

| Table 4-1 Evaluation of the suitability of the third parameter in the log $I_{off}$ versus $I_{on}$ plot                                    |

| Table 4-2 Comparison between various stress engineering techniques                                                                          |

| Table 4-3 Method 1 to ascertain the overall strain-induced $I_{on}$ improvement of <110> NMOS                                               |

| transistors                                                                                                                                 |

| Table 4-4 Method 2 to ascertain the overall strain-induced $I_{on}$ improvement of <110> NMOS                                               |

| transistor using $V_{\text{th,sat}}$ as a third parameter in the log $I_{\text{off}}$ versus $I_{\text{on}}$ plot                           |

| Table 4-5 Overall performance improvement for <100> channel NMOS transistor by stress                                                       |

| engineering when we consider $V_{\text{th,sat}}$ as the third parameter in the log $I_{\text{off}}$ versus $I_{\text{on}}$ characteristics. |

|                                                                                                                                             |

| Table 5-1 The area of open space $(A_{open_space})$ in the silicon crystal lattice for various surface                                      |

| orientation and crystal directions [5.20]112                                                                                                |

| Table A-1: Effects of surface orientation and channel orientation on the effective electron masses                                          |

| along the quantum confinement direction ( <i>m</i> <sub>z</sub> ) [5.2]133                                                                  |

| Table A-2 Device-level piezoresistance coefficients of the <110> NMOS transistors fabricated on                                             |

| (100)Si and (110)Si (units: 10 <sup>-11</sup> Pa <sup>-1</sup> ) [2.41]                                                                     |

### 1. Introduction

### 1.1 Background

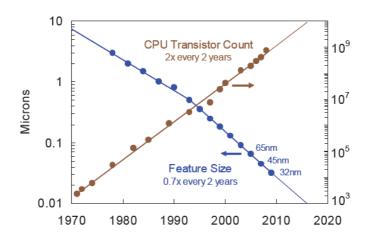

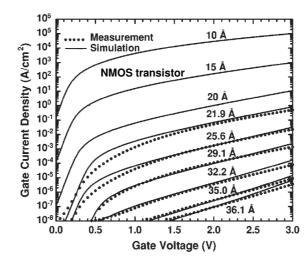

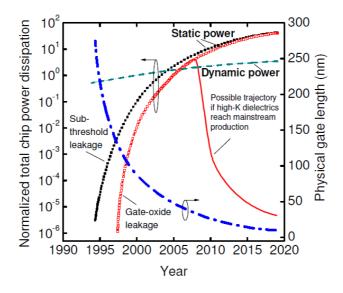

For the past 40 years, relentless focus on Moore's law scaling has provided everincreasing switching speed and packing density in the metal-oxide-semiconductor (MOS) transistor, as illustrated in Fig.1-1 [1.1]. Traditionally, the tradeoffs between the three main indices of transistor performance, which are the on-current  $(I_{on})$ , the short-channel effect (SCE) and the power consumption, can be achieved by simply scaling the thickness of the silicon oxynitride-based gate dielectrics. However, it has been recognized that this conventional scaling has confronted difficulties in the sub-100 nm regime because the gate-oxide leakage current will become excessively large when the physical gate oxide thickness reaches 1.5 nm, as shown in Fig.1-2 [1.2]. From the perspective of the total chip power consumption, the static power dissipation is expected to dominate over the dynamic power dissipation in the nanoscale MOS transistors, as shown in Fig.1-3 [1.3]. Owing to the large increase in the gate leakage for very thin silicon oxynitride-based gate dielectrics, there will be significant increase static power dissipation, leading to a large increase in the total chip power dissipation. Hence, performance enhancement techniques such as mobility enhancement techniques, high-k dielectrics and metal gates [1.4] have been explored to sustain the performance scaling trends. This work will focus on the mobility enhancement techniques rather than the high-k gate dielectric with metal gates.

Figure 1-1 Moore's Law: CPU transistor count has increased by two times and feature size has decreased by 0.7 times in every two years [1.1].

Figure 1-2 Excessive gate-oxide leakage occurs with further scaling of the conventional silicon oxynitride gate dielectric [1.2].

Figure 1-3 Total chip dynamic and static power dissipation trends based on the International Technology Roadmap for Semiconductor (ITRS) [1.3].

### 1.2 Roles of carrier mobility in drain current transport

The drift-diffusion model is typically associated with the long-channel MOS transistors. The drain current ( $I_{ds}$ ) comprises the diffusion current ( $I_{diff}$ ) and the drift current ( $I_{drift}$ ). When the gate bias ( $V_{GS}$ ) is smaller than the threshold voltage,  $I_{ds}$  is dominated by  $I_{diff}$ . When the  $V_{GS}$  is bigger than the threshold voltage,  $I_{ds}$  is dominated by  $I_{diff}$ . The equation for the saturation drain current ( $I_{ds}$ ) of a long-channel MOS transistor [1.5],

$$I_{\rm ds} = \mu_{\rm eff} C_{\rm ox,inv} \frac{W}{2L} (V_{\rm GS} - V_{\rm th,sat})^2$$

(1.1)

where  $\mu_{\text{eff}}$  is the low-field mobility.  $C_{\text{ox,inv}}$  is the gate oxide capacitance at strong inversion per unit area. W is the gate width. L is the gate length.  $V_{\text{th,sat}}$  is the saturation threshold voltage.

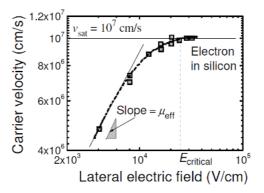

On the other hand, velocity saturation [1.6-1.10] is often associated with the nanoscale MOS transistors. It is based on the balance of energy equation for channel carriers: the rate of energy gained from the lateral electric field is equal to the rate of energy dissipation through the emission of longitudinal optical phonons [1.7]. For nanoscale MOS transistor in velocity saturation [1.6],

$$I_{\rm ds} = v_{\rm sat} C_{\rm ox,inv} W (V_{\rm GS} - V_{\rm th,sat})$$

(1.2)

where  $v_{sat}$  is the saturation velocity. Based on the time-of-flight measurement,  $v_{sat}$  for electrons in silicon is  $10^7$  cm/s while  $v_{sat}$  for holes in silicon is  $6 \times 10^6$  cm/s at a temperature of 300 K [1.9]. According to the theoretical predictions,  $v_{sat}$  is independent of  $\mu_{eff}$  [1.10]. From eqn. (1.2), the velocity saturation model predicts that mobility enhancement will not improve  $I_{on}$  of nanoscale MOS transistor.

However, this is contradictory to the experimental observations of strained-induced  $I_{on}$  improvement in the nanoscale MOS transistors [1.11-1.13]. Furthermore, Monte Carlo simulation by Ruch [1.16] and Mizuno et al. [1.17] showed that the velocity overshoot can occur in the nanoscale MOS transistors. In addition, the Monte Carlo simulation by Miyata et al. [1.18] showed that velocity overshoot can be further increased by the application of mechanical stress. In fact, Kim et al. has reported their experimental observation of electron velocity overshoot in bulk n-channel MOS (NMOS) transistors at room temperature [1.19].

Ballistic transport [1.20-1.23], which is associated with nanoscale MOS transistors, considers an ideal situation where the channel carrier does not undergo any scattering.

Since mobility is a concept that involved scattering, ballistic transport actually disregards  $\mu_{\text{eff}}$  in the nanoscale MOS transistors [1.20-1.23] and thus cannot account for the straininduced  $I_{\text{on}}$  improvement in nanoscale MOS transistors.

In the quasi-ballistic transport [1.24, 1.25], the channel carriers will experience some scatterings when it moves from the source to the drain but the number of channel scatterings is much smaller than that of the velocity saturation model. Since mobility is a concept that involved scattering, quasi-ballistic transport considers the effects of  $\mu_{eff}$  and thus can account for the strain-induced  $I_{on}$  improvement in nanoscale MOS transistor [1.11-1.13]. However, there are some terms in the drain current equation for the quasi-ballistic transport that are not properly defined.

Low-field mobility,  $\mu_{\rm eff}$  (cm<sup>2</sup>/V.s)

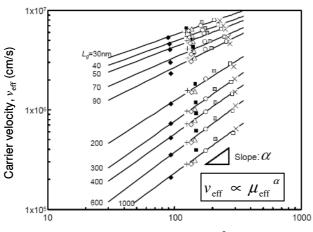

Figure 1-4 Experimental correlation between low-field mobility ( $\mu_{eff}$ ) and the high-field carrier velocity ( $\nu_{eff}$ ) for the nanoscale NMOS transistors [1.29].

At this point, it may seem that quasi-ballistic transport is the most appropriate model for nanoscale MOS transistor. However, some researchers have managed to use the conventional velocity saturation model to fit the experimental saturation drain current ( $I_{ds}$ ) of the nanoscale MOS transistors. In the physics-based model for MOS transistors developed by Hauser [1.26],  $v_{sat}$  is treated as a fitting parameter that can be increased to  $2.06 \times 10^7$  cm/s so as to fit the experimental  $I_{ds}$  versus the drain-to-source voltage ( $V_{DS}$ ) characteristics of the nanoscale NMOS transistor. Although this approach is conceptually wrong, this can avoid detailed discussion in velocity overshoot and quasi-ballistic transport. Furthermore, Khakifirooz et al. introduced a semi-empirical model for the saturation drain current of the nanoscale MOS transistor that is based on the sheet charge approximation [1.27, 1.28]. In addition, Tatsumura et al. [1.29] has performed an extensive experimental study to show that there is indeed a correlation between the low-field mobility and the high-field carrier velocity, as shown in Fig. 1-4. Hence, there is a need to further clarify the drain current transport of the nanoscale MOS transistor.

### **1.3** Mobility enhancement techniques

In view of the increasing cost and complexities involved in the scaling of MOS transistors, the semiconductor industry uses mobility enhancement techniques to improve transistor performance. From Fig. 1-5, the mobility enhancement techniques can be categorized into the substrate-induced stress and the process-induced stress [1.30]. The use of biaxial tensile stressed silicon on relaxed Si<sub>1-y</sub>Ge<sub>y</sub> virtual substrate [1.11, 1.31], will increase the mobilities of both NMOS transistors and p-channel MOS (PMOS) transistors. The use of 45° rotated (100) surface-oriented silicon instead of the conventional (100) surface-oriented silicon increases the hole mobility [1.32, 1.33] but does not affect the electron mobility [1.34]. Since the change in the channel orientation results in the mechanical insensitivity of <100> PMOS transistors [1.35, 1.36], stress engineering techniques cannot be used to improve  $I_{on}$  of <100> PMOS transistors. However, this unique property of <100> PMOS transistor will allow us to use a single tensile contact etch stop layer (CESL) over both <100> NMOS transistors and <100> PMOS transistors without degrading Ion of PMOS transistors. For Hybrid-Orientation Technology (HOT), PMOS transistors are fabricated on (110) surface-oriented silicon with <110> channel orientation while NMOS transistors are fabricated on (100) surface-oriented silicon with <110> channel orientation [1.37]. As opposed to 45° rotated (100) surface-oriented silicon, hole mobility is enhanced by HOT and can be enhanced by uniaxial compressive stress [1.37]. For process-induced stress, mechanical stress can be introduced into the channel through silicon nitride liners, S/D stressors, gate and contact. For liners, mechanical stress in CESL can be modulated such that compressive stressed CESL is deposited over PMOS transistors while tensile stressed CESL is deposited over NMOS transistors [1.38]. Stress Memorization technique (SMT), which involves the deposition of the tensile stressed silicon nitride liner over the NMOS transistor after Ge pre-amorphization implantation and S/D implantation, will induce a beneficial compressive vertical channel stress in NMOS transistor after S/D annealing [1.39, 1.40]. Embedded Si<sub>1-y</sub>Ge<sub>y</sub> (e-SiGe) S/D stressor will induce a longitudinal compressive stress for PMOS transistor [1.41]. Embedded carbondoped silicon (e-Si:C) S/D stressor will induce a longitudinal tensile stress for NMOS transistor [1.42]. Recently, Intel patented a novel way to increase  $I_{on}$  of NMOS transistors

by introducing longitudinal tensile stress to NMOS transistor using trench contact with tensile fill [1.43]. The stress engineering techniques are applicable to the silicon oxynitride gate dielectric/ poly-Si gate stack as well as the high-*k* gate dielectric/ metal gate stack. In fact, the channel strain of Gate-last high-k/ metal gate scheme is higher than Gate-first High-*k*/ metal gate and the conventional SiON<sub>x</sub>/ poly-Si gate schemes [1.44, 1.45] because it does not experience any reaction strain by gate.

Main Mobility Enhancement Techniques

Figure 1-5 Flow chart of the main mobility enhancement techniques [1.30].

### Objectives

### (1) To clarify the drain current transport in the nanoscale MOS transistor

There are some conflicting theories regarding the effects of mobility enhancement on the  $I_{on}$  of nanoscale MOS transistors: (i) velocity saturation model, (ii) quasi-ballistic model, (iii) ballistic model, and (iv) empirical model. However, experimental data has shown that stress engineering can improve  $I_{on}$  of the nanoscale MOS transistors through mobility enhancement. This work will clarify the merits and limitations of the theories and then come up with a simplified drain current equation that can reconcile the existing theories on drain current transport.

# (2) To determine if CESL-induced tensile stress can bring about an overall $I_{on}$ improvement in NMOS transistor

It is intuitive that a higher mobility will increase both  $I_{on}$  and subthreshold  $I_{off}$ . This work will investigate the physics behind the overall strain-induced  $I_{on}$  improvement in NMOS transistors even though stress engineering leads to a bigger percentage increase in log  $I_{off}$  than  $I_{on}$ .

# (3) To determine the effects of switching from the conventional <110> channel orientation to <100> channel orientation on $I_{on}$ and $I_{off}$ of MOS transistors that are fabricated on (100)Si

Apart from the conventional (100) Si, 45° rotated (100)Si is also widely used in the semiconductor industry owing to its higher hole mobility. However, the effects of the change in channel orientation on  $I_{on}$  of NMOS transistor are not well studied. The physics behind the increase in effective channel length ( $L_{eff}$ ) is also left unexplored. This work will first study the effects of the change in channel orientation on electron mobility of NMOS transistors as well as the physics behind the increase in  $L_{eff}$ . Then, we discuss the effects of the change in channel orientation on  $I_{on}$  and  $I_{off}$  of NMOS transistor as well as the strain-induced effects on  $I_{on}$  and  $I_{off}$  of <100> channel NMOS transistors.

### 1.4 Organization of the Thesis

**Chapter 2** gives an overview of the stress engineering techniques and its effects on the conduction band minimum and valence band maximum. The usage of piezoresistance coefficients to predict the strain-induced change in mobility is also discussed.

**Chapter 3** explains the relevance of the low-field mobility ( $\mu_{eff}$ ) in the nanoscale MOS transistors. This work will unify the merits of velocity saturation model, the ballistic transport and the quasi-ballistic transport and then come up with a simplified saturation drain current equation for nanoscale MOS transistor.

**Chapter 4** discusses the effects of mechanical stress on the electrical parameters of MOS transistors. Unlike most publication, this work will discuss the physics behind the strain-induced increase in the  $I_{off}$  of NMOS transistors. This work will address why CESL-induced tensile stress will lead to an overall  $I_{on}$  improvement in NMOS transistors even though the percentage increase in log  $I_{off}$  is bigger than the percentage increase in  $I_{on}$ .

**Chapter 5** discusses the effects of the switching from the conventional (100)Si to 45° rotated (100)Si on  $I_{on}$  and  $I_{off}$  of MOS transistors. This work shows that the effective conductivity electron mass of (100)Si is independent of channel orientation and discusses the mechanism behind the increase in  $L_{eff}$ .

**Chapter 6** concludes the thesis by highlighting the main contributions of this project and providing some suggestions for future work.

### 2. Literature review on Stress Engineering

### 2.1 Methods to introduce channel stress

### 2.1.1 Substrate-induced stress

Fig. 2-1 shows the cross-section of MOS transistors fabricated on the strained-Si on relaxed  $Si_{1-y}Ge_y$  virtual substrate. The fabrication process can be found in Ref.[1.11]. For NMOS transistor, the silicon epitaxial layer is in-situ doped with boron. For PMOS transistor, the silicon epitaxial layer is in-situ doped with arsenic. Owing to the lattice mismatch between the epitaxial Si and the relaxed  $Si_{1-y}Ge_y$  virtual substrate, the transistors will experience biaxial tensile stress, leading to an increase in electron mobility and hole mobility [2.1, 2.2].

Figure 2-1 Cross-section of (a) NMOS transistor, (b) PMOS transistor fabricated on the strained-Si on relaxed  $Si_{1-x}$  Ge<sub>y</sub> virtual substrate.

A decrease in the thickness of the strained-Si layer causes a decrease in the carrier confinement because of quantum mechanical effects at the SiO<sub>2</sub>/ Si interface [2.3]. This leads to carrier conduction through the low-mobility relaxed Si<sub>1-y</sub>Ge<sub>y</sub> underlayer and thus degrading the mobility. When the thickness of the strained-Si layer is bigger than the equilibrium critical thickness ( $t_{crit}$ ), strain relaxation will occur through the formation of misfit dislocations. Although a higher Ge content will increase the amount of biaxial tensile stress,  $t_{crit}$  will decrease with increasing Ge content [2.4]. Fiorenza et al. reported that there is mobility enhancement in MOS transistors fabricated on the strained-Si on relaxed Si<sub>1-y</sub>Ge<sub>y</sub> virtual substrate even though the strained-Si layer is significantly bigger than  $t_{crit}$  [2.5]. However, there will be a significant increase in the off-state leakage current of the MOS transistors whose thickness of the strained-Si layer is significantly bigger than  $t_{crit}$  [2.5]. From the photo-emission microscopy, the increase in the leakage current is caused by the enhanced dopant diffusion near misfit locations, which leads to the S/D electrical shorting [2.5].

### 2.1.2 Process-induced stress

### 2.1.2.1 Shallow trench isolation (STI)

The purpose of shallow trench isolation (STI) is to electrically isolate the adjacent MOS transistors. It involves the deposition of High Density Plasma (HDP) oxide in silicon trenches, followed by chemical mechanical polish (CMP) to planarize the silicon surface. Owing to the difference in thermal expansion coefficient between silicon and silicon dioxide, STI will induce a lateral compressive stress in the channel [2.6]. Based on piezoresistance coefficient, this is undesirable for NMOS transistors and PMOS transistors that are fabricated on (100) surface-oriented silicon. Furthermore, the mechanical stress-induced dopant diffusion model has shown that STI-induced compressive stress will retard the diffusion of boron, arsenic and phosphorus [2.7]. This is consistent with the results obtained using the density function theory calculations [2.8]. In addition, Hsieh et al. showed that a reduction in S/D overhang can decrease the gate-to-S/D overlap of NMOS transistor owing to STI-induced retardation of the lateral diffusion of the n<sup>+</sup> S/D extension implants [2.9].

### 2.1.2.2 Contact etch stop layer (CESL)