# Electrical Modeling and Characterization of Through Silicon via for Three-Dimensional ICs

Guruprasad Katti, Michele Stucchi, Kristin De Meyer, and Wim Dehaene, Senior Member, IEEE

Abstract—Three-dimensional ICs provide a promising option to build high-performance compact SoCs by stacking one or more chips vertically. Through silicon vias (TSVs) form an integral component of the 3-D IC technology by enabling vertical interconnections in 3-D ICs. TSV resistance, inductance, and capacitance need to be modeled to determine their impact on the performance of a 3-D circuit. In this paper, the *RLC* parameters of the TSV are modeled as a function of physical parameters and material characteristics. Models are validated with the numerical simulators like Raphael and Sdevice and with experimental measurements. The TSV *RLC* model is applied to predict the resistance, inductance, and capacitances of small-geometry TSV architectures. Finally, this paper also proposes a simplified lumped TSV model that can be used to simulate 3-D circuits.

Index Terms—Three-dimensional ICs, through silicon via (TSV), TSV lumped RLC model.

#### I. INTRODUCTION

**B** ENEFITS of 3-D integrated circuits (ICs) include improved packing density, better noise immunity, reduced power consumption, and faster speed due to reduced wire length/lower wire capacitance. In addition, 3-D ICs are promising for the heterogeneous integration of different technologies (logic, memory, RF, analog, etc.) which would enable high-performance and compact SoCs [1]. The fabrication of 3-D stacked IC (SIC) involves stacking of one or more chips, and the through silicon via (TSV) [2] constitutes a key component for interconnecting chips vertically and forms a cylindrical metal–oxide–semiconductor (MOS) capacitor with the semiconductor substrate acting as the bulk and the TSV metal acting as a gate.

The impact of TSV on the 3-D circuit performance needs to be evaluated, and there have been attempts to characterize the resistance and capacitance of TSV [3], [4]. The microwave characterization of TSV [5] and the extraction of the high-frequency electrical circuit model of TSV based on S-parameter measurements [6] have been attempted. Cheng *et al.* [3] have presented the TSV C-V characteristics but do not attempt to model the TSV. The TSV structure in [3] also involves

Manuscript received June 16, 2009; revised September 28, 2009. First published November 24, 2009; current version published December 23, 2009. The review of this paper was arranged by Editor J. Woo.

G. Katti, K. De Meyer, and W. Dehaene are with IMEC, 3001 Leuven, Belgium, and also with the Department of Electrical Engineering, Katholieke Universiteit Leuven, Leuven 3001, Belgium (e-mail: guruprasad.katti@ imec.be).

M. Stucchi is with IMEC, Leuven 3001, Belgium.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2034508

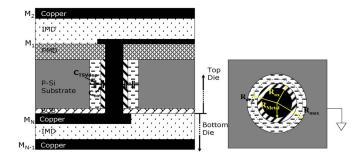

Fig. 1. TSV architecture.

a predominant reversed bias capacitance of the p-n junction diodes. Moreover, the TSV structure and the 3-D process used in [3] and [4] are different when compared to the TSV process [7] adopted today. Leung and Chen [5] measured the resistance and inductance of large TSV structures but do not correlate them with the physical dimensions and material characteristics. Ryu et al. [6] extract the resistance, inductance, and capacitance of the TSV from S-parameter measurements but the corelation to the physical dimensions and material properties of the TSV is missing. In this paper, the TSV resistance  $(R_{\text{TSV}})$ , inductance  $(L_{\text{TSV}})$ , and capacitance  $(C_{\text{TSV}})$  are modeled as a function of physical dimensions and material characteristics of the TSV. A validated lumped TSV model built using the TSV RLC parameters is then approximated to form a simple lumped TSV model, which enables fast yet accurate 3-D circuit simulations.

First-order expressions for  $R_{\rm TSV}$ ,  $L_{\rm TSV}$ , and  $C_{\rm TSV}$  as a function of physical parameters and material characteristics are derived and validated with numerical simulators like Raphael [8] and Sdevice [9] in Section II. Electrical measurements performed to characterize  $R_{\rm TSV}$ ,  $L_{\rm TSV}$ , and  $C_{\rm TSV}$  further validate the models in Section III. Validated models are then extended to predict the *RLC* parameters of the future small-geometry TSV structures foreseen in ITRS [10]. A lumped model for the TSV using  $R_{\rm TSV}$ ,  $L_{\rm TSV}$ , and  $C_{\rm TSV}$  is proposed and further simplified in Section IV. Section V concludes this paper.

#### II. $R_{\text{TSV}}$ , $L_{\text{TSV}}$ , and $C_{\text{TSV}}$ Modeling

In the 3-D TSV first approach [7], TSVs are fabricated after FEOL processing and before BEOL processing and enable the interconnection between the Top Metal of the bottom tier and Metal1 of the top tier, as shown in the cross section of Fig. 1. Analytical modeling starting from the basic electrodynamic principles aid in understanding the impact of physical and technological parameters on  $R_{\rm TSV}$ ,  $L_{\rm TSV}$ , and  $C_{\rm TSV}$ .

TABLE I RTSV DC COMPARISON BETWEEN ANALYTICAL MODEL AND RAPHAEL SIMULATIONS

| TSV<br>Diameter<br>[um] | TSV<br>Dielectric<br>Thickness<br>[nm] | TSV<br>Length<br>[μm] | Analytical<br>R <sub>TSV_DC</sub><br>[mΩ] | Raphael <sup>TM</sup><br>Simulated<br>R <sub>TSV_DC</sub><br>[mΩ] | %<br>Deviation |

|-------------------------|----------------------------------------|-----------------------|-------------------------------------------|-------------------------------------------------------------------|----------------|

| 2                       | 50                                     | 20                    | 118.491                                   | 119.254                                                           | 0.640          |

| 2                       | 100                                    | 20                    | 132.023                                   | 132.872                                                           | 0.639          |

| 5                       | 50                                     | 50                    | 44.539                                    | 44.961                                                            | 0.938          |

| 5                       | 100                                    | 50                    | 46.414                                    | 46.853                                                            | 0.939          |

TABLE II EMPIRICAL  $L_{\text{TSV}}$  Estimations

| TSV<br>Diameter<br>[µm] | TSV<br>Dielectric<br>Thickness<br>[nm] | TSV<br>Length<br>[μm] | Empirical<br>L <sub>TSV</sub><br>[pH] |

|-------------------------|----------------------------------------|-----------------------|---------------------------------------|

| 2                       | 50                                     | 20                    | 13.827                                |

| 2                       | 100                                    | 20                    | 14.039                                |

| 5                       | 50                                     | 20                    | 10.185                                |

| 5                       | 100                                    | 20                    | 10.262                                |

| 5                       | 50                                     | 50                    | 34.262                                |

$R_{\text{TSV}}$  *Model:* The analytical expression of the dc resistance of the TSV is given by

$$R_{\rm TSV\_DC} = \frac{\rho l_{\rm TSV}}{\pi r_{\rm TSV}^2} \tag{1}$$

where  $\rho$  is the resistivity of the conducting material.  $r_{\rm TSV}$  and  $l_{\rm TSV}$  represent the radius and length of the TSV, respectively. The analytical model and Raphael [8] simulations show very good agreement for different TSV architectures, as shown Table I.

For high-frequency signals, however, the increase in resistance due to skin effect should be accounted. Expressions derived by Goldfarb and Pucel [11] are used to derive the  $R_{\rm TSV\_AC}$  for higher frequencies. With Cu as TSV conductor, the resistivity is  $16.8 \,\mathrm{n\Omega} \cdot \mathrm{m}$  and the frequency where skin depth is equal to the radius of the TSV is estimated to be 738 MHz for a TSV with 5- $\mu$ m diameter and 100-nm oxide liner thickness and 4.71 GHz for TSV with 2- $\mu$ m diameter with 50-nm oxide liner thickness, respectively. As expected, resistance increase due to skin effect is quite significant for higher diameter TSV structures.

$L_{\text{TSV}}$  Model: The partial self-inductance of the TSV depends upon the diameter and length of the TSV and is given by the following empirical expression [12]:

$$L_{\rm TSV} = \frac{\mu_o}{4\pi} \begin{bmatrix} 2l_{\rm TSV} \ln\left(\frac{2l_{\rm TSV} + \sqrt{r_{\rm TSV}^2 + (2l_{\rm TSV})^2}}{r_{\rm TSV}}\right) \\ + \left(r_{\rm TSV} - \sqrt{r_{\rm TSV}^2 + (2l_{\rm TSV})^2}\right) \end{bmatrix}$$

(2)

where  $\mu_o$  is the permeability of free space given by  $4\pi \times 10^{-7}$  H/m. Empirical partial self-inductance model estimation results are shown in Table II.

For contemporary TSV architectures with 5- $\mu$ m diameter and 20- $\mu$ m length,  $L_{\text{TSV}}$  is estimated to be 10 pH. Inductive voltage drop  $\omega L_{\text{TSV}}$  exceeds  $R_{\text{TSV}}$  only for frequencies above 3 GHz,

suggesting that inductance can be ignored for clock frequencies with rise and fall times below 3 GHz.

$C_{\text{TSV}}$  Model: An analytical expression for  $C_{\text{TSV}}$  can be obtained by solving Poisson's equation. While the planar MOS capacitor structure has been studied analytically by solving Poisson's equation [13] in a Cartesian coordinate system, the TSV MOS capacitor requires a solution of Poisson's equation in a cylindrical coordinate system. It is sufficient to solve a 1-D Poisson's equation in the radial direction, as the peripheral  $(\Phi)$  and the longitudinal (z) variation in potential  $(\Psi)$  is insignificant. The 1-D Poisson's equation in cylindrical coordinate system with a p-Si substrate is given by

$$\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial\psi}{\partial r}\right) = \frac{qN_a}{\varepsilon_{\rm si}}\tag{3}$$

where q is the electron charge,  $N_a$  is the doping concentration of p-Si substrate, and  $\varepsilon_{si}$  is the permittivity of silicon. The boundary conditions given by the following equations suggest that the potential and the electric field (E) at the depletion radius  $(R_{dep})$  shown in the top view of Fig. 1 is zero

$$\psi|_{R_{\rm dep}} = 0 \tag{4}$$

$$E|_{R_{\rm dep}} = \frac{\partial \psi}{\partial r}\Big|_{R_{\rm dep}} = 0.$$

<sup>(5)</sup>

This is called the partial depletion approximation that considers a depleted silicon film between  $R_{\text{ox}} < r < R_{\text{dep}}$  near the Si–SiO<sub>2</sub> interface while a neutral region for  $r \ge R_{\text{dep}}$  in p-Si substrate, as shown in the top view of Fig. 1.

An expression for the potential variation with respect to the TSV gate voltage based on the solution of Poisson's equation and the derivation of the key MOS capacitor parameters, such as accumulation, depletion, and minimum depletion capacitance of the TSV, is elaborated in the Appendix. The nature of the TSV C-V characteristics is similar to the planar MOS capacitor such that the accumulation capacitance is the oxide capacitance given as

$$C_{\rm TSVACC} = C_{\rm ox} = \frac{2\pi\varepsilon_{\rm ox}l_{\rm TSV}}{\ln\left(\frac{R_{\rm ox}}{R_{\rm Metal}}\right)}.$$

(6)

As the TSV gate bias increases, the depletion capacitance acts in series with the oxide capacitance such that the effective capacitance is the series combination of the oxide and depletion capacitances. The minimum depletion capacitance is

| TSV<br>Dia<br>[um] | TSV<br>Oxide<br>Thick<br>ness<br>[nm] | Na<br>[/cm <sup>3</sup> ] | Analytical<br>C <sub>ox</sub><br>[fF] | Sdevice <sup>TM</sup><br>Simulated<br>C <sub>ox</sub><br>[fF] | %<br>Dev | Analytical<br>C <sub>TSVMIN</sub> [fF] | Sdevice <sup>TM</sup><br>Simulated<br>C <sub>TSVMIN</sub> [fF] | %<br>Dev |

|--------------------|---------------------------------------|---------------------------|---------------------------------------|---------------------------------------------------------------|----------|----------------------------------------|----------------------------------------------------------------|----------|

| 5                  | 120                                   | 2e15                      | 88.225                                | 88.401                                                        | 0.199    | 35.889                                 | 37.20                                                          | 3.52     |

| 5                  | 120                                   | 1e17                      | 88.225                                | 88.401                                                        | 0.199    | 69.543                                 | 69.982                                                         | 0.627    |

| 2                  | 50                                    | 2e15                      | 84.608                                | 84.765                                                        | 0.185    | 21.429                                 | 21.651                                                         | 1.02     |

| 2                  | 50                                    | 1e17                      | 84.608                                | 84.765                                                        | 0.185    | 52.229                                 | 52.371                                                         | 0.271    |

TABLE III  $C_{\mathrm{TSV}}$  Comparison Between Analytical Model and Raphael Simulations

reached when the depletion radius reaches its maximum and is given by

$$C_{\rm TSVMIN} = \frac{C_{\rm ox} C_{\rm dep\,min}}{C_{\rm ox} + C_{\rm dep\,min}}$$

where

$$C_{\rm dep\,min} = \frac{2\pi\varepsilon_{\rm si}l_{\rm TSV}}{\ln\left(\frac{R_{\rm max}}{R_{\rm ox}}\right)}.$$

(7)

The accumulation and depletion capacitance expressions show that the  $C_{\rm TSV}$  is directly proportional to the length of the TSV and inversely proportional to the TSV dielectric thickness, as expected. Moreover,  $R_{\rm max}$  is inversely proportional to substrate doping concentration such that the depletion capacitance and threshold voltage would be higher for higher doping concentration when compared to lower doping concentration. Thus, lowdoped p-Si substrates are an ideal choice to achieve minimum  $C_{\rm TSV}$ .

The comparison between Sdevice [9] simulations and the analytical model results for various TSV parameters is detailed in Table III. The analytical model is able to accurately predict the oxide capacitance and minimum depletion capacitance for varying TSV diameter, oxide liner thickness, and doping concentration.

$R_{\rm TSV}$  and  $C_{\rm TSV}$  measurement results are shown in the next section. Experimental results are used to validate the RLC TSV models. RLC TSV models are further extended to predict the resistance, inductance, and capacitance values of future small-geometry TSVs.

#### III. TSV ELECTRICAL CHARACTERIZATION AND PROGNOSTICS

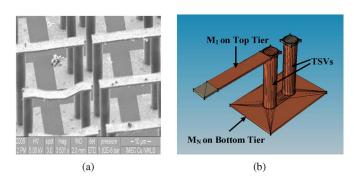

$R_{\rm TSV}$  is characterized from the resistance measurement of TSV daisy chains, as shown in Fig. 2(a). Fig. 2(b) shows a singular section of the simulated TSV daisy chain in Raphael [8]. The TSV diameter is 5  $\mu$ m with 10- $\mu$ m pitch while TSV length is reduced to 20  $\mu$ m after wafer thinning. Raphael simulations are performed, assuming Cu resistivity to be 16.8 n $\Omega \cdot$ m. Simulated resistance values are in good agreement with the measurements as shown in Table IV, suggesting the methodology can indeed be used to model the resistance of a single TSV as in Section II.

The  $L_{\text{TSV}}$  empirical model is validated with the inductance measurements performed by Leung and Chen [5] shown in Table V. It can be seen that the inductance estimations match

Fig. 2. (a) SEM of 3D-SIC TSV daisy chain after etching away top substrate. (b) Section of a TSV daisy chain used for Raphael simulations.

with the inductance measurements, and the model can be used to predict the inductance of future small-geometry TSVs.

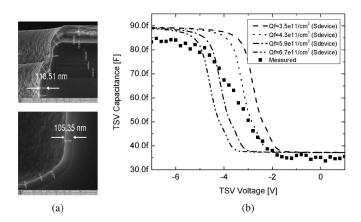

$C_{\rm TSV}$  is characterized by using the TSV embedded and deembedded structures to eliminate the effect of BEOL parasitic capacitances. Fig. 3(a) shows the TSV cross section, indicating the resultant effective oxide liner thickness on the top and bottom of TSV. TSV Sdevice [9] simulation results considering  $\varepsilon_{\rm ox} = 3.9$ ,  $\phi_m = 4.7$  eV,  $N_a = 2 \times 10^{15}/{\rm cm}^3$ , and  $t_{\rm ox} =$ 118.20 nm with varying fixed oxide charges were compared with the TSV high-frequency C-V measurements, as shown in Fig. 3(b). In the desired operating voltage region from 0 to  $V_{\rm dd}$  (~1 V), the TSV exhibits minimum depletion capacitance.

The accumulation and the minimum depletion capacitance match well with the measurements. Five-percent discrepancy in the oxide capacitance can be attributed to the reduction of oxide thickness at the bottom of the tapering TSV. In addition, the discrepancy in different C-V slopes in the depletion region can be attributed to the presence of interface states at the Si-SiO<sub>2</sub> interface, which have been ignored during Sdevice simulations.

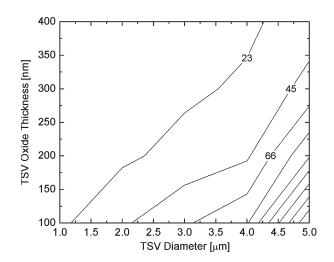

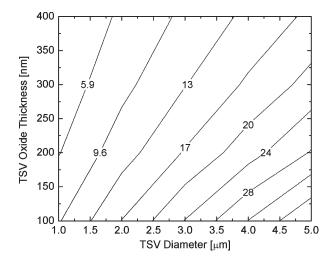

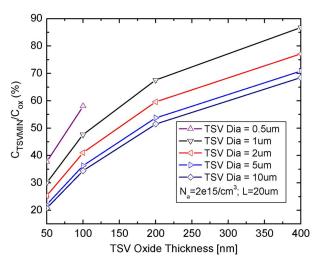

The ITRS [10] predicts TSV architectures with a diameter of 1  $\mu$ m and minimum TSV length of 10  $\mu$ m by 2015. Figs. 4 and 5 show  $C_{ox}$  and  $C_{TSVMIN}$ , respectively, as a function of TSV diameter and oxide thicknesses with  $N_a = 2 \times 10^{15}/\text{cm}^3$ and  $l_{TSV} = 20 \ \mu$ m. It can be seen that  $C_{ox}$  and  $C_{TSVMIN}$ increase with decreasing oxide liner thickness and increasing TSV diameter as expected. Shorter TSV length offers lower  $C_{TSV}$ , and hence, a thin wafer obtained after grinding and CMP would offer minimum capacitance compared with a thick wafer. However, processing a thin wafer increases the processing steps as the wafer has to undergo bonding and debonding with a carrier wafer during the 3-D IC fabrication.

The reduction in capacitance by the depletion capacitance for varying TSV oxide thickness is shown in Fig. 6. The most

| # TSVs in<br>Daisy Chain | Measured<br>Total Chain<br>Resistance [Ω] | Measured Single<br>Chain Resistance<br>[mΩ] | Simulated Single<br>Chain Resistance<br>[mΩ] | % Error |

|--------------------------|-------------------------------------------|---------------------------------------------|----------------------------------------------|---------|

| 8                        | 0.704                                     | 175.881                                     | 183.587                                      | 4.382   |

| 98                       | 10.292                                    | 210.051                                     | 183.587                                      | 12.599  |

| 998                      | 106.222                                   | 212.870                                     | 183.587                                      | 13.756  |

TABLE IV RAPHAEL SIMULATION AND  $R_{\rm TSV}$  Measurement Comparison

TABLE V  $L_{\rm TSV}$  Empirical Model and Measurement Comparison

| TSV<br>Diameter<br>[μm] | TSV<br>Length<br>[µm] | Empirical<br>L <sub>TSV</sub><br>[pH] | Measured<br>L <sub>TSV</sub><br>[pH] | %<br>Deviation |

|-------------------------|-----------------------|---------------------------------------|--------------------------------------|----------------|

| 50                      | 400                   | 255.191                               | 308.5                                | 17.28          |

| 60                      | 400                   | 241.096                               | 262.5                                | 8.153          |

| 70                      | 400                   | 229.254                               | 254.5                                | 9.919          |

Fig. 3. (a) Single TSV FIB image. (b). Solvice TSV C-V simulations versus measurements.

Fig. 4.  $C_{\rm ox}$  (in femtofarads) variation with TSV diameter and oxide thickness.

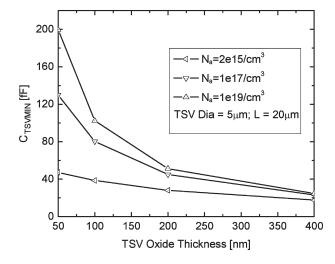

effective reduction is achieved for lower oxide thicknesses. In fact, for lower oxide thickness, the oxide capacitance becomes larger and less significant in the series with the depletion capacitance. The variation of  $C_{\rm TSV}$  with doping concentration is shown in Fig. 7. As expected, lower doping concentrations in-

Fig. 5.  $C_{\rm TSVMIN}$  (in femtofarads) variation with TSV diameter and oxide thickness.

Fig. 6.  $C_{\rm TSVMIN}$  reduction for varying TSV oxide thicknesses.

crease the depletion width and hence reduce  $C_{\text{TSVMIN}}$ , making highly resistive substrate attractive for low-capacitance TSVs.

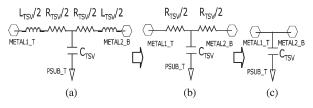

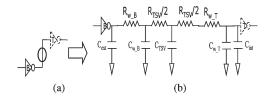

#### IV. LUMPED TSV MODEL

A lumped RLC model for the TSV is shown in Fig. 8(a).  $R_{\text{TSV}}$  and  $L_{\text{TSV}}$  cause the voltage drop along the interconnected nodes between Metal1 of the top tier and Top Metal of the bottom tier.  $C_{\text{TSV}}$  is connected between TSV and ground. As suggested in Section II, for the current TSV dimensions of 5- $\mu$ m diameter and 20- $\mu$ m length,  $L_{\text{TSV}}$  is predominant only for clock frequencies with rise and fall times above 3 GHz when  $\omega L_{\text{TSV}} \ge R_{\text{TSV}}$ . The approximate model by ignoring

Fig. 7.  $C_{\text{TSVMIN}}$  variation with doping.

Fig. 8. (a) RLC TSV model. (b) RC TSV model. (c) C TSV model.

Fig. 9. (a) Bottom inverter–TSV–top inverter schematic. (b) Equivalent electrical circuit.

the inductance reduces to a simplified RC model shown in Fig. 8(b). The impact of  $R_{\rm TSV}$  and  $C_{\rm TSV}$  on the TSV delay can be analyzed with the help of the circuit shown in Fig. 9(a). The circuit consists of an inverter placed on the bottom tier driving an inverter on the top tier through TSV and BEOL RC loads. RC elements appearing in the signal path are shown in Fig. 9(b).  $C_{\rm ext}$  and  $C_{\rm int}$  indicate the output and input capacitances of the inverter.  $R_{\rm w_B}$  and  $C_{\rm w_T}$  denote the lumped BEOL load on the bottom tier while  $R_{\rm w_T}$  and  $C_{\rm w_T}$  denote the lumped BEOL load on the top tier.

The following Elmore delay expression is used to analyze the impact of  $R_{\text{TSV}}$  and  $C_{\text{TSV}}$  on the path delay:

$$tp = 0.69R_{\rm dr}C_{\rm ext} + 0.69(R_{\rm dr} + R_{\rm w\_B})C_{\rm w\_B} + 0.69(R_{\rm dr} + R_{\rm w\_B} + 0.5R_{\rm TSV})C_{\rm TSV} + 0.69(R_{\rm dr} + R_{\rm w\_B} + R_{\rm TSV} + R_{\rm w\_T})(C_{\rm w\_T} + C_{\rm int})$$

(8)

where  $R_{dr}$  is the driving resistance of the inverter.

First-hand calculations [14] indicate that  $C_{\text{int}}$  and  $C_{\text{ext}}$  are on the order of ~3 fF and the driving resistance of the inverter is on the order of kiloohms for 0.25- $\mu$ m technology. Since  $C_{\text{TSV}} = 35$  fF is much larger than the  $C_{\text{int}}$  and  $C_{\text{ext}}$  values, the term  $(R_{\text{dr}} + R_{\text{w}}_{\text{B}} + 0.5 R_{\text{TSV}})C_{\text{TSV}}$  has a larger weight

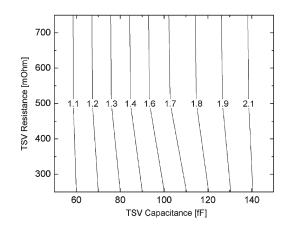

Fig. 10. RO delay (in microseconds) with varying  $R_{\text{TSV}}$  and  $C_{\text{TSV}}$ .

in determining the delay in (8). Moreover, in (8), the term  $R_{\rm TSV}$  is always added to the driving resistance of the inverter  $R_{\rm dr}$  and BEOL resistances  $R_{\rm w\_B}$  and  $R_{\rm w\_T}$ . Smaller cross sections and longer lengths of BEOL metal lines provide larger resistances than estimated  $R_{\rm TSV} = 18 \text{ m}\Omega$  in contemporary TSV architecture with 5- $\mu$ m TSV diameter. Hence,  $R_{\rm TSV}$  would cause a minimal impact on the delay. A predominant impact of  $C_{\rm TSV}$  and a reduced impact of  $R_{\rm TSV}$  approximate the lumped TSV model, as shown in Fig. 8(c).

To corroborate the aforementioned analysis, a 41-stage ring oscillator (RO) with inverters in alternate tiers connected by TSVs is simulated using Spectre [15]. The RO is cascaded with an eight-stage frequency divider circuit at the output.  $R_{\text{TSV}}$  and  $C_{\text{TSV}}$  are varied, and their impact on the RO delay is shown in Fig. 10. Variations in  $R_{\text{TSV}}$  values for a given value of  $C_{\text{TSV}}$  do not change the RO delay significantly but RO delay increases significantly with increasing  $C_{\text{TSV}}$ . Thus, changes in  $R_{\text{TSV}}$ show minimal impact on the delay, while the impact of  $C_{\text{TSV}}$ is not negligible. The dynamic power dissipation  $C_{\text{TSV}}V_{\text{dd}}^2 f$  is also reduced by lower TSV capacitance, and therefore, efforts should be made to reduce the TSV capacitance.

#### V. SUMMARY AND CONCLUSION

The resistance, inductance, and capacitance of a TSV are modeled as a function of physical parameters and material characteristics. Estimations of R, L, and C match very well with the numerical simulation results from Raphael and Sdevice and with experimental measurements. The impact of various technology parameters on the resistance, inductance, and capacitance of TSV has been analyzed, and the models are applied to predict the resistance, inductance, and capacitance of the small-geometry TSVs. The TSV lumped impedance model is based on these RLC elements and shows that the TSV capacitance has the most dominant impact on the delay.

#### APPENDIX

By solving (3) with the boundary conditions given in (4)–(5), the solution of the potential is derived as

$$\psi(r) = \frac{qN_a r^2}{4\varepsilon_{\rm si}} - \frac{qN_a R_{\rm dep}^2}{2\varepsilon_{\rm si}} \ln(r) + \frac{qN_a R_{\rm dep}^2}{4\varepsilon_{\rm si}} \left(2\ln(R_{\rm dep}) - 1\right). \tag{A1}$$

This solution is further elaborated to make the dependence explicit on some of the key parameters like threshold voltage and accumulation, depletion, and minimum depletion capacitance of the TSV.

#### A. Derivation of Threshold Voltage $(V_{\rm Th})$ of TSV

The threshold voltage of TSV is defined as the TSV voltage at which the Si–SiO<sub>2</sub> surface potential is equal to  $2\ln(N_a/n_i)$ , where  $n_i$  is the intrinsic carrier concentration of the Si substrate. This surface potential at the Si–SiO<sub>2</sub> interface is reached when the depletion radius is at its maximum value. Substituting  $\psi|_{r=R_{ox}} = 2\ln(N_a/n_i)$  and  $R_{dep} = R_{max}$  in (A1), the maximum depletion radius is given in

$$\frac{qN_aR_{\rm ox}^2}{4\varepsilon_{\rm si}} - \frac{qN_aR_{\rm max}^2}{2\varepsilon_{\rm si}}\ln(R_{\rm ox}) + \frac{qN_aR_{\rm max}^2}{4\varepsilon_{\rm si}}\left(2\ln(R_{\rm max}) - 1\right) - 2\ln\left(\frac{N_a}{n_i}\right) = 0$$

(A2)

Equation (A2) is solved iteratively to obtain the maximum depletion radius. This solution is quickly converging even for the small-geometry TSV dimensions. Total bulk charge in the radial depletion region is  $Q_B = -qN_a\pi(R_{\max}^2 - R_{ox}^2)$ . The applied TSV voltage drops across the TSV oxide as well as the silicon substrate, as given in

$$V_{\rm TSV} = V_{\rm si} + V_{\rm ox}.$$

(A3)

By applying Gauss's law to the cylindrical MOS system and by considering the work function of the TSV metal in addition to total oxide charges  $(Q_{ot} = Q_f + Q_m + Q_{tr})$ , the expression for threshold voltage is derived as

$$V_{\rm Th} = \phi_{\rm ms} - \frac{2\pi R_{\rm ox} q Q_{\rm ot}}{2\pi \varepsilon_{\rm ox}} \ln\left(\frac{R_{\rm ox}}{R_{\rm Metal}}\right) + 2\ln\left(\frac{N_a}{n_i}\right) + \frac{q N_a \pi \left(R_{\rm max}^2 - R_{\rm ox}^2\right)}{2\pi \varepsilon_{\rm ox}} \ln\left(\frac{R_{\rm ox}}{R_{\rm Metal}}\right)$$

(A4)

where total oxide charges are composed of the fixed oxide charge  $(Q_f)$  at the Si-SiO<sub>2</sub> interface, mobile charges in the oxide  $(Q_m)$ , and oxide trapped charges  $(Q_{tr})$  while  $\phi_{ms}$  denotes the work function difference given by  $\phi_m - \phi_s$ . The flatband voltage in this case equals

$$V_{\rm FB} = \phi_{\rm ms} - \frac{2\pi R_{\rm ox} q Q_{\rm ot}}{2\pi \varepsilon_{\rm ox}} \ln \left(\frac{R_{\rm ox}}{R_{\rm Metal}}\right).$$

As in the planer case, a cylindrical TSV system has three distinct regions of operation, namely, accumulation, depletion, and inversion. The capacitance expressions in each operating region are derived in the following.

### B. Accumulation Region $(V_{\rm TSV} < V_{\rm FB})$

TSV MOSCAP is in the accumulation region when  $V_{\text{TSV}} < V_{\text{FB}}$ . The capacitance in this case is the cylindrical oxide

capacitance given as

$$C_{\rm TSVACC} = C_{\rm ox} = \frac{2\pi\varepsilon_{\rm ox}l_{\rm TSV}}{\ln\left(\frac{R_{\rm ox}}{R_{\rm Metal}}\right)}.$$

## C. Depletion Region ( $V_{\rm FB} \leq V_{\rm TSV} < V_{\rm Th}$ )

For the voltage range of  $V_{\rm FB} \leq V_{\rm TSV} \leq V_{\rm Th}$ , the substrate region is depleted of carriers and the capacitance is the series combination of  $C_{\rm ox}$  and  $C_{\rm dep}$  such that

$$C_{\rm TSVDEP} = \frac{C_{\rm ox}C_{\rm dep}}{C_{\rm ox} + C_{\rm dep}}.$$

The depletion capacitance is given by

$$C_{\rm dep} = \frac{2\pi\varepsilon_{\rm si}l_{\rm TSV}}{\ln\left(\frac{R_{\rm dep}}{R_{\rm ox}}\right)}$$

and  $R_{dep}$  is the radial depletion width obtained by solving (A5) for  $R_{dep}$  for a given bias  $V_{TSV}$ .

$$V_{\rm TSV} = \phi_{\rm ms} - \frac{2\pi R_{\rm ox} q Q_{\rm ot}}{2\pi \varepsilon_{\rm ox}} \ln\left(\frac{R_{\rm ox}}{R_{\rm Metal}}\right) + 2\ln\left(\frac{N_a}{n_i}\right) + \frac{q N_a \pi \left(R_{\rm dep}^2 - R_{\rm ox}^2\right)}{2\pi \varepsilon_{\rm ox}} \ln\left(\frac{R_{\rm ox}}{R_{\rm Metal}}\right)$$

(A5)

#### D. Minimum Depletion Capacitance Region $(V_{\text{TSV}} \ge V_{\text{Th}})$

For high-frequency operation, the depletion width does not increase beyond  $R_{\rm max}$ , and hence, the total capacitance is the series combination of oxide capacitance and minimum depletion capacitance, providing minimal  $C_{\rm TSV}$  given as

$$C_{\rm TSVMIN} = \frac{C_{\rm ox}C_{\rm dep\,min}}{C_{\rm ox} + C_{\rm dep\,min}}$$

where

$$C_{\rm dep\,min} = \frac{2\pi\varepsilon_{\rm si}l_{\rm TSV}}{\ln\left(\frac{R_{\rm max}}{R_{\rm ox}}\right)}.$$

#### ACKNOWLEDGMENT

The authors would like to thank D. Velenis for the helpful discussions and for reviewing the manuscript, IMEC P-line for processing the wafers, and AMSIMEC for the parametric measurement service.

#### REFERENCES

- A. Rahman and R. Reif, "System level performance evaluation of threedimensional integrated circuits," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 8, no. 6, pp. 671–678, Dec. 2000.

- [2] A. W. Topol, D. C. La Tulipe, Jr., L. Shi, D. J. Frank, K. Bernstein, S. E. Steen, A. Kumar, G. U. Singco, A. M. Young, K. W. Guarini, and M. Ieong, "Three-dimensional integrated circuits," *IBM J. Res. Develop.*, vol. 50, no. 4/5, pp. 491–506, Jul.–Sep. 2006.

- [3] C. H. Cheng, A. S. Ergun, and B. T. Khuri-Yakub, "Electrical throughwafer interconnects with sub-pico farad parasitic capacitance," in *Proc. Microelectromech. Syst. Conf.*, Aug. 2001, pp. 18–21.

- [4] E. M. Chow, V. Chandrasekaran, A. Partridge, T. Nishida, M. Sheplak, C. F. Quate, and T. W. Kenny, "Process compatible polysilicon-based electrical through wafer interconnects in silicon substrates," *J. Microelectromech. Syst.*, vol. 11, no. 6, pp. 631–640, Dec. 2002.

- [5] L. L. W. Leung and K. J. Chen, "Microwave characterization and modeling of high aspect ratio through-wafer interconnect vias in silicon substrates," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 8, pp. 2472–2480, Aug. 2005.

- [6] C. Ryu, D. Chung, J. Lee, K. Lee, T. Oh, and J. Kim, "High frequency electrical circuit model of chip-to-chip vertical via interconnection for 3-D chip stacking package," in *Proc. IEEE Top. Meeting Elect. Perform. Electron. Packag.*, Oct. 2005, pp. 151–154.

- [7] J. Van Olmen, A. Mercha, G. Katti, C. Huyghebaert, J. Van Aelst, E. Seppala, Z. Chao, S. Armini, J. Vaes, R.C. Teixeira, M. Van Cauwenberghe, P. Verdonck, K. Verhemeldonck, A. Jourdain, W. Ruythooren, M. de Potter de ten Broeck, A. Opdebeeck, T. Chiarella, B. Parvais, I. Debusschere, T. Y. Hoffmann, B. De Wachter, W. Dehaene, M. Stucchi, M. Rakowski, P. Soussan, R. Cartuyvels, E. Beyne, S. Biesemans, and B. Swinnen, "3D Stacked IC demonstration using a through silicon via first approach," in *IEDM Tech. Dig.*, 2008, pp. 603–606.

- [8] Raphael Interconnect Analysis Program Reference Manual, Ver. A-2007.09, Synopsis Inc., Mountain View, CA, Sep. 2007.

- [9] Sentaurus Device User Guide, Ver. A-2008.09, Synopsis Inc., Mountain View, CA, Sep. 2008.

- [10] International Technology Roadmap for Semiconductors, "Semiconductor Industry Association," 2008.

- [11] M. E. Goldfarb and R. A. Pucel, "Modeling via-hole grounds in microstrip," *IEEE Microw. Guided Wave Lett.*, vol. 1, no. 6, pp. 135–137, Jun. 1991.

- [12] R. Pucel, *Gallium Arsenide Technology*, D. Feny, Ed. Indianapolis, IN: Sams, 1985, ch. 6, p. 216.

- [13] S. M. Sze, *Physics of Semiconductor Devices*. New York: Wiley, 1981.

- [14] J. Rabaey, A. Chandrakasan, and B. Nikolic, *Digital Integrated Circuits*, 2nd ed. Englewood Cliffs, NJ: Prentice-Hall, 2003, ser. Prentice Hall Electronics and VLSI Series.

- [15] Virtuoso Spectre Circuit Simulator Reference, Product Ver. 7.0.1, Cadence Design Syst., Inc. (Cadence), San Jose, CA, Jun. 2008.

**Guruprasad Katti** received the B.E. degree in electrical engineering from A. C. Patil College of Engineering, University of Mumbai, Mumbai, India, in 1999 and the M.S. degree in electrical engineering from the Indian Institute of Technology Madras, Chennai, India, in 2002. His M.S. thesis dealt with the analytical modeling of silicon-oninsulator MOSFETs. He is currently working toward the Ph.D. degree at IMEC, Leuven, Belgium, and Katholieke Universiteit Leuven, Leuven. His Ph.D. focus area is modeling and characterization of its inwards to a 2 D eignvits.

3-D IC interconnects and its impact on 3-D circuits.

Prior to joining the Ph.D. program with IMEC and Katholieke Universiteit Leuven, he was with GE Global Research and National Semiconductor, Bangalore, India, as a CAD Software Engineer.

**Michele Stucchi** received the M.S. degree in electrical engineering from the University of Bari, Bari, Italy, in 1988.

From 1989 to 1991, he was an Interconnect and Silicide Process Engineer for the DRAM plant of Texas Instruments Incorporated, Avezzano, Italy, and from 1991 to 1996, he was an Engineer in failure analysis, FIB analysis, and ESD and latch-up characterization of IC devices with Tecnopolis Science Park, Bari. In 1996, he joined IMEC, Leuven, Belgium, where he managed the Technology Aware

Design research program and where he is currently a Senior Research Engineer in the characterization, modeling, and reliability aspects of 2- and 3-D interconnects.

Kristin De Meyer received the degree in electrical engineering and the Ph.D. degree from the Katholieke Universiteit Leuven (KUL), Leuven, Belgium, in 1974 and 1979, respectively.

From November 1979 to November 1980, she was granted an IBM World Trade Postdoctoral Fellowship and was with the IBM Thomas J. Watson Research Center, Yorktown Heights, NY, on the development of EAROMs using Si-rich oxides. At the end of 1980, she returned to the KUL as a Senior Research Assistant of the NFWO and, from October

1982, as a Research Associate of the NFWO. With the foundation of IMEC, her activities moved from the KUL to IMEC, where she initially remained as a Research Associate of the NFWO. Since October 1986, she has been a part-time Professor with the KUL. Since October 1989, she has been a regular employee of IMEC, where from 1985 to 1992, she was the head of the group on Process and Device Modeling and Simulation, working on process optimization techniques, parameter extraction, analytical and numerical device modeling, and computational physics. Furthermore, statistical process control activities were monitored through her group. From January 1993 to December 2002, she was in charge of deep submicrometer MOS technology and exploratory field-effect devices. In January 2003, she became the Strategic Coordinator of Doctoral Research with IMEC. She was the coordinator for IMEC in the ESPRIT 962 EVEREST, STORM, NOVA, ULTRA, VAHMOS2000 (prime), FASEM, and ULIS projects, in the IST SIGMUND (prime), SATURN (SOI), and NESTOR projects, and in the Marie Curie EST EDITH project. She was also involved in the ESPRIT ACCESS Program, ADEQUAT, ACE, and IST HUNT. She also managed the HCM-SUSTAIN network on deep submicrometer silicon technology with 21 partners from academia and research institutes. She authored or coauthored over 300 publications.

Dr. De Meyer is member of the Flemish and Belgian Federal Councils for Science Policy. She is currently an Editor of the IEEE Electronic Device Letters and a member of the ITRS working groups on Process Integration, Devices and Structures and Emerging Research Devices. She has organized summer courses, the SISPAD 1998 conference, the ULIS 2004 workshop, and an IEDM 2008 short course.

Wim Dehaene (SM'04) was born in Nijmegen, The Netherlands, in 1967. He received the M.Sc. degree in electrical and mechanical engineering and the Ph.D. degree from the Katholieke Universiteit Leuven, Leuven, Belgium, in 1991 and 1996. His thesis is entitled "CMOS integrated circuits for analog signal processing in hard disk systems."

After receiving the M.Sc. degree, he was a Research Assistant with the ESAT-MICAS Laboratory, Katholieke Universiteit Leuven. His research involved the design of novel CMOS building blocks

for hard disk systems. The research was first sponsored by the IWONL (the Belgian Institute for Science and Research in Industry and Agriculture) and later by the IWT (the Flemish institute for Scientific Research in the Industry). In November 1996, he joined Alcatel Microelectronics, Belgium, where he was a Senior Project Leader for the feasibility, design, and development of mixed-mode systems on chip. The application domains were telephony, xDSL, and high-speed wireless LAN. In July 2002, he joined the staff of the ESAT-MICAS Laboratory, Katholieke Universiteit Leuven, where he is currently a Professor. His research domain is circuit-level design of digital circuits. The current focus is on ultralow power signal processing and memories in advanced CMOS technologies. Part of this research is performed in cooperation with IMEC, Leuven, where he is also a part-time Principal Scientist. He is teaching several classes on electrical engineering and digital circuit and system design.