### Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Oct 2008

## Eliminating Via-Plane Coupling using Ground Vias for High-Speed **Signal Transitions**

Songping Wu

Xin Chang

Christian Schuster

Xiaoxiong Gu

et. al. For a complete list of authors, see https://scholarsmine.mst.edu/ele\_comeng\_facwork/1003

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

S. Wu et al., "Eliminating Via-Plane Coupling using Ground Vias for High-Speed Signal Transitions," Proceedings of the Electrical Performance of Electronic Packaging, 2008. IEEE-EPEP, Institute of Electrical and Electronics Engineers (IEEE), Oct 2008.

The definitive version is available at https://doi.org/10.1109/EPEP.2008.4675926

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# Eliminating Via-Plane Coupling Using Ground Vias for High-Speed Signal Transitions

Songping Wu<sup>1</sup>, Xin Chang<sup>1</sup>, Christian Schuster<sup>2</sup>, Xiaoxiong Gu<sup>3</sup>, and Jun Fan<sup>1</sup>

The UMR/MST EMC Laboratory

Missouri University of Science and Technology (formerly University of Missouri-Rolla)

Rolla, MO 65409, {swhv7, xcp46, jfan}@mst.edu

<sup>2</sup>Hamburg Univerity of Technology, Hamburg, Germany, schuster@tuhh.de

<sup>3</sup>IBM T. J. Watson Research Center, Yorktown Heights, NY, xgu@us.ibm.com

Abstract: When a high-speed signal transits through a via that penetrates a plane pair, parallel-plane resonances can cause additional insertion loss for the signal. To eliminate this via-plane coupling, ground vias are added adjacent to the signal via. This paper discusses the impact of the ground vias as a function of the number of the ground vias, their locations, and the size of the plane pair. A block-by-block physics-based equivalent circuit modeling approach is used in the study. The underlying physics of the phenomenon and the design implications are also discussed in the paper.

#### I. INTRODUCTION

In today's high-speed multilayer printed circuit boards (PCBs) or packages, vias are necessary to transit a signal from one layer to another, or to connect integrated circuit (IC) devices to power and ground planes. However, these vias are not ideal transmission-line structures. Rather, they create discontinuities at high frequencies. As the circuit density and data rate continuously increase in digital systems, a signal via that penetrates a plane pair can significantly affect the integrity of the signal [1]. A ground via can be placed adjacent to the signal via to supply a current return path, and it is found that the insertion loss of the signal can be improved by this nearby ground via [2].

This paper describes the underlying physics of the phenomenon and introduces the concept of via-plane coupling. It further investigates the impact of multiple ground vias, the spacing between the signal and ground vias, as well as the plane pair dimensions.

#### II. MODELING APPROACH

Full-wave numerical methods can be used to accurately analyze multilayer multi-via geometries; however, it is time-consuming and the complexity of the model is often limited by the available computational resources. Further, SPICE compatible equivalent circuit models are usually desirable, especially when active IC devices need to be included in the modeling. Various equivalent circuit models have been developed for via geometries over the years. Unfortunately most of them are derived as some mathematical representations. They can usually work well for circuit analysis, but are not suitable for engineering design and discovery.

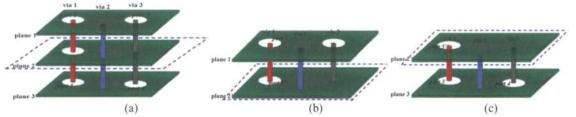

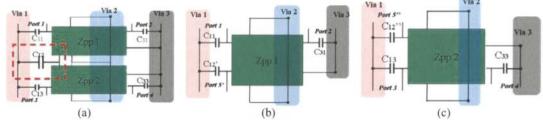

A block-by-block physics-based equivalent circuit modeling approach is used in this study [3-4]. The complicated multilayer via geometry is first divided into multiple blocks at the middle of the power/ground planes or large area fills. Then a physics-based equivalent circuit is extracted for each individual block. The unique benefit of a physics-based model is that every circuit component is directly related to one or some layout features in geometry or some manufacturing tolerances. Thus engineering design and discovery become much easier and more intuitive. Figure 1 illustrates the "divide-and-conquer" strategy. A three-layer via geometry is divided into two blocks at the center of the middle plane. Then physics-based equivalent circuit models for the upper and lower blocks are extracted as shown in Figure 2(b) and 2(c), respectively. Each plane pair is modeled as a multi-port impedance matrix  $Z_{pp}$ . Via-plane capacitances are utilized to account for the displacement currents between the via barrel and the planes. The impedance matrix  $Z_{pp}$  can be obtained using the cavity model [5] and the segmentation technique [6] for arbitrarily-shaped plane pair. The via-plane capacitances can be calculated from an integral-equation formulation [7]. The two blocks are then cascaded together, as shown in Figure 2(a). This modeling approach has been validated by various full-wave simulations and measurements [3-4].

#### III. RESULTS AND DISCUSSIONS

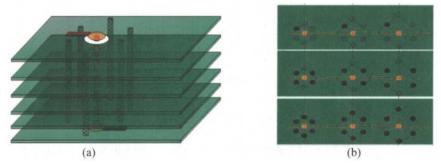

The geometry under study is shown in Figure 3. There is a through-hole signal via connecting a microstrip trace on the top surface to a microstrip trace on the bottom surface. One, four, or six ground vias are added into the geometry adjacent to the signal via. And the spacing between the signal and ground vias varies from 50 mils to 150 mils, as shown in Figure 3(b). Two different board sizes were studied: a larger board with dimensions of 12"×10" representing a typical PCB and a smaller board with dimensions of 2"×1" representing a typical package. The thickness of the planes is 1 mil. The plane separations are 11 mils. The dielectric constant is 3.5, and loss tangent 0.02. The radii of the vias and antipads are 12 mils and 20 mils, respectively.

Figure 1 (a) A three-layer multi-via structure and its breakdown, (b) Upper block, and (c) Lower block.

Figure 2 (a) Equivalent circuit model for the geometry shown in figure 1(a); (b) equivalent circuit model for the upper block shown in Figure 1(b); and, (c)equivalent circuit model for the lower block shown in Figure 1(c).

Figure 3: Test cases under study, (a) a through-hole signal via connecting two microstrip traces; and, (b) ground via configurations.

#### (1). larger board cases

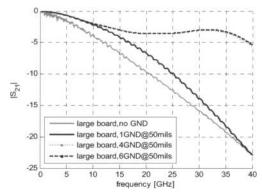

The insertion loss results for the one ground via and four ground via cases are shown in Figure 4 for the larger board whose dimensions are 12"×10". Figure 4 (a) and (c) show the full frequency range results from 10 MHz to 40 GHz. Figure 4 (b) and (d) are the corresponding low-frequency zoom-in plots. As clearly shown in Figure 4(b), there are resonant valleys in the insertion loss curves. When a ground via is added adjacent to the signal via, the magnitudes of these resonant valleys are significantly reduced. Further, the closer the ground via is to the signal via, the lower the magnitudes. The first resonance at 98MHz is due to the lumped resonance caused by the capacitance of the plane pair and the inductance of the ground via. The rest of the resonances are distributed resonances of the parallel planes. In other words, when a signal transits through a via that penetrates a plane pair, the parallel plane resonances can introduce additional insertion loss for the signal. This is called the via-plane coupling. This via-plane coupling can be reduced by adding in an adjacent ground via. When four ground vias are placed close to the signal vias, as shown in Figure 4(d), the resonant valleys completely disappear, indicating that the via-plane coupling can be completely eliminated by the four adjacent ground vias.

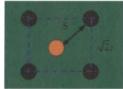

In the full frequency range as shown in Figure 4(c), an additional resonance is introduced by the adjacent ground vias, occurring at approximately 15 GHz and 22 GHz for the 150 mil spacing and 100 mil spacing cases, respectively. The same phenomenon happens in the one via cases as well as shown in Figure 4(a), although it is much less significant. This phenomenon is due to the distributed behavior caused by the spacing between the signal and ground vias. As shown in Figure 5, if assuming the four ground vias form an approximate rectangular cavity with a perfect electric conductor (PEC) boundary, the first distributed resonant frequency of the cavity can be calculated to be approximately 45 GHz, 22 GHz, and 15 GHz for the 50 mil, 100 mil, and 150 mil spacing cases, respectively, which agrees very well with the modeling result shown in Figure 4(c). The additional resonance for the 50 mil spacing case is not shown in Figure 4(c), simply because it occurs at a frequency above 40 GHz.

Figure 4: Insertion loss results, (a) one ground via case from 10 MHz to 40 GHz; (b) low-frequency zoom-in plot of Figure 4(a); (c) four ground via case from 10MHz to 40 GHz; and (d) low-frequency zoom-in plot of Figure 4(c).

Figure 5: Four ground vias form an approximate cavity with a PEC boundary.

Figure 6 shows the  $|S_{21}|$  results when there are zero, one, four, and six ground vias adjacent to the signal via. As clearly shown, there is no significant difference between the four ground via and the six ground via cases, while the difference between the one ground via and the four ground via cases is significant. This indicates that the best choice, if possible, for the number of the ground vias per signal via is four in practical designs.

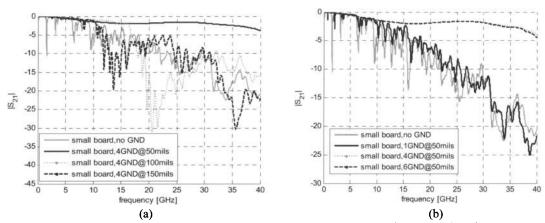

#### (2). Smaller board cases

For the smaller board (2"×1"), as shown in Figure 7, it is significantly different compared to the larger board cases that the resonant valleys are much deeper, indicating that the via-plane coupling is much stronger in the smaller board. This is because waves can easily reach the edges of the board and get reflected without much attenuation. This implies that the via-plane coupling is much stronger in a typical package geometry than in a PCB geometry, and hence the effect of the via-plane coupling shall be carefully taken into account in high-speed package designs.

Similarly, the difference between the four ground via and the six ground via cases is negligible as shown in Figure 7(b). The additional resonance caused by the distributed behavior due to the spacing between the power and ground vias are again obvious in Figure 7(a).

#### IV. CONCLUSIONS

The via-plane coupling is caused by a high-speed signal transiting through a via that penetrates a pair of parallel planes. The coupling can be reduced or eliminated by adding ground vias adjacent to the signal via. However, an additional resonance is introduced due to these adjacent ground vias. To eliminate the effect of this additional

resonance, the spacing between the signal and ground vias needs to be small enough so that the additional resonance is higher than the signal spectrum components.

Multiple ground vias are more effective in terms of reducing the via-plane coupling; however, there's no further improvement when the number of the ground vias exceeds four.

The via-plane coupling is much stronger in a typical package geometry than in a PCB; therefore it shall be carefully considered in high-speed multilayer package designs.

Figure 6: The effect of the number of the ground vias when the spacing between the signal and ground vias is 50mils for the larger board.

Figure 7: The smaller board cases, (a) four ground vias with different spacing values; and, (b) different number of ground vias at a spacing of 50mils.

#### REREFENCES

- [1] H. Chen, Q. Li, L. Tsang, "Analysis of a large number of vias and differential signaling in multilayered structures.", *IEEE transactions on microwave theory and techniques*, Vol.51, No.3, March, 2003.

- [2] X. Chang, B. Archambeault, M. Cocchini, F. De Paulis, V. Sivarajan, et al "Return via connections for extending signal link path bandwidth of via transitions", *submitted at IEEE EMC Europe*, Hamburg Germany, September, 2008.

- [3] C. Schuster, Y. Kwark, G. Selli, and P. Muthana, "Developing a 'physical' model for vias," *DesignCon 2006*, Santa Clara, CA. February, 2006

- [4] G. Selli, C. Schuster, Y. H. Kwark, M. B. Ritter, and J. L. Drewniak, "Developing a physical model for vias part II: coupled and grounded return vias," DesignCon 2007, Santa Clara, 2007.

- [5] Y.T. Lo, W. Solomon, and W.F. Richards, "Theory and experiment in microstrip antennas," IEEE Transactions on Antenna and Propagation, vol. AP-7, no.2, pp37-145, March 1979.

- [6] T. Okoshi, Y. Uehara, and T. Takeuchi, "The segmentation method—an approach to the analysis of microwave planar circuits," *IEEE Trans. Microw. Theory Tech.*, vol. MTT-24, pp. 662-668, October 1976.

- [7] Y. Zhang, F. De Paulis, and J. Fan, "Modeling multilayer power distribution network by systematically incorporating via and cavity models", *IEEE Asia-Pacific EMC week*, Singapore, May, 2008.