# Embedded-gate graphene transistors for high-mobility detachable flexible nanoelectronics

Jongho Lee, Li Tao, Yufeng Hao, Rodney S. Ruoff, and Deji Akinwande

**Applied Physics**

Letters

Citation: Appl. Phys. Lett. **100**, 152104 (2012); doi: 10.1063/1.3702570 View online: http://dx.doi.org/10.1063/1.3702570 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v100/i15 Published by the American Institute of Physics.

#### **Related Articles**

Experimental confirmation of temperature dependent negative capacitance in ferroelectric field effect transistor Appl. Phys. Lett. 100, 163504 (2012)

Improvement in the device performance of tin-doped indium oxide transistor by oxygen high pressure annealing at 150°C

Appl. Phys. Lett. 100, 162108 (2012)

Non-localized trapping effects in AlGaN/GaN heterojunction field-effect transistors subjected to on-state bias stress

J. Appl. Phys. 111, 084504 (2012)

Unipolar transport in bilayer graphene controlled by multiple p-n interfaces Appl. Phys. Lett. 100, 163115 (2012)

Detection of sulfur dioxide gas with graphene field effect transistor Appl. Phys. Lett. 100, 163114 (2012)

### Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

## ADVERTISEMENT

Downloaded 22 Apr 2012 to 128.62.145.58. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

## Embedded-gate graphene transistors for high-mobility detachable flexible nanoelectronics

Jongho Lee,<sup>1</sup> Li Tao,<sup>1</sup> Yufeng Hao,<sup>2</sup> Rodney S. Ruoff,<sup>2</sup> and Deji Akinwande<sup>1,a)</sup> <sup>1</sup>Electrical and Computer Engineering, The University of Texas, Austin, Texas 78758, USA <sup>2</sup>Mechanical Engineering and the Materials Science and Engineering Program, The University of Texas, Austin, Texas 78758, USA

(Received 13 January 2012; accepted 20 March 2012; published online 10 April 2012)

A high-mobility graphene field-effect transistor with embedded gate was fabricated on smooth spin-coated polyimide films. Electrostatic transport measurements reveal a maximum electron and hole mobility of  $4930 \text{ cm}^2/\text{V} \text{ s}$  and  $1130 \text{ cm}^2/\text{V} \text{ s}$ , respectively. Temperature dependent measurements indicate that carrier transport is not limited by intrinsic mechanisms but by charged impurities, surface roughness, and defects, suggesting that further increases in mobility are possible. The measured carrier mobilities are the highest reported for graphene transistors on polymeric substrates and hence enable high-speed devices for flexible electronics from graphene grown by size-scalable chemical vapor deposition. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.3702570]

Very fast carrier transport is one of the main attributes of monolayer graphene field-effect transistors (GFETs), an enabling feature for high-speed nanoelectronics.<sup>1</sup> Intrinsically, carrier mobilities approaching 100000 cm<sup>2</sup>/V s have been observed at room temperature on suspended devices.<sup>2</sup> The carrier mobility degrades on oxide supported GFETs, with values around 10 000 cm<sup>2</sup>/V s frequently measured on clean exfoliated graphene on SiO<sub>2</sub> in agreement with theoretical upper limits.<sup>3–5</sup> However, it is unclear how fast charge carriers can travel in monolayer graphene on polymeric substrates, an important substrate for flexible electronics. It has been suggested that remote phonon scattering from the broad continuum of modes from the polymer substrate should impact the carrier mobilities at a scale comparable to SiO<sub>2</sub>.<sup>6</sup> As graphene holds great potential for fast flexible electronics,<sup>7,8</sup> it is imperative to experimentally access its fast carrier transport on polymer supports.

In this letter, we report embedded-gate graphene fieldeffect transistors (EGFETs) realized from chemical vapor deposited (CVD) graphene with maximum carrier mobilities of 4930  $\text{cm}^2/\text{V}$  s and 1130  $\text{cm}^2/\text{V}$  s for electrons and holes, respectively. The electron mobility is comparable to peak mobilities observed for CVD graphene devices on oxidized Si with high-k dielectrics,<sup>9</sup> indicating that the fast carrier transport observed on SiO<sub>2</sub> supports is also accessible on polymeric substrates. Temperature dependent measurements on the fabricated devices indicate that charge impurity or defect scattering limits carrier transport rather than phonon scattering from the substrate. Hence, further improvement in mobility should be possible on at least some polymeric substrates as the quality and transfer of CVD graphene continue to improve. The carrier mobilities reported here are the highest observed to date for organic and carbon based transistors on flexible substrates,<sup>10,11</sup> potentially enabling high-speed flexible nanoelectronics.

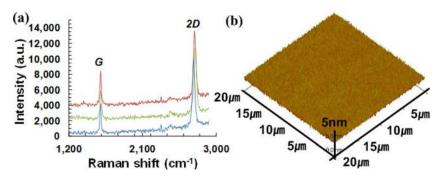

High quality monolayer graphene was synthesized by a low-pressure chemical vapor deposition (LPCVD) method on evaporated 500-nm thick copper film on a 285-nm thick thermal oxide grown on a single-crystal silicon substrate. LPCVD on Cu-coated substrates in a vertical cold-wall chamber with independent showerhead and substrate heaters yielded monolayer graphene. The sample was first annealed in a hydrogen environment for 5 min at 1000 °C, followed by exposure to methane at the same temperature. The ultra-high purity (99.999%) methane was typically flowed at 5-10 sccm for 5 min. After growth, the chamber was cooled below 180 °C before removal of the sample. Raman spectroscopy verified high-quality monolayer graphene with the following characteristics as shown in Fig. 1(a): (i) the full width at half maximum (FWHM) of the 2D-peak is  $\sim 32 \text{ cm}^{-1}$ , (ii) the 2D/G intensity ratio is 2.5-3, and (iii) the D-peak intensity is small or negligible. The conventional wet-transfer process with poly(methyl methacrylate) (PMMA) coated on graphene<sup>12</sup> was employed to transfer graphene from the Cucoated substrate onto a polyimide (PI) coated substrate.

Liquid polyimide (PI-2574 from HD Microsystems) was spin-coated on a 50-nm thick plasma-enhanced chemical vapor deposited Si<sub>3</sub>N<sub>4</sub> sacrificial layer on silicon. The 15  $\mu$ m-thick spin-coated PI affords a smooth surface with root-mean-square (RMS) roughness of <1 nm as shown in Fig. 1(b). After device fabrication, the sacrificial layer is etched to release the free-standing flexible film. The PI coated film is soft-baked at 200 °C for 30 min and subsequently cured at 300 °C for 1 h under a nitrogen atmosphere. Its high glass transition temperature (>300 °C) and high chemical resistance make it a suitable material for flexible electronics and is compatible with standard microelectronic device fabrication.<sup>13</sup>

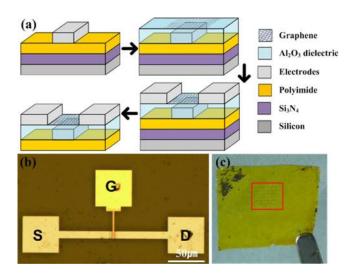

The device fabrication process is illustrated in Fig. 2(a). In brief, an array of gate electrodes were patterned on a PI-coated silicon substrate by electron-beam lithography, evaporation, and liftoff. A high-k dielectric of 20-nm thick  $Al_2O_3$  is deposited by atomic layer deposition (ALD); the estimated

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: deji@ece.utexas.edu.

gate-oxide capacitance ( $C_{ALD}$ ) measured from a test capacitor structure on the same substrate is about 179 nF/cm<sup>2</sup>. A CVD grown graphene film from a Cu/SiO<sub>2</sub>/Si growth substrate was then transferred via a conventional wet-transfer process using ammonia persulfate to etch the copper.<sup>12</sup> Oxygen plasma reactive-ion-etching (RIE) was used to pattern the active channel region while removing the superfluous graphene and ensuring channel isolation. Source and drain electrodes were defined to complete the device fabrication. The gate and source/drain metals are Ni/Au (10 nm/40 nm) and Ni (50 nm), respectively. Finally, buffered oxide etchant (BOE 6:1) was used to strip the Si<sub>3</sub>N<sub>4</sub> sacrificial layer and release the flexible polyimide film from the underlying silicon substrate.

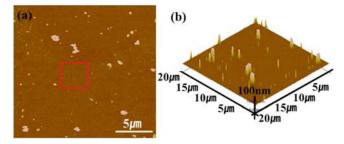

Atomic force microscope (AFM) images of the graphene area on the sample after complete device fabrication are shown in Fig. 3. The RMS surface roughness over the scanned area is 4.25 nm; the high peaks and roughness are the result of the residual resist during graphene transfer and film release. The highlighted rectangle in Fig. 3(a) is a relatively smooth local graphene area having a surface roughness of 1.9 nm. The complete removal of chemical residue is crucial for obtaining high performance transistors since the residue is detrimental to charge transport and motivates the need for cleaner transfer and fabrication methods, a pressing matter that is currently a focus of further research.<sup>14,15</sup>

FIG. 2. (a) Illustration of the EGFET fabrication process on spin-coated PI on a Si<sub>3</sub>N<sub>4</sub>/Si substrate. (b) Optical image of a completed EGFET. The device length and width are 4 and 8  $\mu$ m, respectively. (c) Photograph of the flexible substrate with an array of EGFETs. The highlighted square shows the array of devices.

FIG. 1. (a) Representative Raman spectra of monolayer graphene used for device fabrication. Raman spectra were taken with a 442 nm blue laser at three locations of the synthesized graphene on evaporated Cu film directly before transfer. (b) 3D AFM image of cured polyimide surface with surface roughness <1 nm.

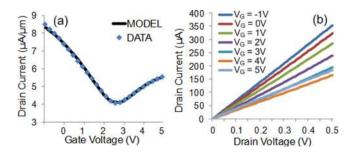

Electrostatic measurements performed under ambient conditions are presented in Fig. 4. Unintentional charge doping of graphene during the wet-transfer process<sup>14</sup> and metalinduced doping from high work-function metals<sup>16</sup> are most likely responsible for the shift of the Dirac voltage to 2.7 V. A well accepted diffusive transport model<sup>17</sup> shows good agreement with the experimental data and is employed to extract key device parameters. From the data in Fig. 4, the extracted electron and hole mobilities are 4930 cm<sup>2</sup>/V s and 1130 cm<sup>2</sup>/V s, respectively. These values are significantly higher than the previously reported GFET mobilities on flex-ible substrates<sup>7,8,18</sup> and are comparable to the highest mobility values for CVD graphene on SiO<sub>2</sub>/Si substrates.<sup>9,19–21</sup>

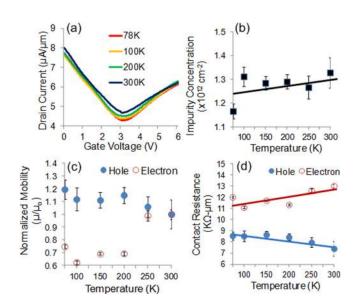

The temperature dependence of the EGFET device parameters is shown in Fig. 5. After the initial measurements, the Dirac point of the sample shifted to over 6 V due to prolonged exposure to the ambient. Before performing the temperature measurements, the sample was kept under ultrahigh vacuum ( $<10^{-8}$  Torr) for over 72 h in order to recover its initial Dirac point. Figure 5 shows the temperature dependence of the key parameters: impurity concentration, mobility, and contact resistance (R<sub>c</sub>).

As shown in Fig. 5(a), the source-drain current slightly increases as the temperature more than tripled from 78 to 300 K. At the Dirac point, current is largely determined by the transport of the (voltage-independent) residual charge concentration consisting of (i) the intrinsic thermally generated carriers which scales quadratically with temperature<sup>22</sup> and (ii) the impurity carrier density from unintentional doping which is largely temperature independent in the thermal range of interest investigated here and corroborated by the experimental profile shown in Fig. 5(b). The weak temperature dependence (<15%) at the Dirac point indicates that the impurity carrier density is mostly responsible for charge transport at the Dirac point. Indeed, the extracted impurity density (~ $1.3 \times 10^{12}$  cm<sup>-2</sup>) is almost an order of magnitude

FIG. 3. AFM images of monolayer graphene after device fabrication. (a)  $20 \,\mu\text{m} \times 20 \,\mu\text{m}$  scan, and (b) 3D image of the scanned area. The surface roughness of the highlighted rectangle is 1.9 nm.

FIG. 4. Experimental current–voltage characteristics of the EGFET. (a)  $I_D$ - $V_G$  profile with extracted electron and hole mobilities of 4930 cm<sup>2</sup>/V s and 1130 cm<sup>2</sup>/V s, respectively.  $V_D = 100 \text{ mV}$ . (b)  $I_D$ - $V_D$  curves showing linear relation.

larger than the intrinsic thermal carrier density  $(\sim 1.6 \times 10^{11} \text{ cm}^{-2})$  at 300 K, further supporting this assertion. The relatively high impurity density is an undesired outcome of unintentional doping from polymer residue during graphene transfer and device fabrication.<sup>14,15</sup> We are presently exploring several experimental routes for improved processing to overcome the high impurity doping that obscures the inherent graphene device physics.

The electron and hole carrier mobility show opposite dependence on temperature. The hole mobility can be interpreted as relatively flat or marginally decreasing with temperature. The weak dependence on temperature is a reflection of carrier scattering that is dominated by (charged or neutral) impurity scattering which is in contrast to phonon scattering that increases strongly with rising temperature and yields a proportional decrease in mobility. However, the electron mobility shows an increase with temperature particularly above 200 K, an unexpected result that has not been previously reported for GFETs. This is most likely due to Coulomb scattering from the large charge impurity density  $(\sim 1.3 \times 10^{12} \text{ cm}^{-2})$  that more strongly interacts with

FIG. 5. Temperature-dependent device characteristics. (a) ID-VG response. The initial and final measurements at 300 K are identical indicating reliability of the measurements. (b) Charge impurity density, (c) mobility normalized to the 300 K value ( $\mu$ o), and (d) contact resistance dependence on temperature. The contact resistance reported here is the total contribution from the source and drain contacts.  $\mu$ o is the reference mobility at 300 K.

electron transport in graphene. Our hypothesis is in line with conventional semiconductor device physics where a mobility increase with temperature is observed for high doping densities and is understood to result from ionized impurity scattering that grows stronger with decreasing temperature owing to the decreased thermal velocities and screening effect.<sup>23–25</sup> The temperature dependency of the screening effect has previously been generally analyzed for graphene on SiO<sub>2</sub> substrates and shown to exhibit a complex behavior that impacts the carrier transport temperature profile.<sup>23</sup> Further detailed studies are needed to shed light on the interaction of the charged impurities with graphene electrons and the specific conditions that result in mobility increase with temperature for the device structure reported here (GFET on Al<sub>2</sub>O<sub>3</sub>/PI substrates). Nonetheless, we can conclude that the carrier mobility of the EGFET is not limited by the intrinsic phonon scattering suggesting that higher mobilities are possible for flexible nanoelectronics.

The high contact resistance (including both source and drain contact contributions) seen in Fig. 5(d) reflects the poor metal graphene interface that likely includes a thin polymer interface of  $\sim 1.9$  nm, evidenced by the surface roughness in Fig. 3. The asymmetry in R<sub>c</sub> is a result of the high work-function metal contact (Ni) which affords a more transparent interface (p-p) for hole transport in contrast to electron transport that involves a p-n junction interface, hence an additional contribution to the contact resistance.26,27 Overall, drift-like behavior mostly accounts for electron transport at the metal-graphene interface resulting in the observed contact resistance increase with temperature (Fig. 5(d)). The  $\sim$ 13% increase in the electron R<sub>c</sub> compares well with the  $\sim 20\%$  increase reported for much lower contact resistance devices made from exfoliated graphene.<sup>28</sup> In contrast, the hole R<sub>c</sub> exhibits a slight decrease with increasing temperature suggesting that thermionic or thermionicfield tunneling,<sup>29</sup> across a barrier (e.g., the thin polymer interface mentioned earlier) is a significant transport mechanism. However, the very weak temperature dependence (differences are within the measurement/extraction uncertainty) might be due to the near cancellation of the temperature dependence of two competing mechanisms including thermionic and drift-like transport, where the former and latter increase and decrease with temperature, respectively.

In conclusion, we have achieved record mobilities of  $4930 \text{ cm}^2/\text{V}$  s and  $1130 \text{ cm}^2/\text{V}$  s, respectively, for electron and hole transport in graphene transistors with high-k dielectrics on polyimide sheets. The device physics have been elucidated indicating further improvements in charge transport is achievable with better fabrication processes. Our work reveals that graphene electrical devices on polymeric substrates are promising for high-speed flexible electronics.

This work is supported by an ONR Grant in the program of Dr. Chagaan Baatar.

- <sup>1</sup>F. Schwierz, Nat. Nanotechnol. 5(7), 487 (2010).

- <sup>2</sup>N. Tombros, A. Veligura, J. Junesch, J. Jasper van den Berg, P. J. Zomer, M. Wojtaszek, I. J. Vera Marun, H. T. Jonkman, and B. J. van Wees, J. Appl. Phys. **109**(9), 093702 (2011).

- <sup>3</sup>B. Fallahazad, K. Lee, S. Kim, C. Corbet, and E. Tutuc, in *69th Annual Device Research Conference* (DRC, Santa Barbara, CA, 2011), p. 35.

- <sup>4</sup>J.-H. Chen, C. Jang, S. Xiao, M. Ishigami, and M. S. Fuhrer, Nat. Nanotechnol. 3(4), 206 (2008).

- <sup>5</sup>V. Perebeinos and P. Avouris, Phys. Rev. B 81(19), 195442 (2010).

- <sup>6</sup>S. Fratini and F. Guinea, Phys. Rev. B 77(19), 195415 (2008).

- <sup>7</sup>O. M. Nayfeh, IEEE Electron Device Lett. **32**(10), 1349 (2011).

- <sup>8</sup>J.-H. Chen, M. Ishigami, C. Jang, D. R. Hines, M. S. Fuhrer, and E. D. Williams, Adv. Mater. **19**(21), 3623 (2007).

- <sup>9</sup>X. Li, W. Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee, L. Colombo, and R. S. Ruoff, Science **324**(5932), 1312 (2009).

- <sup>10</sup>C.-Y. Wei, S.-H. Kuo, Y.-M. Hung, W.-C. Huang, F. Adriyanto, and Y.-H. Wang, IEEE Electron Device Lett. **32**(1), 90 (2011).

- <sup>11</sup>E. S. Snow, P. M. Campbell, M. G. Ancona, and J. P. Novak, Appl. Phys. Lett. 86(3), 033105 (2005).

- <sup>12</sup>X. Li, Y. Zhu, W. Cai, M. Borysiak, B. Han, D. Chen, R. D. Piner, L. Colombo, and R. S. Ruoff, Nano Lett. 9(12), 4359 (2009).

- <sup>13</sup>L. Tao, J. Lee, and D. Akinwande, J. Vac. Sci. Technol. B 29(6), 06FG07 (2011).

- <sup>14</sup>A. Pirkle, J. Chan, A. Venugopal, D. Hinojos, C. W. Magnuson, S. McDonnell, L. Colombo, E. M. Vogel, R. S. Ruoff, and R. M. Wallace, Appl. Phys. Lett. **99**(12), 122108 (2011).

- <sup>15</sup>X. Liang, B. A. Sperling, I. Calizo, G. Cheng, C. A. Hacker, Q. Zhang, Y. Obeng, K. Yan, H. Peng, Q. Li, X. Zhu, H. Yuan, A. R. Hight Walker, Z. Liu, L.-M. Peng, and C. A. Richter, ACS Nano 5(11), 9144 (2011).

- <sup>16</sup>G. Giovannetti, P. Khomyakov, G. Brocks, V. M. Karpan, J. van den Brink, and P. Kelly, Phys. Rev. Lett. **101**(2), 026803 (2008).

- <sup>17</sup>S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, Appl. Phys. Lett. **94**(6), 062107 (2009).

- <sup>18</sup>B. J. Kim, H. Jang, S.-K. Lee, B. H. Hong, J.-H. Ahn, and J. H. Cho, Nano Lett. **10**(9), 3464 (2010).

- <sup>19</sup>A. Venugopal, J. Chan, X. Li, C. W. Magnuson, W. P. Kirk, L. Colombo, R. S. Ruoff, and E. M. Vogel, J. Appl. Phys. **109**(10), 104511 (2011).

- <sup>20</sup>M. E. Ramón, A. Gupta, C. Corbet, D. A. Ferrer, H. C. P. Movva, G. Carpenter, L. Colombo, G. Bourianoff, M. Doczy, D. Akinwande, E. Tutuc, and S. K. Banerjee, ACS Nano 5(9), 7198 (2011).

- <sup>21</sup>J. Heo, H.-J. Chung, S.-H. Lee, H. Yang, J. Shin, U.-I. Chung, and S. Seo, in 69th Annual Device Research Conference (DRC, Santa Barbara, CA, 2011), p. 31.

- <sup>22</sup>H.-S. P. Wong and D. Akinwande, *Carbon Nanotube and Graphene De*vice Physics (Cambridge University Press, 2011).

- <sup>23</sup>T. Ando, J. Phys. Soc. Jpn. **75**(7), 074716 (2006).

- <sup>24</sup>D. B. M. Klaassen, Solid-State Electron. **35**(7), 961 (1992).

- <sup>25</sup>T. T. Mnatsakanov, M. E. Levinshtein, L. I. Pomortseva, and S. N. Yurkov, Semicond. Sci. Technol. **17**(9), 974 (2002).

- <sup>26</sup>B. Huard, N. Stander, J. A. Sulpizio, and D. Goldhaber-Gordon, Phys. Rev. B 78(12), 121402 (2008).

- <sup>27</sup>K. Nagashio, T. Nishimura, K. Kita, and A. Torìi, in *IEEE International Electron Devices Meeting* (IEDM, Baltimore, MD, 2009), p. 1.

- <sup>28</sup>F. Xia, V. Perebeinos, Y.-M. Lin, Y. Wu, and P. Avouris, Nat. Nanotechnol. 6(3), 179 (2011).

- <sup>29</sup>F. A. Padovani and R. Stratton, Solid-State Electron. 9(7), 695 (1966).