# Embedded Pitch Adapters: a High-Yield Interconnection Solution for Strip Sensors

| 3                | M. Ullán <sup>d</sup> *, P.P. Allport <sup>a</sup> , M. Baca <sup>a</sup> , J. Broughton <sup>a</sup> , A. Chisholm <sup>a</sup> , K. Nikolopoulos <sup>a</sup> , S. Pyatt <sup>a</sup> ,                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                | J.P. Thomas <sup>a</sup> , J.A.Wilson <sup>a</sup> , J. Kierstead <sup>b</sup> , P. Kuczewski <sup>b</sup> , D. Lynn <sup>b</sup> , L.B.A. Hommels <sup>c</sup> , C. Fleta <sup>d</sup> ,                                           |

| 5                | J. Fernandez-Tejero <sup>d</sup> , D. Quirion <sup>d</sup> , I. Bloch <sup>e</sup> , S. Díez <sup>e</sup> , I.M. Gregor <sup>e</sup> , K. Lohwasser <sup>e</sup> , L. Poley <sup>e</sup> ,                                          |

| 6                | K. Tackmann <sup>e</sup> , M. Hauser <sup>f</sup> , K. Jakobs <sup>f</sup> , S. Kuehn <sup>f</sup> , K. Mahboubi <sup>f</sup> , R. Mori <sup>f</sup> , U. Parzefall <sup>f</sup> , A. Clark <sup>g</sup> ,                          |

| 7                | D. Ferrere <sup>g</sup> , S. Gonzalez Sevilla <sup>g</sup> , J. Ashby <sup>h</sup> , A. Blue <sup>h</sup> , R. Bates <sup>h</sup> , C. Buttar <sup>h</sup> , F. Doherty <sup>h</sup> ,                                              |

| 8                | T. McMullen <sup>h</sup> , F. McEwan <sup>h</sup> , V. O'Shea <sup>h</sup> , S. Kamada <sup>i</sup> , K. Yamamura <sup>i</sup> , Y. Ikegami <sup>j</sup> , K. Nakamura <sup>j</sup> ,                                               |

| 9                | Y. Takubo <sup>j</sup> , Y. Unno <sup>j</sup> , R. Takashima <sup>k</sup> , A. Chilingarov <sup>l</sup> , H. Fox <sup>l</sup> , A.A. Affolder <sup>m</sup> , G. Casse <sup>m</sup> ,                                                |

| 10               | P. Dervan <sup>m</sup> , D. Forshaw <sup>m,1</sup> , A. Greenall <sup>m</sup> , S. Wonsak <sup>m</sup> , M. Wormald <sup>m</sup> , V. Cindro <sup>n</sup> , G. Kramberger <sup>n</sup> ,                                            |

|                  |                                                                                                                                                                                                                                     |

| 11               | I. Mandić <sup>n</sup> , M. Mikuž <sup>n</sup> , I. Gorelov <sup>o</sup> , M. Hoeferkamp <sup>o</sup> , P. Palni <sup>o</sup> , S. Seidel <sup>o</sup> , A. Taylor <sup>o</sup> , K. Toms <sup>o</sup> ,                            |

| 12               | R. Wang <sup>o</sup> , N.P. Hessey <sup>p</sup> , N. Valencic <sup>p</sup> , K. Hanagaki <sup>q,j</sup> , Z. Dolezal <sup>r</sup> , P. Kodys <sup>r</sup> , J. Bohm <sup>s</sup> ,                                                  |

| 13               | M. Mikestikova <sup>s</sup> , A. Bevan <sup>t</sup> , G. Beck <sup>t</sup> , C. Milke <sup>u</sup> , M. Domingo <sup>u</sup> , V. Fadeyev <sup>u</sup> , Z. Galloway <sup>u</sup> ,                                                 |

| 14               | D. Hibbard-Lubow <sup>u</sup> , Z. Liang <sup>u</sup> , H. FW. Sadrozinski <sup>u</sup> , A. Seiden <sup>u</sup> , K. To <sup>u</sup> , R. French <sup>v</sup> , P. Hodgson <sup>v</sup> ,                                          |

| 15               | H. Marin-Reyes <sup>v</sup> , K. Parker <sup>v</sup> , O. Jinnouchi <sup>w</sup> , K. Hara <sup>x,y</sup> , J. Bernabeu <sup>z</sup> , J.V. Civera <sup>z</sup> , C. Garcia <sup>z</sup> ,                                          |

| 16               | C. Lacasta <sup>z</sup> , S. Marti i Garcia <sup>z</sup> , D. Rodriguez <sup>z</sup> , D. Santoyo <sup>z</sup> , C. Solaz <sup>z</sup> , U. Soldevila <sup>z</sup>                                                                  |

| 17               |                                                                                                                                                                                                                                     |

| 18               | <sup>a</sup> School of Physics and Astronomy, University of Birmingham, Birmingham B15 2TT, United Kingdom                                                                                                                          |

| 19<br>20         | <sup>b</sup> Brookhaven National Laboratory, Physics Department and Instrumentation Division, Upton, NY 11973-5000, USA                                                                                                             |

| 20               | <sup>c</sup> Cavendish Laboratory, University of Cambridge, JJ Thomson Avenue, Cambridge CB3 0HE, United Kingdom<br><sup>d</sup> Centro Nacional de Microelectronica (IMB-CNM, CSIC), Campus UAB-Bellaterra, 08193 Barcelona, Spain |

| $\frac{21}{22}$  | <sup>e</sup> DESY, Notkestrasse 85, 22607 Hambrug, Germany                                                                                                                                                                          |

| $\bar{2}\bar{3}$ | <sup>f</sup> Physikalisches Institut, Universitä <sup>*</sup> t Freiburg, Hermann-Herder-Str. 3, D-79104 Freiburg, Germany                                                                                                          |

| 24               | <sup>8</sup> DPNC, University of Geneva, 24, Quai Ernest-Ansermet, CH-1211 Genve 4, Switzerland                                                                                                                                     |

| 25               | <sup>h</sup> SUPA- School of Physics and Astronomy, University of Glasgow, Glasgow G12 8QQ, United Kingdom                                                                                                                          |

| 26               | <sup>i</sup> Solid State Div., Hamamatsu Photonics K.K., 1126-1, Ichino-cho, Higashi-ku, Hamamatsu-shi, Shizuoka 435-8558,                                                                                                          |

| 27               | Japan                                                                                                                                                                                                                               |

| 28<br>29         | <sup>j</sup> Institute of Particle and Nuclear Study, KEK, Oho 1-1, Tsukuba, Ibaraki 305-0801, Japan<br><sup>k</sup> Department of Science Education, Kyoto University of Education, Kyoto 612-8522, Japan                          |

| 30               | <sup>1</sup> Physics Department, Lancaster University, Lancaster LA1 4YB, United Kingdom                                                                                                                                            |

| 31               | <sup>m</sup> Oliver Lodge Laboratory, Department of Physics, University of Liverpool, Oxford St., Liverpool L69 7ZE, United                                                                                                         |

| 32               | Kingdom                                                                                                                                                                                                                             |

| 33               | <sup>n</sup> Joz <sup>*</sup> ef Stefan Institute and Department of Physics, University of Ljubljana, Ljubljana, Slovenia                                                                                                           |

| 34               | <sup>o</sup> Department of Physics and Astronomy, University of New Mexico, MSC07 4220, 1919 Lomas Blvd. NE, Albuquerque,                                                                                                           |

| 35               | NM 87131, USA                                                                                                                                                                                                                       |

| 36<br>37         | <sup>p</sup> Nikhef, Science Park 105, 1098 XG Amsterdam, Netherlands<br><sup>q</sup> Department of Physics, Osaka University, Machikaneyama-cho 1-1, Toyonaka-shi, Osaka 560-0043, Japan                                           |

| 38               | <sup>1</sup> Charles University in Prague, Faculty of Mathematics and Physics, V Holesovickach 2, Prague 8, Czech Republic                                                                                                          |

| 39               | <sup>s</sup> Academy of Sciences of the Czech Republic, Institute of Physics, Na Slovance 2, 18221 Prague 8, Czech Republic                                                                                                         |

| 40               | <sup>t</sup> School of Physics and Astronomy, Queen Mary University of London, London E1 4NS, United Kingdom                                                                                                                        |

| 41               | "Santa Cruz Institute for Particle Physics (SCIPP), University of California, Santa Cruz, CA 95064, USA                                                                                                                             |

| 42               | <sup>v</sup> Department of Physics and Astronomy, The University of Sheeld, Hicks Building, Hounsfield Road, S3 7RH Sheeld,                                                                                                         |

| 43<br>44         | United Kingdom                                                                                                                                                                                                                      |

| 44<br>45         | <sup>w</sup> Institute of Science and Engineering, Tokyo Institute of Technology, Ookayama 2-12-1, Meguro-ku, Tokyo 152-8551,<br>Japan                                                                                              |

| 46               | <sup>x</sup> Institute of Pure and Applied Sciences, University of Tsukuba, Tsukuba, Ibaraki 305-8751, Japan                                                                                                                        |

| 47               | <sup>y</sup> Center for Integrated Research in Fundamental Science and Engineering, University of Tsukuba, Tsukuba, Ibaraki 305-                                                                                                    |

| 48               | 8571 Japan                                                                                                                                                                                                                          |

| 49               | <sup>z</sup> IFIC/CSIC-UVEG, Ed. Inst. Investigacion, PO Box 22085, 46071 Valencia, Spain                                                                                                                                           |

| 50               |                                                                                                                                                                                                                                     |

| 51               |                                                                                                                                                                                                                                     |

<sup>\*</sup> Corresponding author: e-mail: miguel.ullan@imb-cnm.csic.es, Ph: +34 935947700, Fax: +34 935800267

<sup>&</sup>lt;sup>1</sup> Now at Syracuse University

#### Abstract

2 A proposal to fabricate large area strip sensors with integrated, or embedded, pitch adapters is 3 presented for the End-cap part of the Inner Tracker in the ATLAS experiment. To implement the 4 embedded pitch adapters, a second metal layer is used in the sensor fabrication, for signal routing to 5 the ASICs. Sensors with different embedded pitch adapters have been fabricated in order to optimize 6 the design and technology. Inter-strip capacitance, noise, pick-up, cross-talk, signal efficiency, and 7 fabrication yield have been taken into account in their design and fabrication. Inter-strip capacitance 8 tests taking into account all channel neighbors reveal the important differences between the various 9 designs considered. These tests have been correlated with noise figures obtained in full assembled 10 modules, showing that the tests performed on the bare sensors are a valid tool to estimate the final noise in the full module. The full modules have been subjected to test beam experiments in order to 11 evaluate the incidence of cross-talk, pick-up, and signal loss. The detailed analysis shows no 12 indication of cross-talk or pick-up as no additional hits can be observed in any channel not being hit 13 14 by the beam above 170 mV threshold, and the signal in those channels is always below 1% of the 15 signal recorded in the channel being hit, above 100 mV threshold. First results on irradiated minisensors with embedded pitch adapters do not show any change in the interstrip capacitance 16 17 measurements with only the first neighbors connected.

18

19

*Keywords: Silicon radiation detectors; Strip sensors; HL-LHC; ATLAS Upgrade; ITk; Pitch adapters.*

20

# 21 1. INTRODUCTION AND MOTIVATION

22 The interconnection of sensors and readout electronics is a subject of critical impact in the module design for High Energy Physics experiments, such as ATLAS. The sensors are made progressively 23 24 larger, and the readout ASICs smaller, and both contain increasingly more channels. On the other 25 hand, the pitch between bonding pads is usually very different between sensors and ASICs, which 26 leads to unrealizable wire-bonding angles between them. With all this, the actual design of the 27 electrical connection between sensors and ASICs is not trivial and it becomes a yield issue when the experiment contains tens or hundreds of millions of strip channels. The question is not anymore if 28 29 the wire-bonding can be done, but if it can be done reliably enough to build a whole tracker in the 30 required production time.

31

32 In the case of the current ATLAS experiment the interconnection was solved by adding external 33 pitch adapters which facilitated the bonding at both sides, sensor and ASIC, and made the pitch adaptation by routing with metal tracks on a high-density metal-on-glass technology [1]. The 34 35 downside of this solution is that, although the bonding is very much facilitated, the number of bonds is doubled. On top of that, an extra piece is added to the module, increasing the total mass, assembly 36 37 complexity, and costs. The groups involved in the developments of the ATLAS Upgrade Inner Tracker (ITk) want to avoid this solution. Several studies have been made in order to identify the 38 39 maximum angle that can be achieved by direct wire-bonding between detectors' and ASICs' bonding 40 pads [2]. Angles below 20° are considered safe, which results in that direct wire-bonding can be used 41 for the barrel design, but for the End-cap a solution might be needed due to the larger pitch variations 42 in the 6 different sensor layouts [3].

43

In this paper, a proposal to fabricate large-area strip sensors with integrated, or embedded, pitch adapters is presented for the End-cap part of the Inner Tracker in the ATLAS experiment. To

- 45 adapters is presented for the End-cap part of the Inner Tracker in the ATLAS experiment. To 46 implement the embedded pitch adapters (EPA), a second metal layer is used at the end of the sensor

- fabrication in order to form additional metal tracks which contact the top metal of the strip's

- 48 coupling capacitor (where the standard AC pad is) with an "embedded pad" that is placed on the

1 sensor right in front of the corresponding ASIC pad. In this way, the routing for the pitch adaptation 2 from sensor to ASIC is done on the sensor itself, and direct bonding from sensor to ASIC is 3 facilitated without the need to double the number of wire-bonds, making the wire-bonding faster and

- 4 more reliable.

- 5

6 Nevertheless, there are some possible effects that have to be taken into account in the evaluation and 7 use of the EPA:

8 Inter-strip Capacitance: An increase of the inter-strip capacitance can be expected from the 9 increase of the total metal length and from the additional coupling of the second-metal tracks 10 with each other and with the first-metal tracks, especially taking into account that the secondmetal tracks have to cross over several first-metal tracks. This increase in the inter-strip 11 capacitance implies an increase in the overall noise, thus the sensor channels with EPA will 12 13 show more noise than the standard one-metal channels. Also, as the inter-strip capacitance in the EPA will depend strongly on the particular design, the noise can also vary from channel to 14 15 channel, resulting in larger *noise variability* through the sensor.

16 **Cross-talk**: Signal transmitted between first-metal tracks (standard detector strip metal) and 17 second-metal tracks (EPA metal) due to the coupling between them. This can result in spurious 18 signals in not hit channels and in loss of signal (*efficiency*) for the hit channel.

- Pick-up: Charge that can be induced in the second-metal tracks directly from the bulk when a particle crosses the sensor and charge is created in the bulk. This can also induce spurious signals in channels that are away from the actual hit channel and in loss of signal (*efficiency*) for the hit channel.

- **Yield**: From a technological point of view, as there is an increase of the number and length of tracks plus the addition of an extra photolithographic step with the EPA, this could increase the probability of a short-circuit between channels, or an open circuit in a channel during the processing. This means a possible reduction in the number of good channels per sensor, and consequently also a possible reduction of the number of good sensors in a whole production.

- 28

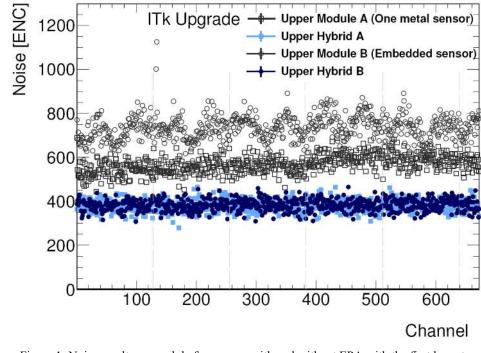

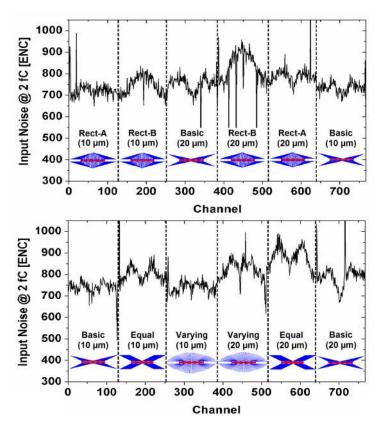

29 The EPA have been implemented on the sensors fabricated for the prototype of the End-cap part of 30 the ATLAS Upgrade Inner Tracker (ITk), the "petalet" [4][5]. Initial results on these sensors, which had first-generation layout designs, have shown no indication of cross-talk or pick-up from laser tests 31 32 [6]. Nevertheless an increase in noise and noise variability has been observed in the first modules 33 fabricated with those sensors as can be seen in Fig 1, where the noise results for petalet modules 34 made with and without the first designs of EPA are shown. These tests were taken using threshold scans on a digital readout system to determine the noise level in electron noise equivalent. Fig 1 35 shows the noise per channel comparing typical sensors of "One metal" and "Embedded" designs. 36 37 The electrical noise stemming from the readout system alone (without the sensors) is 380 +/- 10 ENC and has not been subtracted in the figure. For a typical one-metal sensor, the ENC noise is 550 38 with a deviation of at most 50 ENC. Six sensors with EPA have been built into modules and showed 39 40 consistent behavior as seen in Fig. 1

Figure 1: Noise results on module for sensors with and without EPA with the first layouts implemented.

1

#### 5 2. DESIGN OF THE EMBEDDED PITCH ADAPTERS

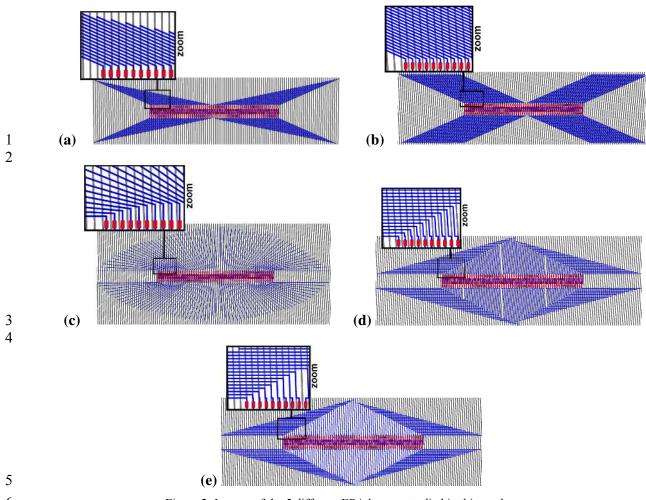

6 In view of the results just mentioned about noise variability across the detector due to the different 7 inter-strip capacitance in each channel for the initial design, 4 new layouts were designed in order to 8 attempt reducing this variability and the rest of effects mentioned above. Fig 2 shows the 5 layouts 9 that have been tried.

- 10 (a) Basic: This is the first layout made for the initial batches and tests. The second-metal tracks 11 keep the same angle (in each quadrant), i.e. they are parallel to each other, and this angle is 12 the maximum that can be used for a minimum separation between tracks of 20 µm. This distance is chosen as a small but technologically safe distance between tracks in order not to 13 14 compromise the yield.

- 15 (b) Equalized: In this layout the second-metal tracks are parallel as in the *Basic*, but they are 16 enlarged in order for them all to have the same length. This is done to equalize the inter-strip 17 capacitance between all the channels and to avoid the variability in the noise.

- 18 (c) Varying: In this layout the second-metal tracks have a constant angle with respect to each 19 other. This angle is calculated so that they occupy all the 360 degrees  $(180^{\circ} / 63 = 2.86^{\circ})$ . In 20 this way, the channels will be separated from each other, reducing their inter-strip 21 capacitance. The channels are also enlarged in the center to make them have roughly the 22 same length.

- (d) Rectangular-A: In this case, the second-metal channels go parallel to the first-metal channels 24 from the pads until they can cross perpendicularly to them to reach their corresponding 25 contact. The second-metal channels go in between the first-metal ones, and on top of the p-26 stop. In this way, the inter-strip capacitance to the first-metal channels is minimized.

- (e) *Rectangular-B*: In this case, the second-metal channels go parallel to the first-metal channels, 28 but on top of them. This layout is more like a test structure (a worst-case) because in this case the inter-strip capacitance will be increased, although maybe the pick-up is minimized.

29 30

27

Figure 2: Images of the 5 different EPA layouts studied in this work.

8 Additionally, there are two options of each of these layouts: one in which the second-metal tracks 9 have 20  $\mu$ m width (as in the first designs), and another in which there tracks have 10  $\mu$ m width. This 10 second case is still far from the resolution limits of the technology but will allow a lower coupling 11 between metal tracks.

11 12

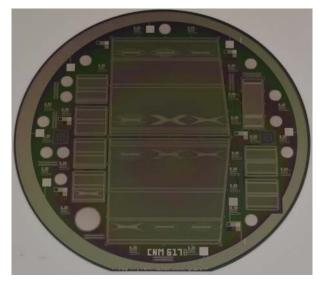

13 All these layouts of EPA were added in a new full wafer mask which includes the two TOP sensors 14 of the petalet prototype [4]. Each of these sensors has 2 strip rows and each strip row has 384 15 channels. The strip pitch in these sensors is variable, because the channels are oriented toward the 16 beam in the End-cap part of the ITK, plus the strips are designed with built-in stereo angle. The strip pitch ranges then roughly from 93 µm to 104 µm across these sensors. The chips used for the readout 17 in the petalet prototypes are the so-called ABC250 [7] which have 128 readout channels and pads 18 19 staggered in two rows with constant pitch of 50 µm. Therefore there is room for 12 EPA in the whole 20 wafer. One sensor (TOP-Left) includes the 5 EPA layouts with 20 µm track width, plus one basic 21 design with 10 µm track width; and the other sensor (TOP-right) includes the 5 EPA layouts with 10 22  $\mu$ m track width, plus one basic design with 20  $\mu$ m track width. The full wafer design can be seen in 23 Fig 3.

24

# 25 3. TECHNOLOGY AND FABRICATION

1 One full batch of TOP petalet sensors have been fabricated in the clean room of the Centro Nacional 2 de Microelectronica (IMB-CNM, CSIC), Barcelona, Spain. High-resistivity, p-type, 300 µm thick wafers with 4 inches diameter have been used as substrates. The "standard" first-metal tracks, which 3 are the top plate of the coupling capacitors, are made with a 0.5 µm thick sputtered Aluminum layer. 4 5 The inter-metal oxide layer is deposited by a low-temperature Plasma Enhanced Chemical Vapor 6 Deposition (PECVD) processing step. Four different inter-metal oxide thicknesses have been 7 implemented in order to see the influence of this parameter and to study the technological 8 difficulties. Finally, the second-metal tracks are made with a sputtered Aluminum layer which is 1.5 9 um thick. A picture of one of the fabricated wafers is shown in Fig 3, where the different EPA designs can be clearly seen.

- 10

- 11

12 13

14

15

Figure 3: Picture of one of the wafers fabricated in the batch of TOP petalet sensors with the five EPA layouts, including also different mini-sensors and test structures.

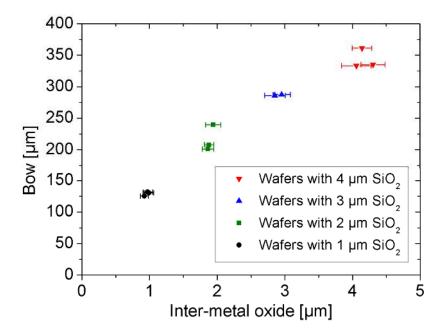

16 Due to the different thermal expansion coefficients of silicon oxide and silicon, the inter-metal oxide layer creates stress. Many yield issues in multilevel technologies are related to stress [8]: cracking of 17 18 dielectric layers, hillocks or stress voiding in aluminum lines, etc. These have not been observed 19 during fabrication. We will therefore focus on the resulting wafer bowing which can affect the 20 subsequent photolithographic steps, because it interferes with the alignment marks that are defined 21 before and after the inter-metal oxide. The bowing of the sensors can also affect the assembly of the 22 whole module, plus position resolution can be compromised. All this limits the inter-metal oxide 23 thickness that can be used for the EPA fabrication. Consequently, the bowing of the different wafers 24 was monitored during the fabrication of the sensors. Fig. 4 shows the results of wafer bowing tests 25 for the different inter-metal oxide thicknesses. The bow is defined here, according to standards [9], 26 as the distance between a point at wafer center, and a reference plane defined by three points at the 27 wafer edges. Note that the bow can be positive or negative, which results respectively from compressive or tensile stress. In our case, the bow is positive because the stress from the inter-metal 28 29 oxide is compressive. As it can be seen, the bowing is already very significant (roughly 300 µm) 30 with 3 µm thick oxide, and although the photolithography could be realized without problems, this bowing would be too large for the proper assembly of the modules, and for particle position 31 32 resolution for the tracking. In the case of 4  $\mu$ m oxide thickness, the bowing of the wafers already 33 generated difficulties in the processing, so this option is discarded already for technological reasons. 34

Figure 4: Wafer bowing as a function of the inter-metal oxide thickness for all the wafers fabricated.

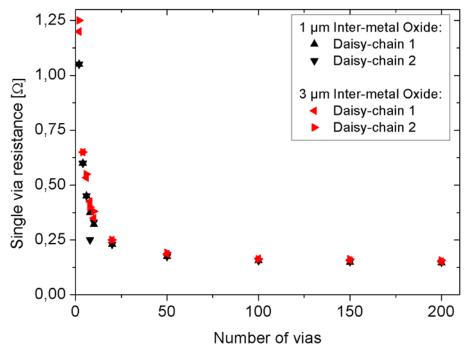

5 The quality of the via contact between the second metal and the first metal was also checked in order 6 to find out if this affects the yield of good channels in the sensors. Daisy-chain test structures 7 including more than 200 vias were implemented in the wafer design for this purpose. The daisy 8 chains are just series of vias connected in series such that the first via goes from metal 2 to metal 1, 9 then a short line of metal 1 connects to the next via which goes from metal 1 to metal 2, then a short 10 line of metal 2 connects to the next via with goes from metal 2 to metal 1, and so forth. Fig 5 shows 11 the results obtained for the via resistance when different number of vias are measured in series. As it 12 can be seen, the value stabilizes very nicely at about 0.18 Ohms/via for high number of vias series, 13 when the influence of parasitic resistances from the setup becomes negligible (high number of vias 14 measured in series). The resistance value is independent of the inter-metal oxide thickness, indicating 15 a very good fill of the via contact with the metal. Regarding yield, not a single daisy-chain failure was found in measurements of 200 vias in series, measuring at least 2 daisy chains per wafer in all 16 17 the wafers. The daisy chain test structures could not be distributed across the wafer, as it would have 18 been optimal, due to layout limitations. The structures were placed only on one side, not very close 19 to the center of the wafer. It has to be mentioned that a technological problem was found in the thick 20 oxide wafers, where an incomplete etching of the vias produced defective contact from second to 21 first metal in the center of the wafers. This is due to the combined inhomogeneity of the oxide 22 deposition and etching process, and can be easily corrected by a controlled via over etch. Still, this is 23 not considered a via yield problem, as the vias that are correctly etched make a correct low-resistance 24 contact with no-measurable statistical failure.

Figure 5: Values of the via resistance obtained from measurements of resistance of daisychains of vias in series, and for different number of vias. As it can be seen, when the number of vias in series is too small the error in the result is large because the parasitic resistances of the measurement become relevant Measurements shown for different daisychains and for different inter-metal oxide thicknesses.

1

#### 8 4. INTER-STRIP CAPACITANCE TESTS

As explained above, the use of an additional second-metal track on every channel in order to make the connectivity and pitch adaptation to the ASIC, can produce an increase in the inter-strip capacitance of the channel. This will result in an increase of the noise per channel. Additionally, the inter-strip capacitance will vary from channel to channel as the second-metal track is in principle different for every channel, and so will do the noise, increasing the noise variability. In order to control that and to identify the differences between the five EPA layouts with respect to noise, interstrip capacitance has to be measured for all the channels.

16

17 On the other hand, one specific feature of the EPA is that the second-metal channels cross on top of 18 many of the first-metal channels, increasing the coupling between channels that are far from each 19 other in the sensor, the "far neighbors". This implies that the usual way of testing inter-strip 20 capacitance by measuring it only with respect of the 2 or 4 neighbors, is not a good approximation in 21 this case. A test of the inter-strip capacitance of every channel has to take into account all the rest of 22 the channels, "all neighbors", in order to have a proper measurement. Only this way the channel 23 noise variability could be deduced from the inter-strip capacitance tests. For this purpose, a probe 24 card with 128 probes has been used for inter-strip capacitance tests in this work. Only this way, the 25 correct capacitance measurement can be done between the strip under tests and all the rest of the channels that are purposely grounded. In practice, our switching matrix has only 24 input channels, 26 27 therefore the strips are measured in groups of 20, by moving the probe card across the EPA pads. But 28 with the 128 probe card we can be assured that all the relevant neighbor channels (the ones that can 29 cross the strips under test) are grounded during the measurement. The measurements have been 30 performed using and Agilent 4284A LCR meter. A correction has been applied to all the 1 measurements individually. Before probing the pads, a capacitance measurement is performed in the 2 active probes without connecting the probe card to anything ('OPEN' configuration). This value 3 is recorded for each probe and subtracted for every individual capacitance measurement that is taken 4 with this particular probe.

5

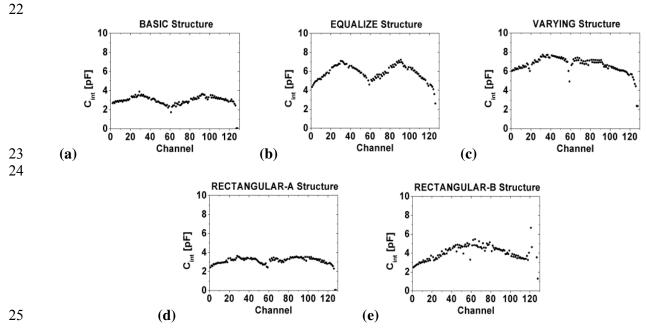

6 The results of the inter-strip capacitance tests for the 5 EPA structures fabricated according to the 5 7 layouts described above using 20 µm track width can be seen in Fig 6. In the first plot (a) one can 8 confirm that the inter-strip capacitance reproduces qualitatively the noise shape shown in Fig 1 for 9 modules assembled with the first EPA layout implemented. The second plot (b) reveals that although 10 the number of crossings between second metal and first metal and the total track length is made the same in this layout for all the channels, the coupling of the second-metal tracks with far neighbors is 11 12 dominant because of the short separation between tracks, therefore, the channels with more 13 neighbors show increased inter-strip capacitance, actually enhancing the undesired shape of the *Basic* layout. The third plot (c) shows that with the *Varying* layout, the inter-strip capacitance is 14 15 "equalized" in the center of the structure with respect to the *Basic* structure, but the inter-strip 16 capacitance reduction at the structure edges keeps its variability. The forth plot (d) shows the best 17 equalization on inter-strip capacitance achieved with all structures, corresponding to the 18 Rectangular-A layout. The fact that the second-metal tracts are quite separated from each other and 19 from first-metal tracks, seems to be the dominant influence in this result. Finally, the fifth plot (e) 20 shows the expected behavior of the *Rectangular-B* layout where the fact that the central tracks are on 21 top of the first-metal tracks for long distances, increases the inter-strip capacitance for them.

26 27

28

Figure 6: Inter-strip capacitance tests results for the 5 EPA layouts with 20 μm track width. (a) *Basic*, (b) *Equalize*, (c) *Varying*, (d) *Rectangular-A*, and (d) *Rectangular-B*

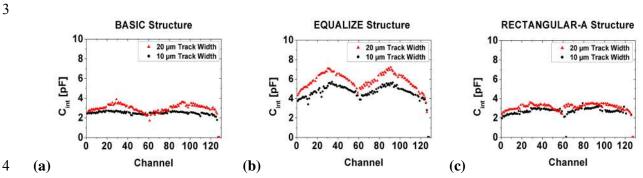

Fig 7 represents the differences in inter-strip capacitance for 3 selected structures for second-metal track width of 20 or 10  $\mu$ m. As can be seen in the first plot (a) the variability of the *Basic* layout is quite improved when the track width is reduced due to the important reduction in second-metal tracks coupling with each other when the track width is halved while maintaining the track pitch, which has effectively increased the track separation by a 50%. The same effect is observed, although enhanced, in the *Equalize* structure (b), where the inter-strip capacitance variability has been quite reduced. Finally, *Rectangular-A* structure shows only a small effect of the track width reduction on

2 inter-strip capacitance, as the separation between tracks is already large with 20 µm track width.

5 6

7

Figure 7: Inter-strip capacitance results for 20 and 10 µm track width for different structures: (a) Basic, (b) Equalize, and (c) Rectangular-A

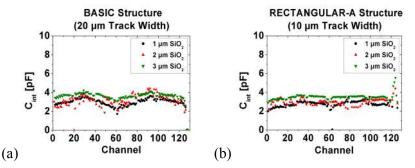

8 Finally, Fig 8 shows the effect of inter-metal oxide thickness on the inter-strip capacitance in *Basic* 9 and *Rectangular-A* layouts. In plot (a) one can see that the increase in inter-metal oxide does not 10 have an effect in the inter-strip capacitance variability. This agrees with the fact that the inter-strip capacitance variability in the Basic layout comes mainly from the second-metal tracks coupling to 11 12 each-other, and not with the coupling with the first-metal tracks. In plot (b) it can be seen that the 13 inter-strip capacitance in *Rectangular-A* is flattened even more, resulting in quite a flat plot, reducing 14 very much the variability. This is consistent with the fact that the inter-strip capacitance in 15 Rectangular-A layout is mostly dependent on first metal to second metal coupling. On the other 16 hand, in both cases a general increase of the inter-strip capacitance is observed for thicker oxides. 17 We do not have an explanation for this result yet.

19 20

Figure 8: Inter-strip capacitance results for different inter-metal oxide thicknesses in two structures. (a) Basic and (b) Rectangular-A

21 22

23 The two TOP sensors from one of the wafers fabricated with 1 µm inter-metal oxide thickness were 24 mounted in a module. Fig 9 shows the equivalent noise charge (ENC) measured for all the channels 25 in this module, indicating the correspondence with the different EPA layouts. For the measurements, 26 2 fC charges are injected into all channels, then 200 triggers are sent into each channel and the 27 ASICs are read out repeatedly with increasing thresholds. From the resulting S-curve, all 28 characteristics of each channel, such as noise, are determined in a fit. The readout is done with the 29 full testing setup [10]: the module is connected to HSIO ('High Speed Input Output') board 30 developed by the ITk collaboration) [11], and read out with a root program called SCTDAQ 31 developed at Rutherford Appleton Laboratory (RAL) [12]. One can confirm the expected good 32 correlation between the inter-strip capacitance and the noise for the different structures [13][14], 33 which demonstrates that the inter-strip capacitance measurements, with all-neighbors considered, are 34 a proper test to estimate the noise behavior of the different EPA layouts [15].

Figure 9: Noise results for the different EPA layouts measured on a module assembled with one of the wafers fabricated.

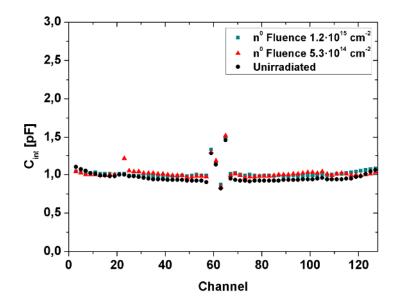

5 6 Additionally, some miniature sensors with EPA have been irradiated with 70 MeV protons at the 7 Cyclotron and Radioisotope Center (CYRIC), Tohoku University, Japan, in order to see the influence 8 of radiation on the inter-strip capacitance of sensors with EPA. The fluences achieved were  $5.3 \times$  $10^{14}$ , and  $1.2 \times 10^{15}$  1 MeV equivalent neutrons/cm<sup>2</sup>. The last fluence is the current target value for 9 10 the strip sensors in the future ITk. Sensors irradiated to those fluences with the Basic EPA layout, 20  $\mu$ m track width, and 1  $\mu$ m inter-metal oxide thickness have been tested. At this point, only inter-strip 11 12 capacitance measurements considering first neighbor channels have been taken, because the 13 irradiated sensors need cooling in order to bias them at full depletion voltage with controlled leakage current, and the test setup with the 128-probes probe card does not have a cooling system available. 14 15 Nevertheless, as it can be seen in Fig 10, the results of the tests performed on the irradiated miniature 16 sensors do not show any influence of radiation in the inter-strip capacitance. This will have to be 17 confirmed with all-neighbors inter-strip capacitance tests.

Figure 10:First-neighbors interstrip capacitance tests for the irradiated miniature detectors.

#### 2 3

#### 4 5. BEAM TEST

5 The full module assembled with two TOP petalet sensors from one of the wafers fabricated with 1 6 µm inter-metal oxide thickness have been subjected to test beam experiments at the Diamond Light 7 Source synchrotron in the UK. The 15 keV beam has a rate of up to 2 kHz and it is microfocused to a 8 spot size of 3.27µm x 1.65µm (FWHM) which guarantees to hit only one strip at a time. There is an 9 xyz-stage with micron precision positioning to move the beam across the target. As for the setup, the 10 module was held in place with vacuum, a chiller with a cooling liquid of a temperature of 15°C was 11 used to cool the module. The environmental conditions inside the box where the module was 12 mounted were monitored using temperature and humidity sensors placed close to the module. A low 13 flow of nitrogen at room temperature was used to prevent condensation inside the box. During the 14 whole duration of the measurement, inside the box temperature and humidity were stable at 20°C, 15 and 50% humidity.

16

17 One quarter of each EPA structure was scanned with the beam hitting every other channel, meaning 18 that 16 strips were scanned of each structure. Each structure was scanned twice: once on top of the 19 second-metal tracks, and once away from them, in order to distinguish between cross-talk and pick-20 up. 3500 triggers were allowed per strip and per threshold, but the photon conversion efficiency 21 inside a time window opened by a trigger is only roughly 60%, which results in about 2000 events 22 registered per strip. Three threshold ranges were used: 80-200 mV in steps of 6.4 mV, 200-300 mV 23 in steps of 39.4 mV, 300-450 mV in steps of 9.6 mV, resulting in 40 threshold steps per beam 24 position on the strips. For each photon undergoing interactions in the silicon, a deposited charge of about 0.6 fC is expected, corresponding to a minimum signal of roughly 60 mV. Since multiple 25 26 interactions can occur, up to 3 fC can be deposited. A minimum ionizing particle is expected to 27 produce a signal of about 300 mV.

28

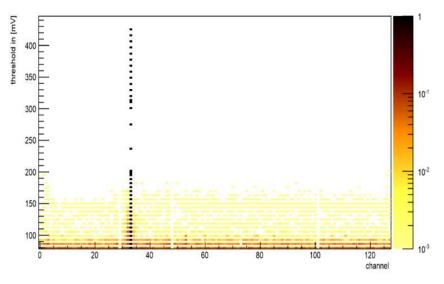

29 Fig 11 shows one typical result for the beam pointing to a specific strip (here strip 33) hit in a

- 30 structure (here structure Rectangular B as the worst-case structure). The figure represents the ratio

- 31 between the signal in every channel with respect to the signal in the channel being hit, once the

- 32 background has been subtracted, for all the thresholds. The background has been determined by the

1 spurious signal, that is, noise, measured in a specific strip if the beam was pointing at a completely 2 different area of the sensor that is read out by a different readout chip, and averaged over 16 times 10 3 measurements. As it can be seen, there is no sign of spurious signal in any channel above 170 mV threshold. On the other hand, the signal in the channels not being hit is below 1% of the signal 4 5 recorded in the channel being hit, above 100 mV. The non-zero occupancy for the non-hit channel is 6 likely due to the readout electronics performance at low threshold levels. All this is an indication that 7 there is no sign of cross-talk or pick-up, at least to the level of statistics achieved in this test beam. A 8 deeper analysis of the test beam results is being done to obtain more detailed information on the 9 possible spurious signals at lower thresholds. More test beams are foreseen with tracking capabilities 10 and using irradiated sensors to confirm these results.

- 11

- 12

13 14

15

16

17

18

Figure 11: Channel signal ratio to the hit channel signal for all the thresholds (background subtracted). The color code on the right corresponds to ratio between the signal (number of hits) in the corresponding channel with respect to the signal in the channel being hit, once the background has been subtracted.

# 19 6. CONCLUSION

20 A new proposal is presented to improve the throughput and reliability of the interconnection between 21 sensors and electronics in the Inner Tracker on the ATLAS Upgrade experiment for the HL-LHC. A 22 second metal layer is used to make the pitch adaptation integrated in the sensor. New layouts for 23 these Embedded Pitch Adapters are tested, together with new design and technological 24 improvements such as the reduction of second-metal track width, and the increase in the inter-metal 25 oxide thickness. The effect of these factors on the inter-strip capacitance is measured by a new 26 method that takes into account the effect of all neighbors. The results presented demonstrate the 27 reduction in interstrip capacitance variability down to a few tenths of pF with some of the designs 28 and with the reduction of the second-metal track width. The increase in inter-metal oxide thickness 29 helps in the flattening of the inter-strip capacitance for some of the structures, but produces a general 30 increase of its value in all the channels of about 1 pF that is still to be fully understood. 31 Measurements of miniature sensors irradiated at different fluences show no influence of radiation 32 damage on the interstrip capacitance, for measurements with first neighbors. The analysis from the 33 beam test shows no indication of cross-talk or pick-up above 170 mV threshold. A deeper analysis of 34 the test beam results and more test beams with tracking capabilities are foreseen to confirm this 35 result in detail.

# 2 7. ACKNOWLEDGEMENT

3 The irradiations were performed at Cyclotron and Radioisotope Center (CYRIC), Tohoku 4 University, with Y. Sakemi, M. Ito, and T. Wakui. The test beam was performed in the Diamond 5 Light Source Synchrotron in the UK. The research was supported and financed in part by the 6 Ministry of Education, Youth and Sports of the Czech Republic (Grant No. LG13009), the German 7 Federal Ministry of Education and Research, and the Helmholtz Association, the European Social 8 Fund and by the Ministry of Science, Research and Arts, Baden-Wuerttemberg, Germany, the Japan 9 Society for Promoting Science KAKENHI-A Grant number 20244038 and KAKENHI-C Grant 10 number 20540291, the Ministry of Education, Culture, Sports, Science and Technology-Japan, KAKENHI for Research on Priority Area Grant number 20025007 and for Scientific Research on 11 12 Innovative Areas Grant number 23104002, the Slovenian Research Agency, the Spanish Ministry of 13 Economy and Competitiveness through the Particle Physics National Program (ref. FPA2012-39055-14 C02-01 and FPA2012-39055-C02-02) and co-financed with FEDER funds, the financial support of 15 the State Secretariat for Education, Research, and Innovation, the Swiss National Science Foundation and the Canton of Geneva, Switzerland, the UK Science and Technology Facilities Council (under 16 17 Grant ST/M006409/1), and the United States Department of Energy, grant DE-FG02-13ER41983. 18

# 19 8. REFERENCES

- [1] M. Ullan, et al, "High-pitch petal-on-glass technology for pad pitch adaptation between

detectors and readout electronics", IEEE Transactions on Nuclear Science, NS-51 (3) (2004)

pp. 968.

- [2] C. Lacasta, Presentation at the ATLAS Upgrade Week (AUW), Feb 2009, CERN, Switzerland.

2009.

- S. Díez. "Silicon strip staves and petals for the ATLAS Upgrade tracker of the HL-LHC",

Nuclear Instruments and Methods in Physics Research Section A, vol. 699 (2013), pp. 93-96.

- [4] V. Benitez, et al. "Sensors for the End-cap prototype of the Inner Tracker in the ATLAS

detector upgrade", TL-COM-UPGRADE-2015-027, CERN, 2015

- [5] M. Aliev, et al. "A forward silicon strip system for the ATLAS HL-LHC upgrade", Nuclear

Instruments and Methods in Physics Research Section A, vol. 730 (2013), pp. 210–214.

- M. Ullán, et al. "Embedded pitch adapters for the ATLAS Tracker upgrade". Nuclear

Instruments and Methods in Physics Research A, vol. 732 (2013) pp. 178–181.

- W. Dabrowsky et al., "Design and performance of the ABCN-25 readout chip for the ATLAS

inner detector upgrade", Proceedings of the Nuclear Science Symposium (NSS-MIC), Orlando,

USA. Oct 2009.

- [8] W.D. Nix. "Mechanical Properties of Thin Films", Metal Transactions, vol. 20A (1989), pp.

2217

- [9] "Standard Test Method for Bow of Silicon Wafers", ASTM F534-02a, ASTM International,

West Conshohocken, PA, 2002, <u>www.astm.org</u>

- 40 [10] S. Díez, et al. "A double-sided, shield-less stave prototype for the ATLAS Upgrade strip

- 41 tracker for the High Luminosity LHC", Journal of Instrumentation, vol. 9, P03012, 2014.

- 42 [11] D. Nelson, HSIO development users guide (2010),

- 43 http://www.slac.stanford.edu/~djn/Atlas/hsio/.

- L. Eklund et al., ATLAS SCT test DAQ online documentation (2002), <u>http://sct-testdaq.home.cern.ch/sct-testdaq/sctdaq.html</u>.

- 46 [13] S. Chatterji et al. "Analysis of interstrip capacitance of Si microstrip detector using simulation

- 47 approach", Solid-State Electronics, v. 47 (2003) pp. 1491–1499

- [14] H. Ikeda et al. "Detector capacitance of silicon microstrip detector", Nuclear Instruments and

Methods in Physics Research Section A, vol. 313 (1992), pp. 31-36.

- [15] S. Braibant et al. "Investigation of design parameters for radiation hard silicon microstrip

detectors", Nuclear Instruments and Methods in Physics Research Section A, vol. 485 (2002),

pp. 343-361.