## Energy autonomous systems: future trends in devices, technology, and systems

Citation for published version (APA):

Belleville, M., Cantatore, E., Fanet, H., Fiorini, P., Nicole, P., Pelgrom, M., Piguet, C., Hahn, R., Van Hoof, C., Vullers, R. J. M., & Tartagni, M. (2009). *Energy autonomous systems: future trends in devices, technology, and* systems. CATRENE.

#### Document status and date:

Published: 01/01/2009

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 23. Aug. 2022

**CATRENE Working Group on Energy Autonomous Systems**

2009 - CATRENE - Cluster for Application and Technology Research in Europe on Nanoelectronics

# **Energy Autonomous Systems:** Future Trends in Devices, Technology, and Systems

#### **Contributors:**

Marc Belleville (CEA-LETI, France)

Eugenio Cantatore (TU Eindhoven, The Netherlands)

Herve Fanet (CEA-LETI, France)

Paolo Fiorini (IMEC, Belgium)

Pierre Nicole (THALES, France)

Marcel Pelgrom (NXP, The Netherlands)

Christian Piguet (CSEM, Switzerland)

Robert Hahn (FhG, Germany)

Chris Van Hoof (IMEC, Belgium)

Ruud Vullers (IMEC-NL, The Netherlands)

Marco Tartagni (University of Bologna, Italy), Coordinator <marco.tartagni@unibo.it>

© 2009 - CATRENE

http://www.catrene.org

ISBN: 978-88-904-399-0-2 ISBN-A: 10.978.88904399/02

# Index

| Index                                                               | 3  |

|---------------------------------------------------------------------|----|

| Foreword                                                            | 4  |

| 1. Introduction to Energy Autonomous Systems                        | 5  |

| 1.1. Definition of Energy Autonomous Systems                        | 5  |

| 1.2. Opportunities and applications of EAS                          | 6  |

| 1.3. Challenges of EAS and applications                             |    |

| 2. Current status of Energy Harvesting (EH) and Forward Look        | 12 |

| 2.1. Science and Technology                                         | 12 |

| 2.2. Commercial Exploitation                                        | 21 |

| 3. Current Status of Energy Sources (ES) and Forward Look           | 24 |

| 3.1. Science and Technology                                         | 24 |

| 3.3. Commercial Exploitation                                        | 30 |

| 4. Current Status of Ultra Low Power (ULP) Systems and Forward Look | 31 |

| 4.1. Science and Technology                                         | 31 |

| 4.2. Commercial Exploitation                                        | 47 |

| 5. Current status of Power Management (PM) and Forward Look         | 49 |

| 5.1. Science and Technology                                         | 49 |

| 5.3. Commercial Exploitation                                        | 56 |

| 6. European Situation and Forward Look                              | 58 |

| 6.1. Overview of Funding and Supporting Actions                     | 58 |

| 6.2. Recommendations and Suggested Actions                          | 63 |

| 6.3. Interdisciplinary Education and Training                       | 70 |

| 7. Bibliography                                                     | 75 |

| 7.1. Key Reports on EAS                                             | 83 |

| Acknowledgments                                                     | 84 |

#### **Foreword**

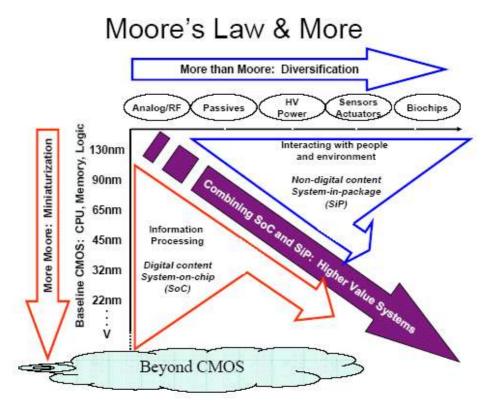

The rapid evolution of electronic devices since the beginning of the nanoelectronics era has brought about exceptional computational power in an ever shrinking system footprint. This has enabled among others the wealth of nomadic battery powered wireless systems (smart phones, mp3 players, GPS, ...) that society currently enjoys. Emerging integration technologies enabling even smaller volumes and the associated increased functional density may bring about a new revolution in systems targeting wearable healthcare, wellness, lifestyle and industrial monitoring applications.

As systems continue to shrink, less energy is available on board which is creating a power challenge that prompts several important questions. What are the ultimate autonomy limits? Can systems be made completely energy autonomous? And if so, what are the ambient sources that could help enable such energy autonomy? Could on-board intelligence allow greater net energy efficiency, despite its overhead in computational power?

Even though low-cost batteries have been fostering the expansion towards nomadic systems, they currently delay its further expansion as battery replacement or disposal is not an option in many of the envisaged applications and energy density is insufficient to achieve adequate autonomy. Although research towards higher energy-density batteries is ongoing and new materials are revolutionizing the battery dimensions, their energy density does not scale accordingly.

To overcome this trend, another energy paradigm is needed and energy harvesting (also referred to as energy scavenging) from the environment may provide a solution. A decade of research in the field of energy harvesting has led to the efficient capturing of small amounts of energy from the environment and transforming them into electrical energy. In parallel, suitable power management techniques are increasing the available energy budget, e.g. by dynamic optimization of voltage and clock rate, hybrid analog-digital designs, and clever wake-up procedures. Furthermore, advances in microprocessor technology have dramatically increased power efficiency, effectively reducing power consumption requirements. These developments together have stirred interest in new applications that rely entirely on energy harvesting for system power.

Energy autonomous systems using energy harvesting are particularly attractive when long-term remote deployment is needed or wherever a natural long-term energy source is available (such as for example temperature or vibrations) for continuous replenishing of the energy consumed by the system. Such inexhaustible energy supply is a significant advantage over battery supply or mains powering. Extended lifetime and autonomy are also particularly advantageous in systems with limited accessibility, such as medical implants and infrastructure-integrated micro-sensors.

Based on the information collected during the study, specific recommendations and suggested actions have been made on public initiatives, working methodology, and efficient research on a specific section of the report.

# 1. Introduction to Energy Autonomous Systems

## 1.1. Definition of Energy Autonomous Systems

**Energy Autonomous System:** an electronic system that has been designed to operate and/or communicate as long as possible in known/unknown environments providing, elaborating and storing information without being connected to a power grid. The systems could operate in external natural or industrial environments as well as for in-vivo applications in the diagnostic and therapeutic area. The power target should be particularly aggressive, and it is likely that several generations of prototypes will be necessary to achieve the goal to realize a system totally independent from the energy point of view. Regarding to the nowadays status-of-the-art it will be referred to systems with ability to operate with less than **hundreds of \mu W** of power within less than **some cubic centimeter**. Examples of such systems are nomadic devices operating at ultra low power (wireless sensor networks, in-vivo sentinels and actuators, ambient intelligence devices, "smart dust"). Cell phones or portable consumer electronics devices are not belonging, at the moment to this class.

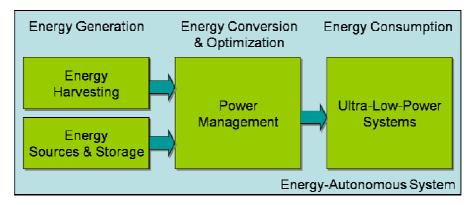

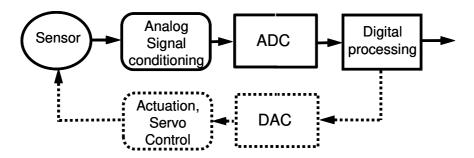

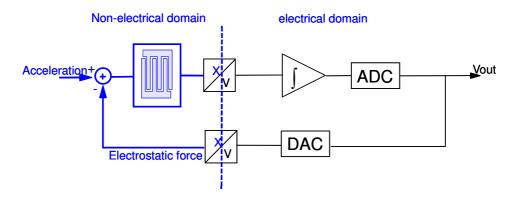

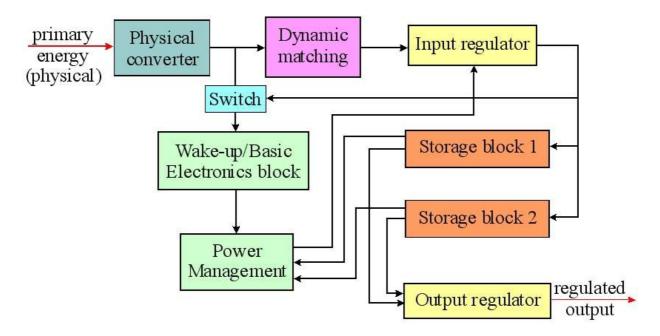

**Energy Autonomous Systems** could be roughly divided into three parts (Figure 1):

- **Energy Generation**, that consists of:

- o **Energy Harvesting:** Takes into account any device or system that could harvest energy from correlated or uncorrelated sources of energy. It could consist of many techniques that can be classified by the type of energy used: temperature differences, light radiation, electromagnetic fields, kinetic energy, etc. The technique could take advantages of more sources at the same time.

- o **Energy Sources:** this section takes into account any kind of energy storage element that could be used to accumulate energy in excess from the harvester and provide it to the system in its place whenever the energy is insufficient. Typically energy sources consist of electro-chemical elements such as batteries or fuel cells or electrical storage systems such as capacitors.

- **Energy Conversion and Optimization:** this section is the trade of any energy conversion within the system and it has impact for two reasons. The first is that any source of harvesting energy should be disciplined with respect to the existing sources. The second point is that the energy used by intelligence should be less than what gained by the process itself.

- **Energy Consumption:** this is the section related to data acquisition, storage and transmission. This is of fundamental importance since most of the opportunities for energy harvesting are related to the efficiency of this part.

Figure 1: Structure of the Energy Autonomous Systems

# 1.2. Opportunities and applications of EAS

The opportunities of EAS became increasingly interesting in the last five years due to the interactions of several key factors, more specifically, the decreasing computational energy, the increasing storage source capabilities and the energy conversions efficiency. However, the asymptotic energetic constraints of the system could be easily identified: the lower bound of computation is set by fundamental thermodynamic limit and the energy generation capability is restricted by several physical characteristics. Summarizing in few tips the key points of Energy Autonomous Systems:

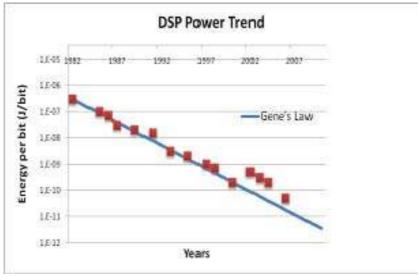

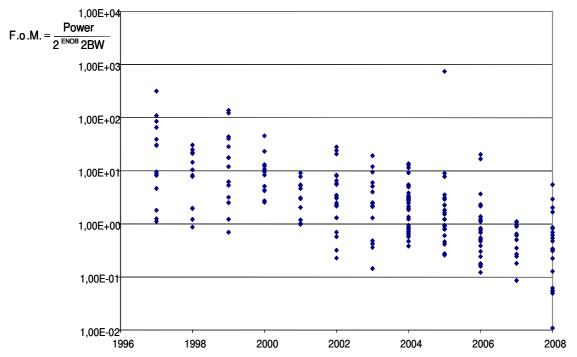

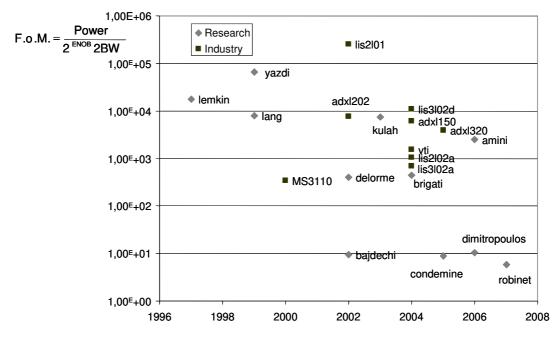

- The good: the energy per computation bit decreases according to the technology trend. More specifically, it has been surprisingly found that over the last 20 years the energy/bit is scaling with a trend similar to the Moore's law, that is ~1.6x/year. This behavior was discovered on TI DSPs and it is usually referred to as Gene's law (Figure 2). Even if the trend is exponential, we are currently quite far (~40 years) to reach the thermodynamic energy limit for computation (~20zI/bit).

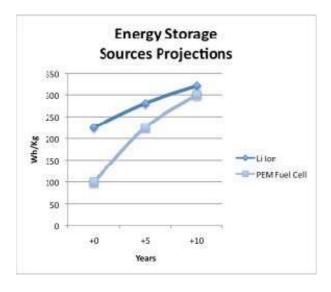

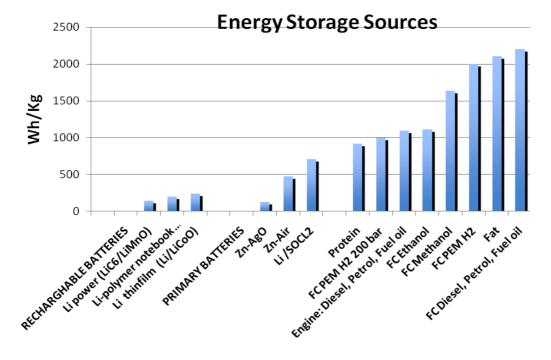

- The bad: Gene's law does not apply to analog sensing and transmission. In other words, the energy per bit spent for converting an analog value depends on the required conversion resolution and scales down with a trend that is usually slower with respect to Gene's law. Moreover, the energy storage density in general increases only by ~1.5x/decade (~1.04x/year, Figure 3) factor, against faster trends such as wireless transmission rate (~1.4x/year), computer CPU speed (~1.7x/year) and hard disk storage (~2.0x/year). Additionally, energy conversion efficiency is bounded by physical limits. Finally, if transmission is required, a minimum amount of energy should be spent whose value strongly depends on the quantity of data and on the length of the transmission path.

- The truth: the decrease of energy demanded by electronic systems and the increase of the energy stored and/or harvested by the generation systems give the opportunity for new extremely interesting applications. Some of them already reached the market, however, the real limits of the issues should be carefully analyzed on a case-by-case basis.

Figure 2: Energy per bit scaling trend for Digital Signal Processors. The trend is similar to Moore's law (1.6x/year) and it is usually referred to as Gene's law (source: Texas Instrument)

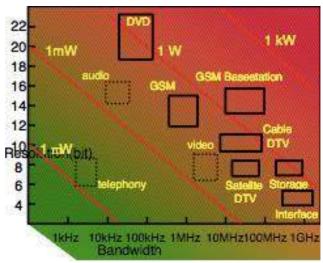

Given the energy trends demanded by electronics systems or supplied by storage units, another important issue to be considered in the design of EAS is the application. The main factors related to the energy consumed are: speed and resolution. Figure 4 illustrates the power demanded by various applications in different bandwidth and resolution requirements. This behavior is the first issue to be considered in EAS design.

Figure 3: Energy storage projections for Li-ion batteries and PEM Fuel cells. Even if the trend has a positive slope over the years, it shows asymptotic saturation due to the limitation of the energy conversion processes.

Figure 4: Energy demanded by various applications. The more precision and amount of data required, the more energy spent per time. Data are based on 5pJ/conversion. (Source: M. Pelgrom)

One of the key point of the durability of Autonomous Systems is the availability to store electrical power in different forms and to efficiently convert energy between them. Thus, energy conversion efficiency seems to be crucial in any storage process as illustrated in Figure 5. Interestingly, the process of energy harvesting by food used by living organisms and developed by Nature over the last billions of years, is one of the most efficient among the existing energy conversion processes. This means that there is "plenty of room" for future research on the energy storage and conversion issue.

Figure 5: Energy source densities. The comparison takes into account energy efficiency conversion.

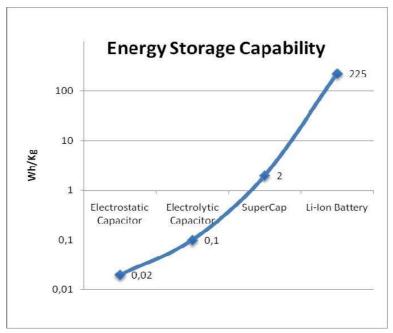

Figure 6: Energy storage capabilities for different useful technologies in Autonomous Systems.

Another interesting comparison is related to the energy storage capability of electronic energy storage components, illustrated in Figure 6. According to this plot, the capability of Li-ion batteries are four orders of magnitude greater than electrostatic capacitors and two-fold greater than supercaps.

# 1.3. Challenges of EAS and applications

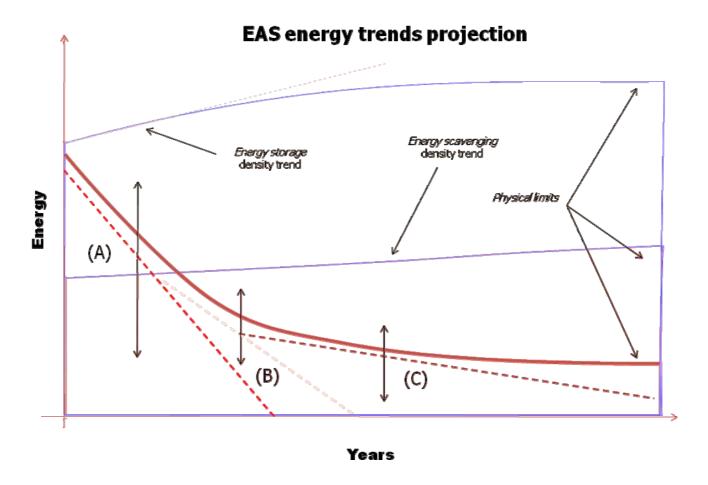

Making a forecast on the applications of Energy Autonomous Systems is very difficult, even in the near future, due to the overwhelming amount of variables that are involved. However, a very rough estimate could be done considering trends of electronic systems. Figure 7 shows a possible trend of the energy required by electronic systems in the next years. Given an application, we could consider the system composed of three parts: digital signal processing, A/D conversion and transmission. The application is composed of a blend of these subsystems, following different energy scaling trends: digital according Gene's law, analog on a slower trend and transmission depending on path link and data rate. According to the specific application and on the subsystem which is prevailing, asymptotic trend lines are shifted one respect to the others in the plot. Obviously, the trend comes to flat in the far end, due to fundamental limits (thermodynamic or minimum transmission energy required, whichever comes first).

Figure 7: Energy Autonomous Systems trends related to the demanding energy. (A):"digital systems trend", the energy per bit scales according to the Gene's law. (B): "A/D conversion trend", the energy per bit of the analog conversion systems scales slower than Gene's law. (C): "transmission systems trend", the energy per bit scales even slower and it is related to the path link to be covered and on the data rate. Usually, transmission energy trend is measured in [J/bit/m] according to the application. Intersection plot of energy storage and harvesting densities trends with electronic systems required trend. An EAS system could be fully (dark zone) or partially (light zone) supported by energy harvesting or scavenging whenever the two line do (or do not) intersect.

The intersection of the above plot with that related to the energy trend provided by sources and/or harvesting is illustrated in Figure 7. As previously mentioned, energy density trends for sources are usually slower than those related to the electronic systems. The plot is useful to understand whether it is possible to fully or partially energize an electronic system by scavenging or harvesting. More specifically, if the electronic system energy plot trend is below that of the energy harvesting (dark zone), it would be possible to fully support the EAS system by harvesting. If not, harvesting could contribute to the energetic balance. In that case, the sum of the energy storage and of the harvesting trends should be greater than that of the energy consumption.

Another important influence of the kind of application on EAS systems is summarized in Table 1. According to this view, autonomous systems could have dramatically different behavior, according to the task that they are supposed to be used for.

| Scenarios Characteristics                                             |                                                                                                                      | Examples                                                      |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Sensing, elaboration and physical collection of data                  | Senses until energy sources can support it. Data is recovered by physical recollection                               | Advanced in-vivo<br>diagnostics systems,<br>intelligent pills |

| Sensing, elaboration and collection of data by proximity energization | Senses until energy sources can<br>support it. Data is recovered by<br>providing external artificial burst<br>energy | Active RFID                                                   |

| Sensing, elaboration and RF data transmission                         | Senses, elaborate and transmit<br>data. The energy should be<br>provided to the system lifelong                      | Wireless sensor<br>networks                                   |

Table 1: several scenarios of Energy Autonomous Systems according to the application constraints.

| Scenarios                                               | arios Characteristics                                                                                         |          |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------|

| System power decreases and area is kept constant        | For a given application, the computational requirements decrease. The area for energy harvesting is constant. | Moderate |

| Computational power increases and area is kept constant | Scaling gives opportunity for increasing computational power. Area for energy harvesting is constant.         | Large    |

| Size of the whole system shrinks                        | The area for both computation and energy storage and harvesting is scaled down                                | Huge     |

Table 2: scalable trends of Energy Autonomous Systems

Finally, an outlook of the scalability trends of EAS systems is given in Table 2. There are two different areas that could be considered to be shrunk in the perspective trends: one related to the energy conversion and consumption and another related to the energy generation. According to the applications, those areas could require or not to be scaled down. Thus, Table 2 summarizes the criticality of the approaches in the future scaling trends.

Reviews on this subject could be found in [1][2][3][4][5][7][9].

*Energy Autonomous Systems* may contribute to many applications in different sectors. Among them portable autonomous systems could open new endemic scenarios for:

- wireless sensor networks (e.g. environmental monitoring in production plants, humanized environments, agriculture, etc.)

- wireless security systems (e.g. ad-hoc networking in harsh environments)

- in situ monitoring for mobile/moving systems (e.g. tire pressure monitoring systems, industrial process control)

- body area networks (e.g. health monitoring, active clothing, wearable energy sources, pervasive electronics)

- biomedical devices (e.g. pacemakers, continuous biological parameters monitoring systems, in-situ drug delivery)

- portable power generation for mobile electronics.

#### **Technology Readiness Levels**

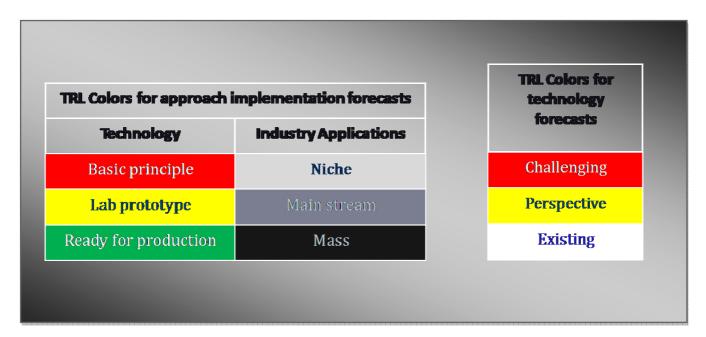

One of the main output of this study has been the preparation of a Technology Readiness Levels (TRL) document for each of the areas of the report: energy harvesting and sources, ultra low-power systems and power management. These levels are derived from a tentative classification of the existing EAS technologies and systems. TRL approach is an assessment of the present state of development as well as a projected timeline for future development.

In the report, two TRL classifications have been adopted for generic approaches and for specific technologies, respectively. In the first case, a broad forecast in the next 5 and 10 years for the approach itself (red, yellow, and green) and for the industrial applications (grey levels) are included. In the second case it has been adopted a more specific reference to the evolution of the technology in the next years (white, yellow, red, following ITRS reports approach)

Figure 8: Technology Readiness Levels (TRL) colors synopsis regarding approaches (left) and technologies (right). These colors will be used in the final tables of each section of the report..

# 2. Current status of Energy Harvesting (EH) and Forward Look

# 2.1. Science and Technology

Energy harvesting or scavenging is the conversion of ambient energy into electrical energy, by means of a specific transduction principle. Vibration, heat or solar energy are the main sources of ambient energy. In a strict definition, harvesting makes use of ambient energy which is not released on purpose and otherwise would be lost. However, in this report a broader definition is used: Also the case where energy is released with the purpose of feeding remote harvesting devices will be discussed. An example of the latter case is the conversion of RF energy which is transmitted by a designated emitting device.

#### 2.1.1. Harvesting Principles

In this section we briefly describe the physical principles on which harvesting of vibrational, thermal, photovoltaic and RF energy is based. More specifically, various extended reviews exist on energy harvesting from human body [4][5] and environment [6][7][8][9].

#### A. Vibrational harvesting

A vibration harvester is typically composed of a frame anchored to the vibration source and a mass m connected to the frame by a suspension having a stiffness k. The vibration induces a relative motion of the mass and the frame, a transducer transform the energy of this relative motion into electricity.

The main characteristic of a vibration energy harvester is that it operates in resonance. The resonance frequency is given by:

$$f = \frac{1}{2\pi} \sqrt{\frac{k}{m}}$$

The power in resonance for a mass-spring system is given by [7]:

$$P(f) = 4\pi^3 m f^3 Y z_{\text{max}}$$

where Y is the external vibration amplitude and  $z_{max}$  the maximum displacement of the proof mass, limited by the dimensions of the frame. It follows from the above equation that large output powers are enabled by higher vibration frequencies.

There are three ways of converting vibration into energy

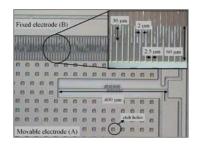

- Electrostatic (ES): A capacitor is made consisting of two opposing metal structures. One of these structures is fixed, the other one moves in presence of an external force. The change in voltage is proportional to the capacitance change

- Piezoelectric (PE): A mass is suspended by a beam, with a piezo electric layer on top of the beam. When the mass starts to vibrate, the piezoelectric layer is deformed and a voltage is generated

- Electromagnetic or Inductive (EM): A mass of magnetic material moves through a magnetic field. The change in flux generates a voltage.

In the figures below, some of the published results are shown for Electrostatic (Figure 9), Piezoelectric (Figure 10) and Electromagnetic (Figure 11) harvesting devices. One can clearly differentiate between the ES and PE on one hand, and on the EM on the other hand. The latter ones are rarely completely micromachined, most of the time macroscopic fabrication techniques are used

(eventually combined with micromachining). This has consequences for the size of these devices, which is then reflected in the power output values, which can be in the order of mW. A true micromachined device is shown by Beeby et al. [20], but it has a very low power output of 150 nW, produced at 0.4 g @ 8 kHz. In general one can state that it is very difficult to make EM harvesters using micromachining, the reason being the integration of magnetic materials and/or the fabrication of coils with enough windings.

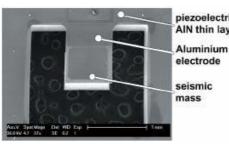

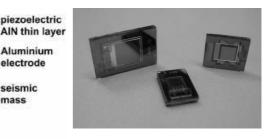

From a point of view of micromachining, the ES and PE harvesters are easier to fabricate. Therefore many devices have sizes in the sub cm $^2$  regime. The largest output for a micromachined PE device is reported to be  $45\mu W$  for PZT (Renaud et al. [21]) and  $60\mu W$  for AlN based devices (Elfrink et al. [15], Figure 10).

The vibration harvesters are the main candidates to end up in a first product for energy harvesting, namely as energy providers for a tire pressure monitor systems. However, still a lot of research has to be performed in order to get power levels up, cost down and reliability issues solved.

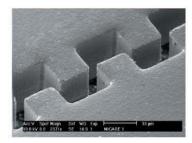

T. STERKEN ET AL. [10], IMEC, 2003: 12 nW, 1 g @ 1 kHz, 2 mm<sup>3</sup>

E. YEATMAN ET AL. [11], Imperial College, 2006: 2.4 μW, 40g @ 20 Hz, 3 cm<sup>2</sup>

G. DESPESSE ET AL. [12], LETI – MINATEC, 2007:  $12~\mu W$ , 0.3g~@50~Hz,  $1cm^2$

Figure 9: Examples of Electrostatic devices

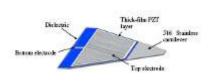

GLYNNE-JONES ET AL. [13], University of Southampton, 2001:  $3 \mu W$ , 1 g @ 80 Hz

M. MARZENCKI ET AL [14], Tima Labs, 2007:  $2 \mu W$ , 4g @ 1.3 kHz,  $2 \text{ mm}^2$

R. ELFRINK ET AL. [15], IMEC, 2008: 60 μW, 2g @ 571 Hz, 0.2 cm<sup>2</sup>

Figure 10: Examples of Piezoelectric devices

WEN J. LI ET AL. [16], Chinese Univ. of Hong Kong, 2000:  $680 \mu W$ , 95 g @ 110 Hz, 1 cm<sup>3</sup>

PERPETUUM [17], 40 mW, 1 g @ 100 Hz, 110 cm<sup>3</sup>

D. SPREEMANN ET AL. [18], HSG-IMIT, 2006: 300 mW, 300 μW, 1.4 g @ 60 Hz, 2.5 cm<sup>3</sup>

T. STERKEN ET AL. [19], IMEC, 2007: 300 μW, 50 g @ 5 Hz, 5 cm<sup>3</sup>

Figure 11: Examples of Electromagnetic devices

#### B. Thermal harvesting

In the case of thermal harvesting, two effects can be deployed. Using the Seebeck effect, one makes use of a spatial temperature difference. Another option is using a pyrolectric element, which can turn a temporal temperature difference into electricity. Since the efficiency of the latter is very low, only the first effect will be considered.

Thermal energy harvesters are based on the Seebeck effect. Their core element is a thermopile, formed by a large number of thermocouples placed between a hot and a cold plate. The thermocouples are thermally connected in parallel and electrically in series. The generator may include a radiator for efficient dissipation of heat in the ambient and specific structures aimed to increase thermal isolation between the hot and cold plate.

#### THE SEEBECK EFFECT

The Seebeck effect is associated with the generation of a voltage along a conductor when it is subjected to a temperature difference. Charged carriers (electrons or holes) diffuse from the hot side to the cold side, creating an internal electric field that opposes further diffusion. The Seebeck coefficient is defined as the voltage generated per degree of temperature difference between two points. In practice, the measurement of the potential difference drifting of the Seebeck electric field requires the use of a second driver to carry out the contact with the Voltmeter, which leads to the direct measurement of the difference of the Seebeck coefficients of two materials concerned:

$$\Delta V = -(\alpha_A - \alpha_B)(T_h - T_c),$$

where  $\Delta V$  is the observed potential difference (in Volts), and  $\alpha_i$  the Seebeck coefficients of materials A and B (in V/K) respectively, and ( $T_h - T_c$ ) the temperature difference between the hot source and the cold source (in Kelvin). This equation is valid if the variation in temperature is sufficiently weak to be able to neglect the dependence in temperature of the Seebeck coefficient.

#### **EFFICIENCY OF A THERMOGENERATOR**

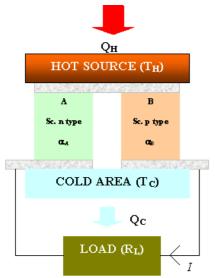

By considering the simplest generators consisting of a single thermocouple with thermo elements fabricated from n and p type semiconductors (Figure 12), the efficiency of the generator is given by:

$$\eta = \frac{W}{Q_H}$$

Assuming constant electrical conductivity, thermal conductivity and Seebeck coefficient in the thermoelectric couple and negligible contact resistances, then the electrical power is given by:

$$W = R_{I}I^{2}$$

and the current *I* is:

$$I = \frac{\alpha_{pn} (T_H - T_C)}{R_n + R_p + R_L}$$

We now define  $Z_{np}$ , which is the figure of merit of the n/p couple,

$$Z_{np} = \frac{\alpha_{pn}^2}{(R_n + R_p)(K_n + K_p)}$$

A thermoelectric converter (usually referred to as a module) is shown schematically in Figure 13. It consists of n-type and p type semiconductor thermo-elements connected electrically in series by highly conducting metal strips and sandwiched between thermally conducting (electrically insulating)

plates. It can be shown that the efficiency depends on  $Z_{np}$ , which is maximum when  $(R_n+R_p)(K_n+K_p)$  is minimum. This condition is realized when:

Figure 13: Schematic of thermoelectric converter (thermoelectric module).

$$\frac{\alpha_n}{\alpha_p} = \sqrt{\frac{\rho_n \lambda_n}{\rho_p \lambda_p}}$$

Then figure of merit becomes:

$$Z_{np} = \frac{(\alpha_p - \alpha_n)^2}{(\sqrt{\lambda_n \rho_n} + \sqrt{\lambda_p \rho_p})^2}$$

The maximum efficiency of the thermoelectric module is then found to be dependent on the factor *ZT* (figure of merit):

$$\eta = \frac{T_{C} - T_{F}}{T_{C}} \cdot \frac{\sqrt{1 + Z_{np}T_{m}} - 1}{\sqrt{1 + Z_{np}T_{m}} + \frac{T_{C}}{T_{F}}}$$

Since the efficiency of a thermoelectric device depends on the figure of merit ZT, a lot of research is conducted in the world in order to increase the figure of merit ZT. Values as high as 3.5 have been reported, but none of these claims have been confirmed independently [22]. Many questions remain to be answered.

#### MAXIMUM ELECTRICAL POWER RECOVERY

The optimal load for achieving maximum electrical power transfer is:

$$R_L = R_n + R_p$$

The maximum electrical power is then given by:

$$W = \frac{R_L}{4} \left[ \frac{\alpha_{pn} (T_C - T_F)}{R_n + R_p} \right]^2$$

In Figure 14 some of the devices published in literature are listed. These devices either make use of BiTe, a conventional material with ZT values close to 1, or in the case of Nextreme Thermal, superlattices of alternating BiTe/SbTe layers are used. Note that it is extremely difficult to compare the different power output values directly. For example, in the case of commercial vendors (e.g. Thermolife, Nextreme Thermal, Micropelt), the output values are calculated using a well defined temperature drop over the TEG ( $\Delta_{TEG}$ ). In reality, this value is different from the temperature drop present over the complete system ( $\Delta_{sys}$ ): since ( $\Delta_{TEG}$ ).<< ( $\Delta_{sys}$ ), this will lead to the result that the stated power output levels are much too optimistic when considering specific harvesting applications.

IMEC: 25µW/cm² for human body applications

THERMOLIFE: 5200 BiTe thermocouples on kapton tape  $123\mu W @ \Delta T = 5K$  (42.5 $\mu$ A at 2.9V)

NEXTREME THERMAL: Superlattices, 140μW @ ΔT = 0.8K (5mV open circuit voltage)

MICROPELT:

BiTe thermocouples.

2.8mW @ ΔT =10K,

(2.3V open circuit voltage)

Figure 14: Examples of thermoelectric devices

#### C. Photovoltaic harvesting

Photovoltaic converts incoming photons into electricity. Outdoor these cells have been used for many years, where power densities are available up to  $100 \text{mW/cm}^2$ . Efficiencies range from 5% to 30%, depending on the material. Indoor the situation is much different, since the illumination levels are much lower than outdoor (100 to  $1000 \mu \text{W/cm}^2$ ). Furthermore, at low illumination levels, the efficiency of solar cells will drop considerably. Much research is therefore needed to optimize these cells for low level illuminations.

#### WORKING PRINCIPLE OF PV CELLS

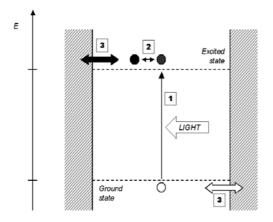

Conversion of light directly into electric energy involves the photovoltaic effect where photon energy is used to excite an electron from its ground state to an excited state, see Figure 15. A functional photovoltaic scheme should implement at least the following three steps:

- *Light harvesting*: photons are absorbed and their energy used to excite electrons.

- *Charge separation*: the excited electrons are separated spatially from the ground state to avoid recombination.

- Selective charge transport/extraction: electrons and holes are transported to the terminals of the device where the high-energy electrons are selectively extracted at one terminal while the holes selectively are replenished from the other terminal.

Ideally, there should be a one-to-one relationship between light and electric current: each photon that strikes the device delivers its energy to an electron, which in turn transports the energy to an electrical load connected to the terminals of the device. Here the energy can be released in the form of work.

n-doped p-doped

Figure 15: Diagram of photovoltaic principle showing the elemental steps: 1) light harvesting; 2) charge separation; and 3) charge transport.

Figure 16: Principle of photovoltaic device based on a semiconductor junction.

Figure 17: Principle of photoelectrochemical (PEC) cell.

Figure 18: Principle of simple single-layer organic PV with charge separation at one of the interface layers.

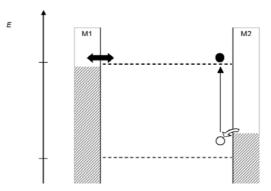

The PV scheme of Figure 15 is implemented elegantly in the classical semiconductor solar cell (first generation). In these PV's all the steps necessary for conversion of light to electric energy are provided by the cleverly manipulated band structure of a single semiconductor crystal. Figure 16 shows the band structure of such a semiconductor pn- junction. An excited electron-hole pair will - provided that its lifetime is sufficiently long - diffuse to the junction region where the charge carriers are separated. The activated electron is carried through the n-doped region to the negative terminal while the hole is replenished through the p-doped region from the cells positive terminal. Because impurities and grain boundaries acts as recombination centres, these devices should preferably be produced from high purity single- or multi-crystalline semiconductor material.

In order to reduce the high materials cost intrinsic to first generation PV technology, several thin film technologies are being pursued to enable higher volumes to be produced at a lower cost. But even though the materials costs of thin film PV devices can be reduced to a very low level, it may still be difficult to bring down the overall production cost to the level where solar power becomes economically competitive to power produced from fossil fuels. This is mainly because of the vacuum processes involved in the production. Recently, emerging low-cost alternatives are PV cells based on dye or organics:

Photo-electrochemical (PEC) or Grätzel cells [27].

These cells implement the photovoltaic principle differently from the semiconductor solar cells

- see Figure 17. Light absorption occurs in a transition metal complex (dye) that is absorbed on the inner surface of a nano-particulate, porous layer of anatase (titanium dioxide, a white pigment used in paints and tooth paste). The excited electron is immediately transferred to the conduction band of the anatase, and the remaining electron vacancy is replenished from a liquid or solid redox electrolyte.

#### • Organic-Based Photovoltaics.

Recently, substantial advances have been achieved in the conversion efficiencies of PV's based on molecular (organic) semiconductors and on conducting polymers [28]. In these organic-based PV's, *excitons* play an important role. Excitons are mobile, electrically neutral, optically excited states, which exist because they do not have enough energy to separate into an electron and a hole – in other words: the optical band gap is smaller than the electrical band gap. In organic materials this is often because charge separation involves a conformation change and thus requires a relatively large energy (Figure 18). Nanowires or quantum dot like absorber materials are used to validate the proof of concept of the nanotechnologies. The main objectives of this will be to decrease the manufacturing cost

#### INDOOR ILLUMINATION CONDITIONS

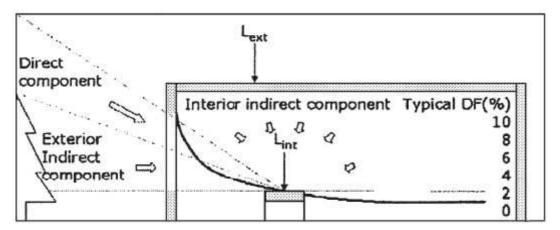

Figure 19: In-door illumination situation taking into account direct and indirect solar components, as well as in-door components

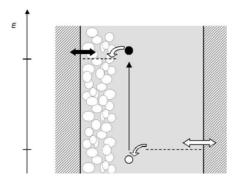

As shown in Figure 19, indoor illumination conditions are not as well defined as the solar light spectrum for outdoor lighting. Multiple contributions have to be respected and integrated into the test conditions:

- Direct sunlight contributions through windows (specular & diffuse)

- Indirect sunlight contribution reflected from nature or buildings

- Indirect sunlight contribution from interior (walls)

- Direct interior lighting contribution (incandescent lamps, neon lighting)

Especially for the last mentioned point, the definition of the light source is crucial, as the spectral distribution varies from one commercial product to the other, as well as the light power density emission of the global spectrum.

Therefore for a given scenario, spectral illumination conditions as well as light power density going typically from 1-100 mW/cm² have clearly to be defined and mentioned in a test report. A clear deduction of power conversion efficiency is therefore less defined as for the standard test conditions and an expression of delivered power should be preferred.

Standard Test Conditions are defined by using a AM1.5G solar spectrum, 100 mW/cm² light intensity and 25 °C device temperature. The definition of an AM spectrum is as follows:

- AM: Air Mass AM= $(P/P_0)^*(1/\sin\theta)$ , with P: local pressure,  $P_0$ : 1013 mbar,  $\theta$ : Angle between the direct solar light vector and the horizontal surface.

- AM0: Solar spectrum without atmosphere interaction

- AM1: Solar spectrum with normal incidence

- AM1.5: Solar spectrum on a 37° tilted surface (for average sun trajectory)

- AM1.5G: as AM1.5 taking into account direct and diffuse lighting

#### IDENTIFYING IN-DOOR PV TECHNOLOGIES

Solar cell comparison is generally based on an arbitrary maximum terrestrial intensity and spectra (of 1 sun,  $1000 \text{ W/m}^2$ ) at  $25^{\circ}\text{C}$  perpendicular to the cell plane referred to by specialists as AM1.5. In practice, no solar cell experiences such conditions, yet few alternative bases for comparison exist [29]. Given that the indoor photovoltaic devices, when compared with the outdoor solar cells, are characterised by much lower radiant energy intensities, various spectra (including artificial light sources), complete comparison data for indoor conditions are not freely available.

The inexorable growth in low power micro-electronic devices such as sensors and MEMS is an opportunity for increasing the use of PV especially for indoor applications. Photovoltaic modules may be used to partially or completely source the energy required for the functioning of such systems. For information, indoor consumer PV represented 4 MWP in 1997. It is of note that the 1 sun efficiency reference of such statistics is misleading for indoor products, as electrical efficiency is much less important indoors. This is because the end-user decision to purchase an indoor PV (IPV) product is not related to the solar cell electrical efficiency but rather to such benefits as reduced reliance on batteries ("plug and forget") and increased reliability i.e. a correctly designed and used IPV system can run longer without user intervention than when powered by batteries alone. From an environmental responsibility perspective, reducing battery waste is also laudable.

Using semi-conductor materials for the development of in-door photovoltaic devices leads rapidly to the use of direct band-gap materials. In fact, the low irradiance conditions (0.01 - 0.1 sun) creates charge generating and transport mechanism condition, that in-direct semiconductor materials like crystalline silicon are suffering of significant energy conversion losses.

#### D. RF Harvesting

RF harvesting converts electromagnetic radiation into electricity. This can be done in two ways.

- Make use of existing EM radiation (e.g. GSM, FM, WiFi)

- Broadcast an EM signal at a specific wavelength in order to power a wireless node.

The first solution has the advantage that radiation can be used that is already present. The disadvantage is the low energy density (typically  $\mu W/cm^2$ ). Furthermore, it is not always desirable or even legal to block radiation (e.g. for emergency calls). Therefore, a solution is to use dedicated broadcasting device, which can power sensors in the neighborhood. A point of concern is the maximum power that is allowed to be transmitted into the environment, which is typically around 100 mW.

A company called Powercast uses this principle to charge mobile devices (Figure 20). Using 3W of transmitted power at an operating frequency of 900MHz and a distance between device and transmitter around 30 cm, around 100mW of power is received. Larger distances mean larger radiation power, but 3W is already much higher than the allowed energy in Europe (around 100mW). However, the received power decreases very rapidly with distance. Furthermore, 3W as transmission power is not allowed in Europe. There is room for improvement, though, in transmission (e.g. beam

steering), receiving (improved antenna design) and the conversion efficiency. For example, at a transmission power of 100mW, values of 1.5mW at 20 cm [31] have been reported (Figure 21).

Other techniques still in the research phase are developed by MIT ("non-radiative-resonant-energy transfer"), for distances less than a few meters. The technology relies on copper coils tuned to resonate in identical magnetic fields [32]. In addition, researchers at the University of Tokyo (http://www.u-tokyo.ac.jp) have developed a four-layer plastic sheet with printed coils, organic transistors, and MEMS switches that use inductive coupling to power devices fitted with receiver coils [33]. Both of these technologies are still undergoing research, and commercialization is at least a few years away.

Figure 20: Solution by Powercast [30]: an RF transmitter (1) is plugged into a wall socket, it radiates radio waves (2) to tiny receivers integrated into devices (3).

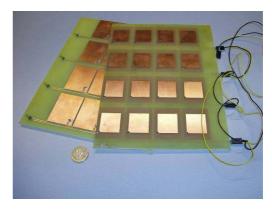

Figure 21: 2.45 GHz microstrip rectenna boards, back and front views [31].

#### 2.1.2. Estimate of typical harvested power values

| Source           |         | SOURCE<br>CHARACTERISTICS                  | PHYSICAL<br>EFFICIENCY | HARVESTED<br>POWER      |

|------------------|---------|--------------------------------------------|------------------------|-------------------------|

| PHOTOVOLTAIC     |         |                                            |                        |                         |

| Office           |         | $0.1 \text{mW/ cm}^2$                      |                        | 10 μW/cm <sup>2</sup>   |

|                  |         |                                            | 10-24%                 | •                       |

| Outdoor          |         | 100mW/ cm <sup>2</sup>                     |                        | 10mW/ cm <sup>2</sup>   |

| VIBRATION/MOTION |         |                                            |                        |                         |

| Human            |         | 0.5m@1Hz                                   | max power              | $4 \mu W/ cm^2$         |

| 7.6              |         | 1m/s <sup>2</sup> @50Hz                    | is source              | , <b>p</b> , •          |

| Industry         |         | 1m@5Hz<br>10m/s²@1kHz                      | dependent              | $100 \mu W/ cm^2$       |

| THERMAL ENERGY   |         |                                            |                        |                         |

| Human            |         | 20mW/ cm <sup>2</sup>                      | 0.10%                  | $25~\mu W/~cm^2$        |

| Industry         |         | 100 mW/ cm <sup>2</sup>                    | 3%                     | 1-10mW/ cm <sup>2</sup> |

| RF               |         |                                            |                        |                         |

| GSM              | 900MHz  | $0.3\text{-}0.03~\mu\text{W}/\text{ cm}^2$ | 50%                    | 0.1 μW/ cm <sup>2</sup> |

|                  | 1800MHz | $0.1-0.01 \; \mu W/ \; cm^2$               | JU /0                  | ο. τ μνν/ Citi          |

Table 3: Estimated power output values per harvesting principle [34]

In Table 3 the estimated figures of energy output values per harvesting principle are listed (from [34]). Note that these numbers are just first order indications, and they have to be considered to have a large error margin. However, they do give some indication of the typical expected power levels.

# 2.2. Commercial Exploitation

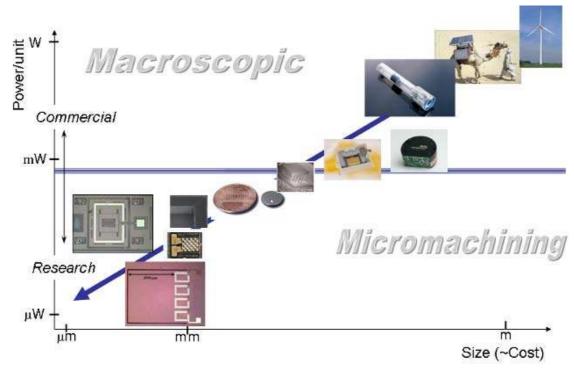

Harvesting devices in a large form factor have been around for quite some time (e.g. windmills). These devices can be characterized as being bulky, heavy and expensive. The main purpose of these devices has been to produce power. Only recently, the form factor has decreased such that applications in wireless sensor node have become feasible. The first products are appearing on the market, being still at considerable cost and size (here called macroscopic devices, see Table 4). They can only be found in special niche applications, e.g. at oil plants, underwater applications, etc. A majority of these companies are US based, as is shown in Table 5.

A further decrease in size and price is necessary, for the wireless sensors node applications to become widely accepted. Therefore, a transition to micromachining is inevitable, using MEMS (or MST) processing, as depicted in Figure 22. In Table 4 some of the main characteristics of the macroscopic and micromachined harvesting devices are being compared. Micromachining holds the promise of low cost devices, but many issues still need to be resolved. First of all, there are numerous processing issues to be resolved. Secondly, by scaling down the device size, the power output also decreases. As a consequence, much work is ahead to reduce power consumption of a real device (which is the subject of other chapters in this document).

|                      | Macroscopic  | Micromachined   |

|----------------------|--------------|-----------------|

| Fabrication          | Conventional | MST or MEMS     |

| Volume               | > cm3        | < cm3           |

| Weight               | g- kg        | mg – g          |

| Power output         | 1-100 mW     | 1-100 μW        |

| Phase                | Commercial   | Research        |

| Conversion Circuitry | Conventional | Ultra low Power |

Table 4: The main characteristics of macroscopic and micromachined devices

An alternative to standard MEMS is fabrication on foil. In that case, large area does not immediately mean heavy and expensive. Especially the cost of these systems on foil is expected to be low due to low fabrication cost. However, research on this topic has only just started.

Micromachined harvesters are still far from a product, their evolution will be technology driven (see Table 6) In order to accelerate technology development it is very important to coordinate the activities of small research groups, SME and Universities which address only a specific aspect of the wireless sensor networks. International projects are the key tool to bring together the groups active on harvesters, low power transceivers, data processing and power management.

Figure 22: The transition from macro to micromachining will cause a decrease in device size, as well as output power.

| Macros      | copic devices                     | Technology Readiness Levels |          | evels          |

|-------------|-----------------------------------|-----------------------------|----------|----------------|

| Technology  | Examples                          | 5 years                     | 10 years | Present Market |

|             | Advanced Cerametrics Face company |                             |          |                |

| Vibrational | Noliac                            |                             |          |                |

|             | Smart materials Enocean           |                             |          |                |

|             | Ferro Solutions                   |                             |          |                |

| Inductive   | <u>Perpetuum</u>                  |                             |          |                |

|             | KCF technology                    |                             |          |                |

| RF          | <u>IQ-Mobil GmbH</u>              |                             |          |                |

| IM.         | <u>Powercast</u>                  |                             |          |                |

|             | <u>Schott solar</u>               |                             |          |                |

| Solar Cells | <u>Asahi Glass</u>                |                             |          |                |

| (outdoor)   | (Mitsubishi)                      |                             |          |                |

|             | <u>Fuji Electronics</u>           |                             |          |                |

Table 5: Technology Chart of Macroscopic Harvesting devices

| Micromad    | chined devices     | Technology Readiness Levels |          | els            |

|-------------|--------------------|-----------------------------|----------|----------------|

| Technology  | Examples           | 5 years                     | 10 years | Present Market |

|             | <u>Siemens</u>     |                             |          |                |

| Vibrational | <u>Infineon</u>    |                             |          |                |

| Vibrational | <u>LV Sensors</u>  |                             |          |                |

|             | <u>IMEC/LETI</u>   |                             |          |                |

|             | Ferro Solutions    |                             |          |                |

| Inductive   | <u>Perpetuum</u>   |                             |          |                |

| mauctive    | <u>Tyndale</u> /   |                             |          |                |

|             | <u>Transense</u>   |                             |          |                |

|             | <u>Powercast</u>   |                             |          |                |

| RF          | <u>Microstrain</u> |                             |          |                |

| T.          | Ferro Solutions    |                             |          |                |

|             | <u>IMEC</u>        |                             |          |                |

|             | <u>Micropelt</u>   |                             |          |                |

|             | <u>Thermolife</u>  |                             |          |                |

| Thermal     | <u>IMEC</u> /      |                             |          |                |

|             | Fraunhofer/        |                             |          |                |

| DV          | TIMA               |                             |          |                |

| PV          | IMEC/TU Delft/     |                             |          |                |

| (indoor)    | <u>Fraunhofer</u>  |                             |          |                |

Table 6: Technology Chart of Micromachined Harvesting devices (research institutes in italic)

# 3. Current Status of Energy Sources (ES) and Forward Look

## 3.1. Science and Technology

# 3.1.1. Science and Technology of micro battery technology, especially as buffer storage for energy harvesting devices

Effective intermediate energy storage is required for all energy harvesting concepts, due to the varying availability of ambient energy and varying energy requirements of the device. In most cases this intermediate storage is best done with the help of a secondary micro battery. Secondary batteries have a much higher energy density compared to capacitors and sufficient power pulse capability.

Thus, the development of miniaturized power sources, with high volumetric energy density, is of crucial importance for small electronic applications like small sensor nodes, active smart labels or MEMS.

The energy density of batteries decreases rapidly by reducing the size of the batteries. This is caused by the increasing amount of passive packaging material in proportion to active material in small batteries. There is a significant reduction of energy density at a thickness of below 1 mm because the volume of the packaging foil becomes dominant.

Several approaches have been described for the development of micro batteries. At Oak Ridge National Laboratory a process has been created in which a secondary thin-film lithium battery can be deposited onto a chip [35]. The thickness of the entire battery is in the order of 100's of  $\mu$ m's and the areas studied are in the cm² range. This battery is a layered structure with alternate layers of lithium manganese oxide (or lithium cobalt oxide), lithium phosphate oxynitride and lithium metal. The maximum cell voltage is 4.2 V at max. current output in the order of 1 mA/cm² and 5 mA/cm² for the LiCoO2 - Lithium based cell respectively. All layers are fabricated using vacuum processing. The deposition of the electrolyte layer is a particularly highly sophisticated and time consuming process that leads to high production costs. Electrical cycling of the solid-state battery leads to cyclic changes of crystallite volume and material tension. Therefore, the total capacity is rather low since layer thickness cannot be increased above a few micrometers.

Another way of miniaturization was developed by downsizing the technology for laser welded metal casings and glass feed through technology [36]. Since this battery has a cylindrical format, integration and interconnection is not straight forward. Costs of these batteries as well as thin film batteries is very high which prevents utilization in the mass marked.

A three-dimensional battery assembly process [37] was developed whereby battery materials are filled into high aspect ratio holes of a substrate such as glass or silicon. Although the capacity per substrate area is rather high (up to 2 mAh/cm²), volumetric energy density is not more than approx. 80 Wh/l. While batteries according to approach [35] and [36] are already on the market, this technology is still in academic stage.

Table 7 gives an exemplary overview of the existing battery technologies. It can be seen, that the energy density of micro batteries is far below that of standard Li-polymer (200 Wh/kg, 400 Wh/l) batteries which are used for example in mobile phones.

| BATTERY                   | Thin film [35]                   | Medical [36]                                       | Chip card                   |

|---------------------------|----------------------------------|----------------------------------------------------|-----------------------------|

| SUPPLIER                  | Front Edge<br>Technology         | Eagle Picher                                       | Varta Microbattery          |

| SYSTEM                    | Li-LiCoO <sub>2</sub> -secondary | Li MnO <sub>2</sub> primary (secondary prototypes) | Li MnO <sub>2</sub> primary |

| DIMENSIONS [mm]           | 25×25×0.15                       | 6.73 × 2.37 diameter                               | 29×22×0.4                   |

| PACKAGE                   | thin glass, adhesive             | welded Ti, glass                                   | Metal foil,<br>polymer seal |

| CAPACITY [mAh]            | 0.7                              | 2.7 (at 30 μA)                                     | 25                          |

| SELF DISCHARGE            | 2 % / year                       | 2 % / year                                         | -                           |

| WEIGHT [g]                | 0.19                             | 0.09                                               | 0.65                        |

| VOLUME [cm <sup>3</sup> ] | 0.03                             | 0.03                                               | 0.25                        |

| CYCLES                    | 3500 (70%)                       | -                                                  | -                           |

| MAXIMUM<br>TEMPERATURE    | 150 °C                           | -                                                  | -                           |

| ENERGY DENSITY [Wh/kg]    | 13                               | 77                                                 | 115                         |

| ENERGY DENSITY [Wh/l]     | 26                               | 233                                                | 300                         |

|                           |                                  | i                                                  |                             |

Table 7: State of the art micro batteries. Images courtesy of Fraunhofer IZM, Berlin [36][41].

## 3.1.2 Science and Technology of micro fuel cells

In recent years, work on small portable fuel cell systems advanced significantly. The main goal is to increase the runtime and the availability of portable electronic devices far beyond those of battery-powered systems. The complete portable fuel cell consists of three major parts in analogy to the fuel cell systems for automotive and stationary applications:

- the fuel cell stack which determines the power output,

- the fuel tank which determines the total amount of available energy, and

- the balance of plant (BOP) which includes all of the peripheral systems like

- reformer, valves, pumps, and control circuits that support the overall function of the systems.

For micro systems only low temperature fuel cells are considered. This are the polymer electrolyte fuel cells (PEM) with hydrogen from chemical hydrides of water-metal reaction and the direct methanol fuel cell (DMFC). Other organic liquid fuels like ethanol and formic acid are under consideration as well.

For smaller systems, however, it is not simple to scale down components and system architectures of the existing fuel cell. Consequently, many of the components were redesigned taking into account the requirements of portable systems and the knowledge available on traditional fuel cell systems. Many components, such as micro pumps, valves, and sensors, presently do not have the long-term stability which is required in portable power supplies. It is therefore focused on reducing the

peripheral components and building the so-called "passive systems". Thus, costs and volume can be reduced and reliability increased.

#### Comparison of Li-ion batteries and portable fuel cells

In most cases, the only parameters of interest when comparing portable fuel cells and batteries are the energy and power density of fuel cell systems. The DMFC system as benchmark (the system using pure methanol is considered herein) is compared with the Li-ion battery. In addition to energy and power density, all other aspects like safety, durability, reliability, and costs are of importance. Table 8 displays some typical battery test specifications with pertinent remarks concerning portable fuel cells. As batteries are becoming smaller or even micro systems safety concerns will be less severe.

| Test                                                     | Battery specification                                                         | Remarks concerning portable fuel cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cycling<br>performance                                   | 80% of capacity after<br>200 cycles<br>100% discharge at<br>room temperature  | So far, rechargeable fuel cells have not been developed for portable products. Nevertheless, it would be a big advantage for the user to recharge the fuel by plugging the system into the mains instead of buying new fuel cartridges. At the moment, this parameter can be used as a lifetime indicator. After two to four years, the performance should not fall below 80% of the initial value                                                                                                      |

| Performance<br>at different<br>discharge<br>temperatures | -10 °C, 40 °C 20% of<br>initial capacity after<br>200 cycles                  | Fuel cell restart at temperatures below zero has only been demonstrated for stationary systems with the help of elaborate thermal management systems. For small fuel cells, this still is an issue. A solution is the hybrid system, where a Li battery powers the system at temperatures below zero degrees. Long-term operation at + 40 °C could lead to membrane dry-out. DMFCs with concentrated methanol supply also may have problems with water loss. Nevertheless, these issues will be solved. |

| Capacity at<br>different<br>currents                     | Capacity comparison<br>between 50 and 5<br>hours discharge: less<br>than 20%  | The working point of the fuel cell has to be designed properly. In contrast to batteries, the efficiency does not only drop at high currents, but also at low currents.                                                                                                                                                                                                                                                                                                                                 |

| Voltage drop<br>at high<br>currents                      | Capacity comparison<br>between 5 and 0.5<br>hours discharge: less<br>than 20% | The power density of fuel cells is much lower compared to Li batteries. Consequently, intermediate energy stores like capacitors or secondary batteries should be introduced for high power peaks.                                                                                                                                                                                                                                                                                                      |

| Test                                     | Battery specification                                                        | Remarks concerning portable fuel cells                                                                                                                            |

|------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Short-time<br>storage<br>characteristics | Capacity drop at 50 °C,<br>25% RH after 7 days<br>below 30%                  | Capacity will be unaffected, but start of the fuel cell may be difficult due to membrane dry-out.                                                                 |

| Long-term<br>storage                     | Capacity recovery<br>after one year at -20<br>+ 35 °C above 60%              | See above. Hydrogen leakage through packages and valves may be of concern.                                                                                        |

| Mechanical<br>tests                      | Drop test: survive<br>drop from 1.5 metres<br>height onto a concrete<br>base | Since fuel cells have a lot of mechanical components, this may be a crucial point. A low weight and stable design of the stack and components are very important. |

| Safety tests                             | No fire in case of short<br>circuit, overcharge or<br>overheating            | For fuel cells, new safety tests and specifications are under development                                                                                         |

Table 8: Typical battery test specifications and remarks

#### 3.2.1. Future Development of Micro Batteries

Current battery technology is not suitable for micro integration at low cost. The battery parameters of current rechargeable batteries are not optimized for energy harvesting devices: a life time of more than 10 years, several thousand charge-discharge cycles and high C-Rates (10...50) are required. These parameters cannot be addressed with state of the art lithium polymer materials. New materials based on carbon free anodes, ceramic electrolytes and long terms stable cathodes are necessary. Nanomaterials can help to achieve these goals.

Nanomaterials are currently being investigated in order to further increase the current density. It has been found that cathode materials with an olivine structure are suitable for a better lithium intercalation. LiFePO $_4$  with olivine structure belongs to the family of NASICON-type compounds (NASICON – sodium super-ionic conductor) that are known to be fast ionic conductors and used as solid electrolytes in electrochemical cells. In LiFePO $_4$  the hexagonal close-packed lattice of oxygen has a two-dimensional channel network that may act as fast diffusion paths for lithium ions. In addition, LiFePO $_4$  has the highest thermal stability of the so far known materials, which guarantees safe use and stable capacity after numerous work cycles.

Indeed, with a crystallite size in the range of  $\sim 10^{-9}$  m, high-current / high-power batteries can be achieved. Thus, the diffusion length within the bulk material is dramatically reduced due to the high surface area of the active material. As a result, power density is increased.

At the moment, lithium titanate ( $Li_4Ti_5O_{12}$ ) is a promising alternative material for the negative electrode. This material has a better cycle stability than conventional mixed graphite anodes. Tin based anodes are another alternative to graphite. Low cycle life and rate capability may be improved with help of nano structured Sn-based anodes.

Optimized active materials, such as nanoparticles of  $\mathrm{Li_4Ti_5O_{12}}$  with olivine structures as cathode intercalation matrix, can be used to reduce the bulk diffusion and, hence, increase the ability to operate at high current peaks.

Additional performance improvement may be realized through the use of 3-D architectures. This is especially convenient for micro scale batteries since Lithography and technologies adapted from Si and MEMS processing can be used. The use of the vertical dimension enables the battery to have a small areal footprint. Power density can be improved due to short ion diffusion length and high surface area.

Special crystal growth and vacuum deposition technologies, which will never be scalable for large batteries can be used to increase the performance of micro batteries. This may be carbon nano tubes or nano sized silicon columns for improved conductivity and Li intercalation [42].

Substrate integration of micro batteries is an important practical issue [38].

In case of wafer-level batteries where battery laminates can be assembled in cavities of silicon wafers to use the silicon substrate as an MEMS hermetic package. Battery laminates from Li-polymer mass production can be used for this technology. Thus, costs are relatively low.

In mass production usually a laminated foil package is used and liquid electrolyte is dispensed before encapsulation. The liquid electrolyte is not easy to handle and will degrade the sealing surfaces of a micro battery. In addition, the high vapor pressure of the battery prevents the use of vacuum technology for encapsulation. Therefore a gel type electrolyte would be required which is compatible to the active masses of the secondary battery. All materials and processes have to be optimized for ultra low water content and ultra low humidity and gas permeation.

Typical specifications are as follows:

- High energy density (> 300 Wh/l)

- High pulse discharge rate (> 10 C)

- small geometrical dimensions and flexible form factors (down to 1 mm<sup>2</sup>, 200 μm thickness),

- minor self-discharge

- high cycle stability of up to 10000 cycles

- long life of 10 years and more

- in some cases high temperature stability.

## 3.2.3. Future Developments of Micro Fuel Cells

A significant research effort is to miniaturise the fuel cells. Special improvement is required for the balance of plant by using miniaturised and high-reliability components and more passively working fuel cell technologies. Especially, water management is a crucial part of any fuel cell system and is particularly challenging to miniaturise. For small units, MEMS pumps and valves probably will have to be developed. While the first components appear on the market, a huge effort is still needed to increase the reliability, reduce their own energy consumption, and the costs.

The use of micro technologies for the fuel cell core is aimed at reaching two objectives:

- The specific fuel cell performance may be significantly improved when micro scaling processes are used. Fuel cells built to investigate micro-scale phenomena are smaller, use the volume more efficiently, and improve heat and mass transfer. Therefore, problems critical in conventional stack technology may be solved by the micro technological design of the three-phase boundary, the development of ultra-thin ion-conducting membranes, the fabrication of transport-optimised flow channels on the micro scale, the introduction of nanomaterials, and others. Most of these aspects are interdependent and have to be investigated and designed simultaneously. For example, ultra-thin electrolytes require the presence of narrow support structures in the micrometre range that may impede the flow of reactants.

- The majority of research activities related to micro-scale fuel cells is also aimed at micro-power applications. There are many new miniaturised applications which can only be implemented, if a higher-energy-density power source is available compared to button cells and other small batteries. Miniaturisation of the conventional fuel cell stack technology is not possible down to these dimensions.

While PEM micro fuel cell can be regarded as relatively mature and the research focus is on hydrogen supply, the liquid fuel cells like DMFC and DEFC still suffer from a lot of problems. Most critical are:

- The slow reaction rate and thus low power

- Poisoning from reaction intermediates

- Fuel cross over and

- Material degradation of catalysts, three phase boundary and ion membrane.

- A significant amount of materials research is required to tackle theses issues.

Another direction of research will be directed towards energy autarkic micro fuel cells which derive their fuel from the surrounding ambient. Two basic principles can be distinguished:

- 1. Autarkic fuel generators which are producing the fuel for the fuel cell separately. This may be hydrogen, generated from electrochemical corrosion of metals, from algae, from self catalytic decomposition of organics and others. This hydrogen is than fed into a PEM micro fuel cell.

- 2. Directly converting fuel cells which are integrated with their electrodes into the fuel and oxidant. This may be for example biological fuel cells which are using blood.

# 3.3. Commercial Exploitation

| Micro batteries                     | Technology Readiness Level |          | Present Market |

|-------------------------------------|----------------------------|----------|----------------|

|                                     | 5 years                    | 10 years |                |

| Thin film battery                   |                            |          |                |

| Si integrated micro battery         |                            |          |                |

| 3D micro structure electrodes       |                            |          |                |

| High temperature integrated battery |                            |          |                |

Table 9: Technology chart for micro batteries

| Micro fuel cells                             | Technology Readiness Level |  | Present Market |

|----------------------------------------------|----------------------------|--|----------------|

| Micro fuel cell with integrated fuel storage |                            |  |                |

| 3D MEMS based fuel cells                     |                            |  |                |

| Bio fuel cells                               |                            |  |                |

| Ambient fuel generator for micro fuel cells  |                            |  |                |

Table 10: Technology chart for micro fuel cells

# 4. Current Status of Ultra Low Power (ULP) Systems and Forward Look

# 4.1. Science and Technology

#### 4.1.1 Radio links

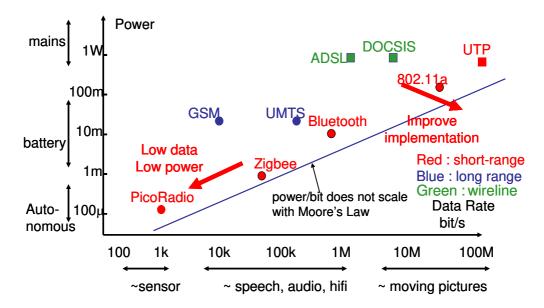

In wireless communications, the power consumption is mainly related to the data rate and to the range. These trends are illustrated Figure 23. Requirements for Wireless Sensor Networks (WSN) are usually short range communications and medium to low data rates. The resulting relaxed power constraints allow the perspective of Energy Autonomous Systems including wireless communication capability. To ensure a very long autonomy, a WSN application must also transmit and/or receive with a low duty cycle compared to the sleep duration, which also implies optimised Medium Access Control (MAC) mechanisms and routing protocols.

Figure 23: Trends in Wireless links power consumption

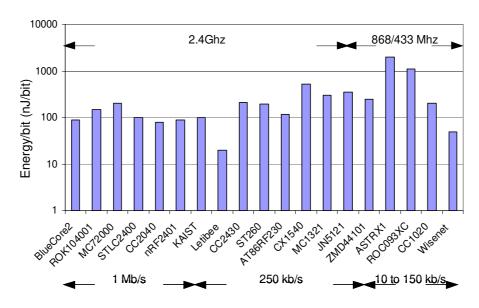

Although the power consumption/bit does not scale with the Moore's Law, the air interface data transfer of WSN has continuously been improved by device integration, low power architectures, design techniques, and efficient protocols. The IEEE-802.15.4 standard was voted in 2003 [43]. Based on this standard, which makes use of the 2.4 GHz band for 250 kbps data rates but also 868/915 MHz for lower ones, an industrial consortium has pushed the Zigbee protocol. Other fields of research are now driven by the Ultra Wide Band-based IEEE-802.15 which includes new functionalities, such as localization [44].

In November 2006, a consortium announced a new protocol, named Wibree [45], merging a high data rate up to 1Mbps with relaxed connectivity constraints. This proposal specifically targets multistandard WSN and easy co-integration with Bluetooth chips.

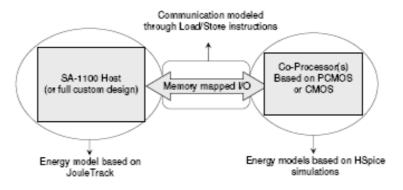

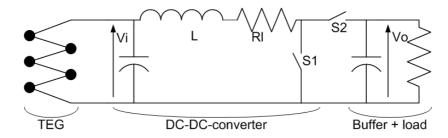

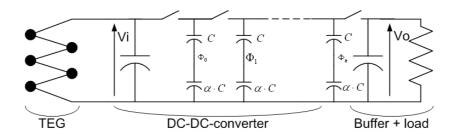

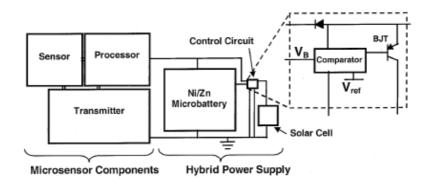

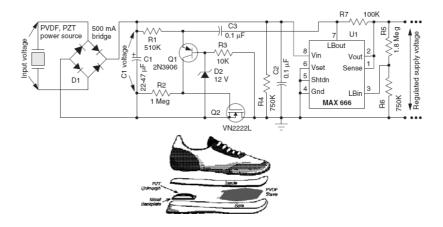

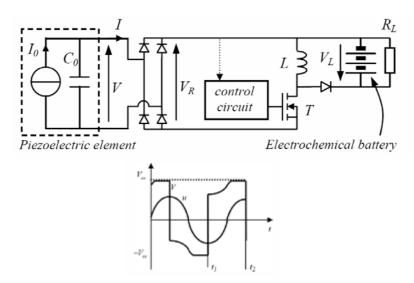

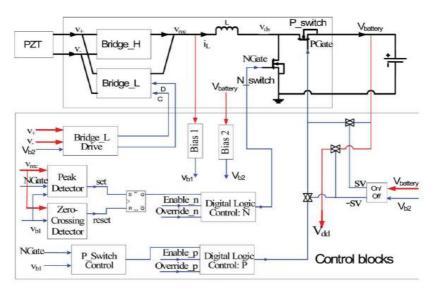

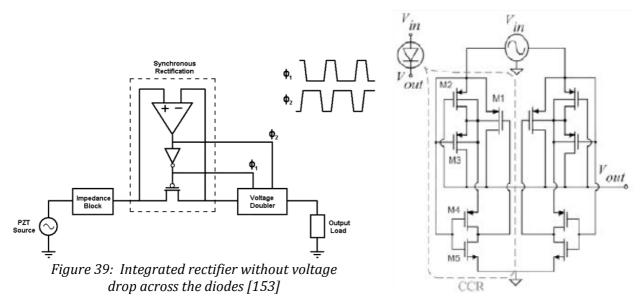

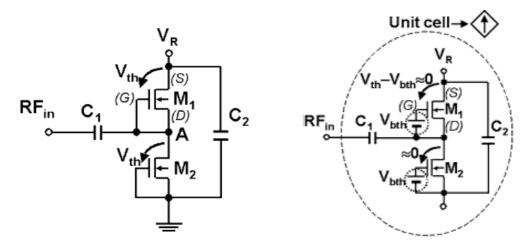

#### **ZigBee**