# Energy Yield Simulations of Interconnected Solar **PV** Arrays

Narendra D. Kaushika and Nalin K. Gautam

Abstract-In this paper, the electrical characteristics of array interconnection schemes are investigated using simulation models to find a configuration that is comparatively less susceptible to shadow problem and power degradation resulting from the aging of solar cells. Three configurations have been selected for comparison:

- i) simple series-parallel (SP) array which has zero interconnection redundancy;

- ii) total-cross-tied (TCT) array which is obtained from the simple SP array by connecting ties across each row of junctions; it may be characterized as the scheme with the highest possible redundancy;

- iii) bridge-linked (BL) array in which all cells are interconnected in bridge rectifier fashion. The explicit computer simulations for the energy yield and current-voltage distributions in the array are presented, which seem to favor cross-tied configurations (TCT and BL) in coping with the effects of mismatch losses.

Index Terms-Cross-tied array, energy yield, shadow problem, solar cell interconnection schemes, solar PV array.

## NOMENCLATURE

Ideality constant  $\cong$  2. а

A matrix (as described in Section II and flowchart A diagram).

$A \sim^x$ Inverse of the matrix A.

$$b \qquad (q^*V_{oc})l(a^*k^*T)$$

С Cell Current (A).

- $C_{max}$ Array current corresponding to maximum output power of the array (A).

- Assumed array current (A).

- Short circuit current for cell (A). I<sub>sc</sub>

- Junction current (A). J

- Boltzman's constant  $\cong$  1.3806 x It)"<sup>23</sup> J/°K. k

- $(M 1) \ge N$ ; The number of junctions in SP array. LI L2 $(M - 1) \ge (N/2)$ ; The number of junctions in BL

- array.  $1, \ldots, M.$ m

- $1, \ldots, N.$ n

- M Number of rows in an array.

- N Number of columns in an array.

- Р Junction potential (V).

- Electron charge  $\cong$  1.6022 x 10<sup>"19</sup> Coulomb. a

- Characteristics resistance for cell =  $(F_{oc}//_{sc})(0)$ . R<sub>o</sub>

- $R_{s}$ Series resistance for cell (fi).

The authors are with the Center for Energy Studies, Indian Institute of Technology, Hauz Khas, New Delhi-110016, India (e-mail: kaushika@ces.iitd.ernet.in; nalingautam@yahoo.com).

| R <sub>s</sub> h | Shunt resistance for cell directly across the diode ^ 1000 ( <i>ft</i> ). |

|------------------|---------------------------------------------------------------------------|

| Т                | Cell operating temperature ≅ 300° K.                                      |

| v                | Terminal voltage of the array (V).                                        |

| V                | Cell voltage (V).                                                         |

| Vmax             | Array voltage corresponding to maximum output power of the array (V).     |

| $V_{oc}$         | Open circuit voltage for cell (V).                                        |

| W                | Maximum power (W).                                                        |

| W                | Maximum power generated by an array with none of the cell shadowed (W).   |

| $W_2$            | Maximum power generated by an array with some cells shadowed (W).         |

| AW               | Change in maximum power generated by an array due to shadow effect (%).   |

| $\sigma$         | $R_o/R_{sh}$ .                                                            |

## I. INTRODUCTION

COLAR photovoltaic (PV) arrays consist of many cells connected to provide required terminal voltage and current ratings. In field conditions the arrays exhibit faults such as their power output is less than the sum of output power of constituent solar cells. The mismatch in power output can be due to such factors as manufacturer's tolerances in cell characteristics, partial or full opening of a string due to environmental stresses and the shadow problems. The mismatch loss may tend to enhance with time due to degradation resulting from aging of cells.

Fault-tolerance for the electrical mismatches has been investigated [1], [2] for both terrestrial as well as satellite born solar PV systems. The approach involves limiting of component malfunctions by redundant circuit design. For example, Series-Paralleling [3]-[8] in which a branch circuit is divided into series blocks to reduce the effects of electrical mismatches. The electrical output of the shadowed solar cell arrays can be considerably improved if each row of parallel cell strings (series blocks) is shunted by a diode [8]-[11]. More recently, several other interconnection schemes have been proposed and tested [12]—[15]. These schemes include the following.

- i) Total-cross-tied (TCT) array which is obtained from the simple Series-Parallel (SP) array (which has zero interconnection redundancy) by connecting ties across each row of junctions; it may be characterized as the scheme with the highest possible redundancy,

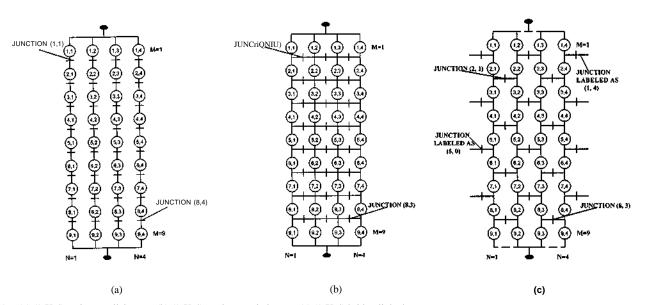

- ii) Bridge-linked (BL) array in which all cells are interconnected in bridge rectifier fashion. The circuit design features of SP, TCT and BL schemes for (9 x 4) array are illustrated in Fig. 1(a)-(c), respectively.

Manuscript received March 8, 2000; revised February 14, 2002.

Digital Object Identifier 10.1109/TEC.2002.805204

Fig. 1. (a) (9 X 4) series-parallel array; (b) (9 X 4) total-cross-tied array; (c) (9 X 4) bridge-linked array.

It is of practical importance to find a configuration that is comparatively less susceptible to the effects of mismatch losses due to shadow problem and power degradation resulting from to each of four-cell junctions of  $(M \ge N)$  array. For an  $(M \ge N)$ the aging of solar cells.

In this paper, electrical characteristics of the above array configurations are investigated using the computational network analysis approach [16]. Several mathematical models exist [7], [8], [15] for the evaluation of I-V characteristics of solar PV arrays. In this paper, a computer algorithm, based on junction analysis, is applied to minimize the current at each junction to zero as a limiting value. Explicit computational results on energy yield and current-voltage distributions in interconnected arrays are presented.

## **II. SIMULATION MODELS**

The current voltage relationship for a single diode solar cell can be expressed as follows [17]:

$$C - I_{sc} + I_o \left[ \exp\left(\left(\frac{q}{akT}\right)(V + CR_s)\right) - 1 \right] + \left(\frac{V + CR_a}{R_{sh}}\right) = 0. \quad (1)$$

Assuming  $R_s$  to be negligible, (1) can be expressed as

$$C = I_{sc} - \left[I_{sc} \times \left(\frac{1 - o}{\exp(b) - 1}\right) \times \left(\exp\left[b\left(\frac{V}{V_{oc}}\right)\right] - 1\right)\right] - \left(I_{sc} \times \left(\frac{V}{V_{oc}}\right) \times a\right)$$

(2)

where b and a are dimension less groupings [18] and can be expressed as

$$b = \frac{\int_{a}^{NV} \sigma \sigma}{akT} \text{ and } \sigma = \int_{R_{sh}}^{Y} \int_{asc}^{A} \sigma$$

(3)

In series-parallel (SP) array configuration the current through each string of the array is considered independently. For an  $(M \ge N)$  array, there are N parallel strings with each string having M solar cells connected in series. The number of junctions are ((M-l)xN). As shown in Fig. 1(a), a junction located below the cell (TO, n) has been labeled as the junction (TO, n) where rn, = 1 to (M - 1) and n = 1 to N. In the bridge-linked (BL) configuration, a Kirchoff type junction analysis is applied b each of four-cell junctions of  $(M \ge N)$  array. For an  $(M \ge N)$  array,  $((M - 1) \ge (N/2))$  four-cell junctions are considered. A junction has been labeled the value (m, n) if it is located below and to the right of the cell (TO, n) as shown in Fig. 1(c). The (rn, n) values of four-cell junctions are determined as follows: rn = 1 to (M - 1) and  $n = ((2 \le k) - 1 - (m \le (mod 2)))$ , where k = 1 to (N/2).

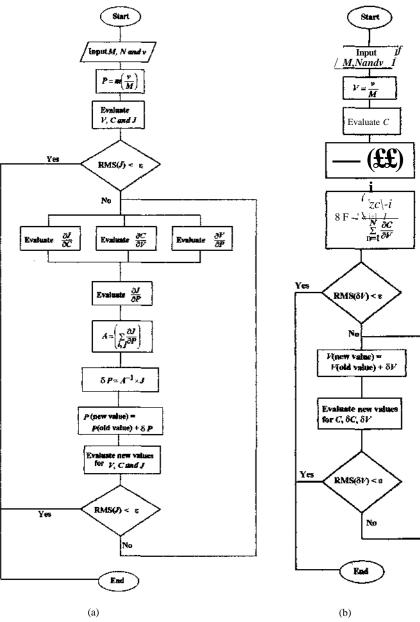

A flowchart diagram for the simulation model corresponding to SP and BL configurations is shown in Fig. 2(a). The initial trial potentials at each junction, in cases of SP and BL arrays, are approximated as

$$\operatorname{PTO}_{>^{''}} \sim {}^{m} \left( \frac{v}{M} \right).$$

(4)

The voltage across cell (rn, n) can be given as

$$\mathbb{V}_{*} = P_{m,n} - \mathbf{I}_{m-1,n}$$

(5)

The current through the junction (rn, n) can be expressed as the following.

In case of SP array

In case of BL array

$$Jm,n = \pounds'm,n + -\mathcal{P}'m,n+l \sim C'm+l.n \sim n'm+l,u+l- (7)$$

The current  $C_{mvn}$  through cell (m, n) can be obtained using (2). Let the upper and lower terminals of the cells be connected to the bus bars at potential zero and v respectively, the applicable boundary conditions are

In case of SP and BL arrays

$$P_{0}n = 0; P_{M}n = V.$$

(8)

In case of BL array

$$Pm,0 = Pm.N-$$

(9)

tions are ((M-l)xN). As shown in Fig. 1(a), a junction located The values of junction currents corresponding to the approxible below the cell (TO, n) has been labeled as the junction (TO, n), mate values of junction potentials can be regarded as small per-

Fig. 2. (a) Flowchart for SP and BL configurations, (b) Flowchart for TCT configuration.

turbations from their theoretical zero values. The perturbations in the junction currents can, therefore, be expressed as follows:

$$T = -A7 = -\begin{pmatrix} I & Y^{\alpha} & T \\ I & Y^{\alpha} & \cdots & I, J \\ i, j & \cdots & i, J \end{pmatrix} \times \delta P_{i,j}$$

(10)

where

$$\frac{\partial J_{m,n}}{\partial P_{i,j}} = \left[\frac{\partial J_{m,n}}{\partial C_{i,j}}\right] \times \left[\frac{\partial C_{i,j}}{\partial V_{i,j}}\right] \times \left[\frac{\partial V_{i,j}}{\partial P_{i,j}}\right].$$

(11)

Here  $(m - 1) \le i \le (m + 1)$  and  $(n - 1) \le j \le (n + 1)$ The first term on the right hand side of (11) can be expressed as follows.

In case of SP array

$$\frac{dJ_{m:n}}{\partial C_{i,j}} = \frac{d}{\partial C_{i,j}} \left[ C_{m,n} - C_{m+1,n} \right].$$

(12)

In case of BL array

$$\frac{\hat{C}T_{m,n}}{\partial C_{i,j}} = \frac{\hat{C}}{\partial C_{i,j}} \left[ C_{m,n} + C_{m,n+1} - C_{m+1,n} - C_{m+1,n+1} \right].$$

(13)

The second term on the right hand side of (11) can be expressed as

$$\frac{\partial C_{i,j}}{\partial V_{i,j}} = -\left[ (I_{sc})_{i,j} \left( \frac{b_{i,j}}{(\tilde{V}oc)ij} \right) \left( \frac{1 - \sigma_{i,j}}{\exp(b_{i,j}) - 1} \right) \right]$$

$$\left[ \left( \frac{\sigma_{i,j}}{V} \left( \frac{1 - \sigma_{i,j}}{V} \right) \right) \right] - \left( \frac{\sigma_{i,j}}{(V_{oc})_{i,j}} \right).$$

(14)

The third term on the right-hand side of (11) can be expressed as

$$\frac{\partial V_{i,j}}{\partial P_{i,j}} = \frac{\mathbf{d}}{\partial P_{i,j}} \left[ P_{i,j} - P_{i-1,j} \right]. \tag{15}$$

Equation (10) can also be expressed in matrix notation as

$$\mathbf{J} = A \mathbf{x} \ \boldsymbol{6P}. \tag{16}$$

The perturbation series  $(dJ_{mtn}/dP_{mn})_{s}$  in (10) can be expressed as a matrix A with nonzero elements in its [((m - 1)\*N) + n + 1 - (m\*(mod 2))]/2 rows and [(('i - 1)\*N) + j + 1 - (\*(mod 2))]/2 columns.

Here  $(m-1) \ll i \ll (m+1)$  and  $(rt-1) \ll j \ll (rt+1)$ . The matrix A is of size (LI x LI) in case of SP array and (L2 x L2) in case of BL array.

The calculated values of 6P are used to obtain a new set of junction potentials. A new set of junction currents  $J_{m>n}$ is then calculated as described in the Fig. 2(a). This whole process is successively repeated until the root mean square value (RMS) of  $J_{mnn}$  converges to a predetermined value e, say, (e =  $0.001^{*}/_{sc}$ ). In case of SP array, the array current against the assumed voltage v is determined by the sum of currents  $C_{mnn}$  through the cells, located along any row. In case of BL array, the sum of currents  $C_{m>n}$  in cells located along the upper terminal at potential zero must be reasonably equal to the sum of currents in cells located along the lower terminal at potential v.

A flowchart diagram for the simulation model corresponding to TCT configuration is shown in Fig. 2(b). Incase of TCT array, the initial trial voltage at each cell of a string is approximated as

$$V_{m,n} = \frac{V}{M'} \tag{17}$$

For a total-crossed-tied (TCT) array, the voltage across each row of the parallel cells is obtained independently. In this case, the sum of cell currents along any row is the array current whereas the sum of cell voltages along any column is supposed to be equal to the array terminal voltage.

With these approximate values for  $V_m \Lambda_n$ , the perturbation in the values of currents  $C_{mn}$  across cells along a row from their theoretical zero values are approximated as

$$\delta \dot{\mathbf{C}}_{\mathbf{m},\mathbf{w}} = \left(\sum_{n=1}^{N} \frac{\partial C_{m,n}}{\partial V_{m,n}}\right) \mathbf{X} \ \delta \dot{V}_{m,n}. \tag{18}$$

Furthermore, from definition  $\#C_{m,n}$  can be expressed as

$$\hat{\boldsymbol{o}}\,\hat{\boldsymbol{o}}_{,\boldsymbol{m},\boldsymbol{n}} = \left(\sum_{n=1}^{N} C_{m,n}\right) - I \tag{19}$$

where / is assumed array current.

The values of C <sub>m,n</sub> can be determined using the currentvoltage relation given in (6). Using (18) and (19), the variations in the values of cell voltages  $SV_{m < n}$  are determined as described in Fig. 2(b).

A new set of cell voltages is then calculated as described in the Fig. 2(b). This whole process is successively repeated until the root mean square value (RMS) of  $6V_m{}^n$  converges to a predetermined value E, say, (e =  $0.001*V_{cc}^r$ ). The array current against the terminal voltage v is then determined by the sum of all cell currents  $C_{TOrn}$  along any row.

## III. COMPUTATIONAL RESULTS & DISCUSSIONS

The current voltage relationship of a solar cell, as given by (2), depends on certain solar cell parameters. These parameters are  $R_s$ ,  $V_{oc}$ ,  $I_{sc}$ , b and a. The parameters b and a depend on  $V_{oc}$ .

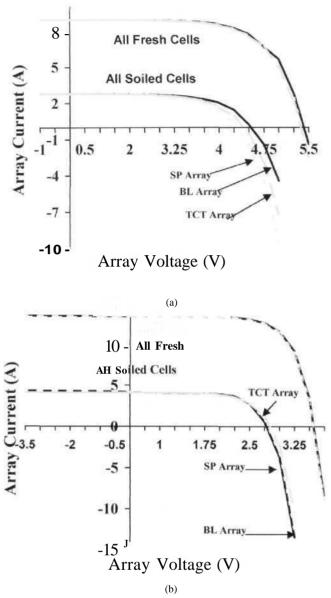

Fig. 3. (a) I-V curve for (9 X 4) BL, SP & TCT arrays and (b) I-V curve for (6 X 6) BL, SP & TCT arrays.

*Isc* and  $R_{sh}$ . To investigate the electrical characteristics of different solar cell interconnection schemes, the characteristic data for all solar cells are required. The data ( $V_{oc}$ ,  $I_{sc}$  and  $R_{sh}$ ) for 36 single crystalline silicon solar cells were supplied by the manufacturer, Central Electronics, Ltd., Sahibabad, India. The data correspond to standard test conditions. The diameter of each solar cell is 0.1 m and its area TTO.0025 m<sup>2</sup>. So the effective area of each array becomes (36 x *n* x 0.0025) m<sup>2</sup>.

Two solar cell ensembles have been considered; one ensemble corresponds to fresh cells and the other to soiled solar cells derived from PV modules used for over five years. Solar cells, without the top transparent cover and lying uninstalled in a panel for more than five years, were used to provide the data corresponding to soiled solar cells. Two modular arrays, one of size (6 x 6) and the other of size (9 x 4), have been considered. The I-V curves, maximum power points and fill factors for the modular arrays of 36 solar cells have been obtained using the above simulation models. The comparative I-V curves of SP,

TABLE I

MAXIMUM POWER AND FILL FACTOR FOR (9 x 4) ARRAYS

| Ensemble        | Maximum Power<br>(W) |       |       | Fill Factor |      |      |

|-----------------|----------------------|-------|-------|-------------|------|------|

|                 | BL                   | SP    | тст   | BL          | SP   | тст  |

| Fresh<br>Cells  | 35.04                | 34.78 | 34.66 | 0.73        | 0.73 | 0.73 |

| Soiled<br>Cells | 8.85                 | 8.14  | 8.57  | 0.70        | 0.69 | 0.70 |

TCT and BL arrays of size  $(9 \times 4)$  for the two ensembles of solar cells are given in Fig. 3(a). Similar results for the  $(6 \times 6)$  arrays are shown in Fig. 3(b).

The corresponding values of energy yield characterized by maximum power and fill factor are given in Tables I and II, respectively. These results indicate that the mismatch losses due to manufacturer's tolerances as well as losses resulting from the aging processes of solar cells are least in BL arrays. Fill factor of an array can be defined as the ratio of the maximum output power and the product of the open-circuit voltage and short-circuit current of the array. It is a measure of rectilinearity of the I-V curve of the array.

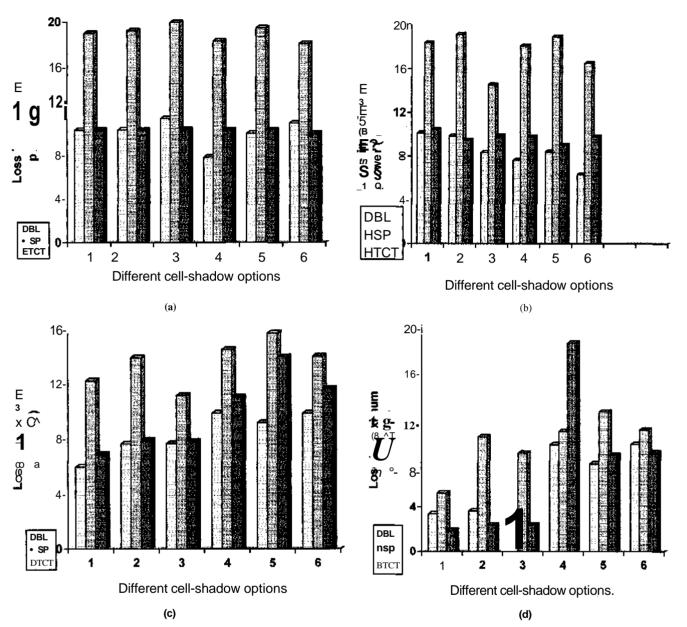

With a view to study the effect of shadow on I-V curve characteristics, the shadow has been taken to correspond to a drop of irradiance from 1000 W/m<sup>2</sup> to 20 W/m<sup>2</sup> and rise of cell temperature by 25° C. [*dlsddT*) and [*dV<sub>oc</sub>/dT*] are taken to be 0.1 A/m<sup>2</sup>°C and -2.2 mV/°C, respectively [19]. Six shadow options, outlined in Table III, have been considered. Each shadow option corresponds to a reduction in power generation of constituent solar cells of the array by 6.5%. Shadowing the cells exhibited changes in I-V curve, maximum power point and the values of current and voltage corresponding to maximum power point in case of each array configuration. However, the degree of change varied from one configuration to the other.

Change in maximum output power due to shadow effect, which is represented by AW (in percentage), is defined as

$$AW = \left(\frac{W_1 - W_2}{W_1}\right) \times 100.$$

(20)

The computed values of AW corresponding to different shadow options and array configurations are illustrated in Fig. 4(a)-4(d). A shadow of one cell width and four cell length considered in several orientations reduces the maximum output power (on the average) by 18 percent in SP array and 7% in BL array. Lower values of A *W* correspond to better fault-tolerance due to shadow problem. The BL arrays are marginally superior (or comparable) to TCT arrays and are significantly superior to SP arrays in fault-tolerance due to shadow effect.

Shadowing of some cells in cross-connected arrays could lead to a situation when the remaining cells have to carry higher current loads than specified. We have, therefore, investigated the currents in individual strings of the arrays under shadow con-

TABLE

II

MAXIMUM POWER AND FILL FACTOR FOR (6 x 6) ARRAYS

| Ensemble        | Maximum Power<br>(W) |       |       | Fill Factor |      |      |

|-----------------|----------------------|-------|-------|-------------|------|------|

|                 | BL                   | SP    | тст   | BL          | SP   | тст  |

| Fresh<br>Cells  | 34.52                | 34.40 | 34.27 | 0.72        | 0.72 | 0.72 |

| Soiled<br>Cells | 7.95                 | 7.55  | 7.85  | 0.68        | 0.68 | 0.68 |

TABLEIIIDIFFERENT CELL SHADOW OPTIONS

| Option | Shadowed Cells Identification                                                                  |

|--------|------------------------------------------------------------------------------------------------|

| i      | (1,1), (1,2), (1,3) & (1,4)                                                                    |

| 2      | (1,1), (2,1), (3,1) & (4,1)                                                                    |

| 3      | (1,1), (2,2), (3,3) & (4,4)                                                                    |

| 4      | (6,1), (6,2), (6,3) & (6,4) for (6 x 6) array<br>(9,1), (9,2), (9,3) & (9,4) for (9 x 4) array |

| 5      | (3,1), (4,1), (5,1) & (6,1) for (6 x 6) array<br>(6,1), (7,1), (8,1) & (9,1) for (9 x 4) array |

| 6      | (6,1), (5,2), (4,3) & (3,4) for (6 x 6) array<br>(9,1), (8,2), (7,3) & (6,4) for (9 x 4) array |

dition (shadow option 1 as described in Table III). The results corresponding to maximum output power, are summarized in Tables IV-VI.

There is no indication of the higher current loads in the strings. However, the shadowed cells were observed to be negatively biased and as long as the negative voltage is less than the diode break down voltage cross-tied configurations can be used to cope with the effects of mismatch losses.

## IV COST IMPLICATIONS

With a view to examine whether the cross interconnection configurations (TCT and BL) could be adopted in practice, we devised two configurations of interconnected modules of 36 solar cells:

i) a module of (6 x 6) array;

ii) a module of (9 x 4) array.

The Central Electronics, Ltd., Sahibabad, fabricated a  $(9 \times 4)$  BL array to examine its practical realization and informed us that in mass production there would be no extra labour and cost involved. We, therefore, think that the practical adoption of the interconnection arrays would not involve any addition of cost.

However, as yet no company in India has adopted the commercial manufacturing of such interconnected modules. So it is very difficult to comment on the comparative cost and investment figures.

Fig. 4. (a) Loss in maximum power for  $(9 \times 4)$  arrays with all fresh cells, (b) Loss in maximum power for  $(9 \times 4)$  arrays with all soiled cells, (c) Loss in maximum power for  $(6 \times 6)$  arrays with all fresh cells, (d) Loss in maximum power for  $(6 \times 6)$  arrays with all soiled cells.

| CURRENT-VOLTAGE DISTRIBUTION IN CASE OF SP ARRAY | ľ |

|--------------------------------------------------|---|

| a      | Series Parallel Array |          |                 |          |  |  |

|--------|-----------------------|----------|-----------------|----------|--|--|

| String | No SI                 | hadow    | Shadow Option 1 |          |  |  |

|        | ^max (V)              | Cmax (A) | »W(V)           | Cmax (A) |  |  |

| 1      | 2.7503                | 2.0843   | 0.2874          | 0.604    |  |  |

| 2      | 2.7503                | 2.0803   | 2.7503          | 1.8953   |  |  |

| 3      | 2.7501                | 2.091    | 2.7501          | 1.9063   |  |  |

| 4      | 2.7515                | 2.0862   | 2.7515          | 1.9012   |  |  |

| 5      | 2.7492                | 2.0873   | 2.7492          | 1.902    |  |  |

| 6      | 2.7503                | 2.0748   | 2.7503          | 1.8867   |  |  |

## V. CONCLUSION

Electrical characteristics of interconnected solar PV array networks have been investigated to find a configuration that is comparatively less susceptible to the effects of mismatch losses due to shadow problem and energy yield degradation resulting from aging of solar cells. Three interconnection schemes—series-parallel, total-cross-tied, and bridge-linked, have been considered for the arrays.

TABLE

V

CURRENT-VOLTAGE

DISTRIBUTION IN CASE OF TCT ARRAY

| <b>G</b> . 1 |           | Total-Cross | -Tied Array     |                       |

|--------------|-----------|-------------|-----------------|-----------------------|

| String       | No Shadow |             | Shadow Option 1 |                       |

|              | *Wx(V)    | Cmax (A)    | ^max (V)        | C <sub>ma</sub> x (A) |

| 1            | 2.7503    | 2.0782      | 0.6604          | 0.6938                |

| 2            | 2.7503    | 2.0712      | 3.1273          | 1.9853                |

| 3            | 2.7501    | 2.0842      | 3.1251          | 1.9213                |

| 4            | 2.7515    | 2.0791      | 3.1265          | 1.9165                |

| 5            | 2.7492    | 2.0804      | 3.1242          | 1.7797                |

| 6            | 2.7503    | 2.0674      | 3.1253          | 1.9043                |

The mathematical expressions for the current-voltage relationship of these circuits can not be obtained in explicit forms. Computer simulation approach is, therefore, applied to evaluate the I-V curves, maximum power points, fill factors and string-wise current-voltage distributions for these arrays. Extensive simulation results for energy yield and string-wise current-voltage distributions in the array are presented. The results conclusively establish the superiority of cross-tied configurations (TCT and BL), marginal in case of normal fresh cell arrays and significant in cases of shadowed and soiled cell arrays. The practical implementation of TCT and BL schemes should not escalate the cost.

TABLE

VI

CURRENT-VOLTAGE DISTRIBUTION IN CASE OF BL ARRAY

| ~      | Bridge-Linked Array |         |                 |                      |  |  |

|--------|---------------------|---------|-----------------|----------------------|--|--|

| String | No S                | hadow   | Shadow Option 1 |                      |  |  |

|        | *W(V)               | Cmax(A) | Kmax (V)        | C <sub>max</sub> (A) |  |  |

| 1      | 2.7503              | 2.0905  | 0.6604          | 0.6882               |  |  |

| 2      | 2.7503              | 2.0908  | 3.1273          | 1.9852               |  |  |

| 3      | 2.7501              | 2.0978  | 3.1251          | 1.9312               |  |  |

| 4      | 2.7515              | 2.0922  | 3.1265          | 1.9255               |  |  |

| 5      | 2.7492              | 2.0932  | 3.1242          | 1.928                |  |  |

| 6      | 2.7503              | 2.0812  | 3.1253          | 1.914                |  |  |

#### REFERENCES

- F. A. Blake and K. L. Hanson, "The hot-spot failure mode for solar arrays," in *Proc. 4th Int. Energy Com. Eng. Conf.*, 1969, p. 575.

- [2] S. H. Raushenbach, "Electrical output of shadowed solar arrays," *IEEE Trans. Electron Devices*, vol. 18, p. 483, Aug. 1971.

- [3] C. Gonzalez and R. Weaver, "Circuit design considerations for photovoltaic modules and systems," in *Proc. 14th IEEE Photovolt. Spec. Conf.*, 1980, pp. 528-535.

- [4] R. G. Ross Jr., "Reliability and performance experience with flat-plate photovoltaic modules," in *Proc. 4th E.C. Photovoltaic Solar Energy Conference*, 1982, p. 10.

- [5] J. J. Appelbaum, J. Bani, and A. Braunstein, "Array power output of nonidentical cells," in *Proc. 12th Intersoc. Energy Com. Eng. Conf*, 1977, pp. 1686-1692.

- [6] L. L. Bucciarelli Jr., "Power loss in photovoltaic arrays due to mismatch in cell characteristics," *Solar Energy*, vol. 23, pp. 277-288, 1979.

- [7] J. W. Bishop, "Computer simulation of the effects of electrical mismatches in photovoltaic cell interconnection circuits," *Solar Cells*, vol. 14, pp. 73-89, 1988.

- [8] V. Quaschning and R. Hanitsch, "Numerical simulation of current-voltage characteristics of photovoltaic systems with shaded solar cells," *Solar Energy*, vol. 56, no. 6, pp. 513-520, 1996.

- [9] M. Sayed and L. Partin, "Effect of shading on CDs/Cu^, S solar cells and optimal array design," in *Energy Com.*, vol. 14, 1975, pp. 61-71.

- [10] M. S. Swaleh and M. A. Green, "Effect of shunt resistance and bypass diode on the shadow tolerance of solar cell modules," *Solar Cells*, vol. 5, no. 2, pp. 183-198, 1982.

- [11] N. F. Shephard and R. S. Sugimura, "The integration of bypass diode with terrestrial photovoltaic modules and arrays," in *Proc. 17th IEEE Photovolt. Spec. Conf*, 1984, p. 676.

- [12] A. Brandstetter, "Solar cell array studies," inProc. Solar World Congr, 1983, pp. 1549-1553.

- [13] S. Singer, B. Rosenshtein, and S. Surazi, "Characterization of PV array output using a small number of measured parameters," *Solar Energy*, vol. 32, no. 5, pp. 603-607, 1984.

- [14] N. D. Kaushika, R. Gera, and K. Kaushika, "Hot spot protection in solar PV modules and arrays," in *Proc. Nat. Conf. Solar Energy Syst*, 1988, pp. 113-117.

- [15] A. Brandstetter and E. K. Inall, "Solar Cell Array Studies," Research School of Physical Sciences, Institute of Advanced Studies, Australian National University, Tech. Rep. NERDDC Project 82/2315, 1985.

- [16] S. W. Director, *Circuit Theory: A Computational Approach*. New York: Wiley, 1975.

- [17] M. A. Green, Solar Cells. Englewood Cliffs, NJ: Prentice-Hall, 1982.

- [18] A. Brandstetter and J. Bani, "Dimensionless groupings for photovoltaic performance analysis," *Energy Com. Manag.*, vol. 20, pp. 119-125, 1980.

- [19] F. C. Treble, Generating Electricity From the Sun. Oxford, U.K.:Pergamon Press, 1991.

**Narendra D. Kaushika** was born in 1941. He received the Ph.D. degree in radio electronics and space physics from Physical Research Laboratory, Gujarat University, India.

He is presently a Professor at the Centre for Energy Studies, Indian Institute of Technology, Delhi. His current research interests are solar photovoltaic and solar energy material devices and systems. He was a Visiting Professor at the University of Technology, Malaysia, in 1997. He was also a Visiting Research Fellow at the Victorian Solar Energy Council, Melbourne, Australia, in 1983, the Australian National University, Canberra, in 1990, and Queensland University, Brisbane, Australia, in 1982. He is author of over 150 research publications.

Nalin K. Gautam was born in 1962. He received the M.S. degree in mathematics from Agra University, India, in 1983, the M.S. degree in operational research from the University of Delhi, India, in 1985, and is currently pursuing the Ph.D. degree at the Indian Institute of Technology, Delhi.

His area of research is computer modeling and simulation of solar P V array characteristics.