### TITLE:

# Enhanced Drain Current of 4H-SiC MOSFETs by Adopting a Three-Dimensional Gate Structure

# AUTHOR(S):

Nanen, Yuichiro; Yoshioka, Hironori; Noborio, Masato; Suda, Jun; Kimoto, Tsunenobu

### CITATION:

Nanen, Yuichiro ...[et al]. Enhanced Drain Current of 4H-SiC MOSFETs by Adopting a Three-Dimensional Gate Structure. IEEE TRANSACTIONS ON ELECTRON DEVICES 2009, 56(11): 2632-2637

# **ISSUE DATE:**

2009-11

#### URL:

http://hdl.handle.net/2433/109802

### RIGHT:

© 2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

# Enhanced Drain Current of 4H-SiC MOSFETs by Adopting a Three-Dimensional Gate Structure

Yuichiro Nanen, Hironori Yoshioka, Masato Noborio, Student Member, IEEE, Jun Suda, and Tsunenobu Kimoto, Senior Member, IEEE

Abstract—4H-SiC (0001) metal-oxide-semiconductor fieldeffect transistors (MOSFETs) with a 3-D gate structure, which has a top channel on the (0001) face and side-wall channels on the {1120} face, have been fabricated. The 3-D gate structures with a 1-5- $\mu$ m width and a 0.8- $\mu$ m height have been formed by reactive ion etching, and the gate oxide has been deposited by plasma-enhanced chemical vapor deposition and then annealed in N<sub>2</sub>O ambient at 1300 °C. The fabricated MOSFETs have exhibited good characteristics: The  $I_{\rm ON}/I_{\rm OFF}$  ratio, the subthreshold swing, and  $V_{\rm TH}$  are  $10^9$ , 210 mV/decade, and 3.5 V, respectively. The drain current normalized by the gate width is increasing with decreasing the gate width. The normalized drain current of a  $1-\mu$ m-wide MOSFET is 16 times higher than that of a conventional planar MOSFET.

Index Terms-Metal-oxide-semiconductor field-effect transistor (MOSFET), multigate FET (MuGFET), silicon carbide (SiC), 3-D gate structure.

### I. INTRODUCTION

□ ILICON CARBIDE metal—oxide—semiconductor fieldeffect transistors (SiC MOSFETs) have attracted much attention as low-loss power MOSFETs as well as devices of integrated circuits for high-temperature use [1]. However, SiC MOSFETs have still suffered from low channel mobility and, thereby, low drain current due to the high interface state density of SiO<sub>2</sub>/SiC. In order to increase the drain current, several approaches can be considered. First, increasing the channel mobility has been intensively investigated by many groups. For example, oxidation or reoxidation in NO or N<sub>2</sub>O ambient is an attractive process to improve the inversion channel mobility [2], [3]. Oxidation or reoxidation in pyrogenic atmosphere is also an effective process to increase the inversion channel mobility [4]. The utilization of the  $\{11\overline{2}0\}$  face [5] or  $(000\overline{1})$  face [6] is another attractive approach to obtain a high channel mobility. Second, reducing the channel length is also effective to enhance the drain current [7], [8]. The third method is to increase the gate capacitance either by reducing the thickness of the gate oxide or by using the high- $\kappa$  material as the gate insulator [9].

Manuscript received February 18, 2009; revised May 28, 2009. First published September 15, 2009; current version published October 21, 2009. This work was supported in part by the Japan Society for the Promotion of Science under Grant-in-Aid for Scientific Research 21226008 and in part by the Ministry of Education, Culture, Sports, Science, and Technology, Japan, under the Global COE Program (C09). The review of this paper was arranged by Editor S. Bandyopadhyay.

The authors are with the Department of Electronic Science and Engineering, Kyoto University, Kyoto 615-8510, Japan (e-mail: nanen@semicon.kuee. kyoto-u.ac.jp).

Digital Object Identifier 10.1109/TED.2009.2030437

Another method to enhance the drain current is to increase the channel width. In advanced Si MOSFETs, MOSFETs with multigate structures have been extensively developed in order to increase the ON-current while minimizing the short-channel effects [10], [11]. In short-channel multigate MOSFETs, the influence of the drain potential on the channel is reduced because the electric field from the drain is effectively terminated by the multigates. The drain current of a multigate MOSFET is the sum of currents flowing along all the interfaces covered by the gate electrode. Therefore, the current of a multigate MOSFET is much higher than that of a conventional planar MOSFET with a given channel area, owing to the large effective channel width. When a 3-D gate structure is adopted to SiC (0001) MOSFETs, the drain current will be further enhanced due to the anisotropy of the inversion channel mobility; a high channel mobility on the {1120} sidewalls will enhance the drain current. The multigate structure can be applied to SiC power MOS devices with a lateral channel, such as doubleimplanted MOSFETs (DMOSFETs) and reduced surface field (RESURF) MOSFETs. In these devices, the channel with the multigate structure is not always formed in the high electric field regions. The short-channel SiC complementary MOS devices are another application of the multigate structure in the future.

In this paper, the authors have fabricated 4H-SiC (0001) MOSFETs with a 3-D gate structure with a  $0.8-\mu m$  height, a  $1-5-\mu m$  width, and a  $5-10-\mu m$  channel length. The fabricated devices showed good characteristics, and the 3-D gate structure MOSFET with the {1120} sidewall exhibited 16 times higher drain current than a conventional planar MOSFET. The mobility on the  $\{11\overline{2}0\}$  sidewall was estimated to be  $42 \text{ cm}^2/\text{V} \cdot \text{s}$ .

# II. DEVICE FABRICATION

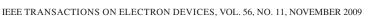

The schematic illustrations of a MOSFET with a 3-D gate structure employed in this paper are shown in Fig. 1(a) and (b). The height of the gate structure (H) was fixed at 0.8  $\mu$ m, the width (W) was varied from 1 to 5  $\mu$ m, and the channel length (L) was varied from 5 to 10  $\mu$ m. The sidewall plane of the 3-D gate structure is either the {1120} face or the {1100} face, which is vertical to the  $\{11\overline{2}0\}$  face. The depth of the n<sup>+</sup> region (source/drain) is 0.8  $\mu$ m (= H) to ensure that the current flows along the sidewall channels. By forming the p<sup>+</sup> region in the bottom plane, the threshold voltage of the bottom channel was significantly increased, so that the drain current flowing along the 3-D gate structure can be evaluated. When a gate oxide is formed by thermal oxidation, the oxide thickness on

NANEN et al.: ENHANCED DRAIN CURRENT OF 4H-SiC MOSFETs

Fig. 1. Schematic illustrations of an SiC 3-D gate structure MOSFET. (a) Bird's-eye view of the MOSFET. (b) Cross section of channel region.

the sidewalls becomes larger than that on the top plane due to the oxidation rate anisotropy of SiC [12]. The thick oxide on the sidewalls results in high threshold voltage and low drain current on the sidewall channels. In order to obtain a thinner gate oxide on the sidewalls than that on the top plane, the gate oxide was formed by plasma-enhanced chemical vapor deposition (PECVD), as described hereafter. The MOSFETs with a 3-D gate structure were fabricated on a p-type 8° off-axis 4H-SiC (0001) epilayer. The thickness and the acceptor concentration of the epilayer was 10  $\mu$ m and 7.8  $\times$  10<sup>15</sup> cm<sup>-3</sup>, respectively. The relatively deep (0.8  $\mu$ m) source and drain regions were formed by multiple N<sup>+</sup> implantation (80–700 keV with total dose of  $1.0 \times 10^{15}$  cm<sup>-2</sup> at 200 °C), combined with high-dose  $P^+$  implantation (10–110 keV with  $5.0 \times 10^{15}$  cm<sup>-2</sup> at 300 °C) into the surface region in order to minimize the contact resistance. A 2- $\mu$ m-thick SiO<sub>2</sub> deposited by PECVD was employed as an implantation mask. The 3-D structures with a  $0.8-\mu\mathrm{m}$ height and a 1–5- $\mu$ m width were formed by reactive ion etching (RIE) with a 1- $\mu$ m-thick SiO<sub>2</sub> mask. Subsequently, Al<sup>+</sup> ions were implanted to form the bottom p<sup>+</sup> region with the same SiO<sub>2</sub> mask. After covering the sample with a carbon cap [13], the implanted dopants were activated in Ar ambient at 1700 °C for 30 min. In order to reduce the damage induced by RIE, sacrificial oxidation at 1100 °C for 1 h was performed. After depositing SiO<sub>2</sub> as a gate oxide by PECVD, N<sub>2</sub>O annealing at 1300 °C for 30 min was carried out to reduce the SiO<sub>2</sub>/SiC interface state density [14]. The thickness of the deposited oxide is 70 nm on the top plane and 45 nm on the sidewall plane, as determined by cross-sectional scanning electron microscopy. Ni was deposited and annealed at 950 °C for 10 min as ohmic contacts on the source and drain. Al was employed as a gate electrode.

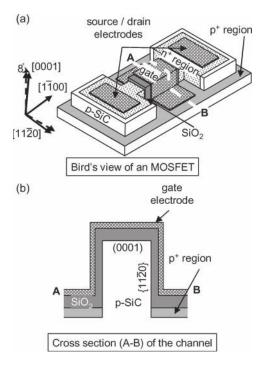

Fig. 2. (a) Scanning electron microscopy image of the fabricated 4H-SiC (0001) MOSFET with a 3-D gate structure. (b) Magnified image of the sidewall channel region indicated by a square in (a).

Fig. 2 shows the scanning electron microscopy image of a fabricated MOSFET with a 1- $\mu$ m-wide 3-D gate structure. As shown in the figure, the sidewall plane is flat and nearly vertical to the bottom plane. The gate electrode covers not only the 3-D gate structure but also the edges of source and drain regions, although the electrode covers only the 3-D gate structure in Fig. 1 for simplicity.

To investigate the effect of the 3-D gate structure, a planar MOSFET was also fabricated on the same chip.

# III. RESULTS AND DISCUSSIONS

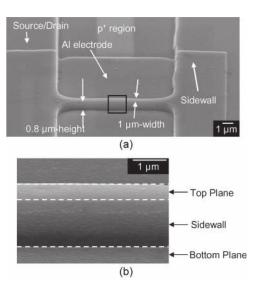

Fig. 3(a) and (b) shows the drain characteristics of fabricated 3-D gate MOSFETs with the  $\{11\bar{2}0\}$  sidewalls (a) and  $\{1\bar{1}00\}$  sidewalls (b), respectively. The channel length and gate width of the MOSFETs are 5 and 1  $\mu\text{m}$ , respectively. Both of the figures show good characteristics as a MOSFET, and the gate leakage current was very low, i.e., in the 1–100-pA range. The drain current of the MOSFET with the  $\{11\bar{2}0\}$  sidewalls is higher than that with the  $\{1\bar{1}00\}$  sidewalls. This can be attributed to higher channel mobility on the  $\{11\bar{2}0\}$  sidewalls than that on the  $\{1\bar{1}00\}$  sidewalls.

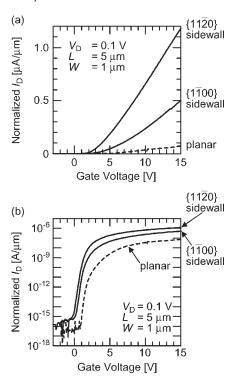

Fig. 4(a) shows the gate characteristics of the MOSFETs with the  $\{11\bar{2}0\}$  and  $\{1\bar{1}00\}$  sidewalls, as well as that of a conventional planar MOSFET in the linear region  $(V_D=0.1~\rm V)$ . Here, the drain current is normalized by the double of the gate width (2W), while that of the planar MOSFET is normalized by the gate width (W). Since the 3-D gate structure will be repeated in parallel to increase the total drain current in real devices, the drain current was normalized by not W but W assuming a periodic 3-D gate structure with a projected gate width of W and a spacing of W (period: W). The drain current of the 1-W-m-wide gate MOSFET with the W-m-wide gate MOSFET with the fabricated MOSFETs exhibited good ON-/OFF-current ratio and subthreshold swing.

Fig. 3. Drain characteristics of 3-D gate structure MOSFETs (a) with the  $\{11\bar{2}0\}$  and (b)  $\{1\bar{1}00\}$  sidewalls. The gate voltage was varied from 0 to 15 V with a 3-V step.

Fig. 4. (a) Gate and (b) subthreshold characteristics of 3-D gate structure MOSFETs with the  $\{11\overline{2}0\}$  and  $\{1\overline{1}00\}$  sidewalls and conventional planar MOSFET. The drain current of the 3-D gate MOSFET is normalized by the double of the gate width (2W), while that of planar MOSFET is normalized by the gate width (W).

Table I summarizes the normalized drain current  $(I_D/2W)$  at  $V_G=12$  V and  $V_D=0.1$  V, threshold voltage  $(V_{\rm TH})$ , the subthreshold swing (S), the ratio of the ON-/OFF-current  $(I_{\rm ON}/I_{\rm OFF})$  of the 1- $\mu$ m-wide and 5- $\mu$ m-long 3-D gate

TABLE I

Characteristics of the Fabricated 1- $\mu$ m-Wide and 5- $\mu$ m-Long 3-D Gate Mosfets with the {11 $\overline{2}$ 0} and {1 $\overline{1}$ 00} sidewalls, While Those of the Planar Mosfet Are Also Shown. The Normalized Drain Current ( $I_D/2W$ ) at  $V_G=12$  V and  $V_D=0.1$  V, Threshold Voltage ( $V_{\rm TH}$ ), Subthreshold Swing (S), and Ratio of on-/off-Current ( $I_{\rm ON}/I_{\rm Off}$ ) are Summarized

|                                  | $I_{\rm D}/2W$ $[\mu{\rm A}/\mu{\rm m}]$ | $V_{ m TH}$ [V] | S [mV/decade] | $I_{ m ON}/I_{ m OFF}$ |

|----------------------------------|------------------------------------------|-----------------|---------------|------------------------|

| $\{11\bar{2}0\}$ sidewall MOSFET | 0.86                                     | 3.4             | 209           | 10 <sup>9</sup>        |

| {1100} sidewall<br>MOSFET        | 0.34                                     | 4.8             | 201           | 10 <sup>9</sup>        |

| planar<br>MOSFET                 | $0.05 \ (I_{ m D}/W)$                    | 5.3             | 177           | 108                    |

MOSFETs with the  $\{11\bar{2}0\}$  and  $\{1\bar{1}00\}$  sidewalls, and those of a planar MOSFET.

The subthreshold swing (S) obtained from the MOSFETs fabricated in this paper is rather good, 177–209 mV/decade, compared with previous reports (220–471 mV/decade) [15]–[17].

The subthreshold swings (S) of the 3-D gate MOSFETs are about 30 mV/decade higher than that of the planar MOSFET. This may be caused by a relatively high interface state density in the energetically deep region for SiO<sub>2</sub>/SiC {1120} and {1100} [18]. The threshold voltage of the MOSFET with the {1120} and {1100} sidewalls and that of the planar MOSFET is 3.5, 4.8, and 5.3 V, respectively. The threshold voltage of the {1120} sidewall MOSFET is about 1.5 V smaller than that of the planar MOSFET. This can be due to the thinner oxide thickness on the sidewall planes than that for the planar MOSFET. The threshold voltage of the {1120} sidewall MOSFET is also smaller than that of the  $\{1\bar{1}00\}$  MOSFET. This can originate from the lower interface state density of  $SiO_2/4H$ -SiC {1120} near the conduction band edge than that of SiO<sub>2</sub>/4H-SiC {1100} because the threshold voltage is evaluated from the linear extrapolation in the gate characteristics [Fig. 4(a)].

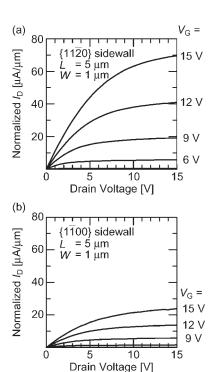

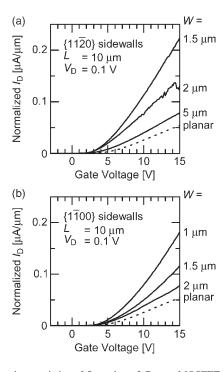

Fig. 5(a) and (b) shows the gate characteristics of 10- $\mu$ m-long 3-D gate MOSFETs with various gate widths with the  $\{11\bar{2}0\}$  sidewalls (a) and with the  $\{1\bar{1}00\}$  sidewalls (b), respectively. As shown in both panels, the normalized drain current increases with decreasing the gate width. This indicates that the geometric effects, forming the inversion channel on the sidewall planes, are effective to increase the drain current per channel area. However, the effects of the high channel mobility on sidewall planes cannot be readily addressed from this result.

The authors tried to estimate the channel mobility on the sidewall channels with simple equations as described next.

The drain current of a 3-D gate MOSFET in the linear region can be written as

$$\begin{split} I_D &= I_{D(\text{top})} + 2I_{D(\text{side})} \\ &= \mu_{\text{top}} \frac{W}{L} C_{\text{ox(top)}} \left( V_G - V_{\text{TH(top)}} \right) V_D \\ &+ 2\mu_{\text{side}} \frac{H}{L} C_{\text{ox(side)}} \left( V_G - V_{\text{TH(side)}} \right) V_D \end{split} \tag{1}$$

NANEN et al.: ENHANCED DRAIN CURRENT OF 4H-SiC MOSFETs

Fig. 5. Gate characteristics of 5- $\mu$ m-long 3-D gate MOSFETs with various gate widths with the (a)  $\{11\overline{2}0\}$  and (b)  $\{1\overline{1}00\}$  sidewalls.

where  $I_{D(\text{top})}$  and  $I_{D(\text{side})}$  are the drain current flowing in the top channel and in the sidewall channels,  $\mu_{\text{top}}$  and  $\mu_{\text{side}}$  are the inversion channel mobility in the top channel and in the sidewall channels,  $V_{\text{TH(top)}}$  and  $V_{\text{TH(side)}}$  are the threshold voltage in the top channel (5.3 V) and in the sidewall channels (3.4 V), and  $C_{\text{ox(top)}}$  and  $C_{\text{ox(side)}}$  are the gate capacitance per unit area of the top plane  $(4.9 \times 10^{-8} \text{ F/cm}^2)$  and of the sidewall planes  $(7.6 \times 10^{-8} \text{ F/cm}^2)$ , respectively. W, H, and L are the width, the height  $(0.8 \ \mu\text{m})$ , and the channel length  $(10 \ \mu\text{m})$  of the 3-D gate structure, respectively.  $V_G$  and  $V_D$  are the gate  $(12 \ \text{V})$  and drain voltage  $(0.1 \ \text{V})$ , respectively. The  $I_{D(\text{side})}$  can be expressed as

$$I_{D(\text{side})} = I_{D(\text{top})} \cdot \frac{\mu_{\text{side}}}{\mu_{\text{top}}} \frac{H}{W} \frac{C_{\text{ox(side})}}{C_{\text{ox(top)}}} \frac{V_g - V_{\text{TH(side)}}}{V_g - V_{\text{TH(top)}}}. \quad (2)$$

Substituting (2) into (1), the drain current normalized by the double of the gate width  $(I_D/2W)$  can be expressed as

$$\frac{I_D}{2W} = \frac{I_{D(\text{top})}}{W} \left( \frac{1}{2} + \frac{\mu_{\text{side}}}{\mu_{\text{top}}} \frac{H}{W} \frac{C_{\text{ox(side)}}}{C_{\text{ox(top)}}} \frac{V_g - V_{\text{TH(side)}}}{V_g - V_{\text{TH(top)}}} \right). \tag{3}$$

All the parameters in (3) are known except for  $I_{D(\text{top})}$  and  $\mu_{\text{side}}/\mu_{\text{top}}$ . By using the normalized drain current of the planar MOSFET  $(I_{D\,\text{planar}}/W_{\text{planar}})$  as  $I_{D(\text{top})}/W$ ,  $I_{D}/2W$  can be calculated by assuming the only unknown parameter  $R=\mu_{\text{side}}/\mu_{\text{top}}$ .

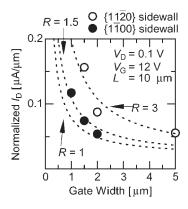

Fig. 6 shows the dependence of the normalized drain current on the gate width at  $V_G=12$  V and  $V_D=0.1$  V. The open and closed symbols indicate the experimental results obtained from the  $\{11\bar{2}0\}$  sidewall MOSFETs and the  $\{1\bar{1}00\}$  sidewall MOSFETs, respectively. The dotted lines denote the dependence calculated for the mobility ratio  $R=\mu_{\rm top}/\mu_{\rm side}=1,1.5,3$  by using (3), where the  $I_{D({\rm top})}/W$  value was deter-

Fig. 6. Dependence of the normalized drain current on the gate width at  $V_G=12~\rm V$  and  $V_D=0.1~\rm V$ . The open and closed symbols denote the experimental results for the  $\{11\bar{2}0\}$  and  $\{1\bar{1}00\}$  sidewall MOSFET, respectively. The dotted lines show the dependence calculated for the mobility ratio  $R=\mu_{\rm side}/\mu_{\rm top}=1,1.5,3$  by using the characteristics of the planar MOSFET.

mined from the characteristics of the planar MOSFET. The closed symbols ( $\{1\bar{1}00\}$  sidewall MOSFETs) and open symbols ( $\{11\bar{2}0\}$  sidewall MOSFETs) show reasonable agreement with the line simulated for R=1.5 and R=3, respectively. The inversion channel mobility in the top channel was determined as 14 cm²/Vs from the characteristics of the planar MOSFET. Then, the inversion channel mobility on the  $\{11\bar{2}0\}$  and  $\{1\bar{1}00\}$  sidewalls can be estimated to be 42 and 21 cm²/Vs, respectively.

Thus, the 3-D gate structure MOSFETs are attractive for increasing the drain current of SiC MOSFETs. The major disadvantages include the increased input capacitance and possibly increased gate leakage.

As the MOSFETs were fabricated on a 4H-SiC (0001) wafer  $8^{\circ}$  inclined toward the [1120] direction, the {1120} sidewalls are apart from the exact  $(11\overline{2}0)$  face. The evaluated mobility of the sidewalls is the average mobility of the two sidewall channels. Although their oxide-forming process is different from that of this paper, Yano et al. have investigated the mobility of a trench MOSFET which has a single sidewall channel on the  $\{1120\}, \{\overline{1120}\}, \{1\overline{100}\}, \text{ and } \{\overline{1100}\} \text{ faces, where the oxides}$ were formed by wet oxidation at 1150 °C for 150 min and followed by wet reoxidation anneal at 750 °C for 180 min, and NO annealing at 1150 °C for 60 min was also carried out [19]. They reported that the mobility on the  $\{1\overline{1}00\}$  and  $\{\overline{1}100\}$ faces is 32 and 35 cm $^2/V \cdot s$ , respectively. These mobilities are higher than that of the  $\{1\overline{1}00\}$  sidewall MOSFET fabricated in this paper. On the other hand, they estimated the mobility on the  $\{11\overline{2}0\}$  and  $\{\overline{1}\overline{1}20\}$  faces as 43 and 21 cm<sup>2</sup>/V · s, respectively, which are similar to that of the  $\{11\bar{2}0\}$  sidewall MOSFET fabricated in this paper. The difference of the mobility values may originate from the difference of the taper of the sidewalls and/or the formation process of the gate oxides. In fact, the mobility in the accurate  $(11\overline{2}0)$  and  $(\overline{1}\overline{1}20)$  sidewall channels has been estimated to be 72 and 66 cm<sup>2</sup>/V · s by the same group, respectively [20].

# IV. CONCLUSION

Some 4H-SiC (0001) MOSFETs with a 3-D gate structure have been fabricated and electrically characterized. The

3-D structures, which have flat sidewalls nearly vertical to the bottom plane, were formed by RIE. The sidewall plane of the gate structure is either  $\{11\bar{2}0\}$  or  $\{1\bar{1}00\}$ . The drain current normalized by the gate width increased with decreasing the gate width, and the normalized drain current of the 1- $\mu$ m-wide MOSFET with the  $\{11\bar{2}0\}$  sidewalls was about 16 times higher than that of a planar MOSFET. This improvement of the drain current originates from both the geometrical effects and the high inversion channel mobility on the  $\{11\bar{2}0\}$  sidewalls. The inversion channel mobility on the  $\{11\bar{2}0\}$  sidewall channels was estimated to be  $42~\text{cm}^2/\text{V}\cdot\text{s}$ .

### REFERENCES

- J. Zhao, G. Pensl, T. Kimoto, J. Cooper, and M. Weiner, "Special issue on silicon carbide devices and technology," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 1795–1797, Aug. 2008.

- [2] G. Chung, C. Tin, J. Williams, K. McDonald, R. Chanana, R. Weller, S. Pantelides, L. Feldman, O. Holland, M. Das, and J. Palmour, "Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide," *IEEE Electron Device Lett.*, vol. 22, no. 4, pp. 176–178, Apr. 2001.

- [3] L. Lipkin, M. Das, G. Chung, J. Williams, N. Saks, and J. Palmour, "N<sub>2</sub>O processing improved the 4H- SiC/N<sub>2</sub>O interface," *Mater. Sci. Forum*, vol. 383–393, pp. 985–988, 2002.

- [4] R. Kosugi, S. Suzuki, M. Okamoto, S. Harada, J. Senzaki, and K. Fukuda, "Strong dependence of the inversion mobility of 4H and 6H SiC(0001) MOSFETs on the water content in pyrogenic re-oxidation annealing," *IEEE Electron Device Lett.*, vol. 23, no. 3, pp. 136–138, Mar. 2002.

- [5] H. Yano, T. Hirao, T. Kimoto, H. Matsunami, K. Asano, and Y. Sugawara, "High channel mobility in inversion layers of 4H-SiC MOSFETs by utilizing (1120) face," *IEEE Electron Device Lett.*, vol. 20, no. 12, pp. 611–613, Dec. 1999.

- [6] K. Fukuda, W. Cho, K. Arai, S. Suzuki, J. Senzaki, and T. Tanaka, "Effect of oxidation method and post-oxidation annealing on interface properties of metal-oxide-semiconductor structures formed on n-type 4H-SiC C(0001) face," Appl. Phys. Lett., vol. 77, no. 6, pp. 866–868, Aug. 2000.

- [7] M. Matin, A. Saha, and J. Cooper, "A self-aligned process for high-voltage, short-channel vertical DMOSFETs in 4H-SiC," *IEEE Trans. Electron Devices*, vol. 51, no. 10, pp. 1721–1725, Oct. 2004.

- [8] M. Noborio, Y. Kanzaki, J. Suda, and T. Kimoto, "Experimental and theoretical investigations on short-channel effects in 4H-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 9, pp. 1954–1962, Sep. 2005.

- [9] T. Hatayama, S. Hino, N. Miura, T. Oomori, and E. Tokumitsu, "Remarkable increase in the channel mobility of SiC-MOSFETs by controlling the interfacial SiO<sub>2</sub> layer between Al<sub>2</sub>O<sub>3</sub> and SiC," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 2041–2045, Aug. 2008.

- [10] D. Hisamoto, T. Kaga, and E. Takeda, "Impact of the vertical SOI 'DELTA' structure on planar device technology," *IEEE Trans. Electron Devices*, vol. 38, no. 6, pp. 1419–1424, Jun. 1991.

- [11] J. Colinge, FinFETs and Other Multi-Gate Transistor. New York: Springer-Verlag, 2008.

- [12] K. Ueno, "Orientation dependence of the oxidation of SiC surfaces," Phys. Stat. Sol. (A), vol. 162, no. 1, pp. 299–304, Jan. 1997.

- [13] Y. Negoro, K. Katsumoto, T. Kimoto, and H. Matsunami, "Electronic behaviors of high-dose phosphorus-ion implanted 4H-SiC (0001)," *J. Appl. Phys.*, vol. 96, no. 1, pp. 224–228, Jul. 2004.

- [14] T. Kimoto, H. Kawano, M. Noborio, and J. Suda, "Improved dielectric and interface properties of 4H-SiC MOS structures processed by oxide deposition and N<sub>2</sub>O annealing," *Mater. Sci. Forum*, vol. 527–529, pp. 987–990, 2006

- [15] Y. Wang, K. Tang, T. Khan, M. Balasubramanian, H. Naik, W. Wang, and T. Chow, "The effect of gate oxide processes on the performance of 4H-SiC MOSFETs and gate-controlled diodes," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 2046–2053, Aug. 2008.

- [16] T. Kimoto, Y. Kanzaki, M. Noborio, H. Kawano, and H. Matsunami, "Interface properties of metal-oxide-semiconductor structures on 4H-SiC {0001} and (1120) formed by N<sub>2</sub>O oxidation," *Jpn. J. Appl. Phys.*, vol. 44, no. 3, pp. 1213–1218, Mar. 2005.

- [17] H. Yano, T. Hatayama, Y. Uraoka, and T. Fuyuki, "Characterization of 4H-SiC MOSFETs with NO-annealed CVD oxide," *Mater. Sci. Forum*, vol. 527–529, pp. 971–974, 2006.

- [18] H. Yano, T. Hirao, T. Kimoto, and H. Matsunami, "A cause for highly improved channel mobility of 4H-SiC metal-oxide-semiconductor field-effect transistors on the (1120) face," *Appl. Phys. Lett.*, vol. 78, no. 3, pp. 374–376, Jan. 2001.

- [19] H. Yano, H. Nakao, H. Mikami, T. Hatayama, Y. Uraoka, and T. Fuyuki, "Anomalously anisotropic channel mobility on trench sidewalls in 4H-SiC trench-gate metal-oxide-semiconductor field-effect transistors fabricated on 8° off substrates," *Appl. Phys. Lett.*, vol. 90, no. 4, p. 042102, Jan. 2007.

- [20] H. Yano, H. Nakao, T. Hatayama, Y. Uraoka, and T. Fuyuki, "Increased channel mobility in 4H-SiC UMOSFETs using on-axis substrates," *Mater. Sci. Forum*, vol. 556/557, pp. 807–810, 2007.

Yuichiro Nanen was born in Mie, Japan, on September 30, 1985. He received the B.E. degree in electrical engineering from Kyoto University, Kyoto, Japan, in 2008, where he is currently working toward the M.E. degree.

His current research activity includes fabrication of SiC MOSFETs and characterization of MOS interface properties.

**Hironori Yoshioka** was born in Japan in 1976. He received the B.E. and M.E. degrees from Kyoto University, Kyoto, Japan, where he is currently working toward the Ph.D. degree in the electronic science and engineering.

In 2002, he joined Toshiba Company, where he was engaged in the development of Si power MOSFETs. His main research activities include nanoscale Si devices such as Si-nanowire MOSFETs and diodes.

Kariya, Japan.

**Masato Noborio** (S'06) was born in Nara, Japan, in 1981. He received the B.E., M.E., and Ph.D. degrees in electrical and electronic engineering from Kyoto University, Kyoto, Japan, in 2004, 2006, and 2009, respectively.

His research interests include short-channel effects in SiC MOSFETs, characterization of SiC MIS interface properties, device simulation for SiC high-voltage devices, designing and fabrication of SiC lateral power MOSFETs, and device processes. Since 2009, he has been with DENSO Corporation,

NANEN et al.: ENHANCED DRAIN CURRENT OF 4H-SiC MOSFETs

2637

**Jun Suda** was born in Japan in 1969. He received the B.E., M.E., and Ph.D. degrees from Kyoto University, Kyoto, Japan.

From 1992 to 1997, he worked on molecular-beam epitaxy and structural and optical characterization of ZnMgSSe strained quantum-well structures for short-wavelength optoelectronics. In 1997, he started research on group-III nitride (III-N) and SiC at Kyoto University, where he is currently an Associate Professor with the Department of Electronic Science and Engineering. His research interests include the

heteroepitaxial growth of III-N, functional integration of III-N and SiC by nanoscale control of the heterointerface, and design and characterization of wide-bandgap semiconductor electronic devices and wide-bandgap MEMS. He has authored or coauthored over 80 publications in peer-reviewed journals and international conferences and is the inventor of 12 pending patents.

Dr. Suda is a member of The Materials Research Society, The Japan Society of Applied Physics, and The Japanese Association for Crystal Growth.

**Tsunenobu Kimoto** (M'03–SM'06) received the B.E. and M.E. degrees in electrical engineering and the Ph.D. degree, based on his work on SiC epitaxial growth, characterization, and high-voltage diodes, from Kyoto University, Kyoto, Japan, in 1986, 1988, and 1996, respectively.

He joined Sumitomo Electric Industries, Ltd., Osaka, Japan, in April 1988, where he conducted research on amorphous Si solar cells and the semiconducting diamond material. In 1990, he started his academic carrier as a Research Associate with Kyoto

University, where he is currently a Professor with the Department of Electronic Science and Engineering. From September 1996 to August 1997, he was a Visiting Scientist with Linköping University, Linköping, Sweden, where he was involved in the fast epitaxy of SiC and high-voltage Schottky barrier diodes. He has published over 200 papers in scientific journals and more than 200 papers in international conference proceedings. His main research activity includes SiC epitaxial growth, optical and electrical characterization, defect electronics, ion implantation, MOS physics, and high-voltage devices. He has also been involved in nanoscale Si devices, novel materials for nonvolatile memory, and GaN-based electronic devices.

Dr. Kimoto is a member of JSAP, IEICE, and IEE.