### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

## Enhancing automotive embedded systems with FPGAs

Shanker, Shreejith

2016

Shanker, S. (2016). Enhancing automotive embedded systems with FPGAs. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/67064

https://doi.org/10.32657/10356/67064

Downloaded on 26 Aug 2022 01:03:32 SGT

#### NANYANG TECHNOLOGICAL UNIVERSITY

## Enhancing Automotive Embedded Systems with FPGAs

Shreejith Shanker

#### School of Computer Science and Engineering

A thesis submitted to Nanyang Technological University in partial fulfilment of the requirements for the degree of Doctor of Philosophy

April 2016

#### THESIS ABSTRACT

#### Enhancing Automotive Embedded Systems with FPGAs

by

Shreejith Shanker

Doctor of Philosophy School of Computer Science and Engineering Nanyang Technological University, Singapore

Modern vehicles represent a complex distributed cyber-physical system that simultaneously handles critical functions like drive-by-wire systems, non-critical functions like window/door control, and compute intensive multimedia functions. Distributed electronic control units (ECUs), which integrate processing elements and supporting peripherals (network interfaces, memory), implement a variety of functions in software, and information is exchanged between ECUs and sensors/actuators over in-vehicle networks. As the complexity of applications rises with increasing automation, extensive hardware support is required in the form of multicore processors or special purpose hardware accelerators to offer required levels of performance. Additional features also drive an increase in the number of ECUs since new functions are rarely consolidated on existing ECUs. Furthermore, network interfaces implemented as ASICs or dedicated logic must be adapted to handle increased communication loads, consuming power and requiring more infrastructure support in terms of cabling and weight. The increasing number of safety-critical functions further impacts complexity if existing one-to-one redundancy schemes are applied. Rising automation also poses news challenges like security, with researchers showing that internal networks are easily manipulated with catastrophic effects and total loss of control. Our research aims to address these challenges using architectural enhancements that are transparent at the computational and network levels, leveraging the capabilities of reconfigurable hardware. We present advanced ECU architectures with extended network capabilities, apply these in the context of safety critical systems, explore ways of extending these schemes to offer advanced security features, and show how such advanced systems can be validated in hardware. Our work represents an advancement in the state of the art with regard to applying FPGAs in vehicular systems.

#### Acknowledgements

I take this opportunity to thank my supervisor, Prof. Suhaib A Fahmy, for giving me the opportunity to work on this exciting project, in association with TUM CREATE, Singapore. His enthusiasm and exuberance have helped me to carry out my research with composure and confidence. He has been appreciative of my ideas and encouraged critical thinking and technical writing, which have helped me improve my skills. I am also thankful to Prof. Samarjit Chakraborty for providing the opportunity to work at the Institute for Real-Time Computer Systems, Technical University of Munich as part of the Joint PhD program, and for his guidance and support during my PhD. I am also grateful to Dr. Martin Lukasiewycz, Principal Investigator at TUM CREATE, for his guidance, support, and suggestions. His experience in the automotive industry helped me channel my research into relevant topics and areas of interest.

I would also like to use this opportunity to thank to my colleagues and peers at the Centre for High Performance Embedded Systems (CHiPES), especially Dr. Sharad Sinha, Dr. Vipin Kizheppatt, Rakesh Varier, Dr. Neethu Robinson, Pham Hung Thinh, Dr. Jiang Lianlian, Ronak Bajaj, Abhishek Jain, Abdullah Shamil, Dr. Kavitha Jubin, and Dr. Smitha Sreekumar for their invaluable suggestions and support. Our laboratory executive, Chua Ngee Tat has been enthusiastic in providing me with help and support on issues related to networks and software at CHiPES. I am also grateful to my friends and fellow PhD candidates Rahul Varier and Dr. Amrith Dhananjay for their companionship and support. I am also thankful to my colleagues at TUM CREATE and the Technical University of Munich, especially Dr. Sidharta Andalam, Dr. Sebastian Steinhorst, Philipp Mundhenk, Florian Sagstetter, Martin Becker, and Martin Geier for their suggestions and creative ideas.

I would also like to thank Prof. Ian McLoughlin, University of Kent (formerly NTU), and Prof. Vinod A Prasad in the School of Computer Science and Engineering at NTU for their guidance and encouragement during my coursework and otherwise. I also express my gratitude to Prof. Douglas Maskell, Prof. Nachiket Kapre, Prof. Kyle Rupnow, and Prof. Arvind Easwaran for their guidance and research support.

I also use this opportunity to thank my previous employers Processor Systems India Pvt. Ltd (ProcSys) in Bangalore for giving me the opportunity to work in the then emerging domain of reconfigurable computing systems for high performance applications. My former mentors Manjusha S., Vinod Narippatta, Hansraj V., and Jaison T. D. were inspiring, and provided me challenging scenarios to stimulate my interest in FPGA design, and their guidance and expertise have proven invaluable. I am also thankful to my previous employer Digital Systems Design Group (DSD), Vikram Sarabhai Space Centre (VSSC), Trivandrum, India, for providing me with the opportunity to work for the Indian Space Research Organisation (ISRO) on cutting edge technology and complex projects. I would like to thank my senior officials at VSSC, A. K. Abdul Samad and Subha Varier, for their guidance on deterministic system design and space technology standards, ideas which have been extremely useful during my research.

Finally, I am indebted to my family and my parents, for their prayers and encouragement. I thank them for their understanding and their efforts to support me in pursuing higher studies. I am also extremely thankful to my wife for her constant support and patience during this period.

## Contents

| A        | Acknowledgements ii |         |                                                         |   |    |  |  |

|----------|---------------------|---------|---------------------------------------------------------|---|----|--|--|

| Li       | st of               | Abbro   | eviations                                               |   | xi |  |  |

| 1        | Intr                | oduct   | ion                                                     |   | 1  |  |  |

|          | 1.1                 | Autor   | motive ECUs and In-Vehicle Networks                     |   | 5  |  |  |

|          | 1.2                 | Motiv   | vation                                                  |   | 11 |  |  |

|          | 1.3                 | Objec   | etives                                                  |   | 13 |  |  |

|          | 1.4                 | Contr   | ibutions                                                |   | 14 |  |  |

|          | 1.5                 | Thesis  | s Organisation                                          |   | 16 |  |  |

|          | 1.6                 | Public  | cations                                                 | • | 16 |  |  |

| <b>2</b> | Lite                | erature | e Survey                                                |   | 19 |  |  |

|          | 2.1                 | In Vel  | hicle Computing Systems                                 |   | 20 |  |  |

|          | 2.2                 | In Vel  | hicle Networks                                          |   | 23 |  |  |

|          |                     | 2.2.1   | Controller Area Networks                                |   | 25 |  |  |

|          |                     |         | 2.2.1.1 Protocol Specification and Scheduling           | • | 25 |  |  |

|          |                     |         | 2.2.1.2 Implementations and Extensions                  | • | 29 |  |  |

|          |                     | 2.2.2   | FlexRay                                                 | • | 31 |  |  |

|          |                     |         | 2.2.2.1 Protocol Specification                          |   | 32 |  |  |

|          |                     |         | 2.2.2.2 Communication, Scheduling, and Implementations  |   | 37 |  |  |

|          |                     |         | 2.2.2.3 Performance, Applications, and Limitations      | • | 42 |  |  |

|          |                     | 2.2.3   | Other Protocols                                         |   | 45 |  |  |

|          |                     |         | 2.2.3.1 Time-Triggered Ethernet                         |   | 45 |  |  |

|          |                     |         | 2.2.3.2 Media Oriented Systems Transport                |   | 49 |  |  |

|          | 2.3                 | Field   | Programmable Gate Arrays                                |   | 53 |  |  |

|          |                     | 2.3.1   | Reusing Resources with Dynamic Reconfiguration          |   | 55 |  |  |

|          |                     | 2.3.2   | FPGAs for In-vehicle Systems                            |   | 57 |  |  |

|          |                     |         | 2.3.2.1 FPGAs as Compute Units (ECUs)                   |   |    |  |  |

|          |                     |         | 2.3.2.2 FPGAs for Prototyping and Validation            |   | 62 |  |  |

|          |                     |         | 2.3.2.3 FPGAs in In-vehicle Networks                    | • | 63 |  |  |

|          | 2.4                 | •       | m-level Challenges : Security and Functional Validation |   | 65 |  |  |

|          | 2.5                 | Summ    | nary                                                    | • | 68 |  |  |

| 3        | $\mathbf{Ext}$      | ensible | e Network Interfaces                                    |   | 69 |  |  |

|          | 3.1                 | Introd  | luction                                                 |   | 69 |  |  |

|   | 3.2 | Related Work                                                                                                                              | 72  |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 3.3 | Contributions                                                                                                                             | 74  |

|   | 3.4 | Architecture Design                                                                                                                       | 75  |

|   |     | 3.4.1 Communication Controller                                                                                                            | 76  |

|   |     | 3.4.2 Implementation and Optimisations of Custom CC                                                                                       | 78  |

|   |     | 3.4.3 Controller Datapath Extensions                                                                                                      | 88  |

|   |     | 3.4.4 Timestamp Synchronisation Mechanism                                                                                                 | 90  |

|   | 3.5 | Implementation Results                                                                                                                    | 91  |

|   | 3.6 | Case Studies                                                                                                                              | 95  |

|   |     | 3.6.1 Deterministic Decoding of System-State Messages in Safety-                                                                          |     |

|   |     | Critical ECUs                                                                                                                             |     |

|   |     | 3.6.2 Extended Communication using Data-layer Extensions                                                                                  |     |

|   |     | 3.6.3 Time-Awareness for Messages                                                                                                         |     |

|   | ~ - | 3.6.4 Handling Volume Data at Interfaces                                                                                                  |     |

|   | 3.7 | Discussion                                                                                                                                |     |

|   | 3.8 | Summary                                                                                                                                   | 103 |

| 4 | Enł | nanced ECU Architectures 1                                                                                                                | .05 |

|   | 4.1 | Introduction                                                                                                                              | 105 |

|   | 4.2 | Related Work                                                                                                                              | 107 |

|   | 4.3 | Contributions                                                                                                                             | 109 |

|   | 4.4 | Consolidation Methods using PR                                                                                                            | 10  |

|   |     | 4.4.1 Evaluating Consolidation using Vendor-based PR 1                                                                                    | 12  |

|   | 4.5 | Redundancy for Safety-Critical ECUs                                                                                                       | 15  |

|   |     | 4.5.1 Extending FlexRay Communication Cycle                                                                                               |     |

|   |     | 4.5.2 Proposed Approach to Reconfiguration                                                                                                | 18  |

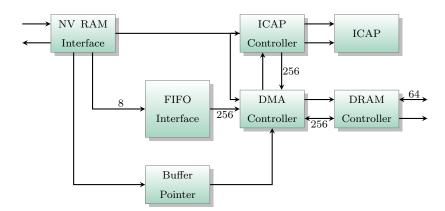

|   |     | 4.5.3 High-Speed Reconfiguration Management                                                                                               |     |

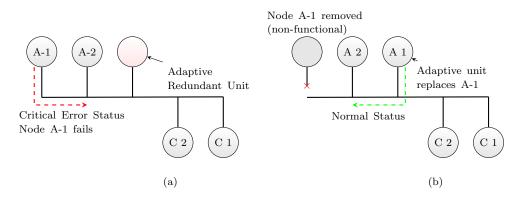

|   |     | 4.5.4 Distributed Redundancy                                                                                                              |     |

|   |     | 4.5.5 Validating PR-based Functional Fault Tolerance 1                                                                                    |     |

|   | 4.6 | Gateway ECUs for In-Vehicle Ethernet Backbones                                                                                            |     |

|   |     | 4.6.1 Zynq Hybrid FPGAs                                                                                                                   |     |

|   |     | 4.6.2 AEG Architecture                                                                                                                    |     |

|   |     | $4.6.2.1  \text{Receive Path}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                           |     |

|   |     | 4.6.2.2 Configurable Switch Interconnect                                                                                                  |     |

|   |     | 4.6.2.3 Transmit Path $\dots \dots \dots$ |     |

|   |     | 4.6.2.4 Translation for FlexRay/CAN Systems 1                                                                                             |     |

|   |     | 4.6.2.5 Run-time Management of Interface Configurations 1                                                                                 |     |

|   | 1 7 | 4.6.3 Evaluating the AEG on Zynq                                                                                                          |     |

|   | 4.7 | Summary                                                                                                                                   | .40 |

| 5 | Sec | uring Vehicular Networks 1                                                                                                                | 47  |

|   | 5.1 | Introduction                                                                                                                              | 47  |

|   | 5.2 | Related Work                                                                                                                              | 150 |

|   | 5.3 | Contributions                                                                                                                             | 153 |

|   | 5.4 |         | ity-Enhanced Network Interfaces: Enabling Zero Latency Mes-     |            |

|---|-----|---------|-----------------------------------------------------------------|------------|

|   |     |         | Ciphers                                                         | . 154      |

|   |     | 5.4.1   | Security Extensions in the Enhanced FlexRay Communica-          |            |

|   |     |         | tion Controller                                                 |            |

|   |     | 5.4.2   | Encryption in Software                                          |            |

|   |     | 5.4.3   | Evaluation of Security-Enhanced Network Interface               |            |

|   | 5.5 |         | ity-Aware Network Interfaces: Integrating System-level Security |            |

|   |     | 5.5.1   | Architecture                                                    |            |

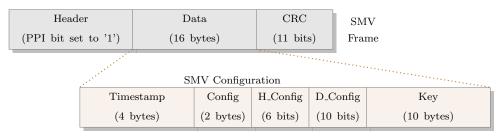

|   |     | 5.5.2   | Run-time Alteration of Cipher Parameters                        |            |

|   |     | 5.5.3   | System Evaluation                                               |            |

|   | 5.6 | Summ    | nary                                                            | . 172      |

| 6 | Fun | ctiona  | l Validation Platform                                           | 174        |

|   | 6.1 | Introd  | luction                                                         | . 174      |

|   | 6.2 | Relate  | ed Work                                                         | . 177      |

|   | 6.3 | Contr   | ibutions                                                        | . 180      |

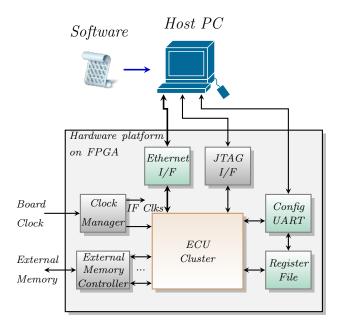

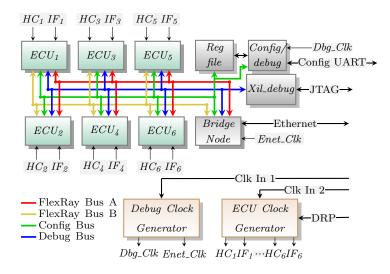

|   | 6.4 | Platfo  | rm Architecture                                                 | . 181      |

|   |     | 6.4.1   | Hardware Architecture                                           | . 181      |

|   |     | 6.4.2   | Management of the Platform                                      | . 186      |

|   |     | 6.4.3   | Accelerated Mode                                                | . 187      |

|   | 6.5 | Evalua  | ating Automotive ECUs on the Platform                           | . 189      |

|   |     | 6.5.1   | Test Cases                                                      | . 191      |

|   |     | 6.5.2   | Evaluating Case Study 1: Cluster of Non-Critical ECUs           | . 192      |

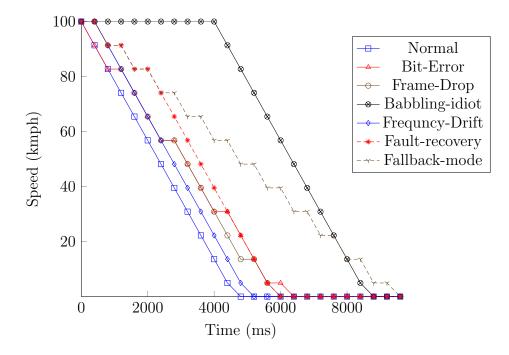

|   |     |         | 6.5.2.1 Network Error Injection                                 | . 192      |

|   |     |         | 6.5.2.2 Babbling Idiot Test                                     | . 193      |

|   |     |         | 6.5.2.3 Clock Drifts/Jitter                                     | . 194      |

|   |     | 6.5.3   | Evaluating Case Study 2: Cluster of Safety-Critical ECUs        | . 195      |

|   |     |         | 6.5.3.1 Network Error Injection                                 | . 195      |

|   |     |         | 6.5.3.2 Babbling Idiot Test                                     | . 196      |

|   |     |         | 6.5.3.3 Clock Drifts/Jitter                                     | . 196      |

|   |     | 6.5.4   | Acceleration Tests                                              | . 198      |

|   | 6.6 | Host 1  | Interface over PCIe                                             | . 198      |

|   | 6.7 | Summ    | hary                                                            | . 200      |

| 7 | Con | nclusio | ns and Future Research                                          | <b>201</b> |

|   | 7.1 | Summ    | nary of Contributions                                           | . 202      |

|   |     | 7.1.1   | Extensible Network Interfaces                                   |            |

|   |     | 7.1.2   | Enhanced ECU architectures                                      | . 203      |

|   |     | 7.1.3   | Network and System-level security                               | . 204      |

|   |     | 7.1.4   | Functional Validation Platform                                  |            |

|   | 7.2 | Future  | e Research                                                      | . 205      |

|   |     | 7.2.1   | Enhancing Evolving Time-Triggered Standards                     | . 205      |

|   |     | 7.2.2   | Distributed Fault-Tolerance                                     |            |

|   |     | 7.2.3   | Higher layer security management                                | . 206      |

|   |     | 7.2.4   | Hardware in the Loop Optimisation Flow                          | . 207      |

| 7.3 \$    | Summary | • • |  | • | • | • | <br>• | • | • | • | • | • | • | <br>• | • | • | <br>• | • | • | • | • | • | • | 207 |

|-----------|---------|-----|--|---|---|---|-------|---|---|---|---|---|---|-------|---|---|-------|---|---|---|---|---|---|-----|

| Bibliogra | aphy    |     |  |   |   |   |       |   |   |   |   |   |   |       |   |   |       |   |   |   |   |   |   | 209 |

## List of Figures

| 1.1        | Typical ECU architecture.                                            | 7        |

|------------|----------------------------------------------------------------------|----------|

| 2.1        | The abstraction layers in AUTOSAR                                    | 22       |

| 2.2        | Typical in-vehicle network architecture in a modern car.             | 24       |

| 2.3        | Frame format for Data Frames and Remote frames                       | 27       |

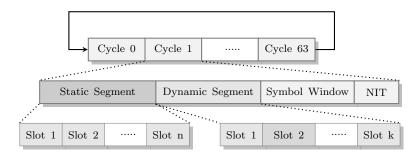

| 2.4        | FlexRay communication cycle                                          | 33       |

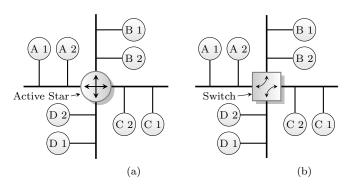

| 2.5        | FlexRay frame structure                                              | 35       |

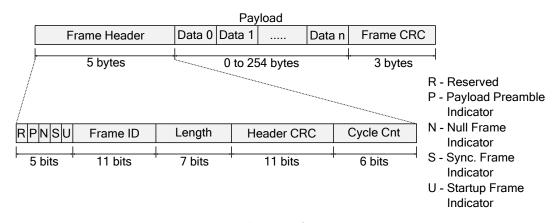

| 2.6        | A FlexRay node.                                                      | 36       |

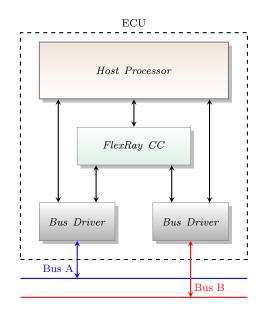

| 2.7        | A standard FlexRay network topology (a) and a switched network       |          |

|            | (b)                                                                  | 41       |

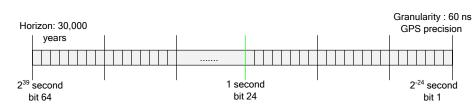

| 2.8        | 64-bit time format used in TTE                                       | 47       |

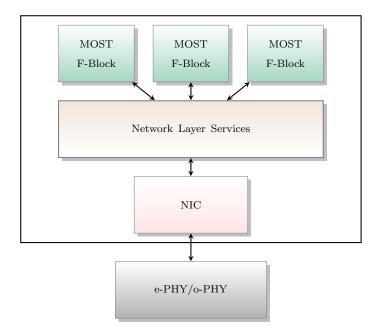

| 2.9        | MOST Device Model                                                    | 50       |

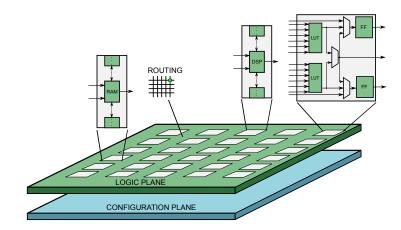

| 2.10       | An abstract visualisation of FPGA Architecture                       | 55       |

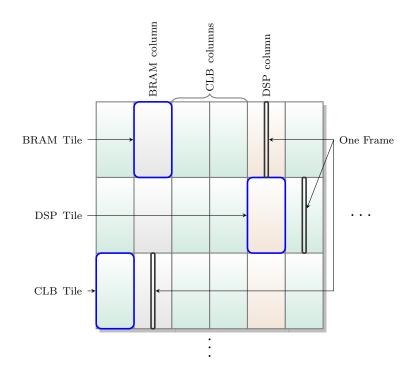

| 2.11       | A section from Virtex-6 FPGA architecture                            | 57       |

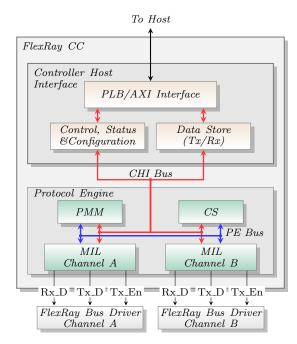

| 3.1        | Architecture of custom FlexRay communication controller              | 76       |

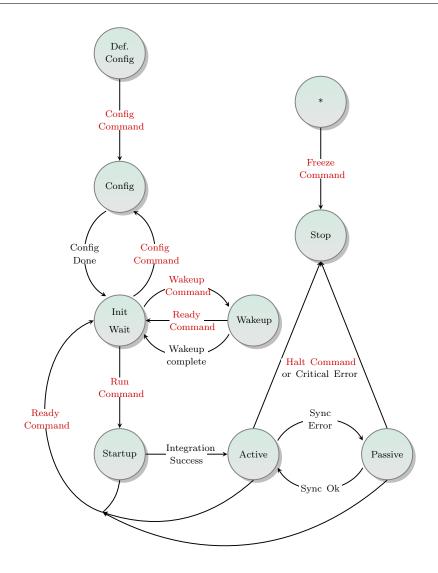

| 3.1<br>3.2 | FlexRay CC Modes of Operation.                                       | 70<br>80 |

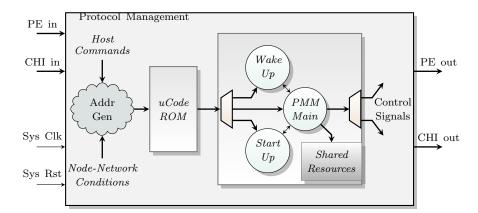

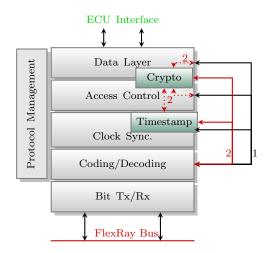

| 3.2<br>3.3 | Protocol Management Module (PMM) architecture.                       | 80<br>81 |

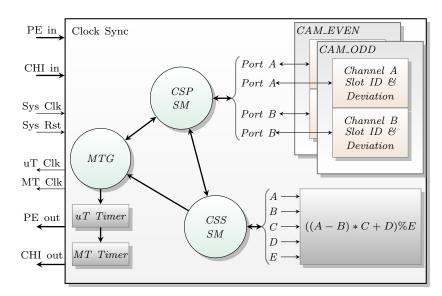

| 3.4        | Clock Sync (CS) module architecture                                  | 81<br>82 |

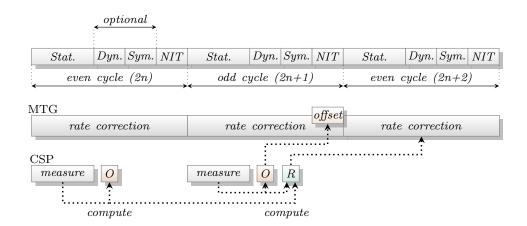

| 3.4        | Rate and offset computation by MTG and CSP.                          | 83       |

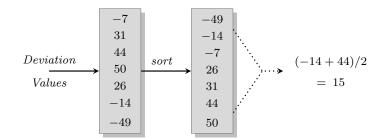

| 3.6        | Fault tolerant midpoint illustration for seven deviation values.     | 83       |

| 3.0<br>3.7 | CAM organisation and fault tolerant mid-point computation for        | 00       |

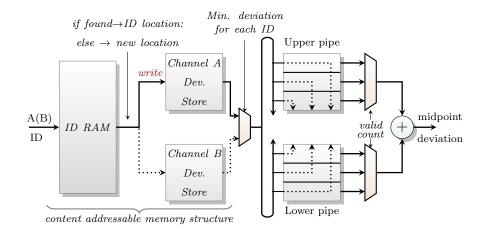

| 5.7        | offset correction.                                                   | 84       |

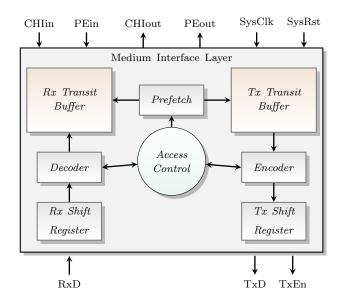

| 3.8        | Medium Interface Layer architecture.                                 | 85       |

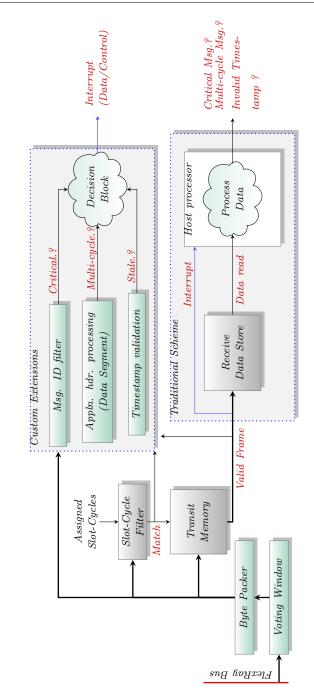

| 3.9        | Receive path extensions on custom CC versus traditional schemes.     | 89       |

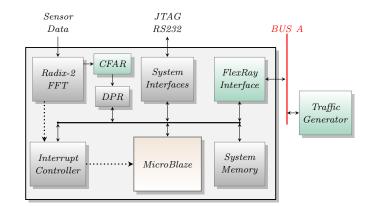

| 3.10       | Integrated ECU function on Spartan-6 FPGA                            | 94       |

| 3.11       | Test setup for brake-by-wire system.                                 | 96       |

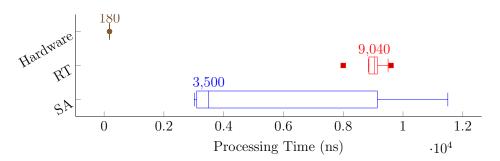

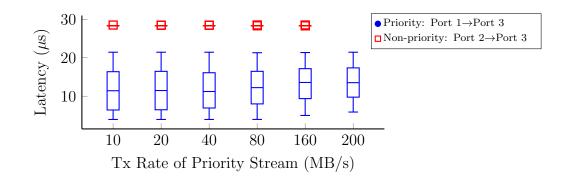

|            | Latency distribution for interrupt-based critical data processing    | 98       |

|            | Encapsulating additional information into existing messages as data- |          |

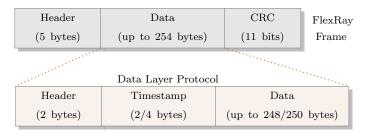

|            | layer headers.                                                       | 98       |

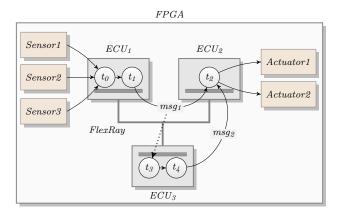

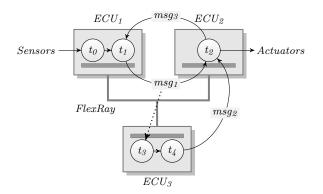

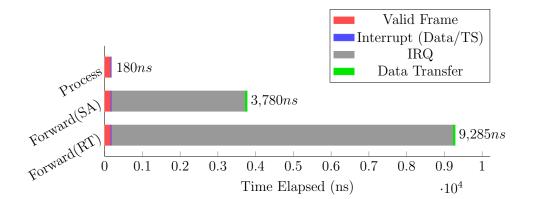

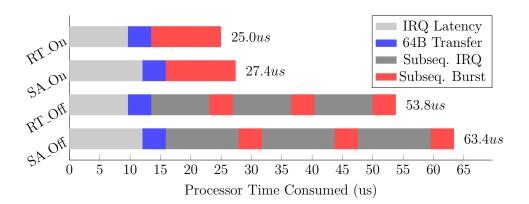

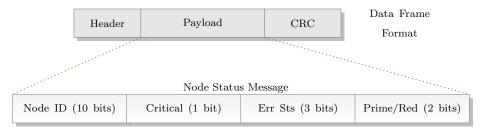

| 3.14       | Messages exchanged between the ECUs                                  | 99       |

| 3.15       | Timestamp processing at interface.                                   | 101      |

| 3.16       | Data re-packing for multi-cycle data transfers                       | 102      |

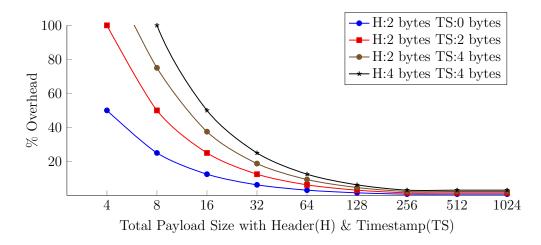

|            | Overheads for including headers and timestamps                       |          |

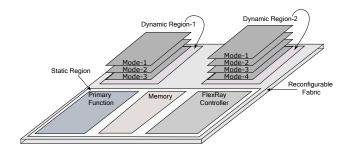

| 4.1        | Visualisation of adaptive ECUs on an FPGA using PR                   | 111      |

| 4.2  | Consolidating non-concurrent ECUs on FPGA                                                            |

|------|------------------------------------------------------------------------------------------------------|

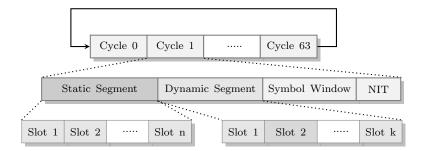

| 4.3  | Specification of the FlexRay cycle                                                                   |

| 4.4  | Dynamic segment payload with Message ID                                                              |

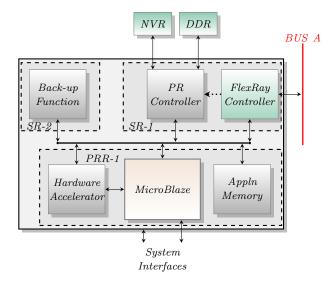

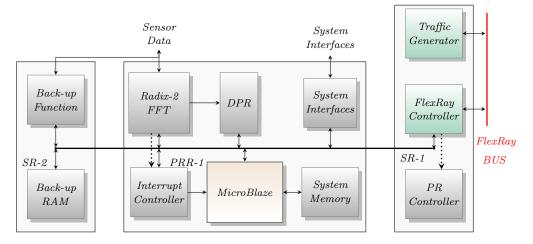

| 4.5  | Fail-safe ECU architecture on FPGA                                                                   |

| 4.6  | DMA based PR controller                                                                              |

| 4.7  | A Distributed redundancy scheme for non-critical ECUs                                                |

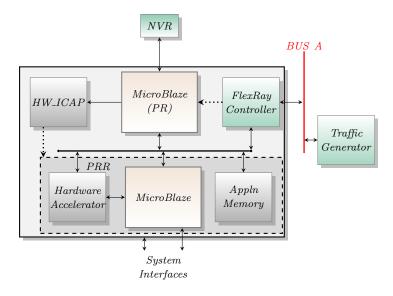

| 4.8  | Prototype for fail-safe Radar Signal Processing node                                                 |

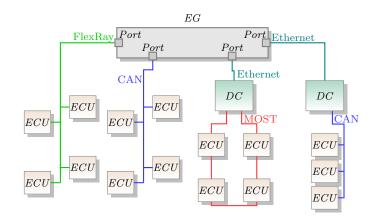

| 4.9  | Proposed vehicular network structure for Ethernet backbone networks $128$                            |

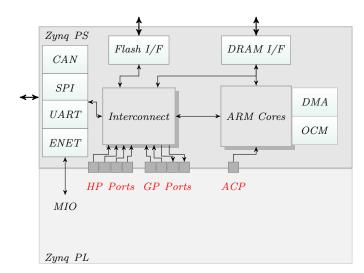

| 4.10 | Zynq Architecture showing the Processor Subsystem (PS) and Pro-<br>grammable Logic (PL)              |

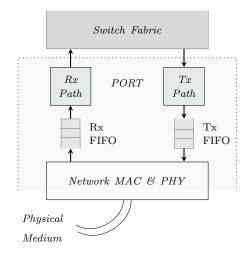

| / 11 | High-level block diagram of a Port                                                                   |

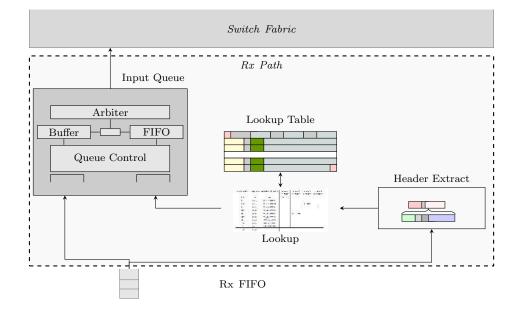

|      | Receive path of a Port with their functional sub-modules                                             |

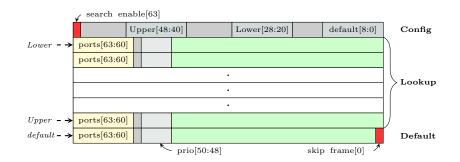

|      | Lookup table structure in the Receive Path                                                           |

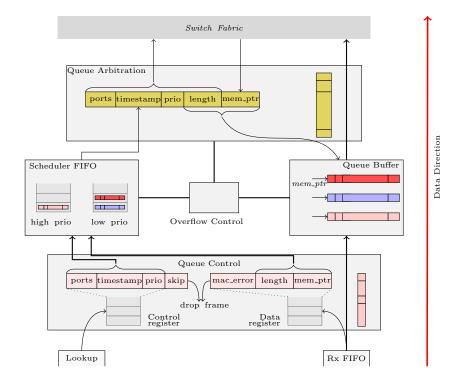

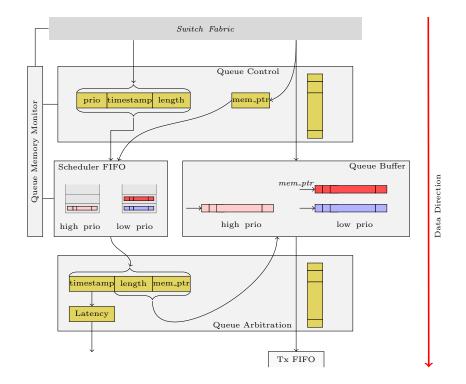

|      | Input queue block diagram                                                                            |

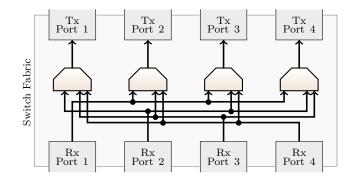

|      | Crossbar matrix implementation of the switch fabric                                                  |

|      | Block diagram of the output queue module and its sub-modules 137                                     |

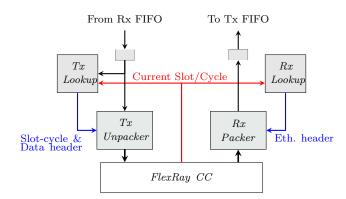

|      | Architecture of tblock and its integration with the FlexRay com-                                     |

|      | munication controller (CC)                                                                           |

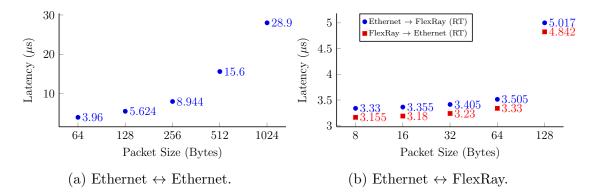

| 4.18 | Switching performance of AEG for different payload sizes 144                                         |

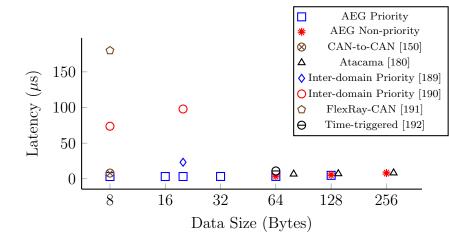

|      | Comparison of end-to-end latencies of our AEG with other imple-                                      |

|      | mentations from literature                                                                           |

| 4.20 | End-to-end latency measurements of our AEG in the presence of                                        |

|      | cross-traffic                                                                                        |

| 5.1  | Time-triggered Network enhanced with an Intermediate Timestamp                                       |

| 0.1  | and Data-ciphers                                                                                     |

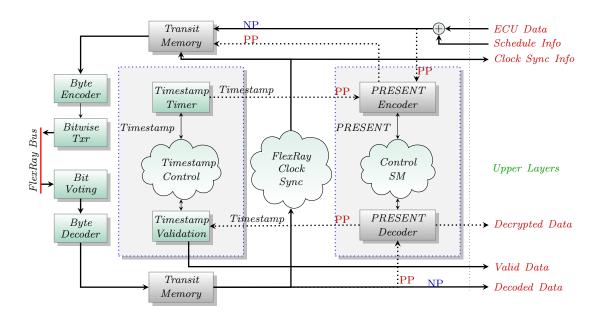

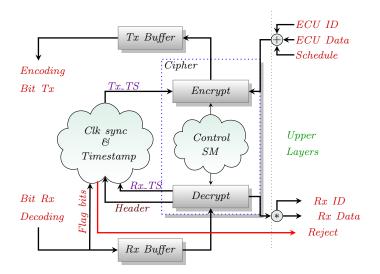

| 5.2  | Datapath Extensions: Timestamp synchronisation, Processing and                                       |

|      | Cipher logic. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $156$ |

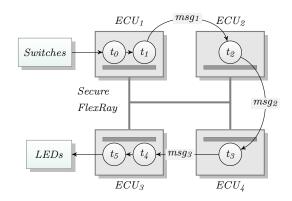

| 5.3  | Test setup with 4 ECUs on ML-605 development board                                                   |

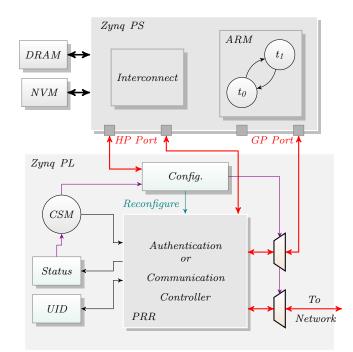

| 5.4  | High-level System Architecture on Xilinx Zynq                                                        |

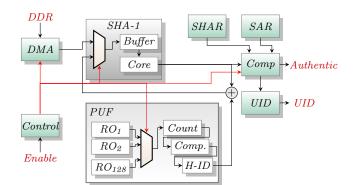

| 5.5  | The Hardware-Software Authentication logic                                                           |

| 5.6  | Enhanced Datapath at the Cipher logic for incorporating Header                                       |

|      | Obfuscation                                                                                          |

| 5.7  | Frame format of the Security Management Vector (SMV) 167                                             |

| 5.8  | Entropy of FlexRay frame with Obfuscation                                                            |

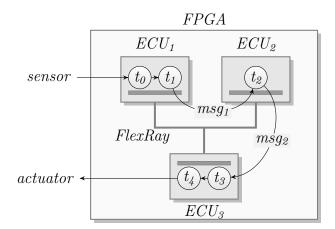

| 6.1  | Replicated test bed comprising 4 ECUs                                                                |

| 6.2  | Hardware-in-the-loop test setup                                                                      |

| 6.3  | System Architecture of the Validation Platform                                                       |

| 6.4  | Hardware Architecture of the Validation Platform                                                     |

| 6.5  | Example ECU architecture                                                                             |

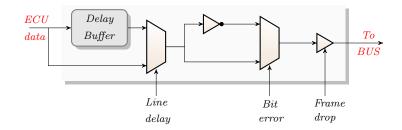

| 6.6  | Architecture of the Bus buffer module. $\ldots$ . $\ldots$ . $\ldots$                                |

| 6.7  | Python Software Flow                                                                                 |

| 6.8  | Evaluation of Case Study II                                                                          |

## List of Tables

| 1.1 | SAE in-vehicle network classification                                               |

|-----|-------------------------------------------------------------------------------------|

| 3.1 | Commands from Host that affect CC operating modes                                   |

| 3.2 | FlexRay node parameters                                                             |

| 3.3 | CC Implementation on hardware                                                       |

| 3.4 | Comparison of implementations                                                       |

| 3.5 | Spartan-6 implementation of ECU on Chip                                             |

| 3.6 | Software and hardware performance comparison                                        |

| 4.1 | Modes of Operation for Consolidated ECUs                                            |

| 4.2 | Virtex-6 Implementation of Adaptive Smart ECU                                       |

| 4.3 | Resource Utilisation of Radar ECU                                                   |

| 4.4 | FlexRay Parameters used for evaluating Radar ECU                                    |

| 4.5 | Turnaround time to the Redundant mode for different Fault-Tolerant<br>Architectures |

| 4.6 | Recovery time for the different Fault-Tolerant Architectures 126                    |

| 4.7 | AEG: Resource Consumption on Zynq XC7020                                            |

| 5.1 | Comparison of CC resources on XC6VLX240T                                            |

| 5.2 | Latency of operation per 64 bit data block                                          |

| 5.3 | Comparison of Resources on XC7Z020                                                  |

| 6.1 | Register file description of the Validation Platform                                |

| 6.2 | Software APIs for controlling/configuring the Platform                              |

| 6.3 | Resource utilisation on XC6VLX240T and XC7VX485T 190                                |

| 6.4 | Communication schedule for the Cluster                                              |

| 6.5 | Evaluation of Case Study I                                                          |

| 6.6 | Observations during acceleration tests                                              |

| 6.7 | Resources consumed by interfaces on ML605 board                                     |

## List of Abbreviations

| ABS     | Anti-lock Braking System                                            |

|---------|---------------------------------------------------------------------|

| ACC     | Adaptive Cruise Control                                             |

| AEG     | Automotive Ethernet Gateway                                         |

| API     | Application Programming Interface                                   |

| ASAM    | Association for Standardisation of Automation and Measuring Systems |

| ASIC    | Application Specific Integrated Circuit                             |

| AUTOSAR | AUTomotive Open Systems ARchitecture                                |

| AXI     | Advanced eXtensible Interface                                       |

| BD      | Bus Driver                                                          |

| BRAM    | Block Random Access Memory                                          |

| C2X     | Car to X                                                            |

| CAM     | Content Addressable Memory                                          |

| CAN     | Controller Area Network                                             |

| CAS     | Collision Avoidance Symbol                                          |

| CC      | Communication Controller                                            |

| CFAR    | Constant False Alarm Rate                                           |

| CPS     | Cyber-Physical System                                               |

| CRC     | Cyclic Redundancy Check                                             |

| DCM     | Digital Clock Manager                                               |

| DMA            | Direct Memory Access                   |

|----------------|----------------------------------------|

| DPR            | Dynamic Partial Reconfiguration        |

| DRAM           | Dynamic Random Access Memory           |

| DSP            | Digital Signal Processing              |

| ECU            | Electronic Control Unit                |

| FIBEX          | Field Bus Exchange Format              |

| FIFO           | First In First Out                     |

| $\mathbf{FF}$  | Flip-Flop                              |

| FFT            | Fast Fourier Transform                 |

| FPGA           | Field Programmable Gate Array          |

| FSM            | Finite State Machine                   |

| F-TDMA         | Flexible-Time Division Multiple Access |

| FTM            | Fault Tolerant Mechanisms              |

| HS-CAN         | High Speed Controller Area Networks    |

| ICAP           | Internal Configuration Access Port     |

| IVC            | In-Vehicle Communication               |

| JTAG           | Joint Test Architecture Group          |

| LIN            | Local Interconnect Network             |

| LS-CAN         | Low Speed Controller Area Networks     |

| $\mathbf{LUT}$ | Look-Up Table                          |

| MCAL           | Micro-controller Abstraction Layer     |

| MDM            | MicroBlaze Debugger Module             |

| MMCM           | Mixed Mode Clock Manager               |

| MOST           | Media Oriented Systems Transport       |

| MT             | Macro-Tick                             |

- NMV Network Management Vector

- **OBD** On Board Diagnostics

- **OFDM** Orthogonal Frequency Division Multiplex

- **OSEK** Open Systems and their Interfaces for the Electronics in Motor Vehicles

- PC Personal Computer

- PCIe Peripheral Component Interconnect Express

- PL Programmable Logic

- PLB Processor Local Bus

- PR Partial Reconfiguration

- **PRR** Partially Reconfigurable Region

- **PS** Processing System

- **RTE** Run-Time Environment

- SMV Security Management Vector

- SUP Start-Up Pattern

- **TTCAN** Time Triggered Controller Area Networks

- **TDMA** Time Division Multiple Access

- **TMR** Triple Modular Redundancy

- **TPMS** Tire Pressure Monitoring System

- **TTE** Time Triggered Ethernet

- WUDOP Wake-Up During Operation Pattern

- WUP Wake-Up Pattern

- **UART** Universal Asynchronous Receiver/Transmitter

- V2V Vehicle to Vehicle

- V2X Vehicle to X

# 1

## Introduction

Three decades ago, a car was a highly mechanical piece of equipment that incorporated an engine, drive mechanism, and wheels, with a battery, alternator system and some controls for the lights as the only electrical parts. The first computing device to be used in a vehicle was a tiny micro-controller for handling the timing of spark plugs, with a modest control function implemented in a few lines of code [1]. Improving electronics allowed this functionality to be extended to engine timing control, control of the fuel injection system, and diesel engine control, using more powerful micro-controllers which executed code that monitored a set of sensors and controlled a sequence of actuators. The extensive use of micro-controllers for engine related control or management resulted in these small computing devices being called engine control units or engine management units (EMU). The ability to control functionality through software was appealing and numerous vehicular applications exploited micro-controllers in safety-related systems like Anti-lock Braking Systems (ABS) and airbag control, as well as in comfort functions like window controls, radio/cassette players and others towards the late 1980s. While complex computation was typically not required, reliability became an important factor. When connectivity was required, these embedded units were wired up using point-to-point links.

A modern vehicle today, by comparison, incorporates much more complex computation and dedicated network-based connectivity to handle the complex exchange of information. A high-end vehicle today can execute over 20 million lines of code in real-time, over a distributed array of embedded processing units (called electronic compute units or ECUs), that together control and coordinate both critical and comfort functions [2]. The number of computing units in a vehicle has thus risen across all ranges of cars, with low-end vehicles incorporating 30 to 50 ECUs, while the top of the line models can incorporate over 100 ECUs. These are supported by multiple in-vehicle networking standards that have also evolved to accommodate the reliability and bandwidth requirements of these functions.

The complexity of applications on modern vehicles is significantly higher; many mechanical functions like hydraulic power steering and drive controls (like acceleration and braking) are being replaced by their electronic versions (called *x*-by-wire systems), which require hard real-time performance. On the other hand, advanced assistance systems makes use of a variety of sensors to present the driver with information about the vehicle and its surroundings, and may even be able to physically assist the driver (like automatic parking). These applications can also be adaptive to conditions, as in the case of adaptive terrain response systems, which can detect the road surface and adapt vehicle settings automatically, increasing their complexity. Such complex applications require major and minor adjustments in near real-time, based on intensive computations performed on data collected from a multitude of sensors. Software offers the benefits of flexibility, easier development cycle, and field upgradability but more advanced special purpose architectures and/or multi-core processor systems are needed to meet requirements. Even with these enhanced compute platforms, the scalability of systems is bounded by the limited parallelism on offer. Multi-core and application specific platforms can also consume higher power, degrading the energy efficiency of the system.

Another challenge is the integration model followed in vehicular embedded systems that treats each new function as a new ECU. This lack of consolidation depends on multiple factors, but is largely influenced by the capabilities of the computational platforms (or lack thereof). For these new functions to be consolidated onto existing ECUs, the architectures must provide support for isolating different applications to ensure that both of them can operate reliably and are not affected by the presence (or actuation) of other applications. On processor-based architectures, this level of isolation is a non-trivial problem since the processor hardware will be shared by the functions that are being executed on the compute core, resulting in contention that has to be explicitly handled, creating further complexity. This generally results in the use of the "new compute unit for each new function" integration model, along with its associated packaging and network connectivity complexity. It is estimated that a mid-sized vehicle incorporates over 6 km of interconnect cabling contributing over 70 kg to the weight, largely due to this integration model [3].

The increasing proliferation of mobile technology is also pushing newer features into vehicular systems like inter-vehicle communication and connected services. The vehicle-to-vehicle (V2V) communication concept enables vehicles to exchange information about themselves and surroundings, and aims to achieve better road systems in a co-operative manner. The increasing connectivity and automation in vehicles brings with it new challenges like security; a connected vehicle controlled by software provides huge opportunities for a hacker. Computational systems and networks in modern and future vehicles will have to integrate mechanisms to combat security threats at the application layer or at the platform level, further adding to their complexity.

For a mass production industry like automotive, application specific integrated circuits (ASICs) would provide the most cost effective solution. Applications that

demand large scale deployment across ranges of vehicles like ABS can benefit from the highly energy efficient, dedicated approach. However, their complete lack of flexibility to adapt to changing standards and requirements can prevent their widespread adoption in some vehicular systems. For example, automotive manufacturers like *Tesla Inc.* often provide software-based updates to the electronically controlled functions in their electric vehicles, aiming to improve performance and efficiency. Furthermore, the development cycle for software-based functionality is much smaller compared to the development flow of ASICs.

Reconfigurable computing platforms like Field Programmable Gate Arrays (FP-GAs) provide an alternative. The configurability of the platform allows designers to build customised circuits which provide many of the performance and energy benefits of ASICs, while retaining the flexibility of software systems. Beyond the obvious performance boost, such systems provide a powerful platform for implementing multiple functions on the same hardware with complete isolation, using hard partitioning, and partial or complete reconfiguration. This further improves cost benefits and power consumption, along with savings in other factors such as size and weight. Moreover, FPGAs enable systems to be built with guaranteed deterministic results. This is particularly important for safety-critical in-vehicle systems, where reliability is of paramount importance.

New generation hybrid reconfigurable platforms further extend the appeal by enabling tight integration of software based control flow with hardware processing, allowing both components to be upgraded after deployment, similar to existing software-based functionality while benefiting from higher performance, lower energy consumption and massive scalability. This would enable a single ECU-on-chip architecture possible, where the computational function is closely integrated with accelerators, sensor/actuator interfaces and network communication interfaces.

Despite these advantages, reconfigurable hardware is not widely used in ECUs. The main hurdle is the difficulty associated with designing and evaluating ECU architectures and the expertise required to design, manage and execute runtime reconfiguration. In the following sections, we discuss the general architecture of ECUs and in-vehicle networks in modern vehicles and the challenges in adopting new architectures for the in-vehicle infrastructure. This thesis contributes enhanced network architectures, compute systems, and security infrastructure for next generation vehicular computing systems on reconfigurable platforms. It proposes techniques to incorporate such features in a manner that is transparent to the application and develops mechanisms to automatically validate such features.

#### **1.1** Automotive ECUs and In-Vehicle Networks

Early vehicular electronics consisted of simple devices like 8-bit micro-controllers with simple I/O support to connect to sensors [4]. With the introduction of more demanding applications, more powerful 16 and 32-bit processors and domain specific controllers were used to provide improved computational capabilities. Special purpose hardware like Digital Signal Processors (DSPs) are used in modern vehicles to accelerate computations for signal processing applications. The primary advantage of using software-programmable processors is portability and independence from underlying hardware due to abstractions supported by high level languages. This trend was encouraged by standardisation of the requirements and capabilities of underlying operating systems, which enable application developers to design their product independent of the hardware target. These standards, OSEK [5] and its evolution AUTOSAR [6], are widely adhered to in the automotive industry, and determine a standardised platform for automotive applications.

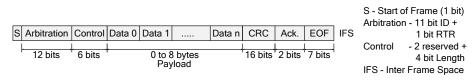

Early automotive systems used simple switches and actuators, and their functionality was achieved using point-to-point wiring. As more complex systems were introduced, point-to-point connections became infeasible due to the complexity of the wiring harness and the resulting additional weight and volume [7]. The early 1980s marked the introduction of vehicle networking as a step to reduce the wiring costs and complexity. Bosch introduced the Controller Area Network (CAN) in the mid-1980s, which gained widespread acceptance in the automotive industry and later became the most widely used networking backbone for in-vehicle systems. CAN provides flexibility to the user, since it can operated at multiple speeds and thus at varied costs. For instance, low-speed CAN can run at 125 kbps and can cater to all the user oriented electronics in a car, like power windows, electric seats and air conditioning, while high-speed CAN could run at up to 1 Mbps, serving real-time and safety-critical applications like engine management, ABS and others.

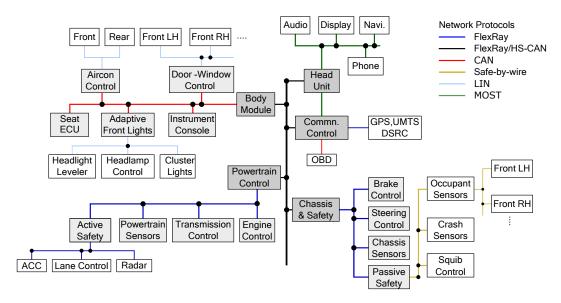

Depending on the performance and/or safety requirements, an application in a modern vehicle can be classified into one of the following domains:

- 1. The *Body Domain* incorporates user comfort features that are not safetycritical and have low quality of service (QoS) requirements.

- 2. The *Powertrain* handles engine management, power delivery and transmission and has hard real-time requirements.

- 3. The *Chassis Domain* includes systems which affect vehicle dynamics and controllability like steering, brakes, and suspension. These are safety-critical functions since they affect the behaviour of the vehicle and its response to user inputs.

- Telematics and In-Vehicle Infotainment (IVI) Systems integrate high speed multimedia, driver assistance systems, and the human-machine interface (HMI). This domain typically has relaxed real-time constraints.

- 5. Occupant Safety is primarily concerned with active protection systems for passenger safety and thus has strict real-time requirements.

Each domain requires different levels of service, such as response time, bandwidth, redundancy, and error detection, among others, often referred to as Quality of Service (QoS) levels [8]. These also feature different real-time and performance capabilities at the software level and the associated hardware level.

#### **ECU** Architectures

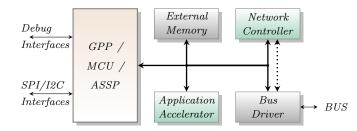

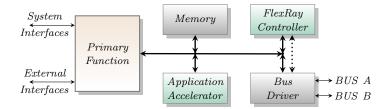

Typically, an ECU is composed of a processing element, a network interface and associated storage, as shown in Figure 1.1. The processing element may be an automotive grade micro-controller, general purpose processor or an application-specific

Figure 1.1: Typical ECU architecture.

controller. These execute the software tasks required for the ECU's functionality. The processing element usually integrates common peripherals like timers, I2C/SPI interfaces that may be utilised by the application code. Most applications are executed on top of a standard real-time capable operating system like  $\mu$ C-OS, QNX Automotive, or Windows Embedded (Automotive), which provide the required abstraction for the application tasks. Operating systems may also need to support the abstractions defined by OSEK or AUTOSAR (either on their own or using middleware), which use a set of libraries to provide a standardised interface to the application developer.

The placement constraints for many ECUs that requires their compute blocks and/or sensor/actuator units to be positioned in certain parts of the vehicle led to a distributed computing architecture. To support this distributed model, ECUs integrate automotive standard network interface(s), either as dedicated ASICs, or as co-processing logic integrated into the same die. Multiple network protocol implementations may also be integrated in the case of ECUs which require interfaces to different physical networks. ECUs that handle an extensive amount of data and computation may also incorporate dedicated accelerators (hardware) and memory systems like DRAM. Off-the-shelf components from automotive vendors also incorporate additional features like security extensions, hardware cryptographic blocks, or others.

Depending on the domain the ECU is intended for, vendors also provide customised architectures that are best suited for functionality in that domain. For example, a body domain controller might integrate different network protocols and offer little or no hardware acceleration support, while a telematics controller would integrate high speed interconnect and dedicated accelerator blocks for video processing or

| Class   | Throughput            | Domain                                            | Leading Protocol                   |

|---------|-----------------------|---------------------------------------------------|------------------------------------|

| Class A | below 10 kbps         | Body Domain: Low end                              | LIN                                |

| Class B | $10$ to $125\rm kbps$ | Body Domain: Non-critical<br>and non-diagnostic   | Single-wire CAN<br>(SWC) & CAN 2.0 |

| Class C | 125 kbps<br>to 1 Mbps | Powertrain: Real-time<br>critical parameters      | High speed<br>CAN (HSCAN)          |

|         |                       | Powertrain, Chassis:<br>Hard Real-time & Reliable | FlexRay                            |

| Class D | above 1 Mbps          | Occupant Safety:<br>Real-time & Reliable          | Safe-by-wire<br>& Byteflight       |

|         |                       | Streaming Media and<br>Entertainment              | MOST                               |

Table 1.1: SAE in-vehicle network classification.

radar interfaces. This "right-sizing" enables manufactures to control the cost (development and parts) as well as standardise the software framework for each domain.

#### **In-Vehicle Networks**

A variety of in-vehicle networks evolved, driven primarily by cost and performance requirements. CAN proved too expensive and complicated for simple functions like power windows or boot release. Simpler protocols like the Local Interconnect Network (LIN) could offer similar functionality at lower cost per module and power consumption, and thus found widespread adoption for non-critical functions. CAN also proved too slow for high bandwidth applications like multimedia in higher end vehicles resulting in the development of high bandwidth protocols like Media Oriented Systems Transport (MOST) for such applications. Time-triggered CAN (TTCAN) is an evolution of standard CAN, which addresses the lack of determinism by introducing a time-triggered mechanism above the CAN framework. The FlexRay protocol, developed by the FlexRay consortium, offers a combination of time-triggered and event-triggered communication for in-vehicle applications to enhance reliability with higher bandwidth. Time-triggered Ethernet, an extension of standard Ethernet, is also gaining traction as the backbone network for future vehicles. The Society for Automotive Engineers (SAE) classifies in-vehicle networks based on throughput and domain of operation [7, 8, 9], as shown in Table 1.1

As the number of communicating nodes in a network has increased, CAN has proven incapable of consistently providing deterministic data transfer rates, primarily due to its event-triggered architecture. Emerging safety-critical applications demand higher levels of determinism, which cannot be consistently ensured by event-triggered networks. Future functions like drive-by-wire and brake-by-wire will make time-triggered schemes the de-facto standard in critical domains. However, more widespread adoption of FlexRay or similar time-triggered architectures will be limited by the higher cost per node.

#### ECU Consolidation

The "new function as a new ECU" integration model allows integration into existing and proven in-vehicle infrastructure with minimal time and cost. However, this approach increases the weight and power consumed by electronic modules in the vehicle and reduces the communication bandwidth. For future electric vehicles, the powertrain, battery management, and control interfaces will be fully computerised, requiring more computational power. The total weight of the on-board computing systems and their power consumption become more critical considerations to maximise performance and range for electric vehicles.

Consolidating multiple functions onto fewer ECUs is important to counter this problem. Traditional approaches using processors running real-time operating systems do not allow for reliable isolated sharing since processor hardware resources are shared by the two (or more) functions. Even in the case of multi-core processor architectures shared caches or registers represent a point of contention. Determinism in such an environment would require more complex real-time support and explicit management in software.

#### **Enhanced Capabilities**

Currently, any enhancement to the communication network or computational system are enabled due to software flexibility. For instance, integrating security using upcoming standards like secure hardware extensions (SHE) requires the application to leverage enhancements to underlying libraries. This creates additional overheads in software execution to utilise these extensions and requires extensive data re-routing which must be handled in software. Furthermore, additional latency is incurred for each data/message, which must be factored into the task/message schedule and re-evaluated to ensure real-time deadlines are not violated. Abstracting such operational details and latencies from the application provides a better mechanism. However, this is not possible with off-the-shelf components and requires extensible, configurable datapath features to be integrated in the hardware architecture.

Evolving automotive systems are adaptive in nature, meaning such systems make intelligent choices to react to operating conditions. Systems like adaptive cruise control and driver assistance systems provide better performance than their corresponding static implementations [10]. On a conventional ECU architecture, adaptation is achieved through sophisticated software routines running on general purpose platforms. More advanced adaptive applications are more computationally complex, often requiring special purpose hardware support and accelerators. Likewise, security policies and algorithms need to adapted during the lifetime of an ECU, which can be 20 years. These trends suggest that flexible hardware will play a key part in next generation ECU architectures, offering benefits like accelerated computation, lower latency, security, and deterministic execution.

#### **FPGAs** for Automotive Applications

Reconfigurable hardware platforms like Field Programmable Gate Arrays (FP-GAs) offer an alternative for implementing such systems. FPGAs started as simple programmable chips for glue logic at the board level. Modern FPGAs from Xilinx and Altera are capable of implementing large and complex systems [11], and offer a wide range of built in hard macro blocks, such as processors, DSP blocks and block memories (RAMs). FPGAs can allow aggregation of multiple functions and execution in complete functional isolation. They also allow integration of network controllers and ECU functions (either as software running on embedded processors or as custom logic) in a compact footprint. Deterministic behaviour is also

easily factored into systems implemented on reconfigurable hardware. Techniques like dynamic or partial reconfiguration (PR) allow hardware-level adaptation to enable more adaptive next generation automotive applications. PR also provides alternative ways of handling redundancy for advanced safety-critical systems, as well as mechanisms to adapt only segments of the architecture (like cryptographic blocks), without requiring extensive redesign of the entire ECU architecture.

#### 1.2 Motivation

FPGAs are not widely used in the automotive industry partly because they are expensive and also because they require substantial hardware expertise. Exploiting the potential of reconfigurable hardware for automotive applications requires development of architectures which are compact and power-efficient. Validation and certification concerns have also held back adoption, as many of the methodologies applied to software systems do not map well to these architectures. Many vendors provide IP cores for automotive applications but these are mostly generic and platform agnostic, and hence often inefficient. Furthermore, advanced features like partial reconfiguration are rarely exploited. We believe that efficient compute architectures that conform to automotive standards (like AUTOSAR), can offer an abstracted view to the system designer, making reconfigurable hardware more appealing.

Hardware-level adaptation using dynamic reconfiguration currently requires management through low-level hardware access. This is contradictory to the AU-TOSAR implementations which require hardware details to be abstracted from application designers. The design process is also extremely complex with significant low-level architecture steps required. This makes integration and management of run-time hardware adaptation an expert feature, further reducing its attractiveness for automotive system and application designers. By providing a standard architecture that integrates run-time reconfigurability and abstracting its management, we believe that next generation ECU architectures can benefit from hardware-level adaptation that is integrated as a standard feature of the platform.

For enhancing the electrics/electronics (E/E) architectures for next generation vehicular computing systems, enhanced mechanisms are required at the communication/network layer for improving reliability and determinism with high performance and energy efficiency. While current research aims to achieve this through dedicated communication channels (bandwidth or slots) for communicating system status, this requires extensive rescheduling and revalidation of communication and computation each time a new feature is integrated. Such information must also be passed up to the software application layer for processing, which further increases latency. We believe that integrating intelligence into the network layer provides a better alternative, and would help to abstract such low level details from the application designer. This is especially true for applications like in-vehicle network security, which is closely tied to the network properties and can benefit from tight integration with the communication protocol. However, such extensions must be adaptable and configurable so that these can be updated in-field, as with ECU software updates, making reconfigurable hardware the ideal platform for such intelligent network systems. Our research aims to develop architectures for next generation time-triggered network systems that provide extended security and reliability features without affecting the determinism of the protocol, while abstracting such details from the (software) application layer.

Another challenge associated with architecture evaluation for future automotive E/E systems is the difficulty associated with validating the functionality of applications. Presently, a complex hardware-in-the-loop test setup that replicates the E/E architecture in a vehicle is recreated in a laboratory environment, on which the changes to architecture and/or functionality of ECUs are evaluated. A more scalable approach is to use a reconfigurable validation testbed platform that can be easily configured with the required architecture and evaluated in real-time, with bit-level precision.

In the past decade, research on next generation vehicular systems has mainly concentrated on application level enhancements: novel functionality and applicationlevel mechanisms for reliability and security. Most of this work presents approaches from the application designers' perspective, relying on standard ECU architectures and communication systems. Little research work has aimed at improving the underlying hardware architecture and/or evaluating enhancements to the network layer. Though many applications include the use of FPGAs for their performance benefits, they did not consider ECU architectures that exploit the full capabilities of FPGAs across the layers of the hierarchy. While we do acknowledge the hardware expertise required for efficient designs and effective use of reconfigurability, we believe that such details can be abstracted from the application designers and can be embedded within the architecture as a feature. The techniques we propose integrate these extensions at the lower layers of the architecture and the network, over which existing research and applications can be directly ported without any loss in performance or determinism. In this research, we concentrate on ECU systems that rely on FlexRay as the network interface, as time-triggered networks like FlexRay have been established as the architecture of choice for safety-critical applications for future vehicles. The proposed methods can be equally adapted to ECU systems that integrate emerging time-triggered standards like Automotive Ethernet. We validate our approaches on Xilinx devices because of their established dynamic reconfiguration flow, though the same can be ported to the emerging Altera devices and tool flow.

#### 1.3 Objectives

The main objectives of the research in this thesis are to:

1. Demonstrate how extended communication can be integrated into existing infrastructure without sacrificing reliability of the protocol and in a transparent manner.

- 2. Propose ECU architectures that provide advanced functionality like faulttolerance and consolidation, leveraging enhanced communication and abstracted from the application layer.

- 3. Develop techniques to integrate configurable security extensions into the architecture that provide network and application security.

- 4. Develop a real-time functional validation platform that enables hardware validation of ECU functionality with bit-level accuracy and real-time performance.

#### **1.4 Contributions**

The main contributions of this thesis are the architectures and techniques developed for enhancing E/E architectures and communication infrastructure for next generation vehicular systems. The architectures and techniques are designed in a transparent manner such that system designers can port existing automotive functions to the enhanced E/E architecture with minimal modification.

- 1. We have performed a comprehensive study of in-vehicle networks and architectures with a focus on time-triggered networks like FlexRay. We have also identified features which can be enhanced through extended communication on existing infrastructure.

- 2. An optimised FlexRay communication controller for reconfigurable architectures has been developed that has configurable extensions that integrate features like timestamps, message identifiers, and reordering logic. The optimised controller offers tight integration with the functional logic on the ECU, while the extensions abstract network-level operations from the application for better system performance and efficiency.

- 3. An efficient scheme for implementing functional consolidation for non-critical ECUs and hardware-level fault-tolerance for safety-critical ECUs on reconfigurable hardware has been developed. The scheme extends the FlexRay

protocol framework to support system state messages that are handled at the network layer. The network layer also manages the self-healing capability by integrating intelligence (and reconfiguration logic), abstracting such details from the application layer.

- 4. An efficient Gateway ECU architecture based on a hybrid FPGA platform has been developed that provides deterministic switching performance in a compact and energy efficient footprint. The gateway ECU is developed to support future vehicular systems that utilise Automotive Ethernet as the backbone network, respecting priorities imposed by automotive functions on certain messages while providing gigabit interconnect between different branches.

- 5. A scheme for integrating zero-latency message encryption is developed as a configurable extension to our enhanced FlexRay interface. This is further extended to provide a network access prevention scheme and cross-layer security for improved entropy of the ciphertext. This enhanced scheme also integrates tamper protection for the software application and hardware bit-stream, preventing compromised ECUs from accessing a secure network. The scheme is integrated transparently to the application, allowing standard FlexRay applications to be directly ported to the secure domain.

- 6. A super-real-time bit-precise hardware evaluation platform has been developed to functionally evaluate an ECU within its network cluster by recreating the cluster on a large FPGA chip. The platform provides numerous capabilities to inject common errors and faults into the system, while a real-time monitor enables the cluster behaviour and network communication to be observed on a standard PC. Furthermore, the entire platform can be automated using simple scripts for long duration and complex test cases. Finally, the entire platform can be accelerated without loss in precision, lowering the validation time.

#### 1.5 Thesis Organisation

The remainder of this thesis is organised as follows. Chapter 2 presents a detailed literature survey on the evolution of embedded systems and networks covering state of the art systems like CAN, FlexRay and Time-triggered Ethernet. We look at other aspects of in-vehicle communication like scheduling, reliability analysis, and extensions like switched FlexRay. We also look at the evolution of reconfigurable hardware, its applicability in ECUs and advanced techniques like PR in this chapter. Chapter 3 describes the implementation of our extensible FlexRay communication controller, the optimisations we have achieved for reconfigurable hardware and the datapath enhancements that allow extended communication using existing messages. The chapter also presents a comparison of our implementation against existing platform agnostic implementations, and the potential of the extensions. In Chapter 4, we describe the enhanced architecture for ECUs on reconfigurable hardware that integrates capabilities of consolidation and fault-tolerance. We also present an architecture for high-performance gateway ECUs for the proposed Ethernet-backbone in-vehicle infrastructure on hybrid reconfigurable platforms. Chapter 5 presents our scheme for integrating transparent network level security and comprehensive system-level security offering system and network level protection without incurring additional latency. Chapter 6 describes the functional validation platform and its extensions for improved observability. Finally, Chapter 7 concludes the work presented in this thesis and outlines future research directions.

#### **1.6** Publications

Most of the work presented in this thesis has been included in a number of published and submitted papers.

- S. Shreejith, K. Vipin, S. A. Fahmy, M. Lukasiewycz An Approach for Redundancy in FlexRay Networks Using FPGA Partial Reconfiguration, in Proceedings of the Design Automation and Test in Europe (DATE) Conference, Grenoble, France, March 2013, pp. 721-724 [12].

- S. Shreejith, S. A. Fahmy, M. Lukasiewycz Reconfigurable Computing in Next Generation Automotive Networks, IEEE Embedded Systems Letters, vol.5, no. 1, pp. 12-15, March 2013 [13].

- S. Shreejith, S. A. Fahmy, M. Lukasiewycz, Accelerating Validation of Time-Triggered Automotive Systems on FPGAs, in Proceedings of the International Conference on Field Programmable Technology (FPT), Kyoto, Japan, December 2013, pp. 4-11 [14].

- K. Vipin, S. Shreejith, D Gunasekera, S. A. Fahmy, N. Kapre, System-Level FPGA Device Driver with High-Level Synthesis Support, in Proceedings of the International Conference on Field Programmable Technology (FPT), Kyoto, Japan, December 2013, pp. 128-135 [15].

- S. Shreejith, S. A. Fahmy, Enhancing Communication On Automotive Networks Using Data Layer Extensions, in Proceedings of the International Conference on Field Programmable Technology (FPT), pp. 470–473, Dec. 2013 [16].

- S. Shreejith, S. A. Fahmy, Zero Latency Encryption with FPGAs for Secure Time-Triggered Automotive Networks, in Proceedings of the International Conference on Field Programmable Technology (FPT), Shanghai, China, December 2014, pp. 256-259 [17].

- S. Shreejith, S. A. Fahmy, Extensible FlexRay Communication Controller for FPGA-Based Automotive Systems, IEEE Transactions on Vehicular Technology, Vol. 64, No. 2, pp. 453–465, Feb. 2015 [18].

- S. Shreejith, S. A. Fahmy, Security Aware Network Controllers for Next Generation Automotive Embedded System, in Proceedings of the Design Automation Conference (DAC), San Francisco, USA, June 2015, 39:1–39:6 [19].

9. S. Shreejith, P. Mundhenk, A. Ettner, S. A. Fahmy, M. Lukasiewycz, S. Chakraborty AEG: An FPGA-based Gateway Architecture for Ethernet backbone In-vehicle Networks, IEEE Transactions on Very Large Scale Integration (VLSI) Systems (prepared for submission).

## 2

### Literature Survey

The introduction of electronics for vehicular computation began in the early 1980s with lightweight micro-controllers and point-to-point wired connections for control tasks like fuel injection control, anti-lock braking systems (ABS), and other control functions. The addition of more functions resulted in a large number of point-topoint links, which became complicated and difficult to manage. Moreover, the amount of wiring began contributing noticeably to the overall weight of the car. Network-based connectivity and advanced compute units progressively made their way into vehicles to offer new applications and improve cost, efficiency, and performance. In this chapter, we review the architecture of existing state-of-the-art vehicular networks like CAN, FlexRay and Time-triggered Ethernet (TTE) and proposed extensions for these networks. We review the evolution of ECU architectures and analyse the potential of FPGA-based computing infrastructure for in-vehicle systems. We also discuss evolution of FPGA architectures and advanced capabilities like partial reconfiguration offered on state-of-the-art FPGAs.

#### 2.1 In Vehicle Computing Systems

The first reported use of an electronic safety-critical control function in vehicles was in 1981. General Motors adopted micro-computer based engine control for their gasoline powered cars which greatly improved efficiency and performance [1]. With the introduction of laws regulating emission control, the use of electronic engine control was required to meet the legal requirements as well as to maintain acceptable efficiency and performance. The ease of implementation and the cost/efficiency benefits motivated manufacturers to adopt electronic control for engine management and this later spread to other domains.

Modern vehicles incorporate upwards of 30-50 ECUs across all segments. These ECUs employ automotive grade micro-controllers and/or general purpose processors which execute software implementations of control and comfort applications. The number of ECUs in vehicles has been rising at the rate of approximately  $1.45 \times$  a year, while the application software has been growing at a rate of 4.5 MB per year [20].

Embedded computing in modern vehicles is segmented into different domains mainly differentiated by the criticality of the function executed. In general, each ECU integrates a processing element (single or multi-core processor), memory subsystems (including volatile and non-volatile), optional dedicated accelerators like cryptographic or image processing engines, power supply elements, and the interfaces to the different sensors, actuators, and network. Specific combinations are chosen depending on requirements for each application. For example, in the body electronics domain that handles simple comfort functions like doors, access control, lighting systems, and climate control, an ECU architecture may be composed of an 8- to 32-bit micro-controller, non-volatile code memory, and network interfaces like CAN and LIN. Further, the ECU may have features like ultra-low power operation to enable it to be constantly active (as in the case of access control systems) [21, 22, 23]. However, in the driver information and multimedia domain, an ECU might integrate a GPS interface for navigation, a display driver interface(s), a 32-bit single or multi-core processor, and a video accelerator, along with an optical network interface like MOST, offering higher compute and communication performance at higher power consumption [24].

Most current generation compute units use CISC/RISC core(s) as the central processing element [21, 22, 23, 24]. These can be custom designed cores or flavours of generic 16/32-bit cores available from multiple vendors. Supporting peripherals interface to the processing element over standard interfaces like Advanced Micro-controller Bus Architecture (AMBA) Advanced eXtensible Interface (AXI) or similar high-speed on-chip interconnect. Commonly integrated peripherals include hardened network controllers (CAN, LIN, FlexRay or others), timers, clock generators, sensor interfaces (analog/digital), PWM modules, and others. The choice of peripherals is determined by the application domain and these are often integrated on the same die as the processing element.

Beyond the functional requirements of dependability and reliability, other factors like maintainability, safety and security are important [4]. Compute units are expected to offer a very high mean time between failures (MTBF), ease of fault diagnosis, and ease of maintenance. Also, since drivers are not trained like pilots to use the systems properly, the electronics must be capable of handling varying driver input patterns without degrading safety. Such complex requirements along with the rising computational requirements and economic constraints make the design of automotive embedded systems challenging.

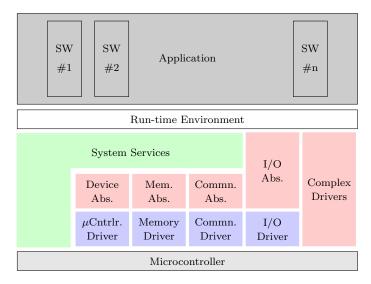

With features becoming more sophisticated and diverse manufacturers have had to address the the rising complexity in design, development, and management of these systems, giving rise to multiple standards: OSEK/VDX, AUTOSAR, and the ISO 26262. These define the way systems are developed, both at the hardware and software levels. The 'Open Systems and their Interfaces for the Electronics in

Figure 2.1: The abstraction layers in AUTOSAR.

Motor Vehicles' (OSEK) was founded by a consortium of German automotive companies to standardise the software architecture for different embedded platforms and promote software reuse. It includes specifications for the operating systems, interfaces to the underlying platform, communication, network management, and fault-tolerance mechanisms [5]. This was superseded by the Automotive Open Systems Architecture (AUTOSAR) specification, jointly developed by automotive manufacturers in 2003 [6]. The 'Road Vehicles – Functional Safety' standard (ISO 26262) describes standard procedures for fault detection, fault handling, and fault avoidance in automotive systems to prevent violation of system safety requirements [25, 26]. The entire ECU architecture and software development for automotive applications is governed by these standards.