## ENHANCING MANAGEABILITY OF EXECUTION AND DATA FOR GPGPU COMPUTING

A Thesis Presented to The Academic Faculty

by

Anshuman Goswami

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology May 2017

Copyright  $\bigodot$  2017 by Anshuman Goswami

# ENHANCING MANAGEABILITY OF EXECUTION AND DATA FOR GPGPU COMPUTING

Approved by:

Dr. Matthew Wolf, Committee Chair Computer Science and Mathematics Division Oak Ridge National Laboratory

Prof. Karsten Schwan, Advisor School of Computer Science Georgia Institute of Technology

Prof. Richard Vuduc School of Computational Science and Engineering Georgia Institute of Technology Prof. Hyesoon Kim School of Computer Science Georgia Institute of Technology

Prof. Ling Liu School of Computer Science Georgia Institute of Technology

Prof. Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology

Date Approved: December 9, 2016

To Susmita.

#### ACKNOWLEDGEMENTS

First of all, I would like to express my sincere gratitude and appreciation to my adviser Prof Karsten Schwan. His trust in me was the most important factor leading to the completion of this thesis. I sorely miss his presence today but will remember him always to be the perfect guide for me, as a student. Next, I would like to thank Dr Matthew Wolf, my co-adviser and committee chair, for his immense support in guiding me through the tumultuous phase after the passing away of Professor Schwan and help me reach the end of my PhD journey without giving up. His technical inputs as well as his genuine concern in the forward progress of my academic and professional career is something that I will remain ever indebted for. Besides, I want to thank Dr Jeffrey Young, Dr Greg Eisenhauer and Prof Ada Gavrilovska for their immensely useful feedback in shaping much of the research that has gone into this thesis.

Next, I would like to thank the members of my thesis committee, Prof Ling Liu, Prof Sudhakar Yalamanchili, Prof Richard Vuduc and Prof Hyesoon Kim, for sparing their valuable time and serve as the committee members. The constructive feedback and comments they have provided have gone a long way into refining the content of the thesis as well as stimulate future research directions worth pursuing. I must mention the support and guidance I have received from Prof Venkateswaran as the PhD program coordinator whom I could go to for advice under any situation. I should also mention that the contribution of this thesis has been significantly influenced by my experiences at three different internships for which I would like to thank my mentors, Dr Zhikui Wang and Dr Antonio Lain, at Hewlett Packard Labs; Jonathan Pearce at Intel; and Dr Inam Rahman at Apple.

During my time at Georgia Tech, I was fortunate to have made some very good friends who have become a part of my life. I would like to mention Chang-chih Chen, Pranith Kumar, Nagesh Lakshminarayana, Mohammad Hosaain, Dushmanta Mohapatra, Minsung Jang, Jai Dayal, Alexander Merritt and Dipanjan Sengupta among my past and present labmates who have made this journey so much more enojoyable. A special mention for my undergrad friends from JU, Ayan Paul and Sudipto Dolui, who have been the ever available support system that I could fall back on during every crisis. Any success would be as much a joy for them as it would be to me.

Finally, I would like to thank my wife for her constant support and unwavering patience through every high and low during my PhD. I have always admired her level of enthusiasm to see me succeed and this has been a key driving force for me to continue striving whatever the situation be. I would like to dedicate this thesis to her without whom I could not have come this far.

## TABLE OF CONTENTS

| DE  | DIC | ATIO            | Ν                                                       | iii           |

|-----|-----|-----------------|---------------------------------------------------------|---------------|

| AC  | KNC | OWLE            | DGEMENTS                                                | $\mathbf{iv}$ |

| LIS | T O | F TAE           | BLES                                                    | ix            |

| LIS | T O | F FIG           | URES                                                    | x             |

| SU  | MM  | ARY .           |                                                         | xiii          |

| Ι   | INT | RODU            | UCTION                                                  | 1             |

|     | 1.1 | Manag           | ging performance isolation                              | 1             |

|     | 1.2 | Enforc          | ing predictable sharing                                 | 2             |

|     | 1.3 | Superv          | vizing low-level scheduling                             | 3             |

|     | 1.4 | Enabli          | ing distributed computing                               | 3             |

|     | 1.5 | Thesis          | Statement                                               | 4             |

|     | 1.6 | Contri          | ibutions                                                | 4             |

|     | 1.7 | Disser          | tation Structure                                        | 6             |

| II  | REI | LATEI           | OWORK                                                   | 7             |

| III | LAN | NDRU            | SH : RETHINKING IN SITU ANALYSIS FOR GPGPU WOF          | ۲K-           |

|     | FLC | $\mathbf{WS}$ . |                                                         | 10            |

|     | 3.1 | Motiva          | ation                                                   | 12            |

|     |     | 3.1.1           | How Much of The GPU Is Left Unused?                     | 12            |

|     |     | 3.1.2           | Why Offload Analysis Computations to GPUs?              | 13            |

|     |     | 3.1.3           | What About Moving Data?                                 | 14            |

|     |     | 3.1.4           | How to Restrict Analysis Tasks' GPU Use to Idle Cycles? | 14            |

|     | 3.2 | Landr           | ush System Design and Implementation                    | 15            |

|     |     | 3.2.1           | Monitoring Usage                                        | 15            |

|     |     | 3.2.2           | Communicating opportunity triggers                      | 16            |

|     |     | 3.2.3           | Managing analysis' kernel launch calls                  | 18            |

|     |     | 3.2.4           | Multi-context kernel scheduling by the GPU driver       | 20            |

|     |     | 3.2.5           | Enforcing analysis kernels to fit inside gaps           | 21            |

|     | 3.3 | Evalua          | ation                                                   | 21            |

|    |     | 3.3.1  | Idle Period Analysis                                                       | 22        |

|----|-----|--------|----------------------------------------------------------------------------|-----------|

|    |     | 3.3.2  | Improvement in 'Time to Answer' with Gap-aware Co-location $$ .            | 27        |

|    |     | 3.3.3  | Discussion                                                                 | 33        |

|    | 3.4 | Chapt  | er Summary                                                                 | 34        |

| IV | GP  | USHA   | RE: FAIR-SHARING OF GPU CLOUD                                              | 35        |

|    | 4.1 | Backg  | round                                                                      | 37        |

|    |     | 4.1.1  | Programming Model, Host Application and Runtime                            | 37        |

|    |     | 4.1.2  | Driver                                                                     | 37        |

|    |     | 4.1.3  | Hardware Scheduling of Thread Blocks                                       | 38        |

|    | 4.2 | Motiv  | ation                                                                      | 38        |

|    | 4.3 | Design | 1                                                                          | 41        |

|    |     | 4.3.1  | Profiling                                                                  | 41        |

|    |     | 4.3.2  | Prediction                                                                 | 41        |

|    |     | 4.3.3  | Yielding                                                                   | 42        |

|    |     | 4.3.4  | Central Scheduling                                                         | 43        |

|    | 4.4 | Evalua | ation                                                                      | 43        |

|    |     | 4.4.1  | Metric to measure fair sharing                                             | 44        |

|    |     | 4.4.2  | Fair sharing between two tenants                                           | 45        |

|    |     | 4.4.3  | Overhead                                                                   | 46        |

|    |     | 4.4.4  | Scalability                                                                | 51        |

|    | 4.5 | Chapt  | er Summary                                                                 | 52        |

| V  |     |        | ONY : A SOFTWARE-SUPERVISED, MULTI-KERNEL SCHI<br>DR IN SITU GPU WORKFLOWS | ED-<br>53 |

|    | 5.1 | Motiv  | ation for GPU-resident Coscheduling of Analytics                           | 54        |

|    | 5.2 | Design | 1                                                                          | 57        |

|    |     | 5.2.1  | Warp-level vs Thread block-level abstraction                               | 58        |

|    |     | 5.2.2  | Hardware thread block scheduling - ignored or software supervised?         | 58        |

|    |     | 5.2.3  | Dynamic vs static resource allocation                                      | 59        |

|    |     | 5.2.4  | Additional offload APIs vs more compiler directives                        | 59        |

|    | 5.3 | Imple  | mentation                                                                  | 60        |

|    |     | 5.3.1  | Deployer                                                                   | 60        |

|    |             | 5.3.2  | Orchestrater                                  | 62      |

|----|-------------|--------|-----------------------------------------------|---------|

|    |             | 5.3.3  | Consolidater                                  | 63      |

|    |             | 5.3.4  | Limitations of the Symphony Approach          | 64      |

|    | 5.4         | Evalu  | ation                                         | 64      |

|    |             | 5.4.1  | Setup                                         | 65      |

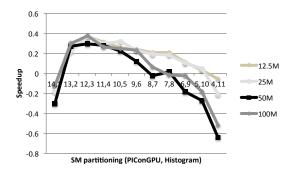

|    |             | 5.4.2  | Throughput                                    | 66      |

|    |             | 5.4.3  | Overhead                                      | 68      |

|    | 5.5         | Chapt  | ter Summary                                   | 72      |

| VI |             |        | LOW : SIMULATING THE DATA TRANSFER CHALLENGES | S<br>74 |

|    | 6.1         | Backg  | ground                                        | 76      |

|    |             | 6.1.1  | Motivation                                    | 80      |

|    | 6.2         | Simul  | ator Design                                   | 84      |

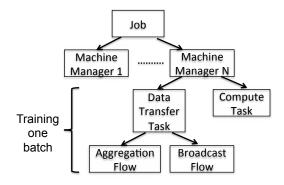

|    |             | 6.2.1  | Workload generation                           | 85      |

|    |             | 6.2.2  | Assignment of jobs to machines                | 87      |

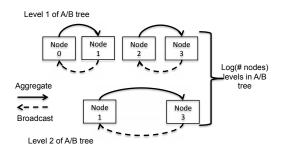

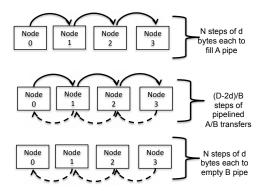

|    |             | 6.2.3  | Aggregation and broadcast scheme              | 89      |

|    |             | 6.2.4  | State machine to track job progress           | 90      |

|    |             | 6.2.5  | Scheduling Policies for bandwidth sharing     | 92      |

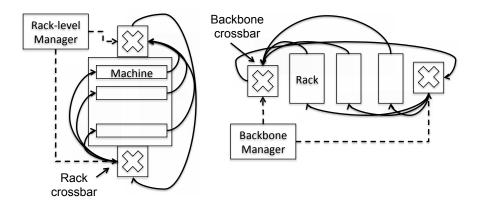

|    | 6.3         | Design | ning GPU coflow middleware                    | 94      |

|    |             | 6.3.1  | Multi tenancy vs. single job per machine      | 94      |

|    |             | 6.3.2  | Manager per job vs. manager per machine       | 95      |

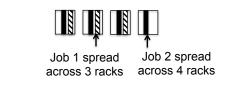

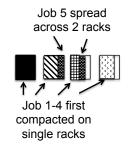

|    |             | 6.3.3  | Overlapping vs. spread out inter-rack traffic | 96      |

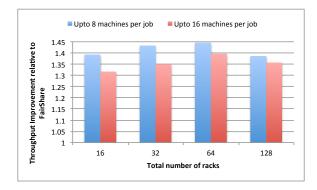

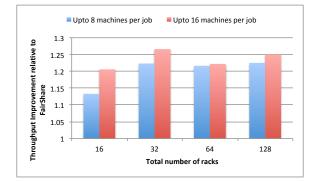

|    | 6.4         | Exper  | imental Evaluation                            | 96      |

|    | 6.5         | Chapt  | ter Summary                                   | 99      |

| VI | I CO<br>101 | NCLU   | SIONS, RECOMMENDATIONS AND FUTURE DIRECTION   | S       |

| RE | FER         | ENCE   | $\mathbf{S}$                                  | )5      |

| VI | ТА.         |        |                                               | 17      |

|    |             |        |                                               |         |

## LIST OF TABLES

| 1 | GPU Use in Representative Scientific Applications                              | 13 |

|---|--------------------------------------------------------------------------------|----|

| 2 | ANNs with high number of (>50M) weights to train $\ldots \ldots \ldots \ldots$ | 97 |

| 3 | ANNs with low number of (<50M) weights to train                                | 98 |

## LIST OF FIGURES

| 1  | Landrush Components and Gap-Aware Co-Location                                                  | 15 |

|----|------------------------------------------------------------------------------------------------|----|

| 2  | Actions on kernel launch call                                                                  | 17 |

| 3  | Actions on asynchronous memcpy calls                                                           | 17 |

| 4  | Actions on other asynchronous calls                                                            | 18 |

| 5  | Actions on synchronous calls                                                                   | 18 |

| 6  | Gaps in one time step of Lammps Lennard Jones Potential                                        | 22 |

| 7  | Lammps Lennard Jones Potential gaps across 64 nodes                                            | 22 |

| 8  | Gaps in one time step of GTC-P                                                                 | 23 |

| 9  | GTC-P gaps across 64 nodes                                                                     | 24 |

| 10 | Gaps in one time step of PIConGPU                                                              | 25 |

| 11 | PIConGPU gaps across 64 nodes                                                                  | 26 |

| 12 | Co-location Performance with Convolution : GTC-P                                               | 28 |

| 13 | Co-location Performance with Convolution : PIConGPU                                            | 28 |

| 14 | Co-location Performance with Convolution : LAMMPS                                              | 29 |

| 15 | Co-location Performance with Histogram : LAMMPS                                                | 30 |

| 16 | Co-location Performance with Histogram : PIConGPU                                              | 31 |

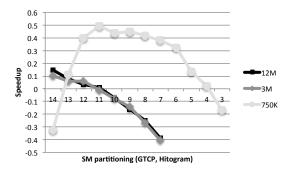

| 17 | Co-location Performance with Histogram : GTC-P                                                 | 31 |

| 18 | Co-location Performance with Scan : LAMMPS                                                     | 32 |

| 19 | Co-location Performance with Scan : PIConGPU                                                   | 32 |

| 20 | Co-location Performance with Scan : GTC-P                                                      | 33 |

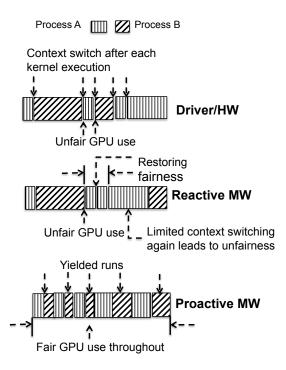

| 21 | Granularity of time slicing with GPUShare                                                      | 40 |

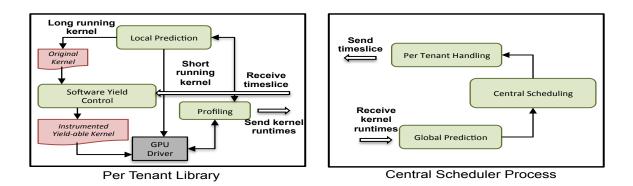

| 22 | Interworking of different components of GPUShare                                               | 41 |

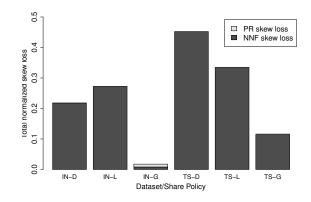

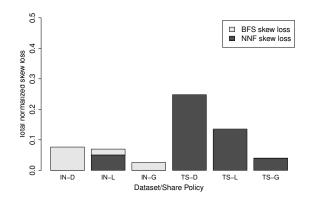

| 23 | NNForge and PageRank                                                                           | 46 |

| 24 | NNForge and BFS                                                                                | 47 |

| 25 | BFS and PageRank                                                                               | 47 |

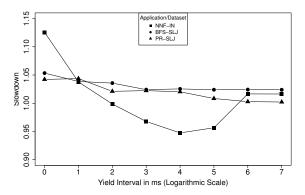

| 26 | Local Only Yield : Slowdown at different yield intervals                                       | 47 |

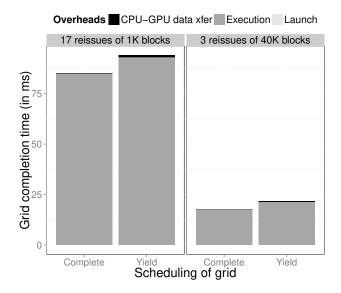

| 27 | Breakdown of yield overhead                                                                    | 48 |

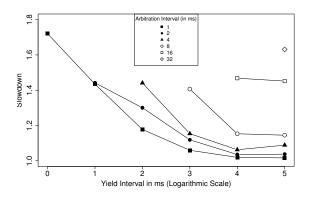

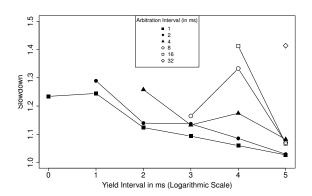

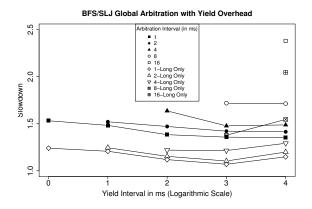

| 28 | Neural Net Training on Imagenet : Slowdown at different yield intervals and arbitration epochs | 49 |

| 29 | Pagerank on SocLiveJournal : Slowdown at different yield intervals and arbitration epochs                                                               |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30 | Breadth-first-search on SocLiveJournal : Slowdown at different yield intervals and arbitration epochs                                                   |

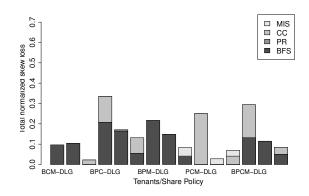

| 31 | More than two Tenants $(3 \text{ and } 4) \dots $ |

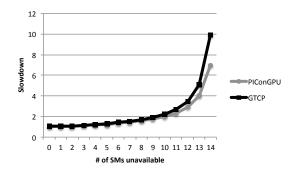

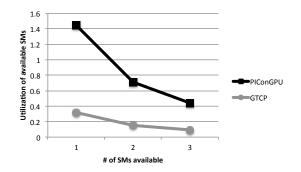

| 32 | Impact of available SMs on throughput of two well-known PIC codes                                                                                       |

| 33 | Utilization of available SMs for histogram analysis                                                                                                     |

| 34 | Processing cores and scheduling hardware in modern GPUs                                                                                                 |

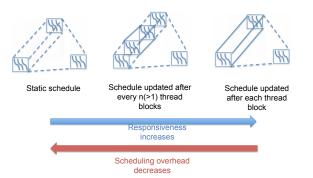

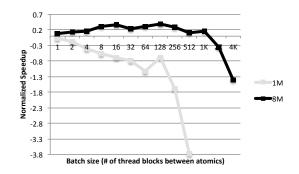

| 35 | Software-supervised thread block scheduling : Responsiveness vs Overhead                                                                                |

| 36 | SM scaled throughput of PIConGPU and Histogram workflow                                                                                                 |

| 37 | SM scaled throughput of GTC-P and Histogram workflow                                                                                                    |

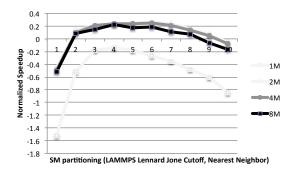

| 38 | Scaling throughput of LAMMPS Lennard Jones with Cutoff and Nearest Neighbor workflow                                                                    |

| 39 | Software scheduling overhead of PIConGPU                                                                                                                |

| 40 | Software scheduling overhead of GTC-P                                                                                                                   |

| 41 | Software scheduling overhead of LAMMPS                                                                                                                  |

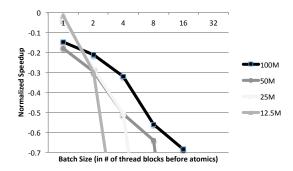

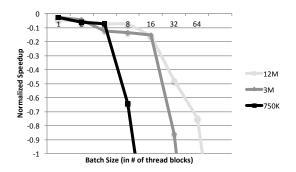

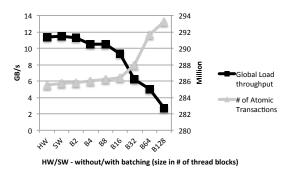

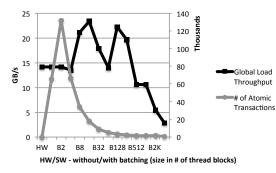

| 42 | Effect of batching on atomics and total overhead in GTC-P $\ . \ . \ . \ .$ .                                                                           |

| 43 | Effect of batching on atomics and total overhead in LAMMPS                                                                                              |

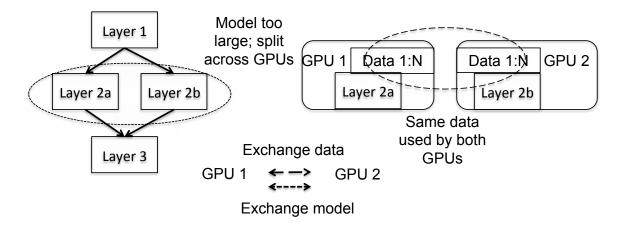

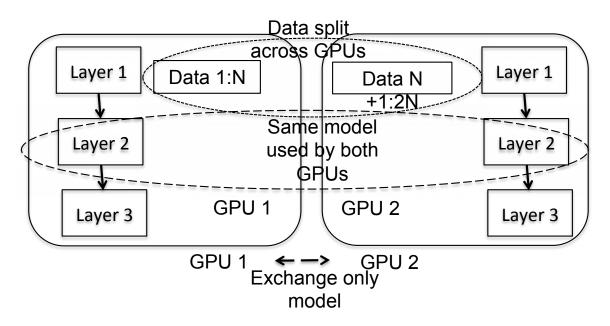

| 44 | Distributed ANN training : Model Parallelism                                                                                                            |

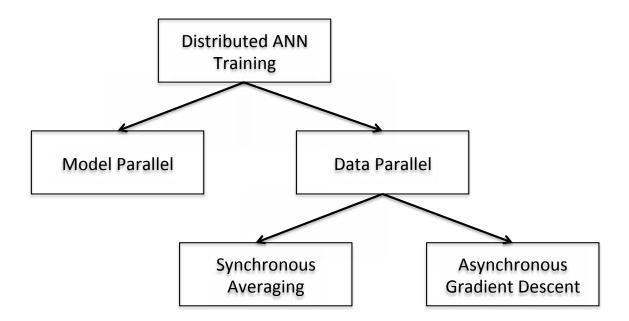

| 45 | Distributed ANN training : Data Parallelism                                                                                                             |

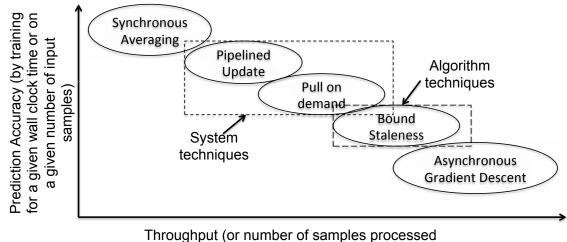

| 46 | Distributed ANN Nomenclature                                                                                                                            |

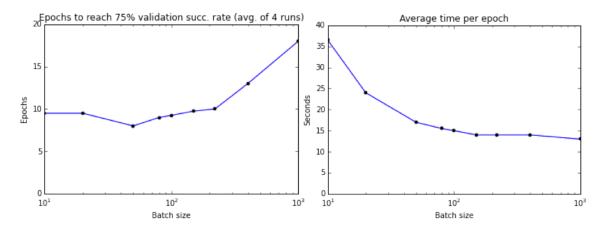

| 47 | Distributed ANN : Throughput v/s Accuracy $\hdots$                                                                                                      |

| 48 | Distributed ANN : Limits on Weak Scaling                                                                                                                |

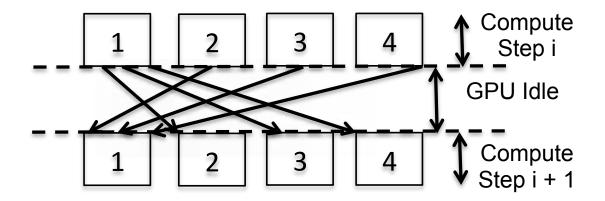

| 49 | GPU utilization : Without software pipelining                                                                                                           |

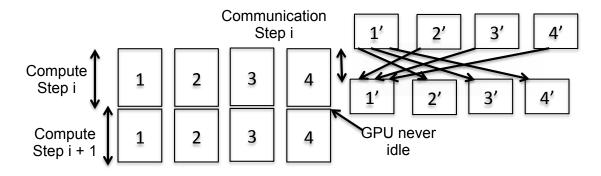

| 50 | GPU utilization : With software pipelining - GPUs never idle                                                                                            |

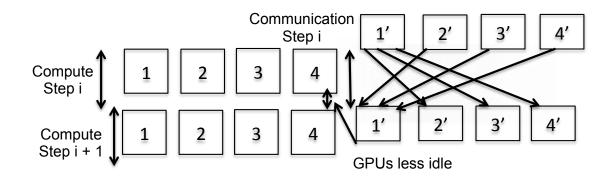

| 51 | GPU utilization : With software pipelining - GPUs idle for less time $\ . \ . \ .$                                                                      |

| 52 | Always spread across racks                                                                                                                              |

| 53 | First compacted then spread                                                                                                                             |

| 54 | Compacted or bounded spread                                                                                                                             |

| 55 | Aggregation and broadcast using a tree                                                                                                                  |

| 56 | Aggregation and broadcast using a pipeline                                                                                                              |

| 57 | Components of a job to process a single batch of training data                                                                                          |

| 58 | GPUCoflow controllers                                                     | 95 |

|----|---------------------------------------------------------------------------|----|

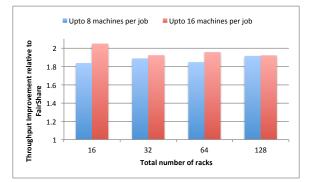

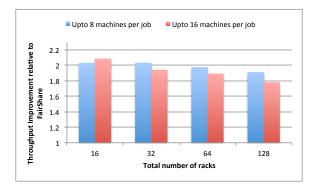

| 59 | LRBF throughput : Mix of ANNs with low and high number of weights $\ .$ . | 97 |

| 60 | LASF throughput : Mix of ANNs with only high number of weights $\ldots$   | 98 |

| 61 | LASF throughput : Mix of ANNs with low and high FLOPs to compute          | 99 |

| 62 | LASF throughput : Mix of ANNs with high and high FLOPs to compute .       | 99 |

|    |                                                                           |    |

### SUMMARY

With hardware accelerators like GPUs becoming increasingly common in high end scientific computing environment, new opportunities arise to co-locate scientific simulations and online analysis performed on the scientific data generated by the simulations. However, the offload-driven nature of scheduling of kernels on GPU and the limited context-switching capabilities on the GPU pose challenges to co-locating all the desired tasks.

Additionally, many new cloud-focused applications such as deep learning and graph analytics have started to rely on the high computing throughput of GPUs, but cloud providers cannot currently support fine-grained time-sharing on GPUs to enable multi-tenancy for these types of applications. Instead, scheduling is performed by the GPU driver in combination with a hardware thread dispatcher to maximize utilization. However, when multiple applications with contrasting kernel running times and high-utilization of the GPU need to be co-located, this approach unduly favors one or more of the applications at the expense of others.

This work brings together these two use cases to show how agile coscheduling of separate tasks can be achieved. Through a careful orchestration of compute, memory and network bandwidth resources, the techniques presented in this thesis demonstrate that it is possible to high performance and multi-tenancy in a number of usage and hardware scenarios.

#### CHAPTER I

#### INTRODUCTION

A decade ago[91], the Compute Unified Device Architecture (CUDA) API[89] was announced and Nvidia came out shortly after with compatible GPUs and software to support computing on GPUs. Abruptly, this shifted many assumptions about the relative bottlenecks between FLOPs and memory accesses. Other GPU vendors followed suit[63] by adapting their hardware and providing software to enable their GPUs for computing that extends much beyond the domain of graphics and media. Over these ten years, many classes of applications have been adopted to leverage the immense computing potential of GPUs. The HPC community, with a focus on scientific computation, were the early adopters of GPU computing. In recent times, enterprise computing has experienced a sudden burst of GPU use with the growth of computationally intensive analytics in today's era of the big data. Even so, there still exists some fundamental technical and macro-economic barriers in extending modern operating systems, which have evolved based on traditional CPU architectures, to manage GPUs. In particular, the persistent divide between regular schedulable cores and "device" management of GPUs poses issues for users and developers alike. Clearly, there exist opportunites for further pushing the envelope in terms of the performance perceived by the applications while enforcing superior resource utilization. This thesis introduces four different scenarios where there exist opportunities to push the state-of-the-art in GPU computing along with the associated challenges involved, which we detail in the following subsections.

#### 1.1 Managing performance isolation

Accelerators, particularly GPUs, have become the dominant computational engines of today's high-end machines, and this has been recognized and is being exploited by a wide variety of scientific applications, including adaptation of existing ones such as LAMMPS([111]) and GTC-P([137]) and evolution of new ones, such as, PIConGPU([22]). This changing landscape creates new possibilities for running in situ analysis using heterogeneous compute node resources like GPUs. Such in situ workflows are of significant interest as applications and middleware developers look towards exascale computing, as it offers a way to deal with the significant imbalance between compute capacity and I/O bandwidth by reducing and refactoring data before it exits the machine. Sharing GPUs between long-running scientific simulations and in situ analysis, however, must ensure performance isolation for the execution of the scientific simulations. For simulations that offload some or all of their computation tasks to GPUs, stealing idle GPU cycles presents a different set of challenges. For CPUs, when the co-running analysis task do not completely fit inside gaps, their rapid preemption immediately returns resources back to the simulation process([143]). But such is not the case for GPUs. This makes performance isolation much more challenging with GPUs restricting context switches to kernel boundaries.

#### 1.2 Enforcing predictable sharing

GPUs are being used for more data-rich applications in cloud computing environments than ever before ([81], [134]), and kernels in these applications have increasingly become longer in terms of running time due to larger and larger input datasets. However, in a cloud computing environment like Amazon's EC2[9], long-running kernels on GPUs can hinder scheduling flexibility and fairness for multiple-tenant scheduling. This lack of scheduling granularity and flexibility for discrete GPUs drives up the cost of using GPUs in a cloud computing environment due to limited multi-tenancy and subsequent skews in fair sharing. It also doesn't allow for fair usage of GPU resources that can currently be guaranteed for CPU-based virtualized systems.

All this points to the need for more fine-grained context-switching of GPU kernels that can be done in a manner that is both transparent to the user and improves fairness between multi-tenant kernels. A hybrid scheduling approach is called for which is software-based for managing long-running kernels delegating short-running kernels to the existing hardware scheduler for ensuring utilization remains high.

#### 1.3 Supervising low-level scheduling

HPC environments, where in situ analysis of data generated from scientific applications provide significant advantages, expose the limitations of the GPU hardware scheduler[10] that is responsible for the thread blocks of compute kernels running on the GPU. The GPU's native assignment policies for thread blocks in several scenarios are not suitable for the execution needs of all components in the overall worklow. As such, valuable scheduling opportunities may be lost. One approach would be to only allow analysis to be scheduled in the gaps of the main scientific application's use of the GPU. Being left only to using the gaps, light-weight, scalable data analysis tasks may not get the necessary amount of GPU cycles to make desired progress.

To address the above challenges, fine-grained and flexible scheduling control of execution on the GPU is necessary to effectively manage in situ analysis of scientific worklows on GPU supercomputers. Software supervized scheduling can combine the existing hardwarebased thread block scheduling mechanism with traditional software synchronization-based multi-core CPU scheduling techniques to balance between the conflicting needs of good performance for data-parallel GPU kernels and multi-tenancy on the GPU.

#### 1.4 Enabling distributed computing

Finally we address an emerging opportunity due to changes in hardware. Future supercomputers ([106], [75]) as well as data center clusters[87] with GPUs are likely going to have "dense" configurations where each node will have multiple GPUs with a fewer total number of nodes in the cluster. The majority of workloads for such systems would rely primarily on the GPUs for their computing needs. Examples of applications ready for this transition are ones like fully GPU-based plasma simulations[22] or neural network training for advanced analytics[88]. The on-node bandwidth available for data transfers between GPUs is already much higher with PCIe compared to the cross-node bandwidth from commodity Ethernet switches. For specialized networking hardware like Infiniband, the gap is less. However, the difference is set to widen with latest interconnect technologies like NVLink[95]. So, transferring data between nodes is likely to remain a very significant challenge to enable distributed GPU computing compared to data movement inside a node.

As such, the network bandwidth of dense GPU clusters is going to be the scarce resource that needs to be carefully managed to maximize the overall performance achieved as well as meet the individual needs of user applications. Traditional network scheduling algorithms from the software-defined networking community, like [6], are geared towards maximizing the bisection bandwidth obtained from the network. However, such an optimization objective may fail to consider the criticality of bandwidth allocation perceived from an application's standpoint. Taking inspiration from the coflow[25] scheduling paradigm proposed for CPU-centric distributed workloads like Spark[141] and Pregel[76], an equivalent approach is necessary to effectively schedule network traffic across co-running distributed applications that rely primarily on the GPU for their computing requirements.

#### 1.5 Thesis Statement

GPUs have become the primary computational engine in supercomputers ([105] and [104]) and datacenter machines ([87]) that house discrete GPU cards. Individual kernels of applications running on such systems are usually hand-tuned to extract maximum performance from the GPU hardware. However, there exists pressing need for mechanisms to co-run kernels from multiple applications on the GPU. On one hand, it enables in situ analysis of data generated from scientific simulations running on supercomputers. On the other, it reduces cost to run long tasks like neural network training on datacenter GPUs through fair-sharing. Moreover, distributed GPU computing over bandwidth-constrained clusters is going to define the next wave of GPU computing riding on machine learning. To address the above needs, this thesis proposes novel mechanisms to achieve effective multi-tenant scheduling of kernels on the GPU as well as application-aware network bandwidth sharing responsive to GPU use. The proposed mechanisms and policies provide flexibility to address different performance goals as well as meet the target levels of resource utilization.

#### 1.6 Contributions

The key contributions of the thesis are the testing and evaluation of set of mechanisms and policies to address the aforementioned gaps in performance and functionality of the state-of-the-art in management of GPUs. Specifically, we make the following contributions to validate our thesis.

- Landrush. We present a detailed analysis of GPU utilization of multiple state-of-theart science workflows to demonstrate the opportunities that exist for in situ analysis. We design and implement a low-overhead runtime for scavenging idle cycles on the GPU to run data analysis in situ with scientific simulations resulting in lower time to answer.

- **GPUShare.** We characterize the inability of the hardware scheduler in GPUs to achieve fair-sharing across co-running GPU intensive applications with long runnning kernels, a common scenario in the datacenter environment. We present the design trade-offs for such a system and provide an implementation of a low-overhead fair-share scheduling runtime for co-locating compute-intensive analytics jobs.

- Symphony. We investigate the scaling limits of individual kernels of well-known scientific workflows to show that top-of-the-line GPU hardware is often over-provisioned even for highly optimized HPC codes. To exploit such scaling bottlenecks for in situ analysis, we design and implement a CPU-like scheduling library to supervize the fully hardware thread block scheduling of GPUs. As a result, the combined throughput gets improved while incurring minimal overhead during standalone execution.

- **GPUCoflow.** We present a qualitative assessment of execution characteristics of deep learning workloads in a dense GPU computing environment, observing that the efficient sharing of bandwidth would be the most critical consideration to maximize overall throughput of clusters running such workloads. We build a simulator to study scheduling policies for interconnect bandwidth sharing in such an environment demonstrating that "coflow" aware scheduling policies perform much better than application-agnostic fair-sharing policies across different workload mixes. Finally, we present a detailed discussion on the design tradeoffs for implementing such a system.

#### 1.7 Dissertation Structure

The rest of the dissertation is organized as follows.

Chapter 2 presents the design and implementation of the Landrush system along with evaluation of the system to demonstrate its effectiveness in enabling in situ analysis on the GPU with reduced time to answer.

Chapter 3 presents the design and implementation of the GPUShare system to enfore fair-sharing among long-running analytics applications in a GPU cloud environment substantiated by evaluation results to prove improvements in fair sharing as well as the degree of slowdown due to overhead.

Chapter 4 presents the design and implementation of the Symphony system that exploits the scaling limitations of scientific codes on state-of-the-art GPU hardware to further stretch the possibilities for in situ analysis on the GPU. Accompanying evaluation is provided to validate the claim with reduced time to answer at reasonable overhead.

Chapter 5 presents the implementation of GPUCoflowSim, a simulator to study the scheduling policies for controlling network traffic, and use it study application-aware bandwidth sharing policies for distributed deep learning workloads that are effective in improving the overall throughput of the cluster compared to SDN-centric policies that focus on maximizing the bisection bandwidth through the network.

Chapter 6 discusses the wealth of existing research that has preceeded the contributions of the thesis to show how that has inspired the scientific enquiries into in situ analysis, multi tenancy and bandwidth sharing that this thesis has contributed.

Finally, chapter 7 concludes the thesis spelling out some of the future directions to continue research.

#### CHAPTER II

#### **RELATED WORK**

Previous work such as [40] has demonstrated that in situ analytics are important for large GPU clusters like Titan and can also provide important power savings. In addition, research that investigates causes of low GPU utilization([23], [5]) demonstrates that even well-tuned scientific codes leave resources idle. Past work on contention detection and response mechanisms to mitigate interference when applications share resources have focused on CPU and memory interference ([78], [77], [130] and [131]).

Lack of preemption support in GPUs today, makes it difficult to provide performance isolation guarantees. [116] explores preemption-based scheduling but is limited by the GPU programming model and the hardware, with preemption being only possible at kernel boundaries. Pai ei al.[108], building on mcuda[126], provide software-controlled elasticity in the physical resources consumed by a kernel enabling consolidation of kernels that alone do not fully utilize the available SMs on a GPU. Similar ideas were proposed by [19], [45] and [68]. Scientific and production-ready dataceneter applications are already well-tuned to fully utilize the GPU hardware are not likely to benefit from such mechanisms.

Concerning software stacks, the earliest entirely user-level solutions were gvim[46], vcuda[121], gvirtus[41], and rcuda[38]. More recent work([118], [110], [16], [113]) including vendorsupported libraries[97] have tried to exploit hardware improvements such as multiple hardware queues to improve utilization. All of these mechanisms rely on scheduling actions after kernels have already run limiting their effectiveness for long-running kernels. Other solutions, RGEM[60], timegraph[61], gdev[62], Basaran et al.[15], Menychtas et al.[82], Tian et al. [132] and gpuvm[127], replace the vendor-provided software stacks in order to promote GPUs to first-class schedulable entities in the OS and/or hypervisor, but unfortunately they also rely on reactive scheduling actions similar to other user-level middleware.

Hardware solutions[4] to support spatial multitasking on GPUs have been proposed.

Two preemption mechanisms, namely, *context switching* and *SM draining*, are proposed in Tanasic et al. [129]. *Context switching* can provide response-time guarantees, but has prohibitive overhead. *SM draining* does not dispatch new thread blocks and preempts only when the currently executing ones complete. Chimera [109] builds on the above by combining the low latency of *context switching* with the high utilization of *SM draining*, into a single mechanism called *SM flushing*. Assumptions are that kernels are idempotent and if not, they distinguish between global memory writes and overwrites. As hardware changes were proposed, evaluations were performed on simulators[13], making it difficult to gauge if real application kernels would benefit from such mechanisms.

PTask[114], Dandelion[115] and GEMTC[66] offer alternative programming models that give the OS sufficient visibility about an application's use of the GPU, thus permitting it to provide isolation and fairness guarantees. Moving existing GPU applications to such new models would require significant effort. Low-level GPU-side profiling tools are available now like SASSI ([125]) that enable high fidelity GPU code instrumentation. Some of the contributions in this thesis have explored profile-guided execution on the GPU.

The fundamental premise of many of the contributions of this thesis is based on the seminal work on realtime scheduling by Liu and Layland[74]. There has been a good deal of work focused on scheduling for a hybrid system of CPUs, GPUs, [73] and other accelerators [17] but little work on coscheduling applications within a set of GPU accelerators. Both AMD and NVIDIA support hardware virtualization and have projects to support varying levels of user scheduling, but most of this development is focused on improving the performance of graphics-intensive workloads. Previous work on CPU "core pinning" techniques [65] are also relevant.

The parameter server approach for distributed machine learning[71] has been shown to scale well across thousands of nodes with multi-core CPUs. But, artificial neural network training were not among the algorithms evaluated. Given that ANN training is characterized by higher FLOPs to bytes ratio, their performance sensitivity to the use of network resources needs careful consideration. Large-scale deep learning on thousands of machines[31] using the CPU cores have been shown to work. But there is growing evidence[87] that they can be matched by the processing power of merely tens of machines where each machine hosts multiple GPUs.

Recent work[28] has shown distributed deep learning using GPUs can achieve very good speedup. While speedup of individual training jobs are definitely important, overall throughput from a cluster shared by many such jobs is becoming critical as most of these jobs are going to run on shared infrastructure. Other work on intra-node bandwidth sharing over the PCIe[79] (or in future, NVLink) complement some of the contributions in this thesis.

Coflow scheduling([25],[26],[142]) has attracted a lot of research in the last few years due to growing prominence of several big data frameworks([32],[141],[76]) that could benefit from it. MPI has been the distributed programming model of choice for the scientific community and CUDA-aware[93] versions have been around for a while. Whatever be the communication API, coflow aware scheduling holds great promise for distributed GPU computing.

#### CHAPTER III

## LANDRUSH : RETHINKING IN SITU ANALYSIS FOR GPGPU WORKFLOWS

The evolution of high-end computing has allowed scientific simulations to run at higher and higher fidelity, which in turn generates massive amounts of data. This makes infeasible the traditional approach to I/O in which data is written to disk for subsequent post-hoc analysis. Running analysis where and when data is generated, often referred as "in situ" analytics', becomes a necessity rather than an option, particularly for the exascale era [37].

Previous work ([3], [2], [144], [143], [18], [133]) has demonstrated and explored a wide range of solutions for in situ data analysis, ranging from early work on "data staging" to recent work in which scientific simulation and analysis tasks efficiently time-share the CPU resources of compute nodes.

An issue not considered in such prior work is the rapid evolution of node architectures from previously homogeneous, CPU-only platforms to richly heterogeneous machines with accelerators and complex memory hierarchies. Accelerators, particularly GPUs, have become the dominant computational engines of today's high-end machines, and this has been recognized and is being exploited by a wide variety of scientific applications, including adaptation of existing ones such as LAMMPS [111] and GTC-P [137], [54] and evolution of new ones, such as, PIConGPU [22].

This changing landscape creates new possibilities for running in situ analysis using heterogeneous compute node resources like GPUs. Sharing GPUs between long-running scientific simulations and in situ analysis, however, must ensure performance isolation for the execution of the scientific simulations. [143] showed that CPU sharing on compute nodes can be done inobtrusively and effectively, by stealing cycles during the serial phases (MPI communication and I/O) of scientific simulations. However, for simulations that offload some or all of their computation tasks to GPUs, stealing idle GPU cycles presents a different set of challenges. Programming models for today's high-end discrete GPUs are specialized to utilize their high numbers of processing cores and to deal with the latency of offloading over the PCIe bus. Consequently, the task of identifying idle cycles on the GPU has to account for availability of both compute and data transfer resources. Even when such idle gaps are identified, the penalties for mis-predicting them is higher on GPUs than CPUs. This is because on CPUs, an analysis process may run during the idle gaps created by serial phases in the simulation process. If the co-running analysis task does not completely fit in the gap, its rapid preemption immediately returns resources back to the simulation process. In contrast, GPUs restrict context-switch to kernel (parallel programs running on GPUs) boundaries which is a far cry from the instruction-level precise interruption that system designers are used to in the CPU world, thus making performance isolation a much more challenging task( [116], [129]).

In this work, we seek to unlock the GPU resources present on high-end machines for use in running in situ analysis. The advantage of such resource sharing is multi-fold, including (i) the ability to operate on scientific data without moving it to staging nodes thereby reducing network traffic and energy cost, (ii) the accelerated execution of analysis tasks on energy-efficient hardware accelerators, and (iii) the efficient use of all resources present on compute nodes – CPUs and GPUs – to run scientific applications and associated analysis routines.

To this end, we have designed a runtime system, termed *Landrush*<sup>1</sup>, for enabling GPU sharing while also ensuring that GPU sharing does not unduly perturb a scientific simulation's execution. The Landrush solution makes the following technical contributions:

- We characterize the GPU activities for three different types of high-end scientific simulations, demonstrating the feasibility of task co-location using spare GPU cycles.

- We show a reduction in the total 'time-to-answer' seen by end users, by recognizing GPU idle gaps for executing analysis tasks.

- We study the effects of co-locating different complexities of analysis tasks with various

<sup>&</sup>lt;sup>1</sup>'Landrush' is the chaos that ensues from opening previously restricted territory to new uses.

scientific simulations, leading to a better understanding of the GPU sharing characteristics of (simulation, analysis) pairs.

The Landrush approach is evaluated with three state-of-the-art scientific simulation applications, LAMMPS, GTC-P, and PIConGPU, on the Titan [105] supercomputer hosted at Oak Ridge National Laboratory (ORNL). Experimental results demonstrate that up to 90% (!) of the GPU cycles are available over timesteps spanning 100-200 ms that can be used for analysis task co-location. Compared to naive co-location relying on scheduling by the GPU driver and the hardwired thread dispatcher, reductions in time-to-answer range from 8% to 33% across different combinations of co-location with nearly uniform performance from very small (4 nodes) up to very large scales (1024 nodes).

#### 3.1 Motivation

We seek opportunities for sharing the GPU resources on high-end machines between scientific applications and representative analysis applications that consume the generated scientific data.

This requires answering the following questions:

- 1. How much of the GPU is left unused by scientific applications?

- 2. Why offload analysis computations to GPUs?

- 3. What about moving data to/from the GPU?

- 4. How can we restrict analysis tasks' resource usage to idle cycles?

#### 3.1.1 How Much of The GPU Is Left Unused?

A survey of existing HPC applications [102] provides basic information about their use of GPUs. For applications not using the GPU (first row in Table 1), the GPU is idle for the entire duration of the scientific application. For applications using the GPU (second and third rows in Table 1), our analysis results in Section 3.3.1 show considerable variability of GPU idle cycles for a constant problem size of analysis tasks and at the strongest scaled point of simulation. The GPU is idle in LAMMPS (Lennard Jones potential) for 88% and

in GTC-P for 15%. Even an application like PIConGPU, which has been written to perform all of its computations on the GPU, exhibits idle gaps between GPU activities on a subset of the nodes running the application. These gaps result because it is difficult to eliminate all serial phases for applications using the GPUs and also because data movement between nodes cannot be fully overlapped with computation (due to complex transfers from the GPU to the host memory and then to the network device).

| GPU Use        | Applications                  |

|----------------|-------------------------------|

| Not used       | Tinker, Dirac, RedMD, GTS,    |

|                | Pixie3D and many legacy codes |

| Partially used | GROMACS, LAMMPS, NAMD,        |

|                | MILC, NWChem, ENZO, GTC-P,    |

|                | CP2K, Octopus                 |

| Fully used     | HOOMD-Blue, S3D, PIConGPU     |

Table 1: GPU Use in Representative Scientific Applications

#### 3.1.2 Why Offload Analysis Computations to GPUs?

Enabling in situ analysis requires harvesting resources whenever and wherever they are available. [143] exploits the benefit of co-running analysis when idle cycles on CPUs are available. With accelerators like GPUs becoming more prevalent on HPC machines and with end users demanding ever richer online analysis pipelines for processing scientific data, it is imperative to run them on the "fast" resources available on high end machines as opposed to simply delegating them to be run on CPUs. This is particularly the case for computationally intensive codes, i.e., those with small gaps on CPUs or GPUs, for which analysis computation tasks should be run wherever they run fastest.

As evidence, we reference the published performance reports for standard kernels [57], [96] that constitute common analysis tasks, running on CPUs vs. GPUs. Even when compared across state-of-the-art hardware (for both CPUs and GPUs), highly optimized (MKL and TBB for CPUs; cuFFT and Thrust for GPUs) versions of the same algorithms clearly perform best when run on the GPU with problem sizes that are similar to scientific output data. The speedups in computation time range from 2-5x for reduction, sorting and FFT in that order.

#### 3.1.3 What About Moving Data?

A known challenge with using powerful, discrete GPUs (over less powerful, integrated GPUs) is the need to transfer data from system memory to GPU memory over the PCIe link connecting them. Note that this is also a problem for running analysis tasks on idle CPU cores. Our study of high end scientific applications shows that the GPU's DMA engines are not heavily used by the scientific simulation: the percentage of DMA use in LAMMPS (Lennard Jones potential), GTC-P and PIConGPU constitutes only 1.4%, 4.5%, and 0.2% of their running times.

Moreover, programming support like CUDA's inter-process communication (IPC) has further reduced the cost of data movement between memories. IPC allows for sharing buffers between different GPU contexts, and Landrush uses this functionality to efficiently co-locate analysis applications that are node-local and to reduce intra-GPU memory transfers.

#### 3.1.4 How to Restrict Analysis Tasks' GPU Use to Idle Cycles?

Precise interrupts are not supported by the hardware for GPUs. It is difficult to store the context when interrupting more than a hundred concurrently running hardware threads of execution (orders of magnitude higher than the degree of hardware multi-threading in CPUs). Moreover, GPGPU kernels are written to mostly preserve a uniform control flow to make best use of the SIMD execution model. In most situations, there is little to gain from interrupting a GPU thread block (CUDA terminology for a group of threads that share a software managed cache with hardware synchronization) before completion.

However, GPU programming models expose a batching parameter for kernel launches that goes beyond the granularity of execution of a GPU thread block. An application may choose to launch several thread blocks when it makes a kernel launch call. For analysis kernels, it may be the case that the running time of a few (but not all) thread blocks fits inside gaps on the GPU.

In Landrush, analysis kernels are instrumented with an availability check at the start to allow early completion in case a kernel from the scientific application is launched while the analysis kernel is still running. So it is possible to emulate finer-grained software interruption capability despite lack of hardware support for context switch in GPUs.

#### 3.2 Landrush System Design and Implementation

To enable GPU sharing between co-located scientific simulation and analysis, Landrush functionality includes:

- monitoring GPU calls from the scientific simulation and kernel running times on the GPU for both the simulation and the analysis applications

- informing analysis-side Landrush about opportunities to use (or defer use of) the GPU

- managing kernel launch calls from analysis based on four availability heuristics

- scheduling simulation and analysis kernels using the GPU driver

- restricting analysis' use of compute cycles to within the gaps.

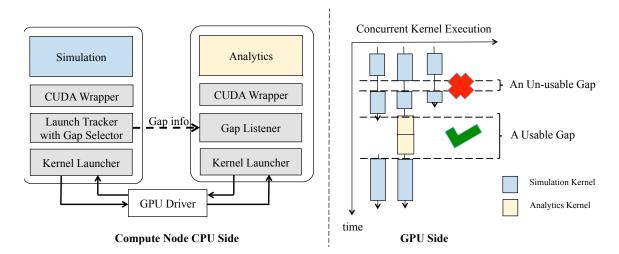

The overall architecture of Landrush is shown in Figure 1 which depicts how the above functionalities interact. They are described in more detail below.

Figure 1: Landrush Components and Gap-Aware Co-Location

#### 3.2.1 Monitoring Usage

Landrush is implemented as a library that resides within the address space of both the science and the analysis applications. It operates by intercepting either's GPU kernel launch calls via wrapper APIs. Kernel launch calls from both the scientific and the analysis applications are accounted and passed to the GPU driver. Analysis kernel launch calls are passed to the driver directly only if no science kernels are waiting to run, otherwise they are deferred.

To track the start and completion of every single kernel execution on the GPU as they occur, "events" exposed by GPU programming models have to be used. But to do this asynchronously, additional threads have to be run to poll for such events which adds a lot of overhead as the number of events increase. Therefore, Landrush relies on an asynchronous but repeated supply of kernel start and end timestamps by asking the GPU runtime to deliver the necessary profiling information[99].

GPGPU calls made by an application are detected by Landrush as they occur by using a wrapper around the runtime. Besides kernel launch calls, Landrush intercepts all data transfer, event and queue <sup>2</sup> related calls from the scientific application. Some of these calls are synchronous, while others are asynchronous. The profiling information sent from the scientific applications consist of (1) the timestamps of the above GPGPU calls, and (2) the GPU use and idle interval data alongwith the kernel(s) corresponding to each such interval. The GPU runtime delivers (2) asynchronously to Landrush which is then sent to the analysis-side component using a light-weight messaging library called nanomsg[85].

On the analysis side, Landrush only tracks GPU execution start and end intervals (but not idle intervals) alongwith the corresponding analysis kernels. It tries to ensure that the science application receive execution time on the GPU whenever it launches a kernel. It also runs an additional thread on the analysis-side to receive the profiling data which also acts as a listener for messages that indicate upcoming gaps on the GPU to run analysis kernels, described next.

#### 3.2.2 Communicating opportunity triggers

In order for the Landrush component on the analysis side to be aware of gaps on the GPU, there needs to be a constant supply of up-to-date GPGPU interactions made by the

$<sup>^{2}</sup>$ Queue (command queue or stream) is another type of logical object exposed by GPGPU programming models that can be used to increase concurrency of execution on the GPU.

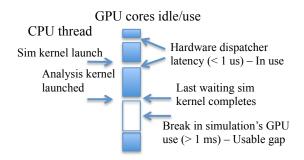

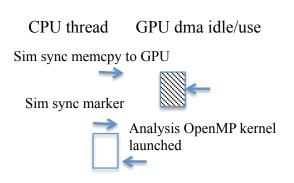

Figure 2: Actions on kernel launch call

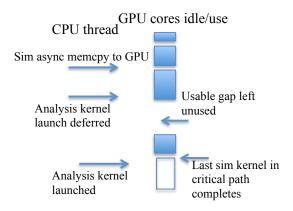

Figure 3: Actions on asynchronous memcpy calls

scientific application. Communication is triggered whenever a GPGPU interaction occurs and is deemed to convey new information. But, this consolidated profiling data is not current but from the recent past. Information about current usage of the GPU by the scientific application is necessary to decide on gaps.

When several simulation kernels are launched in quck succession (no idle time on GPU for a while), sending a message on each such launch can cause an unacceptable slowdown compared to standalone running time. To address this problem, a message is only sent when the last in a batch of kernels are launched or a subsequent data transfer is requested. Such message limiting is enforced by starting a timer (of 1 ms or the context switch interval on the GPU) after every message is send out and then waiting for the timer to expire before sending a new message consolidating all GPGPU interactions that occur during the interval.

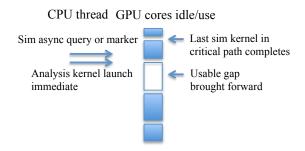

Figure 4: Actions on other asynchronous calls

Figure 5: Actions on synchronous calls

#### 3.2.3 Managing analysis' kernel launch calls

A kernel launch from the analysis application is intercepted by Landrush, and a decision algorithm is run to determine gap availability on the GPU. Even if a single gap is not large enough to fit the analysis kernel but the aggregate of multiple gaps are, the GPU is still used. Only if the aggregate of available gaps on the GPU fall short, the analysis kernel is run on the CPU. This is due to the much superior performance (at least faster by 2x) of the analysis kernels when run on the GPU compared to the CPU for the size of output data produced by the studied scientific simulations.

A gap on the GPU is detected if a period of no GPU activity exceeding 1 us is found as that is considered sufficiently larger than the maximum overhead to schedule the next kernel on the GPU if one was available. But, a gap is considered usable if it is estimated to be more than 1 ms, the context switch interval enforced by the GPU driver. On the CPU side, a gap is considered to be an interval of busy-wait or sleep of 100 ms or more, an order of magnitude more than the maximum scheduling latency of the OS. Gaps on CPU are only considered when the aggregate of usable gaps on the GPU is less than the analysis kernels' total running time as determined from the most recent profiling information.

The decision engine operates on the basis of three heuristics in determining gaps. If the last message is a kernel launch call, it looks up the most recent profiling data identifying the most recent occurrence of this kernel launch and the corresponding usable gap immediately succeeding it. A timer is started to wait for the interval until the next "usable" gap. If a previous record is unavailable, the analysis kernel is allowed to run right after the current kernel completes execution. Otherwise, the analysis kernel is allowed to run after the expiration of the timer as shown in Figure 2.

If the last message is an asynchronous query or GPU-side synchronization (event or queue) or an asynchronous memory copy (GPU to system memory), the decision engine interprets that as an indication that the kernels that need to complete as directed by the last interaction, cannot be deferred. It uses this information to check if the timer expiration could be brought forward by deferring kernels not indicated to be in the critical path. This allows analysis kernels to run before those simulation kernels, as shown in Figure 4. On the other hand, asynchronous memory copy message in the other direction (system to GPU memory) or between buffers on the GPU delays the timer expiration interval by adding the running times of all kernels which are potential consumers of this data movement, as shown in Figure 3.

If gaps on the GPU are not enough as determined from the most recent profiling data, a synchronized memory copy (system to GPU memory or between buffers on the GPU) is used to transfer simulation's output data from the GPU to the system memory. Thereafter, a busy-waiting GPU-side synchronization (on event or queue) is used to run analysis tasks on the CPU. This is shown in Figure 5. Note that this is more generalized than [143] which restricts CPU core use by in situ analysis to never use the core(s) used by the science application. In this case, as the CPU-side application thread is in a busy-waiting or sleep state, it is not necessary to measure interference caused by co-locating an analysis thread on the same core. Synchronous memory copy messages (GPU to system memory), currently unused, presents opportunities to transfer analyzed data back to the GPU memory if a multi-stage analysis workflow is used.

#### 3.2.4 Multi-context kernel scheduling by the GPU driver

Two different GPU contexts cannot time/space share the GPU. This prevents even low footprint analysis kernels from executing on the GPU concurrently with other low footprint kernels from the scientific simulations. By running microbenchmark kernels busy-wait on the GPU for variable intervals of time, we deconstructed the behavior of the driver when trying to simultaneously run kernels from more than one context (in our case, the scientific and the analysis applications).

One of two things happen when an analysis kernel is launched and the GPU is idle. (1) If no other kernel launched by the scientific simulation is in the queue, the analysis kernel can utilize the GPU before the next simulation kernel is launched. If the analysis kernel completes inside the gap, then co-locating analysis works out to be better than running serially. (2) If there are simulation kernels waiting to run, the driver schedules the kernels on the GPU in a round-robin manner with a context-switch interval of 1 ms or when an executing kernel completes. Multiple kernels from a context gets to run until their cumulative running time exceeds 1 ms, at which point, kernels from another context, if waiting, gets to run. If there are no other kernels waiting from other contexts, the same context can keep using the GPU because of the driver's work-conserving scheduling policy.

The above policy breaks down when execution times are near tens or hundreds of milliseconds (which is the case for problem sizes corresponding to the generated scientific output data). The effective context switch interval is reduced to a long running kernel's execution time and explicit scheduling of analysis kernels (not relying completely on the GPU driver) is needed.

In Landrush, analysis kernels are scheduled inside gaps when kernels from the scientific applications are not using the GPU. At any given time, it is ensured that analysis kernels are passed to the GPU driver only when there are no "kernels in the critical path" from the scientific application already waiting to run.

#### 3.2.5 Enforcing analysis kernels to fit inside gaps

In Landrush, analysis kernels are instrumented to insert an availability flag check that runs at the start of each thread block and determines if the GPU is still available to use. Any thread block only runs to completion, if the GPU is still available. The availability flag is stored in the GPU memory and is updated by the gap availability decision engine. Once one or more thread blocks detect the GPU to be unavailable, the remaining thread blocks return early using mechanisms described in [68]. Since the thread block dispatch is done in hardware, the overhead is negligible even for very large number of thread blocks. The same analysis kernel is next resumed to execute from the first thread block that was skipped in the last launch and allowed to run until the availability check fails, with each "round" completing more of the analysis kernel's overall grid of thread blocks, until it is complete. On the CPU, analysis kernels are run during gaps created by the busy-waiting episodes of the scientific application, and POSIX signals (from the OS) are used to interrupt execution beyond the gaps and revoke resource from the analysis tasks.

#### 3.3 Evaluation

All experimental evaluations are performed on the Titan supercomputer at ORNL. Titan consists of 18,688 compute nodes. Each compute node contains a 16-core 2.2GHz AMD Opteron 6274 processor and 32GB of RAM. Two nodes share a Gemini high-speed interconnect router. The resulting partition contains 299,008 traditional processor cores, and 587TB of memory. Each compute node is also equipped with an NVIDIA Kepler K20 GPU accelerator [92] with 6GB of DDR5 memory. Experiments broadly evaluate two questions:

- 1. What idle time is available on the GPU for each of the science codes (LAMMPS, PIConGPU, GTC-P), usable for co-running analysis?

- 2. To what degree does co-running some given analysis with a scientific simulation on the GPU lead to reduction in the total time to answer seen by the end user?

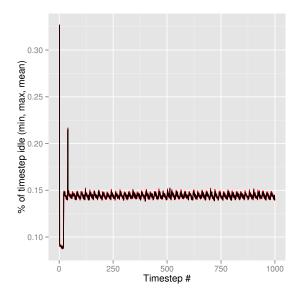

Figure 6: Gaps in one time step of Lammps Lennard Jones Potential

Figure 7: Lammps Lennard Jones Potential gaps across 64 nodes

#### 3.3.1 Idle Period Analysis

Extensive characterizations of the GPU usage of LAMMPS, GTC-P, and PIConGPU demonstrate substantial variability in the extent to which they use the GPU for offloading parallel execution phases, both in terms of occupancy on the GPU and the regularity in their usage patterns.

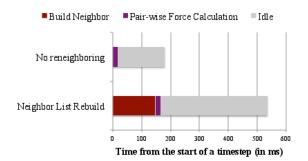

#### 3.3.1.1 LAMMPS

LAMMPS (or Large-scale Atomic/Molecular Massively Parallel Simulator) is a well-known molecular dynamics simulation with both OpenMP based CPU and CUDA based GPU acceleration. The version of LAMMPS run in our experiments is configured to perform

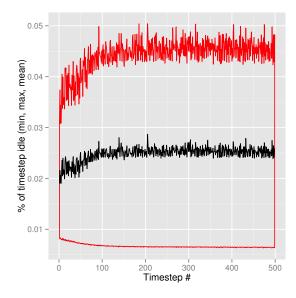

Figure 8: Gaps in one time step of GTC-P

Lennard Jones Potential calculation using GPU acceleration with the core GPU package of LAMMPS (other user contributed GPU packages are available but they are not officially supported by LAMMPS). The input data size used is 2.1 million atoms per GPU requiring 3 gigabytes of memory on a K20 on Titan with a memory capacity of 6 GB. The run configuration consists of 500 steps of dynamics with the velocity-Verlet integrator across 64 nodes (one GPU per node).

Two kernels run on the GPU when LAMMPS is configured with the above parameters: one performs the pair-wise force computations, in each time step, while the other re-calculates neighbors to be used for the force computations, once every twenty steps. For the given input size, the force computation kernel runs for around 17 ms. For 86% of the running time when neighbor calculation is not being performed, the GPU activity constitutes 9% of the average length of a time step. The remaining 14% of the running time are constituted by longer time steps due to the neighbor calculation taking around 146 ms. But even during these steps, the GPU use is only around 33%. This is shown in Figure 6. This is due to fact that the force field computations for Lennard Jones are performed on the CPU. The GPU is idle for nearly 88% of the application's running time. Also, the idle periods appearing in a time step remain nearly constant over the course of the simulation as does their distribution across nodes, shown in Figure 7. To summarize, LAMMPS configured to run Lennard Jones Potential using the GPU, exhibits a low but regular GPU usage.

Figure 9: GTC-P gaps across 64 nodes

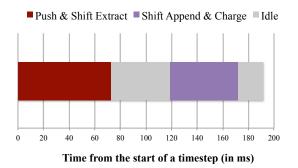

## 3.3.1.2 GTC-P

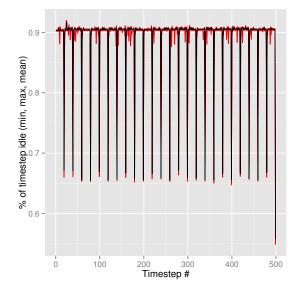

GTC-P (or Gyrokinetic Toroidal Code - Princeton) is a physics simulation evolved from GTC that uses the GPU. It is a solver for the gyrokinetic equation employing a 2-D domain decomposition in the radial and toroidal dimensions respectively. We use a constant toroidal dimension of 4 and vary the radial dimension to achieve weak scaling. The input data size is 12.9 million particles per GPU, resulting in a GPU memory footprint of 2.7 GB which is the highest problem size that can be fit on the K20 GPUs on Titan. GTC-P is run for 500 steps across 64 nodes with each step consisting of 2 sub steps, one for each stage of the Runge-Kutta algorithm that advances simulation time.

There are four main GPU operations that constitute the bulk of GTC-P's GPU usage, viz., push, shift(both toroidal and radial directions) and charge. Some other operations like smoothing, field and poisson calculations are performed on the CPU using OpenMP for parallel phases. As shown in Figure 8, this creates a window of 115 ms, for the above input size, during which the the GPU is left unused by the science application which accounts for nearly 15% of a time step. Moreover, these gaps repeat in every time step and are observed on all nodes running the simulation. This is shown in Figure 9. Thus, GTC-P exhibits high use of the GPU with regularly occurring windows of idleness in each timestep.

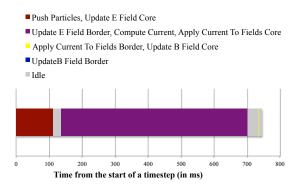

Figure 10: Gaps in one time step of PIConGPU

#### 3.3.1.3 PIConGPU

PIConGPU (or particle-in-cell on GPU) is another physics simulation implementing the PIC (particle-in-cell) method that computes the fully relativistic motion of electrons and ions in the presence of electric and magnetic fields governed by Maxwell's Equations. We configure PIConGPU to simulate a Kelvin-Helmholtz Instability (KHI), where the particles are placed in grids using 44.2 million particles per GPU, requiring a minimum of 2 GB of memory on the GPU. PIConGPU uses a GPU-resident memory allocator, called mallocMC, that pre-allocates most of the available GPU memory and then services runtime allocation requests from GPU kernels. PIConGPU is run for 500 time steps across 64 nodes.

There are four main phases in a time step (shown in Figure 10), each of which run several kernels on the GPU. In the first phase, particles (ions and electrons) are pushed based on the current field, lasting for 15% of the length of a time step. Fields at the border of a grid depend on neighboring grids located on other nodes. So, field towards the center of the grid are updated while waiting for data from other nodes to arrive. The delay in arrival of data from other nodes shows up as the first idle window, idle 1. The current computation phase, is the longest, constituting around 75% of the time step; it is also the busiest with practically no gap on the GPU. The computed current is applied to the fields during the third phase. Similar to the update of fields after particles are pushed to new positions, this phase also involves updating the field based on the newly computed current values. Like before, this also involves waiting for data from other nodes, resulting in, idle

Figure 11: PIConGPU gaps across 64 nodes

2 (nearly 4% in the time step), shown. The first gap, idle 1, only appear when the overlap between push particles and field update does not hide all data dependencies. The second gap, idle2, occurs when the computed currents have been used to update the field towards the center but fields from borders of neighboring grids have not been received yet. As the field data is much less than the particle data, sufficient computation task is not available to hide the communication latency and results in the only usable gap during a time step of PIConGPU.

As shown in Figure 11, there is some variation in the length of this idle period across 64 nodes but the maximum idle period for any node is under 5% of a time step. Landrush in its current form is a local scheduling entity. It would be intersting to look at the utility of multi-node management frameworks [30] in aggregating such idle information and scheduling varying amounts of insitu work based on a node's load, if the data movement cost can be compensated. To sum up, PIConGPU is characterized by very high GPU usage, affording only modest co-location for 0(N) analysis (like scan, minmax, mean etc) on the GPU with the CPU serving as the main available resource for performing more compute-intensive insitu analysis.

#### 3.3.2 Improvement in 'Time to Answer' with Gap-aware Co-location

In this section, we discuss the performance implications if a scientific simulation's GPU idle periods are used to run some analysis codes useful for the produced scientific data. We use three commonly used analysis algorithms run on scientific data: Convolution, Scan and Histogram.

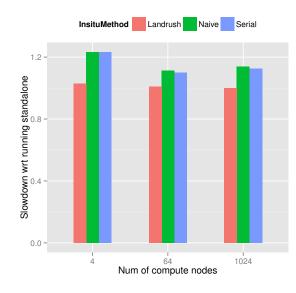

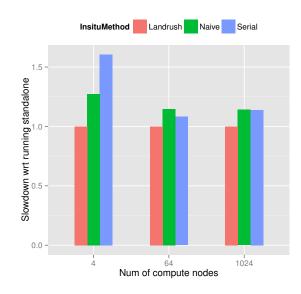

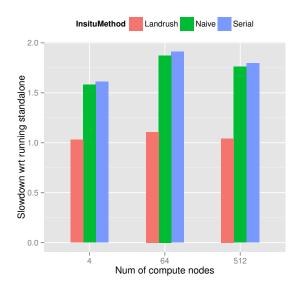

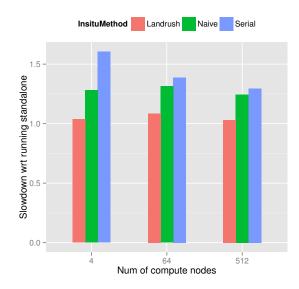

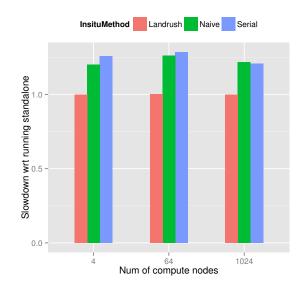

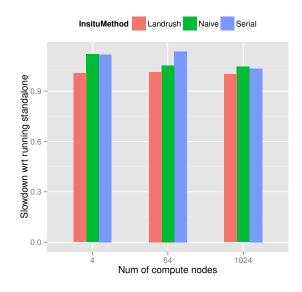

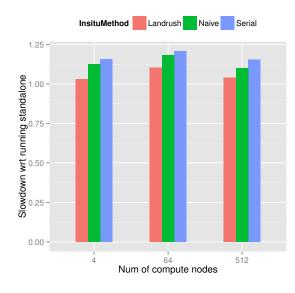

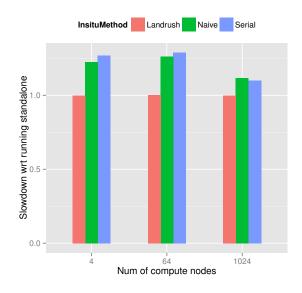

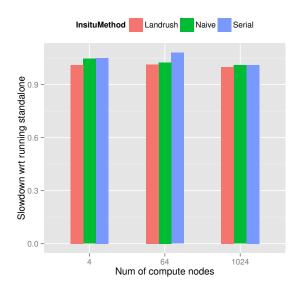

We have shown in the previous sections that different scinetific codes exhibit varying gap amounts on the GPU. We next compare the effects of co-location and serialized execution (Serialized) on the time-to-answer expressed as the % increase in running time over the running time of a standalone execution of a scientific simulation. Two co-location strategies are used: one naively co-locates analysis tasks (Naive) on the GPU relying on the driver and the internal HW threadblock dispatcher, unaware of any contention that may arise; the other (Landrush) co-locates analysis during gaps in the execution of the scientific simulation when the GPU is idle. 100 time steps are executed for the three scientific simulations - LAMMPS, GTC-P, and PIConGPU. The input data size for the analysis application is chosen to be the largest allocated single buffer in the co-running simulation application. Weak scaling is performed at three scales, viz., 4, 64 and 1024 nodes. Due to the limit on atom indices in the Lennard Jones configuration of LAMMPS, the highest scale was limited to 512 nodes.

#### 3.3.2.1 Convolution

Convolution is a fundamental analysis subroutine used by several other higher-level analysis algorithms, most notably, FFT or Fast Fourier Transform. We used a 2-dimensional convolution algorithm where the x- and the y- dimensions are separable using an intermediate buffer. Two kernels are run one for each dimension. The filter co-efficients are stored in constant memory on the GPU to enable fast access.

Experimental results with running convolution in situ are shown in Figures 12, 13 and 14. At a weak scaling of 4 nodes, both serialized and naive configurations co-locate really badly causing slowdowns between 23 and 61%. For the same configuration, the highest slowdown with Landrush is less than 3%.

At 64 and 1024 nodes, the slowdown becomes more tolerable for GTC-P and PIConGPU

Figure 12: Co-location Performance with Convolution : GTC-P

Figure 13: Co-location Performance with Convolution : PIConGPU

Figure 14: Co-location Performance with Convolution : LAMMPS

(as shown in Figure 12 and Figure 13) lying between 8 and 15% but Landrush is still much better keeping slowdowns under 1% for these configurations. But at 64 and 1024 nodes, serialized and naive approaches give very high slowdowns for LAMMPS lying between 76 and 91%.

Although, the slowdown for these configurations using the Landrush approach is not insignificant (4 and 11%), it is within tolerable limits to consider in situ over in-transit. This is shown in Figure 14. Overall using Landrush to run separable convolution over two dimensions, the average speedup seen is 33% compared to the best of the other approaches.

## 3.3.2.2 Histogram

The histogram algorithm we chose for this work performs a sparse histogram over 64 bins. An intermediate buffer is used to stage partial histograms generated by individual thread blocks running on the GPU using the shared memory to compute smaller histograms with much faster data access. Two kernels are run on the GPU with the first one generating the partial histograms and the second one merging them.

We show the performance results of running histogram in situ in Figure 15, 16 and 17. Co-location causes very high slowdowns (between 20 and 60%) at all scales for LAMMPS and PIConGPU. This is shown in Figure 15 and 16. In contrast, the worst slowdown is

Figure 15: Co-location Performance with Histogram : LAMMPS

8.5% when using Landrush.

With GTC-P, slowdown is more tolerable using the serialized or the naive approach (3 to 14%) because timesteps in GTC-P are longer for larger runs (64 and 1024 runs), as shown in Figure 17. Overall using Landrush to run a sparse histogram in situ, the average speedup seen is 17% compared to the best of the other approaches.

#### 3.3.2.3 Scan

Scan (or prefix-sum) is another fundamental algorithm with running time and space requirements similar to moving average computation (that is, O(N)). It is used as a subroutine in many widely used post-processing algorithms, e.g, stream compaction. We have used a divide-and-conquer version of the scan algorithm which runs three kernels on the GPU, a basic inclusive scan, an exclusive scan and a final merge step.

The performance results for co-running scan (or prefix-sum) with different scientific simulations are shown in Figure 18, 19 and 20, with the average speedup being 10%.

When the network communication delays are the smallest (that is, for 4 nodes), the Landrush approach is clearly shown to be useful giving speedups between 9 and 27%. For larger runs on 64 and 1024 nodes, LAMMPS and PIConGPU continue to benefit from using Landrush. This is shown in Figure 18 and 19.

Figure 16: Co-location Performance with Histogram : PIConGPU

Figure 17: Co-location Performance with Histogram : GTC-P

Figure 18: Co-location Performance with Scan : LAMMPS

Figure 19: Co-location Performance with Scan: PIConGPU

Figure 20: Co-location Performance with Scan : GTC-P

In contrast, for GTC-P, the savings diminish due to the higher running time per time step with weak scaling. This is shown in Figure 20.

#### 3.3.3 Discussion

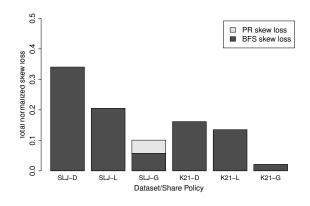

The average speedup obtained with using Landrush to run analysis in situ is 22, 20 and 18 % respectively at 4, 64 and 1024 nodes. This shows that longer communication episodes at higher scale-out does not diminish the importance of Landrush-style co-location of in situ analysis. Naive co-location or serialized execution is not good enough even if there is more slack. It is necessary to carefully place analysis kernels inside gaps when the science application is not using the GPU and that is what Landrush enables.