# **Equivalent Elmore Delay for** *RLC* **Trees**

Yehea I. Ismail, Eby G. Friedman, and Jose L. Neves<sup>1</sup>

Department of Electrical and Computer Engineering University of Rochester Rochester, New York 14627

<sup>1</sup>IBM Microelectronics 1580 Route 52 East Fishkill. New York 12533

Abstract - Closed form solutions for the 50% delay, rise time, overshoots, and settling time of signals in an RLC tree are presented. These solutions have the same accuracy characteristics as the Elmore delay model for RC trees and preserves the simplicity and recursive characteristics of the Elmore delay. The solutions introduced here consider all damping conditions of an RLC circuit including the underdamped response, which is not considered by the classical Elmore delay model due to the nonmonotone nature of the response. Also, the solutions have significantly improved accuracy as compared to the Elmore delay for an overdamped response. The solutions introduced here for RLC trees can be practically used for the same purposes that the Elmore delay is used for RC trees.

### I. Introduction

It has become well accepted that interconnect delay dominates gate delay in current deep submicrometer VLSI circuits [1]-[7]. With the continuous scaling of technology and increased die area, this situation is expected to become worse. In order to properly design complex circuits, more accurate interconnect models and signal propagation characterization are required. Initially, interconnect has been modeled as a single lumped capacitance in the analysis of the performance of on-chip interconnects. Currently, RC models are used for high resistance nets and capacitive models are used for less resistive interconnect [8], [9]. However, inductance is becoming more important with faster on-chip rise times and longer wire lengths. Wide wires are frequently encountered in clock distribution networks and in upper metal layers. These wires have low resistance and can exhibit significant inductive effects. Furthermore, performance requirements are pushing the introduction of new materials for low resistivity interconnect [10]. Inductance is therefore becoming an integral element in VLSI design methodologies, see *e.g.*, [5], [11], [12].

An interconnect line in a VLSI circuit is in general a tree rather than a single line. Thus, the process of characterizing signal waveforms in tree structured interconnect is of primary importance. One of the more popular delay models used within industry for RC trees is the Elmore delay model [13], [14]. Despite not being highly accurate, the Elmore delay is widely used by industry for fast delay estimation. With IC's composed of tens of millions of gates it is impractical to use time consuming methods to accurately evaluate the delay at each node in a circuit. The Elmore delay model is therefore used to quickly estimate the relative delays of different paths in the

This research was supported in part by the National Science Foundation under Grant No. MIP-9610108, a grant from the New York State Science and Technology Foundation to the Center for Advanced Technology - Electronic Imaging Systems, and by grants from the Xerox Corporation, IBM Corporation, and Intel Corporation.

Permission to make digital/hardcopy of all or part of this work for personal or

DAC 99, New Orleans, Louisiana (c) 1999 ACM 1-58113-109-7/99/06..\$5.00 circuit, permitting more exhaustive simulations to be performed for only the critical paths. Also, the Elmore delay is widely used as a delay model for the synthesis of VLSI circuits such as buffer insertion in RC trees and wire sizing [15]-[23]. The wide use of the Elmore delay model as a basis for design methodologies is primarily because the Elmore delay model has a high degree of fidelity [15]: an optimal or near-optimal solution achieved by a design methodology based on the Elmore delay model is also near-optimal based on a more accurate (e.g., SPICE-computed [19]) delay model for routing construction [20] and wire sizing optimization [18]. Simulations [21] have demonstrated that the clock skew derived under the Elmore delay model has a high correlation with SPICE-derived skew data.

The popularity of the Elmore delay model is mainly due to the existence of a simple tractable formula for the delay [24] that has recursive properties [22], making the calculation of the circuit delays highly efficient even in large circuits. However, no equivalent formula for delay calculation has been determined for RLC trees. The absence of a good delay model for RLC trees is primarily due to the fact that the Elmore delay does not consider non-monotone responses [13] which can occur in *RLC* circuits. The focus of this paper is therefore the introduction of a simple tractable delay formula for *RLC* trees that preserves the useful characteristics of the Elmore delay model while maintaining the same accuracy characteristics. The rise time of the signals in an RLC tree is also characterized as well as the overshoots and the settling time (for an underdamped response).

This paper is organized as follows. Background describing the delay of RC trees and an analysis of the relative accuracy of the Elmore delay model are provided in section II. In section III, an equivalent second order approximation of an RLC tree is developed. Closed form solutions for the 50% delay, rise time, overshoots, and settling time of the signals within an RLC tree are introduced in section IV. Finally, some conclusions are offered in section V.

## II. Background and Accuracy of Elmore Delay

A survey of the primary methods for calculating the delay of an RC tree is provided in subsection A. The accuracy of the Elmore delay is characterized in subsection B. It is shown that the Elmore delay for both RC and RLC trees is highly accurate for balanced trees and looses accuracy as the tree becomes more unbalanced.

#### A. Background

In 1948, Elmore [13] introduced a general approach for calculating the propagation delay of a linear system given its transfer function. If the transfer function of the system is G(s), the normalized transfer function g(s) is G(s)/G(0), which can be generally described

$$g(s) = \frac{1 + a_1 s + a_2 s^2 + \dots + a_n s^n}{1 + b_1 s + b_2 s^2 + \dots + b_m s^m},$$

(1)

where  $a_i$  and  $b_i$  are real and m > n. For a monotone response, all the poles of g(s) should be real and for a stable system all the poles should lie on the negative real axis. The unit step response of the normalized transfer function is 1/s\*g(s). In the time domain the transient unit step response e(t) has a final value of one and is monotonically increasing. Elmore proceeded from the observation that the time domain unit step response has the characteristics of the integral of a probability function since it has a final value of one and is monotonically increasing which makes the area under e'(t) equal to

classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage, the copyright notice, the title of the publication and its date appear, and notice is given that copying is by permission of ACM, Inc. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

one and makes e'(t) always positive. Thus, Elmore defined the 50% propagation delay (the time where e(t) is equal to 0.5) as

$$T_D = \int_0^\infty t e^t(t) dt, \qquad (2)$$

which is the centroid of the area under e'(t). By noting that e'(t) for a step input is simply g(t), the transfer function g(s) is

$$g(s) = \int_{0}^{\infty} e'(t)e^{-st}dt = 1 - s\int_{0}^{\infty} te'(t)dt + \frac{s^{2}}{2!}\int_{0}^{\infty} t^{2}e'(t)dt - \dots$$

(3)

Thus, if the normalized transfer function is expanded in the powers of s, the 50% delay can be determined directly as the coefficient of s. From (1), the propagation delay is  $T_D = b_1 - a_1$  which is the definition of the Elmore delay.

In 1987, Wyatt [14] used the relationships that  $b_1$  and  $a_2$  are

$$b_1 = \sum_{i=1}^{m} \frac{1}{p_i}$$

and  $a_1 = \sum_{i=1}^{n} \frac{1}{z_i}$ , (4)

respectively, where  $p_i$  and  $z_i$  are the poles and zeros of the transfer function, respectively. Thus, Wyatt treated  $T_D = b_1 - a_1$  as the reciprocal of the dominant pole (the pole that has the smallest absolute value) of the system. This approximation is accurate for systems that can be modeled by a single dominant pole and has no low frequency zeros near the dominant pole. Using this approximation, the step response of the system is given by

$$e(t) = 1 - \exp(-\frac{t}{T_D}), \tag{5}$$

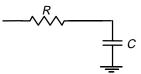

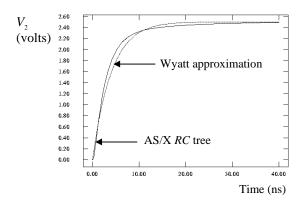

which indicates a 50% propagation delay equal to  $0.693T_{\scriptscriptstyle D}$  rather than  $T_{\scriptscriptstyle D}$  as anticipated by Elmore. For example, the simple *RC* circuit shown in Fig. 1 has the transfer function,

$$g(s) = \frac{1}{sRC + 1}. ag{6}$$

Thus, according to Elmore the propagation delay is *RC* and according to Wyatt the propagation delay is 0.693*RC*. Note that Wyatt's solution is exact for this simple circuit. In general, Wyatt's solution is more accurate than Elmore's solution. Wyatt's modification of the Elmore model is still usually referred to as the Elmore delay.

Fig. 1. Simple RC circuit.

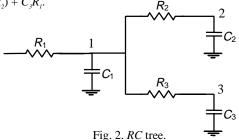

What has made the Elmore (and Wyatt) delay particularly appealing for RC trees is the introduction of a simple closed form solution for the time constant  $T_D$  [24]. For the RC tree shown in Fig. 2, the time constant  $T_{Di}$  at node i is

$$T_{Di} = \sum_{k} C_k R_{ik} , \qquad (7)$$

where k is an index that covers every capacitor in the circuit and  $R_{ik}$  is the common resistance from the input to the nodes i and k. For example, for the RC tree shown in Fig. 2,  $R_{23} = R1$  and  $T_{D2} = C_1R_1 + C_2(R_1+R_2) + C_3R_1$ .

This single pole first order approximation of the transfer function can be inaccurate in certain cases where arbitrary initial conditions can create a low frequency zero, thereby violating one of Wyatt's assumptions [25]. For this reason, Horowitz approximated the voltage across the capacitors in the circuit with a two pole one zero transfer function by matching boundary conditions [26]. Pillage extended this concept by introducing asymptotic wave evaluation (AWE), which depends on matching the first q moments of the transfer function [27]-[29] rather than only the first moment as Wyatt and Elmore did. This concept allows arbitrary accuracy by including additional moments. The normalized transfer function g(s) can be expanded in the powers of s as

$$g(s) = 1 + m_1 s + m_2 s^2 + \dots, (8)$$

where  $m_i$  is the  $i^{th}$  moment of the transfer function [27]. The first 2q moments of the transfer function include the necessary information to calculate the first q poles and the residues of these poles. Numerical methods have been developed [28]-[30] to efficiently calculate the moments, poles, and residues. However, the Elmore (Wyatt) delay is still widely used within industry since it is computationally fast to evaluate. Also, due to the existence of a closed form tractable solution, the Elmore delay is amenable to VLSI-oriented design and synthesis methodologies. Asymptotic wave evaluation is mainly used to analyze those networks that require high accuracy while considering monotone and non-monotone responses.

## B. Analysis of the Accuracy of the Elmore (Wyatt) Delay

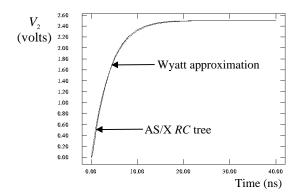

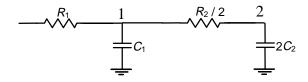

For the RC tree depicted in Fig. 2, if the tree is balanced, i.e.,  $R_2$ =  $R_3$  and  $C_2$  =  $C_3$ , the Elmore (Wyatt) delay accurately describes the signal waveform as shown for output node 2 in Fig. 3. The analytical solution is given by (5) with  $T_{D2}$  calculated according to (7). The transfer function at output node 2 has three poles (there are three capacitors in the circuit) and one finite zero. The other two zeros are at infinity since there are two shunt capacitors in the path between the input and output node 2. Thus, the transfer function is a third order function with one finite zero. However, for a balanced tree, the zero cancels one of the poles and a second order system with no finite zeros remains. This characteristic can be observed by noting that the output at node 3 is the same as the output at node 2 due to the symmetry in the tree. Thus, the RC tree shown in Fig. 2 is equivalent to the reduced order RC ladder circuit shown in Fig. 4, which can be derived by shunting the two branches at nodes 2 and 3. The transfer function at node 2 of this ladder circuit is a second order function with two zeros at infinity and no finite zeros. In general, the equivalent ladder circuit for an RC tree has capacitors equal to the number of levels in the tree. For example, if the tree has a binary branching factor and n levels, the order of the equivalent ladder circuit is n for a tree that has  $2^n-1$  branches. This exponential reduction of the order of the transfer function at the outputs of a balanced tree makes a first order approximation more accurate as compared to the case of an unbalanced tree. Also, since all the finite zeros cancel, Wyatt's assumptions of no low frequency zeros is correct, which again makes Wyatt's solution more accurate at the output nodes of an RLC tree. However, the reduced order transfer function and the cancellation of all of the finite zeros are not the only reasons for the high accuracy of the Elmore (Wyatt) delay for balanced trees. Another important reason is that of the few remaining poles, only one low frequency pole is dominant while all of the other poles are high frequency poles that barely affect the response. This behavior can be illustrated by a closer investigation of Wyatt's approximation and the moments of an RC tree. According to Wyatt and using the value for  $T_{p_i}$  in (7), the transfer function at node i (assumed to be an output node) is

$$g_{i}(s) = \frac{1}{s \sum_{k} C_{k} R_{ik} + 1}.$$

(9)

Expanding this function into powers of *s*, the moments of this transfer function are

$$g_i(s) = 1 - s \sum_{k} C_k R_{ik} + s^2 \left( \sum_{k} C_k R_{ik} \right)^2 - \dots = 1 + m_1^i s + m_2^i s^2 + \dots$$

(10)

Thus the  $r^{th}$  moment is given by

$$m_r^i = \left(-\sum_k C_k R_{ik}\right)^r \tag{11}$$

For a general RC tree, Pillage introduced a simple way to recursively calculate the moments [27]. The moments at node i of an RC tree are

$$m_1^i = \left(-\sum_k C_k R_{ik}\right)$$

$m_2^i = \left(\sum_k \sum_j C_k R_{ik} C_j R_{jk}\right)$  (12)

The second moment can be described as

$$m_2^i = \left(\sum_k C_k R_{ik}\right)^2 - \left(\sum_k \sum_j C_k R_{ik} C_j (R_{jk} - R_{ik})\right)$$

(13)

The second moment of a general RC tree is the same as that of a single pole approximation with an error term that contains the factor,  $R_{ik} - R_{ik}$ . For a balanced tree,  $R_{ik} - R_{ik}$  is equal to zero for most j and k due to symmetry. Thus, the first order Wyatt approximation provides a value for the second moment that is very close to that of the second moment of an output node of a balanced tree. In a similar fashion, higher order moments of Wyatt's approximation are close to the corresponding moments of an output node of a balanced RC tree. This aspect indicates that one of the remaining poles is dominant and the other poles are high frequency poles that can be neglected without a large error. For example, if all the resistances and capacitances in the tree shown in Fig. 2 are equal to one (capacitors are in units of pF, resistors in units of  $k\Omega$ , and time in units of ns), the two poles of the reduced order transfer function at output node 2 are -0.2679 and -3.732. Thus, there is a factor of 14 between the two poles and the high frequency pole (-3.732) can be safely neglected. For larger trees, the single pole approximation is more accurate since the ratio of the number of node pairs j and k for which  $R_{jk} - R_{ik}$  is zero increases as compared to the pairs for which  $R_{jk} - R_{ik}$  is nonzero. This situation makes the moments of the first order approximation more representative of the balanced RC tree.

Fig. 3. Time domain response of the balanced *RC* tree shown in Fig. 2 at output node 2. AS/X [31] simulations are compared to Wyatt's approximation.

Fig. 4. Reduced order *RC* ladder circuit which is equivalent to the *RC* tree shown in Fig. 2 if the tree is balanced.

If the tree shown in Fig. 2 is unbalanced by making  $R_3 = 10R_2$ , errors occur in the accuracy of the derived signal waveform as

shown in Fig. 5. The more unbalanced the tree, the greater the error encountered by the Elmore (Wyatt) delay. In general, it is found that the sensitivity of the second order approximation to an inbalance in an *RLC* tree decreases as the tree size increases.

Fig. 5. Time domain response of the *RC* tree shown in Fig. 2 at output node 2. AS/X [31] simulations are compared to Wyatt's approximation. The tree is unbalanced:  $R_1 = 10R_2$ .

### III. Second Order Approximation for *RLC* Trees

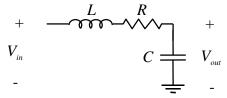

As mentioned in section II, the Elmore (Wyatt) delay does not properly characterize *RLC* networks due to the possibility of a non-monotone response of an *RLC* network. To illustrate this point, consider the simple single section *RLC* circuit depicted in Fig. 6. This circuit has a second order transfer function that is given by

$$g(s) = \frac{1}{s^2 LC + sRC + 1}.$$

Note that the coefficient of  $s'$  is  $RC$ , which does not include the

Note that the coefficient of s' is RC, which does not include the inductance L. This coefficient of the Elmore time constant (and thus the Wyatt approximation) does not depend on the inductance. However, inductance can have a significant effect on the response of a circuit. To better observe the effect of inductance, the transfer function of a circuit can be reconfigured as

$$g(s) = \frac{\omega_n^2}{s^2 + s2\zeta\omega_n + \omega_n^2},$$

(15)

where

$$\zeta = \frac{1}{2} \frac{RC}{\sqrt{LC}}$$

and  $\omega_{\rm n} = \frac{1}{\sqrt{LC}}$  (16)

The poles of the transfer function are

$$P_{1,2} = \omega_n [-\zeta \pm \sqrt{\zeta^2 - 1}]. \tag{17}$$

Note that if  $\zeta$  is less than one, the poles are complex and oscillations occur in the response which violates the monotone response condition of the Elmore delay. In this case, the response is underdamped and overshoots occur. If  $\zeta$  is greater than one, the poles are real and the response is an overdamped response. If  $\zeta$  is equal to one, the response is a critically damped response.  $\zeta$  is called the damping factor of the system. From (16), as the inductance increases,  $\zeta$  decreases which violates the assumption of a monotonic response.

Fig. 6. Simple RLC circuit.

At least a second order approximation is required to characterize a non-monotone response, because a non-monotone response involves complex poles which appear in conjugate pairs in a real system. Thus, a second order system such as (15) is used here to approximate a system with a non-monotone response. It is therefore necessary to determine  $\zeta$  and  $\omega$  in order to make the second order approximation as accurate as possible as compared to the exact transfer function. The transfer function in (15) can be expanded in powers of s where the first two moments of the transfer function are equated to the first two moments of the system which are assumed to be  $m_1$  and  $m_2$ . The expansion of the transfer function in (15) is

$$g(s) = 1 - s \left(\frac{2\zeta}{\omega_n}\right) + s^2 \left(\frac{-1 + (2\zeta)^2}{\omega_n^2}\right) - \dots = 1 + m_1 s + m_2 s^2 + \dots$$

(18)

The parameters that characterize the second order approximation of a non-monotonic system,  $\zeta$  and  $\omega$ , can be calculated in terms of the moments of the non-monotonic system and are

$$\zeta = \frac{-m_1}{2} \frac{1}{\sqrt{m_1^2 - m_2}} \quad \text{and} \quad \omega_n = \frac{1}{\sqrt{m_1^2 - m_2}}$$

(19)

Hence, for a system with a non-monotonic response a second order approximation can be found if the first and second moments of the system are known.

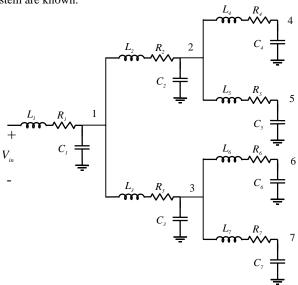

Fig. 7. General *RLC* tree.

For the general RLC tree shown in Fig. 7, the voltage drop at any node i as compared to the input voltage is

$$V_{in}(s) - V_{i}(s) = \sum_{k} C_{k} V_{k}(s) s[R_{ki} + L_{ki} s].$$

(20)

If the input is a unit impulse,  $V_{in}(s)$  is equal to 1.0 and the voltages at the nodes of the tree are the unit impulse responses of these nodes. Thus, the normalized transfer function  $g_i(s)$  at node i is given by  $V_i(s)$

$$g_i(s) = 1 - \sum_k C_k V_k(s) s[R_{ki} + L_{ki} s] = 1 + m_1^i s + m_2^i s^2 + \dots$$

(21)

The first and second moments at node i can be found from

$$m_1^i = \frac{dg_i(s)}{ds}\Big|_{s=0}$$

and  $m_2^i = \frac{1}{2!} \frac{d^2g_i(s)}{ds^2}\Big|_{s=0}$  (22)

Differentiating (21) with respect to  $s$  and substituting  $s = 0$ ,

$$m_{1}^{i} = -\sum_{k} C_{k} R_{ik} V_{k}(s) \Big|_{s=0}$$

$$m_{2}^{i} = -\sum_{k} C_{k} R_{ik} \frac{dV_{k}(s)}{ds} \Big|_{s=0} -\sum_{k} C_{k} L_{ik} V_{k}(s) \Big|_{s=0}.$$

(23)

Note that  $V_k(s) \mid_{s=0} = 1$ , and that  $dV_k(s)/ds \mid_{s=0} = m_1^k$  since  $V_k(s) = g_k(s) = 1 + m_1^k s + m_2^k s^2 + \dots$  Thus, the first and second moments of a general RLC tree at node i are

$$m_{1}^{i} = -\sum_{k} C_{k} R_{ik}$$

$$m_{2}^{i} = \sum_{k} \sum_{j} C_{k} R_{ik} C_{j} R_{kj} - \sum_{k} C_{k} L_{ik}.$$

(24)

Since the Elmore (Wyatt) model approximates the first term in  $m_2^i$

by

$$\left(\sum_k C_k R_{ik}\right)^2$$

, a similar approximation is used here. Thus, the

second moment is approximated by

$$m_2^i = \left(\sum_k C_k R_{ik}\right)^2 - \sum_k C_k L_{ik}$$

(25)

Substituting the first and second moments of a general RLC tree into (19),  $\zeta_i$  and  $\omega_{ii}$  that characterize a second order approximation of the transfer function at node i are

$$\zeta_{i} = \frac{1}{2} \frac{\sum_{k} C_{k} R_{ik}}{\sqrt{\sum_{k} C_{k} L_{ik}}} \quad \text{and} \quad \omega_{ni} = \frac{1}{\sqrt{\sum_{k} C_{k} L_{ik}}}$$

(26)

Note the analogy with  $\zeta$  and  $\omega_n$  for a single *RLC* section in (16). The time constants RC and  $\sqrt{LC}$  are replaced by the summations of the equivalent time constants in the tree. Note also that (26) becomes (16) for a single section. This second order approximation has the same accuracy characteristics as that of the Elmore (Wyatt) approximation for an RC tree. For a step input and a supply voltage of  $V_{DD}$ , the time domain response at node i derived from the second

$$S_{i}(t) = V_{DD} + \frac{V_{DD}}{2\sqrt{\zeta_{i}^{2} - 1}} \left[ \frac{\exp[\omega_{m}t(-\zeta_{i} + \sqrt{\zeta_{i}^{2} - 1})]}{-\zeta_{i} + \sqrt{\zeta_{i}^{2} - 1}} - \frac{\exp[\omega_{m}t(-\zeta_{i} - \sqrt{\zeta_{i}^{2} - 1})]}{-\zeta_{i} - \sqrt{\zeta_{i}^{2} - 1}} \right].$$

(27)

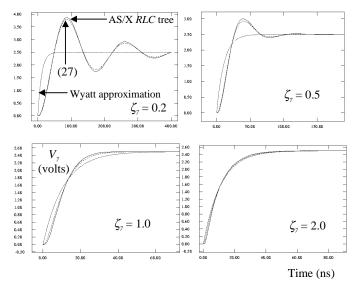

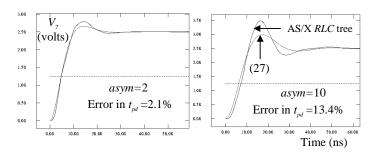

The closed form solution is compared to AS/X [31] simulations of the *RLC* tree shown in Fig. 7 at output node 7 for  $V_{pp} = 2.5$  volts. The simulations are shown in Fig. 8 for a balanced tree with several values of  $\zeta_7$  (the equivalent damping factor at node 7). The Elmore (Wyatt) solution is also shown for comparison. Note the accuracy that the solution exhibits as compared to the AS/X simulations for the case of a balanced tree. The error in the propagation delay is less than 3% for this balanced tree example. In general this solution for RLC trees has the same accuracy characteristics as that of the Elmore (Wyatt) delay with respect to RC trees. The accuracy of the solution introduced here deteriorates as the tree becomes more asymmetric. To quantify the error between the closed form solution introduced here and the AS/X simulations, analytic solutions and simulations for several asymmetric trees are shown in Fig. 9. The parameter asym is introduced to measure the relative asymmetry in an RLC tree. For example, when asym is equal to two, the impedance of the left branch is twice the impedance of the right branch. The higher asym, the higher the asymmetry in the tree. The error in the propagation delay can reach 20% for highly asymmetric trees and the error in the waveform shape is even higher as compared to AS/X simulations. However, these traits are typical accuracy characteristics for the Elmore (Wyatt) approximation for RC trees as discussed before. Thus, this approximation can be used with *RLC* trees for the same purposes that the Elmore (Wyatt) approximation is used with RC trees. Note also that the solution in (27) tends to the Elmore (Wyatt) approximation for large  $\zeta_i$  (low inductance effects), which demonstrates that the general solution introduced here for an RLC tree includes the special case of an RC tree (i.e., zero inductance).

Fig. 8. AS/X simulations as compared to (27) for several values of  $\zeta$ . The Elmore (Wyatt) solution is also shown.

Fig. 9. AS/X simulations as compared to (27) for several asymmetric trees. Results are for node 7 shown in Fig. 7.

## IV. Signal Characterization in RLC Trees for a Step Input

The second order approximation of the transfer function of an RLC tree at node i described by (15) and (26) can be used to determine the time domain signal at node i for an arbitrary input. The Laplace transform of the input is multiplied by the second order approximate transfer function. The inverse Laplace transform is calculated for the resulting expression to determine the time domain signal. Note that a piecewise linear input can also be used [32]. After determining a mathematical expression describing the time domain signal at node i of an RLC tree, an iterative method is needed to calculate the primary parameters characterizing the time domain response such as the 50% propagation delay and the 90% rise time. However, for the special case of a step input, these parameters can be calculated directly without applying the aforementioned procedure due to the mathematical nature of the time domain signal.

The time domain step response of (27) can be used to characterize the 50% delay and the rise time of the signals within an *RLC* tree. The rise time is defined here as the time for the signal to rise from 10% to 90% of the final value. The overshoots and the settling time for the case of an underdamped response are also characterized. In the step response described in (27), note that time is always multiplied by  $\omega_m$ . Thus, if time is scaled by  $\omega_m$ , the step response at node i with a supply voltage of  $V_{DD}$  volts becomes a function of only one variable  $\zeta_i$  and is

function of only one variable

$$\zeta_i$$

and is

$$S_i'(t) = V_{DD} + \frac{V_{DD}}{2\sqrt{\zeta_i^2 - 1}} \left[ \frac{e^{[t'(-\zeta_i + \sqrt{\zeta_i^2 - 1})]}}{-\zeta_i + \sqrt{\zeta_i^2 - 1}} - \frac{e^{[t'(-\zeta_i - \sqrt{\zeta_i^2 - 1})]}}{-\zeta_i - \sqrt{\zeta_i^2 - 1}} \right], \quad (28)$$

where  $S_i'(t)$  is the time scaled response at node i and t' is time scaled

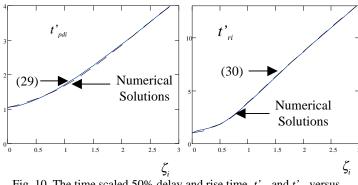

by  $\omega_{ni}$ . The time scaled 50% delay and rise time can be calculated by equating  $S_i'(t)$  to  $0.5V_{DD}$ ,  $0.1V_{DD}$ , and  $0.9V_{DD}$ , respectively. The time scaled 50% delay at node i and the rise time are only functions of one variable  $\zeta_i$ . The 50% delay and the rise time calculated for several values of  $\zeta_i$  are plotted as functions of  $\zeta_i$  in Fig. 10. A curve fitting method is applied to characterize the time scaled 50% delay and rise time as functions of  $\zeta_i$  and these functions are

$$t'_{pdi} = 1.047e^{-\frac{\zeta_i}{0.85}} + 1.39\zeta_i, \tag{29}$$

$$t'_{i} = 6.017e^{-\frac{\zeta_i^{1.35}}{0.4}} - 5e^{-\frac{\zeta_i^{1.25}}{0.64}} + 4.39\zeta_i,$$

(30)

where  $t'_{p,di}$  and  $t'_{ii}$  are the time scaled 50% delay and rise time at node i, respectively. The 50% delay and rise time at node i can be determined by dividing  $t'_{p,di}$  and  $t'_{ii}$  by  $\omega_{p,i}$  and are

$$t_{pdi} = (1.047e^{-\frac{\zeta_i}{0.85}} + 1.39\zeta_i)/\omega_{ni},$$

(31)

$$t_{ri} = (6.017e^{-\frac{\zeta_i^{1.35}}{0.4}} - 5e^{-\frac{\zeta_i^{1.25}}{0.64}} + 4.39\zeta_i)/\omega_{ni}.$$

(32)

Note that the 50% delay and the rise time at node i can be described as

$$t_{pdi} = (1.047e^{-\frac{\zeta_i}{0.85}})/\omega_{ni} + 0.695\sum_k C_k R_{ik} , \qquad (33)$$

$$t_{ri} = (6.017e^{-\frac{\zeta_i^{1.35}}{0.4}} - 5e^{-\frac{\zeta_i^{1.25}}{0.64}})/\omega_{ni} + 2.195\sum_{k} C_k R_{ik} . \tag{34}$$

For large  $\zeta_i$  (low inductance effects), these solutions become the Elmore (Wyatt) approximation of the 50% delay and the rise time for an RC tree at node i. This relationship demonstrates that the general solutions for the 50% delay and the rise time introduced here include the Elmore (Wyatt) delay for the special case of an RC tree. Note also that the general solutions introduced here include all types of responses (underdamped non-monotone, critically damped, and overdamped) in one continuous equation, which is useful in applications such as buffer insertion, wire sizing, and other VLSI-based design, synthesis, and analysis methodologies.

The calculation of  $\zeta_i$  and  $\omega_{ni}$  in (26) requires the calculation of the two summations,  $\sum_{k} C_k R_{ik}$  and  $\sum_{k} C_k L_{ik}$ . The first

summation is the Elmore delay, which can be calculated efficiently with linear complexity by building the solution at a node in a tree based on the solutions at its immediate children, *e.g.*, [22], [27], [29]. The second summation is calculated in precisely the same manner with the branch resistances replaced by the branch inductances. Thus, the second order approximation introduced here and the expressions in (31)-(38) preserve the computational properties of the Elmore delay, permitting highly efficient algorithms to characterize the signals within an *RLC* tree.

Fig. 10. The time scaled 50% delay and rise time,  $t'_{pdi}$  and  $t'_{ri}$ , versus  $\zeta_{i}$ . (29) and (30) are also shown.

For the case of an underdamped non-monotone response ( $\zeta$ , < 1), overshoots and undershoots occur which must also be characterized. Another parameter can also be used to characterize non-monotone responses and is defined as the time when the oscillations about the steady state are smaller than x of the steady state value. This parameter is usually called the settling time and x is typically chosen to be 0.1 [32]. The value of the maximum or minimum oscillations can be determined by differentiating (27) with respect to time and equating the result to zero. The values of the maximum or minimum oscillations at node i as a percentage of the final value are given by

$$\%O_i = (-1)^{n+1} \cdot 100 \exp\left(-\frac{n\pi\zeta_i}{\sqrt{1-\zeta_i^2}}\right) \qquad n = 1, 2, \dots,$$

(35)

where  $\%O_i$  represents the maximum overshoots for n odd and minimum undershoots for n even at node i. The time at which the  $n^{th}$  overshoot occurs at node i is given by

$$t_{0i} = \frac{n\pi}{\omega_{ni}\sqrt{1-\zeta_i^2}} \,. \tag{36}$$

The settling time can be calculated by equating  $\%O_i$  to  $100 \cdot x$  to determine n which represents the first overshoot that is less than x times the steady state value. The time of this overshoot is the settling time and can be calculated by substituting n from  $\%O_i = 100 \cdot x$  in (37). Thus, the settling time at node i is

$$t_{si} = \frac{-\ln(x)}{\zeta_i \omega_{ni}}. (37)$$

For x = 0.1,  $t_{si}$  is

$$t_{si} = \frac{2.3}{\zeta_i \omega_{ni}}. (38)$$

#### V. Conclusions

A general method to characterize the response of a linear non-monotone system that is equivalent to the Elmore delay is presented. The delay expressions for *RLC* trees have the same accuracy characteristics that the Elmore (Wyatt) approximation has for *RC* trees. Simple analytical expressions of signals in an *RLC* tree are provided for the 50% delay, the rise time, overshoots, and settling time. These expressions consider both monotone and non-monotone signal responses. The delay expressions are continuous and hence are useful for optimization, analysis, and synthesis in VLSI-based design methodologies.

## References

- [1] J. M. Rabaey, *Digital Integrated Circuits, A Design Perspective*, Prentice Hall, Inc., New Jersey, 1996.

- [2] D. A. Priore, "Inductance on Silicon for Sub-Micron CMOS VLSI," Proceedings of the IEEE Symposium on VLSI Circuits, pp. 17-18, May 1993.

- [3] D. B. Jarvis, "The Effects of Interconnections on High-Speed Logic Circuits," *IEEE Transactions on Electronic Computers*, Vol. EC-10, No. 4, pp. 476 - 487, October 1963.

- [4] A. Deutsch, et al., "High-Speed Signal Propagation on Lossy Transmission Lines," *IBM Journal of Research and Development*, Vol. 34, No. 4, pp. 601 615, July 1990.

- [5] A. Deutsch, et al., "Modeling and Characterization of Long Interconnections for High-Performance Microprocessors," IBM Journal of Research and Development, Vol. 39, No. 5, pp. 547 667, September 1995.

- [6] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Figures of Merit to Characterize the Importance of On-Chip Inductance," *Proceedings of the IEEE/ACM Design Automation Conference*, pp. 560 – 565, June 1998.

- [7] M. P. May, A. Taflove, and J. Baron, "FD-TD Modeling of Digital Signal Propagation in 3-D Circuits with Passive and Active Loads," *IEEE Transactions on Microwave Theory and Techniques*, Vol. MTT-42, No. 8, pp. 1514 - 1523, August 1994.

- [8] T. Sakurai, "Approximation of Wiring Delay in MOSFET LSI,"

- IEEE Journal of Solid-State Circuits, Vol. SC-18, No. 4, pp. 418 426, August 1983.

- [9] G. Y. Yacoub, H. Pham, and E. G. Friedman, "A System for Critical Path Analysis Based on Back Annotation and Distributed Interconnect Impedance Models," *Microelectronic Journal*, Vol. 18, No. 3, pp. 21 - 30, June 1988.

- [10] J. Torres, "Advanced Copper Interconnections for Silicon CMOS Technologies," *Applied Surface Science*, Vol. 91, No. 1, pp. 112 -123, October 1995.

- [11] C. F. Webb et al., "A 400MHz S/390 Microprocessor," Proceedings of the IEEE International Solid-State Circuits Conference, pp. 448 – 449, February 1997.

- [12] P. J. Restle and A. Duetsch, "Designing the Best Clock Distribution Network," *Proceedings of the IEEE VLSI Circuit Symposium*, pp. 2-5, June 1998.

- [13] W. C. Elmore, "The Transient Response of Damped Linear Networks," *Journal of Applied Physics*, Vol. 19, pp. 55 - 63, January 1948

- [14] J. L. Wyatt, Circuit Analysis, Simulation and Design, Elsevier Science Publishers, North-Holland, 1987.

- [15] J. Cong, L. He, C-K. Koh, and P. Madden, "Performance Optimization of VLSI Interconnect," *Integration, The VLSI Journal*, Vol. 21, pp. 1 - 94, November 1996.

- [16] J. Cong and K. S. Leung, "Optimal Wire Sizing Under the Distributed Elmore Delay Model," Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, pp. 634 - 639, November 1995.

- [17] S. S. Sapatnekar, "RC Interconnect Optimization Under the Elmore Delay Model," *Proceedings of the IEEE/ACM Design Automation Conference*, pp. 387 – 391, June 1994.

- [18] J. Cong and L. He, "Optimal Wire Sizing for Interconnects with Multiple Sources," *Proceedings of the IEEE International Conference on Computer-Aided Design*, pp. 586 574, November 1995

- [19] L. W. Nagel, "SPICE2: A Computer Program to Simulate Semiconductor Circuits," *Technical Report ERL-M520*, UC-Berkelev, May 1975

- [20] K. D. Boese, A. B. Kahng, B. A. McCoy, and G. Robins, "Fidelity and Near-Optimality of Elmore-Based Routing Constructions," *Proceedings of the IEEE International Conference on Computer Design*, pp. 81 – 84, October 1993.

- [21] J. Cong, A. B Kahng, C.-K. Koh and C.-W. A. Tsao, "Bounded-Skew Clock and Steiner Routing Under Elmore Delay," *Proceedings of the IEEE International Conference On Computer-Aided Design*, pp. 66 71, January 1995.

- [22] L. P. P. van Ginneken, "Buffer Placement in Distributed RC-tree Networks for Minimal Elmore Delay," *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 865 - 868, May 1990.

- [23] C. J. Alpert, "Wire Segmenting for Improved Buffer Insertion," Proceedings of the IEEE/ACM Design Automation Conference, pp. 588-593, June 1997.

- [24] J. Rubinstein, P. Penfield, Jr., and M. Horowitz, "Signal Delay in RC Tree Networks," Proceedings of the IEEE/ACM Design Automation Conference, pp. 202 – 211, June 1983.

- [25] L. T. Pillage and R. A. Rohrer, "Delay Evaluation with Lumped Linear RLC Interconnect Circuit Models," *Proceedings of the Caltech Conference on VLSI*, pp. 143-158, May 1989.

- [26] M. A. Horowitz, "Timing Models for CMOS Circuits," Ph.D. Thesis, Stanford University, January 1984.

- [27] L. T. Pillage, R. A. Rohrer, and C. Visweswariah, Electronic Circuit and System Simulation Methods, McGraw-Hill, Inc., 1994.

- [28] L. T. Pillage and R. A. Rohrer, "Asymptotic Waveform Evaluation for Timing Analysis," *IEEE Transactions on Computer-Aided Design*, Vol. CAD-9, No. 4, pp. 352 - 366, April 1990.

- [29] C. L. Ratzlaff, N. Gopal, and L. T. Pillage, "RICE: Rapid Interconnect Circuit Evaluator," Proceedings of the IEEE/ACM Design Automation Conference, pp. 555 – 560, June 1991.

- [30] L. T. Pillage, "Coping with RC(L) Interconnect Design Headaches," Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, pp. 246 – 253, September 1995.

- [31] AS/X User's Guide, IBM Corporation, New York, 1996.

- [32] B. C. Kuo, Automatic Control Systems, A Design Perspective, Prentice Hall of India, New Delhi, India, 1989.